杭州矽力杰笔试

2024年1月杭州市西湖区(技术类)招聘考试《计算机科学》试卷

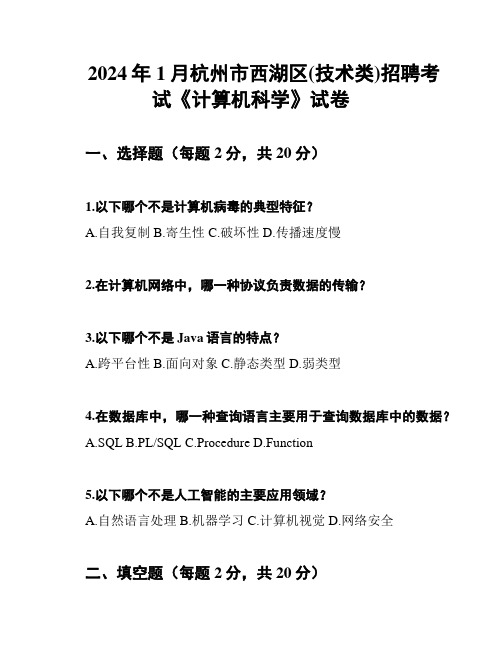

2024年1月杭州市西湖区(技术类)招聘考试《计算机科学》试卷一、选择题(每题2分,共20分)1.以下哪个不是计算机病毒的典型特征?A.自我复制B.寄生性C.破坏性D.传播速度慢2.在计算机网络中,哪一种协议负责数据的传输?3.以下哪个不是Java语言的特点?A.跨平台性B.面向对象C.静态类型D.弱类型4.在数据库中,哪一种查询语言主要用于查询数据库中的数据?A.SQLB.PL/SQLC.ProcedureD.Function5.以下哪个不是人工智能的主要应用领域?A.自然语言处理B.机器学习C.计算机视觉D.网络安全二、填空题(每题2分,共20分)6._____是一种用于描述计算过程的形式化语言。

7._____是一种用于管理和组织计算机硬件和软件资源的操作系统。

9._____是一种用于加密和解密数据的算法。

10._____是一种用于在计算机网络中传输文件的协议。

三、简答题(每题10分,共30分)11.请简述TCP/IP协议的作用和组成。

12.请简述面向对象编程的主要特点。

13.请简述人工智能的发展历程和主要应用领域。

四、案例分析题(共30分)14.某公司采用了一种基于Java语言开发的企业级应用,运行在Linux操作系统上,使用MySQL数据库存储数据。

请回答以下问题:1. 请简述Java语言在企业级应用开发中的优势。

2. 请简述Linux操作系统在企业级应用中的优势。

3. 请简述MySQL数据库在企业级应用中的优势。

五、编程题(共30分)15.请编写一个Java程序,实现以下功能:1. 输入一个字符串,输出字符串中字母和数字的个数。

2. 输入一个整数,输出它的阶乘。

半导体或芯片岗位招聘笔试题与参考答案2025年

2025年招聘半导体或芯片岗位笔试题与参考答案(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、在半导体工艺中,使用多种类型的光刻胶,其中最常用于大规模集成电路生产的是()。

A. GRI-45B. GRI-25C. GRI-46D. GRI-422、MOS(金属-氧化物-半导体)制作技术中,晶体管结构所采用的材料中不包括()。

A. 金属B. 绝缘体C. 导电材料D. 电阻体3.在半导体制造工艺中,以下哪个步骤不属于典型的半导体制造流程?A. 氧化B.光刻C. 薄膜沉积D. 清洗4.下列哪种材料是用于制作半导体器件的理想材料?A. 铜B. 锌C. 石墨D. 硅5、以下哪个半导体工艺技术能够实现更小的晶体管尺寸?A、传统CMOS工艺B、FinFET工艺C、GAAFET工艺D、平面晶体管工艺6、在半导体制造过程中,以下哪个步骤是为了提高硅片的纯度?A、扩散B、蚀刻C、清洗D、热处理7、半导体材料中最常用的材料是什么?()A. 硅(Si)B. 铜(Cu)C. 金(Au)D. 镁(Mg)8、在芯片制造过程中,光刻技术的主要作用是什么?()A. 去除不需要的材料B. 增加材料的功能性C. 将电路设计图案转移到硅片上D. 加热固化硅片结构9.在半导体制造工艺中,以下哪个步骤不属于典型的CMOS工艺流程?A. 氧化硅膜沉积B. 光刻C. 切割D. 离子注入 10.在半导体器件中,MOSFET(金属氧化物半导体场效应晶体管)的主要组成部分包括:A. 沟道区B. 源极C. 栅极D. 上述全部二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪个物理现象通常用于提高晶体管开关速度?()A、短沟道效应B、量子隧道效应C、沟道极化D、多晶硅栅极2、在数字电路中,一种常见的数字缓冲器是 _ 。

()A、反馈触发器B、D触发器C、三态缓冲器D、差分放大器3.以下关于半导体材料的说法正确的是():A. SiC的禁带宽度比 Si 更宽B. GaN的发光效率比 Si 更高C. InGaAs 的电子迁移率比 Si 更快D. ZnSe可以用于制造红光 LED4.在半导体器件制造中,对于离子注入工艺,正确的工作原则包括():A. 离子注入可以形成三维空间中的杂质分布B. 注入离子可以改变晶格特性,增强材料强度C. 注入离子能量过高,可能导致晶体缺陷D. 离子注入温度应当尽可能高,以提高注入效率5.半导体芯片制造过程中,哪些步骤通常需要使用光刻技术?A. 芯片设计B. 光刻C. 薄膜沉积D. 金属化6.在半导体器件中,MOSFET(金属氧化物半导体场效应晶体管)的主要组成部分包括:A. 沟道区B. 源极C. 次沟道区D. 栅极7、在半导体的制造过程中,以下哪个工艺步骤不用于清洗晶圆?A. 刻蚀B. 化学机械抛光C. 清洁去毛刺D.湿法沉积8、在半导体制造过程中,以下哪种类型的晶圆对齐是用来确保图案精确地转移到光罩上的?A. 接触式对准B. 深亚微米对准C. 缩放对准D. 光学对准9.在半导体行业中,晶体管通常分为两种类型:双极型晶体管(BJTs)和场效应晶体管(FETs)。

微电子笔试(笔试和面试题)有答案

微电子笔试(笔试和面试题)有答案第一部分:基础篇(该部分共有试题8题,为必答题,每位应聘者按自己对问题的理解去回答,尽可能多回答你所知道的内容。

若不清楚就写不清楚)。

1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统。

模拟信号,是指幅度随时间连续变化的信号。

例如,人对着话筒讲话,话筒输出的音频电信号就是模拟信号,收音机、收录机、音响设备及电视机中接收、放大的音频信号、电视信号,也是模拟信号。

数字信号,是指在时间上和幅度上离散取值的信号,例如,电报电码信号,按一下电键,产生一个电信号,而产生的电信号是不连续的。

这种不连续的电信号,一般叫做电脉冲或脉冲信号,计算机中运行的信号是脉冲信号,但这些脉冲信号均代表着确切的数字,因而又叫做数字信号。

在电子技术中,通常又把模拟信号以外的非连续变化的信号,统称为数字信号。

FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD 等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

2、你认为你从事研发工作有哪些特点?3、基尔霍夫定理的内容是什么?基尔霍夫电流定律:流入一个节点的电流总和等于流出节点的电流总和。

基尔霍夫电压定律:环路电压的总和为零。

欧姆定律: 电阻两端的电压等于电阻阻值和流过电阻的电流的乘积。

4、描述你对集成电路设计流程的认识。

模拟集成电路设计的一般过程:1.电路设计依据电路功能完成电路的设计。

2.前仿真电路功能的仿真,包括功耗,电流,电压,温度,压摆幅,输入输出特性等参数的仿真。

杭州矽力杰笔试教案资料

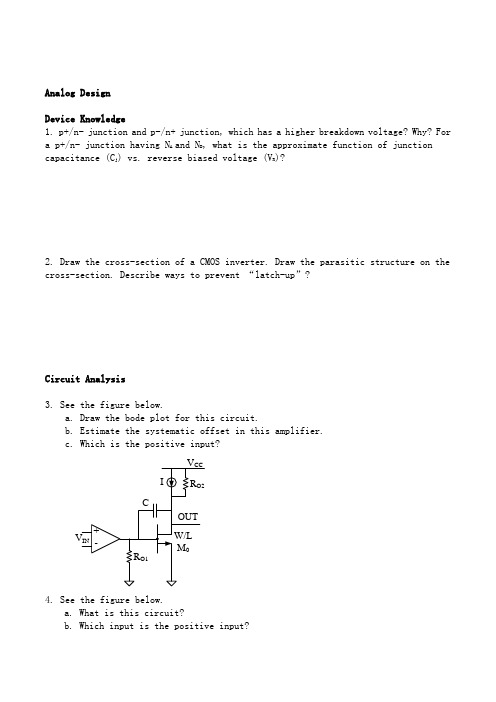

杭州矽力杰笔试IC Design Engineer Test SheetAnalog DesignDevice Knowledge1. p+/n- junction and p-/n+ junction, which has a higher breakdown voltage? Why? For a p+/n- junction having N A and N D, what is the approximate function of junction capacitance (C j) vs. reverse biased voltage (V R)?2. Draw the cross-section of a CMOS inverter. Draw the parasitic structure on the cross-section. Describe ways to prevent “latch-up”?Circuit Analysis3. See the figure below.a. Draw the bode plot for this circuit.b. Estimate the systematic offset in this amplifier.c. Which is the positive input?4. See the figure below.a. What is this circuit?b. Which input is the positive input?c. How much current flows in P2?d. If I=10uA, what is a good selection for the value of R?e. What is the Common Mode Input Range for this circuit?f. What is the Common Mode Output Range for this circuit?g. Assume the only capacitance is from OUT to GND. Draw a Bode Plot.h. Assume no load. What is the maximum positive slew rate if C OUT=C? What is the maximum negative slew rate?5. See the figure below.Assume at time=0 inductor current is 0A. Draw inductor current, V X and V OUT vs. time.I6. See the figure below.a. What is this circuit?b. What is the desired ratio R2/R1?c. How many stable points does this circuit have?d. Assume R1 and R2 have no Temperature Coefficient. Draw a graph of I in R2 vs. Temperature.e. What is the minimum supply voltage necessary for this circuit to work properly?OUT7. See the figure below.a. Write the gain equation of each circuit.b. Assuming V O=0 at time 0. Sketch V O(t) for the given input signal.ABC8. Draw Buck Converter Circuit and key waveform, explain the basic operations at steady state.OtherMust Answer (Question 1-3)Question 1:Write the V/I relationship equations for resistor (R), capacitor (C), and inductor (L).Question 2:Given V B in Table 1, please calculate V C and V E. Assumptions: beta of NPN is infinity, P-N junction forward voltage drop is 0.7V.Question 3:假设图中理想放大器工作在深度负反馈状态,请计算下图输出端电压(V OUT)。

IC笔试题大全(部分含答案)

EE笔试/面试题目集合分类--IC设计基础1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

(仕兰微面试题目)2、FPGA和ASIC的概念,他们的区别。

(未知)答案:FPGA是可编程ASIC。

ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点模拟电路1、基尔霍夫定理的内容是什么?(仕兰微电子)2、平板电容公式(C=εS/4πkd)。

(未知)3、最基本的如三极管曲线特性。

(未知)4、描述反馈电路的概念,列举他们的应用。

(仕兰微电子)5、负反馈种类(电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈);负反馈馈的优点(降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用)(未知)6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子)7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。

(未知)8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。

(凹凸)9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺点,特别是广泛采用差分结构的原因。

(未知)10、给出一差分电路,告诉其输出电压Y+和Y-,求共模分量和差模分量。

(未知)11、画差放的两个输入管。

(凹凸)12、画出由运放构成加法、减法、微分、积分运算的电路原理图。

并画出一个晶体管级的运放电路。

(仕兰微电子)13、用运算放大器组成一个10倍的放大器。

半导体或芯片岗位招聘笔试题与参考答案(某大型国企)

招聘半导体或芯片岗位笔试题与参考答案(某大型国企)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、以下哪个选项不属于半导体制造过程中的关键步骤?A、光刻B、蚀刻C、离子注入D、组装2、在半导体行业中,以下哪个术语用来描述晶体管中用于控制电流流动的导电区域?A、源极B、栅极C、漏极D、基区3、题干:以下关于半导体制造工艺的描述,正确的是:A、光刻工艺是将光刻胶图案转移到硅片上的过程。

B、蚀刻工艺是利用光刻胶保护硅片,通过化学或物理方法去除硅片表面不需要的层。

C、离子注入是将离子直接注入硅片表面,用于掺杂的过程。

D、扩散工艺是通过在硅片表面形成一层光刻胶,然后利用高温使杂质原子扩散到硅片中。

4、题干:在半导体制造过程中,以下哪种缺陷类型对芯片性能影响最为严重?A、表面缺陷B、体缺陷C、界面缺陷D、晶格缺陷5、在半导体制造过程中,以下哪种材料通常用于制造晶圆的基板?A. 石英玻璃B. 单晶硅C. 聚酰亚胺D. 氧化铝6、以下哪种技术用于在半导体器件中实现三维结构,从而提高器件的集成度和性能?A. 厚膜技术B. 硅片减薄技术C. 三维封装技术D. 双极型晶体管技术7、在半导体制造过程中,下列哪种缺陷类型是指由于光刻胶在曝光和显影过程中产生的缺陷?A. 逻辑缺陷B. 光刻缺陷C. 杂质缺陷D. 损伤缺陷8、下列哪种技术用于在硅片上形成纳米级结构的半导体器件?A. 溶胶-凝胶法B. 化学气相沉积法(CVD)C. 离子束刻蚀D. 电子束刻蚀9、以下哪项不属于半导体制造过程中的关键步骤?()A、光刻B、蚀刻C、离子注入D、焊接二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪些是半导体制造过程中常见的工艺步骤?()A、光刻B、蚀刻C、离子注入D、化学气相沉积E、掺杂2、以下哪些是影响芯片性能的关键因素?()A、晶体管结构B、工艺节点C、材料选择D、功耗控制E、封装设计3、以下哪些技术是现代半导体制造中常用的光刻技术?A. 干法光刻B. 湿法光刻C. 电子束光刻D. 紫外光刻E. 激光直接成像4、下列关于半导体材料掺杂的描述,正确的是:A. N型半导体通过加入五价元素如磷(P)或砷(As)来制造B. P型半导体通过加入三价元素如硼(B)或铟(In)来制造C. 掺杂的目的是增加半导体的导电性D. 杂质原子在半导体中的浓度被称为掺杂浓度E. 掺杂过程会改变半导体的电学性质5、以下哪些技术属于半导体制造过程中常用的光刻技术?()A. 光刻胶技术B. 具有纳米级分辨率的电子束光刻C. 紫外光光刻D. 平板印刷技术E. 双光束干涉光刻6、以下哪些因素会影响半导体器件的可靠性?()A. 热稳定性B. 电压应力C. 材料纯度D. 封装设计E. 环境因素7、以下哪些是半导体制造过程中常见的缺陷类型?()A. 晶圆划痕B. 氧化层破裂C. 线路短路D. 热应力裂纹E. 杂质沾污8、在半导体器件的测试与表征中,以下哪些方法用于评估器件的电气特性?()A. 频域分析B. 温度特性测试C. 噪声分析D. 瞬态响应测试E. 微观结构分析9、以下哪些是半导体制造过程中常用的物理或化学方法?()A. 光刻B. 化学气相沉积(CVD)C. 离子注入D. 磨光E. 蚀刻三、判断题(本大题有10小题,每小题2分,共20分)1、半导体制造过程中,光刻是直接将电路图案转移到硅片上的关键步骤。

集成电路设计岗位招聘笔试题及解答(某世界500强集团)2024年

2024年招聘集成电路设计岗位笔试题及解答(某世界500强集团)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、下列晶体管类型的半导体材料中,通常用于集成电路制造中的集电极,其来源最为广泛且成本较低的是?A. 氮化镓 (GaN)B. 硅 (Si)C. 锗 (Ge)D. 金刚石2、在集成电路设计行业中,总线宽度是指一次可以传输的信号数量。

下列总线的有效性排列中,哪一组是可以用在8位处理器的?A. 1位或4位总线B. 4位或8位总线C. 8位或16位总线D. 4位或16位总线3、下列哪种电路拓扑结构通常用于实现高增益放大器?A.மமமமமமமமமமB. 喜欢的肯定是什么?4、CMOS工艺中,为降低漏电流和提高开关速度,通常采用什么措施?A. 增加阈值电压B. 减少阈值电压C. 降低工作电压D. 提高工作电压5.在集成电路设计中,以下哪个因素对芯片的性能有最大影响?A. 电流大小B. 电压水平C. 晶体管尺寸D. 电阻值6.在设计集成电路时,以下哪种布局方法可以最小化信号传输延迟?A. 混合布局B. 紧凑布局C. 顺序布局D. 扇形布局7、数字选数字。

在模拟到数字转换电路中,使用最多的技术是()。

A、反相放大器B、运算放大器C、二极管放大器D、集成运放放大器8、数字选数字。

双极型晶体管在半导体工艺中,通常使用()掺杂技术。

A、P区掺杂B、N区掺杂C、平面掺杂D、表面掺杂9、设一款MMIC Amplifier电路的截止频率为10GHz,其放大倍数为20dB,则该放大器在1kHz处的增益 (以分贝为单位)A.约为20dBB.约为1.2dBC.约为0dBD.约为200dB 10、下列哪种晶体管的工作原理是基于电流的控制效果?A.MOSFETB.BJTTFETD.FinFET二、多项选择题(本大题有10小题,每小题4分,共40分)1.集成电路设计中,以下哪个因素对芯片性能影响最大?A. 电流大小B. 电压频率C. 电磁干扰D. 噪声大小2.在CMOS工艺中,以下哪种器件主要用于实现逻辑非功能?A. 二极管B. 晶体管C. 互连D. 电容3、集成电路设计中,每种不同类型的门电路都有其组成形式和特性方程,其中三态门(Out,tree)电路的特性方程,下述的英文表达准确的为:() A) Out = (A!) B) Out = ( *mc*ai) C) Out = ( ) is not the right choice D)Out = 0并且向上false4、某一电路的表达式为 Out = ( * ),( ) 表示废物符号,关于此电路的描述正确的是哪些?( ) A)只要有一个输入为1,则 Out=1,其 Low电平比单输出 t 高B)当 A,B,C 三个输入都为 0 时, Out=0 C)若 C=0,无论输入为0,1均不产生 anything D)三种输入相等时,三种条件下的结果一样5、下列关于 CMOS 集成电路的描述,哪些是正确的?( )A. CMOS 电路采用互补型 MOSFET 作为开关元件B. CMOS 电路在高速工作时功耗较低C. CMOS 电路主要用于模拟信号处理D. CMOS 电路在静态功耗方面较低6、下列关于设计流程中布局規劃的描述,哪些是正确的?( )A. 布局规划直接影响到芯片的性能B. 布局规划需要考虑每一级线路的容量C. 布局规划主要关心电路的功能实现D. 布局规划阶段可以随意修改电路结构7、在数字电路设计中,以下哪些电压类型是常见的逻辑门电压()。

半导体或芯片岗位招聘笔试题与参考答案

招聘半导体或芯片岗位笔试题与参考答案(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、半导体器件中,以下哪个材料是制作晶体管的最佳选择?A、硅(Si)B、锗(Ge)C、砷化镓(GaAs)D、碳化硅(SiC)2、在半导体工艺中,以下哪个步骤用于形成晶体管的有源区?A、光刻B、扩散C、蚀刻D、离子注入3、题干:在半导体制造过程中,下列哪种设备用于在硅片上形成绝缘层?A. 溶胶-凝胶法B. 气相沉积法C. 化学气相沉积法D. 离子注入法4、题干:下列哪种材料在制造芯片时用作硅片的基板?B. 蓝宝石C. 硅D. 玻璃5、题干:在半导体制造过程中,以下哪个步骤是用于形成晶体管的沟道区域?A. 源极/栅极/漏极扩散B. 化学气相沉积(CVD)C. 光刻D. 离子注入6、题干:以下哪个选项不是半导体器件性能退化的主要因素?A. 氧化B. 金属污染C. 温度D. 磁场7、以下哪种技术不属于半导体制造中的光刻技术?A. 具有曝光光源的接触式光刻B. 具有投影光源的接触式光刻C. 具有曝光光源的投影式光刻D. 具有投影光源的扫描式光刻8、在半导体制造过程中,以下哪种工艺是用来形成半导体器件中的掺杂层的?A. 离子注入B. 化学气相沉积D. 硅烷刻蚀9、在半导体制造过程中,下列哪一种工艺主要用于晶体管的掺杂?A. 离子注入B. 化学气相沉积C. 蚀刻D. 光刻 10、以下哪一项不是半导体芯片制造过程中的关键环节?A. 材料制备B. 设备测试C. 晶圆加工D. 封装测试二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪些是半导体制造过程中的关键工艺步骤?()A. 光刻B. 沉积C. 刻蚀D. 化学气相沉积E. 离子注入2、以下哪些是影响芯片性能的关键因素?()A. 电路设计B. 材料选择C. 制造工艺D. 封装技术E. 电源电压3、以下哪些是半导体制造过程中的关键工艺步骤?A. 光刻B. 溅射C. 化学气相沉积D. 离子注入E. 硅片切割4、以下哪些是影响半导体器件性能的主要因素?A. 杂质浓度B. 静电放电C. 温度D. 电压E. 射线辐照5、以下哪些是半导体制造过程中常见的工艺步骤?A. 光刻B. 化学气相沉积(CVD)C. 离子注入D. 硅片切割E. 激光打标6、在芯片设计过程中,以下哪些工具或方法有助于提高设计效率?A. 逻辑综合B. 硅基模拟C. 动态仿真D. FPGA原型E. 硅验证7、以下哪些是半导体制造过程中常见的工艺步骤?()A. 光刻B. 刻蚀C. 化学气相沉积D. 离子注入E. 线宽控制8、以下哪些因素会影响芯片的性能?()A. 集成度B. 电压C. 温度D. 材料E. 制造工艺9、以下哪些是半导体制造过程中的关键工艺步骤?()A. 光刻B. 化学气相沉积C. 离子注入D. 晶圆切割E. 热处理 10、以下哪些是影响半导体器件性能的关键参数?()A. 集电极电压B. 跨导C. 开关速度D. 噪声电压E. 耗散功率三、判断题(本大题有10小题,每小题2分,共20分)1、半导体制造过程中,光刻是直接在硅片上形成电路图案的关键步骤。

半导体或芯片岗位招聘笔试题及解答(某世界500强集团)

招聘半导体或芯片岗位笔试题及解答(某世界500强集团)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、下列关于半导体材料的描述,错误的是:A、半导体材料在室温下的导电性介于导体和绝缘体之间。

B、常见的半导体材料有硅、锗等。

C、半导体材料的导电性可以通过掺杂来调节。

D、半导体材料在高温下的导电性会降低。

2、在半导体芯片制造过程中,以下哪个步骤是为了提高芯片的集成度?A、光刻B、蚀刻C、离子注入D、化学气相沉积3、以下哪种类型的晶体管是现代半导体器件中应用最为广泛的?A、双极型晶体管(BJT)B、金属-氧化物-半导体场效应晶体管(MOSFET)C、隧道晶体管(Tunnel FET)D、光晶体管(Phototransistor)4、在半导体制造过程中,用于去除硅片表面杂质的工艺是?A、光刻(Photolithography)B、蚀刻(Etching)C、离子注入(Ion Implantation)D、化学气相沉积(Chemical Vapor Deposition)5、在半导体制造过程中,以下哪种设备用于在硅片表面形成绝缘层?A. 离子注入机B. 化学气相沉积(CVD)设备C. 离子束刻蚀机D. 线宽测量仪6、在芯片设计过程中,以下哪个术语描述了晶体管中电子流动的方向?A. 电流B. 电压C. 漏极D. 源极7、以下哪个选项不属于半导体制造过程中的关键步骤?()A. 光刻B. 化学气相沉积C. 蚀刻D. 钎焊8、以下哪种类型的晶体管在数字电路中应用最为广泛?()A. 双极型晶体管B. 场效应晶体管C. 双栅场效应晶体管D. 双极型与场效应晶体管的混合结构9、以下哪个选项不属于半导体制造过程中常见的物理气相沉积(PVD)技术?A. 真空蒸发B. 离子束刻蚀C. 化学气相沉积D. 热丝蒸发 10、在半导体制造过程中,以下哪种工艺是为了提高晶圆的表面平整度?A. 光刻B. 化学机械抛光(CMP)C. 离子注入D. 硅片切割二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪些是半导体制造过程中常见的工艺步骤?()A、光刻B、蚀刻C、化学气相沉积D、离子注入E、封装2、以下关于芯片设计的描述,正确的是?()A、芯片设计主要包括逻辑设计、物理设计和验证设计B、逻辑设计关注电路的功能实现,物理设计关注电路的布局和布线C、验证设计确保设计的正确性,通常通过仿真和测试来完成D、芯片设计过程中,设计者需要考虑功耗、性能和面积等因素E、以上都是3、以下哪些是半导体制造过程中的关键工艺步骤?()A. 光刻B. 化学气相沉积(CVD)C. 离子注入D. 线宽测量E. 晶圆切割4、以下关于半导体材料的描述中,正确的是?()A. 半导体材料的导电性介于导体和绝缘体之间。

[留学生找工作] 诺基亚西门子实习笔试面试分享

![[留学生找工作] 诺基亚西门子实习笔试面试分享](https://img.taocdn.com/s3/m/eb6bbf49f01dc281e53af0ce.png)

[留学生找工作] 诺基亚西门子实习笔试面试分享华为没戏,比较不爽.于是晚上上了intern,看了下诺西的实习生招聘,发现全部是软件类的.将四个职位信息打印出来.第二天(27号)跑到了滨江.好多人呀.等到下沙一些高校的学生来了后,HR介绍了诺西的发展情况,觉得还是很有潜力的一个公司.光是那栋巨牛的楼就很气派呀.九点多钟吧,让我们自己决定选哪个职位,就跟哪个HRMM去相应的房间笔试.发现外企的房间全都被冠以各种名字,如凡尔赛,苏伊士(我在阿朗也看了这个房间,呵呵)等等.考试时间一个小时,其实我觉得三十分钟足够了,因为好多题不会,不会还是不会,会的人一下子可以写完了.当然其他SW部门的我不太清楚了.我选了一个自己听都没听过的LTE测试的卷子,做了起来.感觉好多通信的东东,就是一顿瞎写.又发现有两个Coding的题,像挤牙膏一样挤出来一些代码.然后又发现一个IBM的面试题,就是讲村子里有五十条狗那个题.我想都没想就写三道题,不太想推理,就直接瞎写一通了.提前交卷了.然后去食堂了.附笔试题(前五题必做,后四个题选答两个)1、使用3G(2G)手机打电话,可能要用到什么通信设备,它们各自有什么用途?(我居然把光缆,卫星,海底电缆也写上了,后来让面试官引为笑谈)2、谈谈通信软件的测试的方法?3、村子里有50个人,每人有一条狗,在这50条狗中有病狗(这种病不传染),于是人们要找出病狗。

每个人可以观察其他49条狗,以判断他们是否生病,(如果有病一定能看出来),只有自己的狗不能看,观察后得到的结果不得交流,也不能通知病狗的主人。

主人一旦推算出自己家的狗是病狗就是枪毙自己的狗(发现后必须在一天内枪毙),而且每个人只有权利枪毙自己的狗,没有权利打死其他人的狗。

第一天大家全看完了,但枪没有响,到了第三天传来一阵枪声,问村里共有几条病狗,如何推算出来的?4、测试工程师jack(好像不叫这个名字呵呵)这个月计划有80个case,但是到月底只有两三天的时候只完成了40个,如果是你,你会怎么办?5、如果一个ATM机投入使用前,应该做一些什么测试?写出测试方案?Coding6、给出一段代码,初始给定三个数a, b, c经过一些for switch循环后的结果?7、写一个函数,用指针实现字函数串的反转,完成函数定义,void string_reverse(char *string).可以不使用数组存储中间变量.8、看都没怎么看,忘记了…9什么是HSPDA的全称?其关键技术是什么?(我当时写的是高速个人数字助理,瀑布汗!!) 做完后,当然感觉玩完了.一边做还一边发了好多手机短消息(当然和考试无关).于是在食堂吃完了饭,就一门心思想着赶紧出结果等大巴回去.下午在没有空调的大房子等结果,结果奇迹出现了,大巴来了,我的面试通知也来了.真是太奇怪了.然后就想攒个面经吧.三点钟,叫到我的名字.考官居一边纠正我的发音,呵呵.然后讲项目,边讲面试官边提问.我一边回答.面试官给我讲了一下LTE和部门情况,问我有什么idea没有.我说现在没有,如果有机会在工作当中可能会有.然后面试官问了我的性格问题,呵呵,问仔细认真是不是你最大的优点?然后又问了一个性格的问题.然后又说了具体的工作职责,实习要做些什么事情.因为有一些任务是lab support.考官问了好多实验室管理的问题,具体到我们实验室有几台示波器,安捷伦的频谱仪的具体型号,呵呵.然后又考了我一些通信方面的东西,我答得一般,他强调了好多次这是一些common的东西,我说我会好好再补习的.呵呵.后来又聊了一些关于公司的情况,如这个职位的发展前景等等.我也问了一些问题.感觉自己并不被动.而是交谈得非常愉快.总共面试的时间大概持续了四十多分钟吧.最后考官给我留了个联系方式.然后致谢,我就回去等消息了.附部分面试题:1、模拟信号怎么样变成数字信号?采样(或抽样,取样),保持(好像这个也可以省略),量化,编码2、是什么编码?信源编码还是信道编码?3、一般的编码有哪些?BPSK是调频还是调相?(还好我记得是phase呵呵)4、通信设备一般供电电压?(分交直流,交流一般有220伏和330伏?直流有+24V,--48V??)5、单模光纤和多模光纤的区别?。

杭州矽力杰笔试

Analog DesignDevice Knowledge1. p+/n- junction and p-/n+ junction, which has a higher breakdown voltage? Why? Fora p+/n- junction having NA and ND, what is the approximate function of junctioncapacitance (Cj ) vs. reverse biased voltage (VR)?2. Draw the cross-section of a CMOS inverter. Draw the parasitic structure on the cross-section. Describe ways to prevent “latch-up”?Circuit Analysis3. See the figure below.a. Draw the bode plot for this circuit.b. Estimate the systematic offset in this amplifier.c. Which is the positive input?4. See the figure below.a. What is this circuit?b. Which input is the positive input?c. How much current flows in P2?d. If I=10uA, what is a good selection for the value of R?e. What is the Common Mode Input Range for this circuit?f. What is the Common Mode Output Range for this circuit?g. Assume the only capacitance is from OUT to GND. Draw a Bode Plot.h. Assume no load. What is the maximum positive slew rate if COUT=C? What is the maximum negative slew rate?5. See the figure below.Assume at time=0 inductor current is 0A. Draw inductor current, VX and VOUTvs. time.I6. See the figure below.a. What is this circuit?b. What is the desired ratio R2/R1?c. How many stable points does this circuit have?d. Assume R1 and R2have no Temperature Coefficient. Draw a graph of I in R2vs.Temperature.e. What is the minimum supply voltage necessary for this circuit to work properly?OUT7. See the figure below.a. Write the gain equation of each circuit.b. Assuming VO =0 at time 0. Sketch VO(t) for the given input signal.ABC8. Draw Buck Converter Circuit and key waveform, explain the basic operations at steady state.OtherMust Answer (Question 1-3)Question 1:Write the V/I relationship equations for resistor (R), capacitor (C), and inductor (L).Question 2:Given VB in Table 1, please calculate VCand VE. Assumptions: beta of NPN is infinity,P-N junction forward voltage drop is .Question 3:假设图中理想放大器工作在深度负反馈状态,请计算下图输出端电压(V)。

半导体或芯片岗位招聘笔试题及解答(某大型国企)

招聘半导体或芯片岗位笔试题及解答(某大型国企)一、单项选择题(本大题有10小题,每小题2分,共20分)1、下列哪种材料最适合用于制造半导体器件?A. 铜B. 硅C. 金D. 银答案:B解析:在这些选项中,硅是最常用的半导体材料。

铜、金和银都是良好的导体,而非半导体,因此不适合用来制造半导体器件。

2、在P型半导体中,多数载流子是什么?A. 自由电子B. 空穴C. 质子D. 中子答案:B解析: P型半导体是通过向纯半导体(如硅)中掺入三价元素(如硼)来形成的。

这种掺杂会创造出额外的空穴,这些空穴成为多数载流子。

自由电子则成为少数载流子。

质子和中子不是半导体中的载流子。

3、在半导体工艺中,以下哪种材料常用于制造N型半导体?A. 硼(B)B. 磷(P)C. 镓(Ga)D. 硅(Si)但未经掺杂答案:B解析:N型半导体是指在半导体材料中掺入少量五价元素(如磷P)后形成的半导体。

这些五价元素替代了半导体中的某些四价元素(如硅Si或锗Ge中的原子),从而产生了多余的自由电子,使得半导体导电性增强,并呈现出带负电的特性,即N型半导体。

硼(B)是三价元素,常用于制造P型半导体;镓(Ga)和硅(Si)本身并不直接决定半导体的类型,而是需要通过掺杂其他元素来改变其导电性。

4、在CMOS(互补金属氧化物半导体)技术中,以下哪个组件通常用于实现逻辑非(NOT)门的功能?A. NMOS晶体管B. PMOS晶体管C. NMOS和PMOS晶体管组合D. 电阻和电容组合答案:C解析:在CMOS技术中,逻辑非(NOT)门通常由一对互补的MOS晶体管(即NMOS 和PMOS晶体管)组合而成。

这种配置利用了NMOS晶体管在逻辑高(接近电源电压)时导通、PMOS晶体管在逻辑低(接近地电位)时导通的特性。

当输入为高电平时,NMOS 晶体管导通,将输出拉至低电平;当输入为低电平时,PMOS晶体管导通,将输出拉至高电平。

这样,就实现了逻辑非的功能。

矽力杰公司笔试题库

矽力杰公司笔试题库矽力杰公司作为一家领先的高科技企业,其笔试题库涵盖了多个领域,以确保选拔到具有扎实专业知识和解决问题能力的人才。

以下是矽力杰公司笔试题库的概述:一、基础知识测试矽力杰公司笔试题库首先会对应聘者的基础知识进行测试,这包括但不限于:- 数学问题,如代数、几何和概率论。

- 编程语言基础,如C/C++、Java或Python。

- 数据结构和算法,例如排序、搜索、树和图的基本概念。

二、专业知识测试针对不同岗位的专业知识测试,矽力杰公司会设计不同的题目,例如:- 电子工程领域的电路设计和分析问题。

- 计算机科学领域的操作系统、网络和数据库问题。

- 机械工程领域的力学和材料科学问题。

三、逻辑推理能力测试逻辑推理能力是解决问题的关键,矽力杰公司会通过以下方式测试应聘者的逻辑推理能力:- 逻辑谜题,如数列推理、图形推理等。

- 案例分析,要求应聘者分析问题并提出解决方案。

四、英语能力测试由于矽力杰公司可能涉及国际合作,英语能力测试也是必不可少的部分,包括:- 阅读理解,涉及科技文献和报告。

- 写作能力,可能要求应聘者撰写技术报告或项目提案。

五、创新思维和问题解决能力测试矽力杰公司鼓励创新思维,因此会通过以下方式测试应聘者的创新能力和问题解决能力:- 开放性问题,要求应聘者提出创新的解决方案或改进现有技术。

- 模拟项目,让应聘者在有限的时间内解决一个实际问题。

六、企业文化和价值观测试了解应聘者是否符合公司的企业文化和价值观也是选拔过程中的重要一环,这可能包括:- 对公司历史、使命和价值观的了解。

- 行为面试题,评估应聘者的团队合作能力和职业道德。

结束语矽力杰公司笔试题库的设计旨在全面评估应聘者的综合素质,确保选拔到最适合公司的人才。

我们期待有才华、有热情的你加入我们的团队,共同推动科技的进步和创新。

请注意,以上内容仅为示例,实际的笔试题库可能会根据公司的具体需求和岗位特点进行调整。

矽力杰笔试题

文档收集于互联网,已重新整理排版.word 版本可编辑.欢迎下载支持.

1文档来源为:从网络收集整理.word 版本可编辑. 前三题为必做题,全为英文描述题干

1、写出电阻R 、电容C 、电感L 的V/I 关系式;

2、给出B V 的电压值求NPN 型三极管的C V 、E V (晶体管的开启电压为0.7v)

3.在满足深度负反馈的条件下,求出以下放大电路的O V .

整份试卷包含所有面试方向的题,最后一部分是IC layout 方向的笔试题:

1.简述CMOS 的工艺流程

2.给出nand2的管级图画出其layout 。

3.下图电路图中有两个MOSFET (MA and MB)假设每个MOSFET 有两个gate finger ,右下版图应如何连接,才能使MA and MB 匹配。

4.画出不同的电流镜图,并简述各自特点。

面试时问到的问题

技术部:

1.晶体管的工作原理

2.你在青软实训学到了什么

3.你觉得怎样布局、布线,该注意哪些方面

tch-up 的原理,形成示意图并提取其电路图

5.ESD 的工作原理,做ESD 时你觉得应该注意哪些方面。

负责人:一直不停地从你回答的话中找问题,问问题,

1.自对准工艺(SALICIDE )原理,后做栅会出现什么后果

2.CMOS 的工艺流程

tch-up 的原理以及防止措施, Guard ring 的作用,保护作用具体是怎样做到的。

4.Bandgap 的晶体管部分为什么做成方形。

2024年三年级数学下册期中考试题【及参考答案】

• 通过与苹果的合作,提高了矽力杰半导体在消费电子领域的品牌知名

度和市场占有率

矽力杰半导体与华为公司的合作

• 为华为的智能手机、平板电脑、数据中心等产品提供创新和可靠的传

感器芯片和存储器芯片

• 通过与华为的合作,拓展了矽力杰半导体在通信和数据中心领域的市

场份额

03

矽力杰半导体市场趋势分析与未来展

• 为中低端智能手机提供高性价比的芯片解决方案,满足市场需求

• 通过与行业领导企业的合作,提高品牌知名度和市场占有率

矽力杰半导体在物联网市场的布局与战略

• 为智能家居、可穿戴设备等领域提供创新和可靠的芯片解决方案

• 通过技术创新和产品升级,满足物联网领域对高性能和低功耗的需求

⌛️

矽力杰半导体在人工智能市场的布局与战略

矽力杰半导体与行业领导企业的合作案例与成果展示

矽力杰半导体与特斯拉公司的合作

• 为特斯拉的电动汽车、智能驾驶等产品提供高效、安全的电源管理

芯片和信号处理芯片

• 通过与特斯拉的合作,进一步巩固了矽力杰半导体在汽车电子领域

的市场地位

矽力杰半导体与苹果公司的合作

• 为苹果的iPhone、iPad、MacBook等产品提供高性能、低功耗的

• 通过品牌建设和市场推广,提高品

才和技术资源

的稳定供应

牌知名度和市场占有率

05

结论与建议

矽力杰半导体在半导体产业中的贡献与地位

矽力杰半导体为全球电子产品提供了创新和可靠的

芯片解决方案

矽力杰半导体在半导体产业中的市场地

位

• 为消费电子、工业、汽车电子等领域

• 矽力杰半导体在全球范围内拥有多个

诺西笔试题目

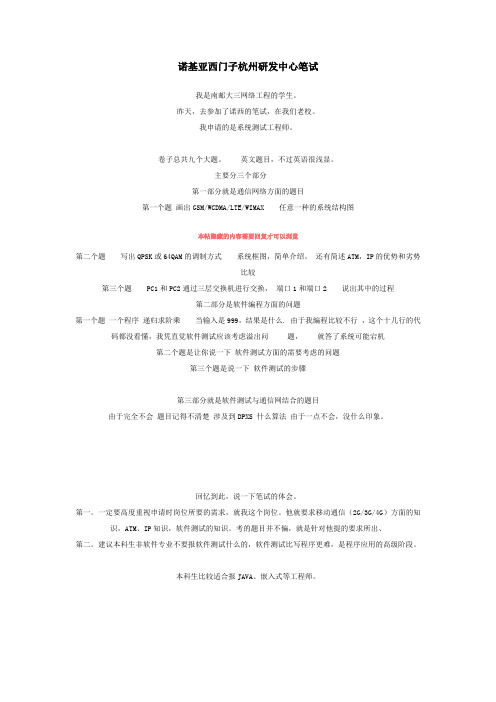

诺基亚西门子杭州研发中心笔试

我是南邮大三网络工程的学生。

昨天,去参加了诺西的笔试,在我们老校。

我申请的是系统测试工程师。

卷子总共九个大题。

英文题目,不过英语很浅显。

主要分三个部分

第一部分就是通信网络方面的题目

第一个题画出GSM/WCDMA/LTE/WIMAX 任意一种的系统结构图

本帖隐藏的内容需要回复才可以浏览

第二个题写出QPSK或64QAM的调制方式系统框图,简单介绍。

还有简述ATM,IP的优势和劣势比较第三个题 PC1和PC2通过三层交换机进行交换,端口1和端口2 说出其中的过程

第二部分是软件编程方面的问题

第一个题一个程序递归求阶乘当输入是999,结果是什么. 由于我编程比较不行,这个十几行的代码都没看懂,我凭直觉软件测试应该考虑溢出问题,就答了系统可能宕机

第二个题是让你说一下软件测试方面的需要考虑的问题

第三个题是说一下软件测试的步骤

第三部分就是软件测试与通信网结合的题目

由于完全不会题目记得不清楚涉及到DPXS 什么算法由于一点不会,没什么印象。

回忆到此,说一下笔试的体会。

第一。

一定要高度重视申请时岗位所要的需求,就我这个岗位。

他就要求移动通信(2G/3G/4G)方面的知识,ATM、IP知识,软件测试的知识。

考的题目并不偏,就是针对他提的要求所出、

第二。

建议本科生非软件专业不要报软件测试什么的,软件测试比写程序更难,是程序应用的高级阶段。

本科生比较适合报JAVA、嵌入式等工程师。

最后,再说一下。

大家一旦报了,就一定要好好准备,至少两个星期。

这样才有更多的机会。

2022年06月西湖大学芯片数字化生产技术研究中心招聘笔试参考题库含答案解析

2022年06月西湖大学芯片数字化生产技术研究中心招聘笔试参考题库含答案解析(图片可自由调整大小)全文为Word可编辑,若为PDF皆为盗版,请谨慎购买!卷I一.高等教育法规(共15题)1.教育行政复议机关应当自收到复议申请()内做出受理、不予受理、限期补正等处理。

A.5日B.7日C.10日D.15日答案:C本题解析:教育行政复议机关应当在收到复议申请十日内做出处理。

2.下列哪个惩罚措施不属于我国对学生进行处分种类()A.警告B.开除学籍C.罚款D.勒令退学答案:C本题解析:暂无解析3.设立独立设置的学院,其全日制在校学生计划规模应为()。

A.2000人以上B.3000人以上C.5000人以上D.7000人以上答案:B本题解析:暂无解析4.普通高校学生贷学金实行()。

A.低息贷款B.贴息贷款C.无息贷款D.都不是答案:C本题解析:暂无解析5.我国现行的学科门类分为()类。

A.10B.11C.12D.13答案:B本题解析:我国学位学科门类分为哲学、经济学、法学、教育学、文学、史学、理学、工学、农学、医学、军事学等11类。

6.某高校一名大学生,大一、大二两年成绩优秀,大学三年级时因病退学。

对于该学生,学校应当()。

A.不发任何学业证书B.颁发肄业证书C.颁发结业证书D.颁发修业证书答案:B本题解析:暂无解析7.所谓受教育权,是指()。

A.在一定的教育机构中,由教育者对受教育者实施的一种有目的、有计划、有组织的影响活动B.公民有从国家接受文化教育的机会,以及获得受教育的物质帮助的权利C.公民有获得知识、技能的权利D.公民均有上学的权利答案:B本题解析:受教育权是中国公民所享有的并由国家保障实现的接受教育的权利,是宪法赋予的一项基本权利,也是公民享受其他文化教育的前提和基础,即公民享有从国家接受文化教育的机会和获得受教育的物质帮助的权利。

8.安徽真题:下列不屈于我国教育行政处罚种类的是()。

A.警告B.罚款C.拘役D.撤销教师资格答案:C本题解析:拘役属于刑事处罚。

杭州笔试分享范文

杭州笔试分享范文您需要登录后才可以回帖登录 | 注册发布昨晚收到今天杭州的BS,要求九点二十到场,自己九点到的,本来还以为可以“早期的虫虫有鸟吃”但到了才发现,原来已经是很晚了,而且确实是海笔啊,浙大紫金港硕大的机房,一楼二楼,众多早起的虫虫已经挤得很满了,于是只好一声长叹,及过去从牌子上看在那个教室考,万科这点做的挺好的,就是把名词按首字母A~Z排列,大家比较容易找的到自己,虽然很简单的一个举措,但以前的众多公司都没这样做,然后翻来覆去一个人得找半天。

进去机房,HR哥哥验过身份安排入座,于是基本上就开始答题。

用的依旧是奕择网络测评,也就是传统的行测,做题的时候必须全屏,但中途可以退出重新登录,这点漏洞是这个测评系统普遍从在的,因为你可以暂停后内事不知问百度,外事不知问google,因此HR(估计是yize的人)反复提醒说不要上其他网络,这样会占用网络资源,导致网络更卡,而且强调他们的题绝对在百度里搜不到。

具体搜不搜的到,我不知道,也没搜过,但有一两道在的模拟题库里是有的,而且这次没考数列题,估计是因为太容易百度了~ 好了,闲话少说,上干货,题目大致构成是这样子滴:第一部分,语文知识,基本上就是选词填空,哪句有病句,哪句不会有歧义等等,这个有点汗,有些题目颇有高考遗风,那是咬文嚼字半天才能看出来的第二部分,逻辑,就是中文GRE,对应关系之类的,还有上面一段话成立还需要什么论据支持等等~看看行测都知道的~ 第三部分,抽象推理,就是一对说话的,那个说的是真话等等之类的题~第四部分,信息阅读,有点类似中文SHL,单比那个简单些,不过不允许用计算器,行测的题库里也有这类型题~第五部分,他叫做什么战略推理,其实就是大杂烩,有推理,有逻辑,等等,稍微难一些,前面四部分每部分10题,最后7题,每部分10分钟,限定时间,分别计时。

几点TIPS:1.不要太早进系统答题,今天一开始浙大网就瘫痪了,以至于开始答题的哥么很紧张,但据说退出后不会计时,但影响心情啊,所以,不是大牛的话还是随大流吧~2.每部分时间没用完可以修改答案,左边有导航条,可以返回当题,所以不用紧张。

微电子专业公司招聘面试笔试题目

(上海华虹)1、国家211工程本科以上,电子类相关专业,外貌具有亲和力2、较强的逻辑思维能力,语言表达能力,善于撰写报告3、勇于承受工作压力和挫折、随机应变4、熟悉mcu软、硬件应用,具备独立开发能力优先5、熟悉模拟电路应用,具备产品开发和应用能力优先(华为)1。

集成电路设计前端流程及工具。

答:前端流程主要是RTL级设计,验证,综合。

后端主要是布图布线综合后的输出文件,可以拿去做layout,将电路fit到可编程的片子里或者布道硅片上,这分单元库和全定制。

单元库下一步就是自动布局布线,auto place & route,简称apr cadence的工具是Silicon Ensembler,Avanti的是Apollo;全定制Cadence的工具是layout editor。

2。

FPGA和ASIC的概念,他们的区别答:FPGA是可编程ASIC;ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。

根据一个用户的特定要求,能以低研制成本,短交货周期供货的全定制,半定制集成电路。

与门阵列等其它ASIC相比,它们又具有设计开发周期短,设计制造成本低,开发工具先进、标准产品无需要测试、质量稳定以及可实时在线检验等优点。

3。

LATCH和DFF的概念和区别答:LATCH和DFF都是时序逻辑,区别为:latch同其所有的输入信号相关,当输入信号变化时latch就变化,没有时钟端;DFF受时钟控制,只有在时钟触发时才采样当前的输入,产生输出。

当然因为二十都是时序逻辑,所以输出不但用当前的输入相关还同上一时间的输出相关。

4。

用DFF实现二分频。

答:module div2(input wire en _ n, input wire out _ clk);Wire D;Wire Q;Assign D=en _n & (~Q);DFF (.clk (clk), .D(D), .Q(Q));Assign out _ clk =Q;endmodule5。

半导体或芯片岗位招聘笔试题与参考答案(某世界500强集团)

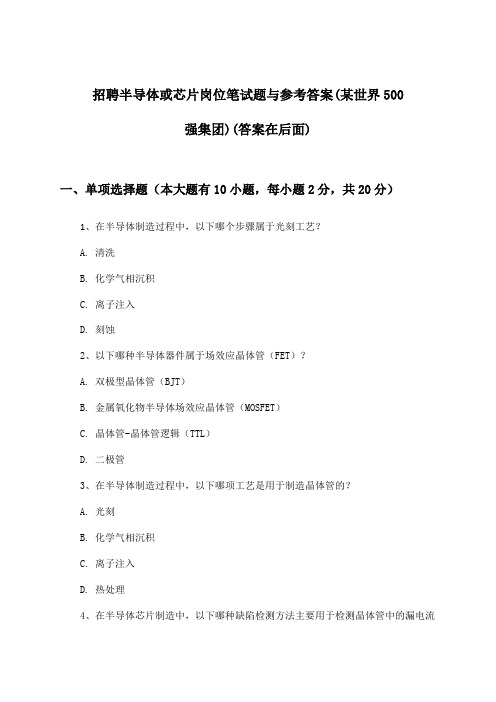

招聘半导体或芯片岗位笔试题与参考答案(某世界500强集团)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、在半导体制造过程中,以下哪个步骤属于光刻工艺?A. 清洗B. 化学气相沉积C. 离子注入D. 刻蚀2、以下哪种半导体器件属于场效应晶体管(FET)?A. 双极型晶体管(BJT)B. 金属氧化物半导体场效应晶体管(MOSFET)C. 晶体管-晶体管逻辑(TTL)D. 二极管3、在半导体制造过程中,以下哪项工艺是用于制造晶体管的?A. 光刻B. 化学气相沉积C. 离子注入D. 热处理4、在半导体芯片制造中,以下哪种缺陷检测方法主要用于检测晶体管中的漏电流问题?A. X射线检测B. 电子显微镜检测C. 荧光检测D. 原子力显微镜检测5、在半导体制造过程中,以下哪种工艺用于去除硅片表面的杂质和缺陷?A. 光刻B. 化学气相沉积(CVD)C. 离子注入D. 化学机械抛光(CMP)6、在芯片设计中,以下哪种设计方法可以提高芯片的集成度和性能?A. 逻辑门级设计B. 结构级设计C. 电路级设计D. 体系级设计7、以下哪项不是半导体制造过程中的关键工艺步骤?A. 光刻B. 化学气相沉积C. 离子注入D. 热压焊接8、以下哪种材料不是常用的半导体绝缘材料?A. 氧化硅B. 氮化硅C. 氮化铝D. 硅9、在半导体制造过程中,以下哪种设备主要用于去除晶圆表面的杂质和缺陷?A. 化学机械抛光机(CMP)B. 刻蚀机C. 离子注入机D. 硅片清洗机 10、以下哪种半导体器件在工作时会产生电流,而电流的大小与输入电压成正比?A. 变容二极管B. 线性稳压器C. 金属氧化物半导体场效应晶体管(MOSFET)D. 二极管二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪些是半导体制造过程中常见的步骤?()A、光刻B、蚀刻C、离子注入D、化学气相沉积E、封装2、以下关于芯片设计的相关术语,正确的是?()A、CPU是中央处理单元的缩写B、GPU是图形处理单元的缩写C、FPGA是现场可编程门阵列的缩写D、ASIC是专用集成电路的缩写E、CPU的主频表示其每秒可以执行的指令数3、以下哪些技术是现代半导体制造中常用的光刻技术?()A. 克雷顿光刻技术B. 紫外光刻技术C. 电子束光刻技术D. 纳米压印光刻技术4、在半导体制造过程中,以下哪些工艺步骤属于化学气相沉积(CVD)技术?()A. 氧化硅的沉积B. 氮化硅的沉积C. 多晶硅的制备D. 氧化物的蚀刻5、以下哪些是半导体制造过程中常用的清洗技术?()A. 水洗B. 氨水清洗C. 酸洗D. 离子液体清洗E. 氩气清洗6、下列哪些因素会影响半导体器件的可靠性?()A. 材料质量B. 制造工艺C. 环境因素D. 使用条件E. 封装设计7、以下哪些是半导体制造过程中常用的光刻技术?()A. 光刻机B. 干法刻蚀C. 湿法刻蚀D. 电子束光刻E. 分子束外延8、以下哪些是影响芯片性能的关键因素?()A. 电路设计B. 材料选择C. 制程工艺D. 温度控制E. 电源电压9、以下哪些是半导体制造过程中常用的光刻技术?()A. 光刻胶B. 光刻机C. 电子束光刻D. 紫外线光刻E. 激光直接成像 10、在芯片设计过程中,以下哪些是常见的电路设计语言?()A. VHDLB. VerilogC. C++D. SystemCE. SPICE三、判断题(本大题有10小题,每小题2分,共20分)1、在半导体制造过程中,光刻是直接在硅片上形成电路图案的关键步骤。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Analog Design

Device Knowledge

1. p+/n- junction and p-/n+ junction, which has a higher breakdown voltage? Why? For

a p+/n- junction having N

A and N

D

, what is the approximate function of junction

capacitance (C

j ) vs. reverse biased voltage (V

R

)?

2. Draw the cross-section of a CMOS inverter. Draw the parasitic structure on the cross-section. Describe ways to prevent “latch-up”?

Circuit Analysis

3. See the figure below.

a. Draw the bode plot for this circuit.

b. Estimate the systematic offset in this amplifier.

c. Which is the positive input?

4. See the figure below.

a. What is this circuit?

b. Which input is the positive input?

c. How much current flows in P

?

2

d. If I=10uA, what is a good selection for the value of R?

e. What is the Common Mode Input Range for this circuit?

f. What is the Common Mode Output Range for this circuit?

g. Assume the only capacitance is from OUT to GND. Draw a Bode Plot.

=C? What is the

h. Assume no load. What is the maximum positive slew rate if C

OUT

maximum negative slew rate?

5. See the figure below.

Assume at time=0 inductor current is 0A. Draw inductor current, V

X and V

OUT

vs. time.

I

6. See the figure below.

a. What is this circuit?

b. What is the desired ratio R

2/R

1

?

c. How many stable points does this circuit have?

d. Assume R

1 and R

2

have no Temperature Coefficient. Draw a graph of I in R

2

vs.

Temperature.

e. What is the minimum supply voltage necessary for this circuit to work properly?

OUT

7. See the figure below.

a. Write the gain equation of each circuit.

b. Assuming V O =0 at time 0. Sketch V O (t) for the given input signal.

A

B

C

8. Draw Buck Converter Circuit and key waveform, explain the basic operations at steady state.

Other

Must Answer (Question 1-3)

Question 1:

Write the V/I relationship equations for resistor (R), capacitor (C), and inductor (L).

Question 2:

Given V

B in Table 1, please calculate V

C

and V

E

. Assumptions: beta of NPN is infinity,

P-N junction forward voltage drop is .

Question 3:

假设图中理想放大器工作在深度负反馈状态,请计算下图输出端电压(V

)。

OUT

For Test Engineer (Question 4-5)

Question 4:

用C语言写一个递归算法求N!

Question 5:

C语言题目

a. 在编译环境下,下列类型变量需要占几个字节内存:

int

float

double

long

char

unsigned char

b. 以下程序的输出结果:

#define ADD(x) (x)+(x)

main()

{

int a=4, b=6, c=7, d=ADD(a+b)*c;

printf(“d=%d\n”,d);

}

c. 设int a=7,b=9,t;执行完表达式t=(a>b)?a:b;后,t的值是?

d. 设计一个排序函数,并同时获得最大值,最小值,均方根。

函数名、排序数列等自行定义。

For AE Engineer (Question 6-8)

Question 6:

a. What is this circuit shown in the Figure?

C1

b. Please draw the waveforms for V

2

for three cases (use the same scale):

C 1=open, R

3

=1k;

R 3=open, C

1

=1uF;

R 3=1k, C

1

=1uF.

0V

0V Question 7:

Draw bode plots of V

O /V

I

(gain and phase) for the circuit shown below. Please label

the proper pole/zero location.

V I

O

Case 1: R3=open

Case 2: R3=1K

Question 8:

Figure below shows a simple buck converter. The switching frequency of the converter is 1MHz.

L 1

I OUT

a. V IN =10V, V OUT =4V, I OUT =5A, what is the ON time of Q 2?

b. Draw waveforms of V SW and I L1 below (under the same time scale of V G -V SW ). Assumption: I OUT =5A.

For Layout Engineer (Question 9-12)

Question 9: 简述CMOS 工艺流程。

Question 10:

Draw the layout of a two-input NAND gate.

Z

A

B

Question 11:

下面电路图中有两个MOSFET(M

A and M

B

)。

假设每个MOSFET有两个gate figure,右下版图应

该如何连接,才能使M

A

和M

B

匹配。

Question 12:

画出不同的电流镜图,并简述各自特点。