RS485高速数据传输协议的设计与实现

RS485总线通信系统的设计及实现毕业论文

RS485总线通信系统的设计及实现毕业论⽂本科学⽣毕业论⽂论⽂题⽬:RS485总线通信系统的设计与实现学院:年级:专业:姓名:学号:指导教师:摘要⽆论是⼯业控制还是信号测试领域,实现不同通讯协议的数据融合都有着迫切需要。

但是⽬前市场中存在的协议转换器只能满⾜两种协议之间的转换,如RS485转RS232,USB转RS485等,但是经常存在着多种数据总线并存的情况,因此研制多种总线协议转换的设备有着⽐较⼤的实际意义。

除此之外,⽬前接⼝标准的RS485总线通信协议不统⼀,需设计⼀个⾼效稳定的通信协议。

基于以上原因,本论⽂提出⼀种基于⾼速RS485的多总线通信系统。

整个系统包含多个RS485节点,各个节点包含的通讯接⼝包括RS232,RS485和USB,从⽽实现这三类总线的通讯协议的转换。

设计并实现了⼀种适⽤于微机和单⽚机之间串⾏通信的通信协议,采⽤RS485简便,通信可靠性⾼总线标准,可⽤于⼯业测控和控制现场。

实验结果表明,该通信协议是切实可⾏的,达到了预期的设计要求。

关键词RS485总线;主从式;多机通信;通信协议AbstractWhether in the field of industrial control or signal test, the achievement of data fusion which is based on different communication protocol is urgent needed. However, in the current market, protocol converter can only achieve conversion between two protocols, such as RS485 to RS232, USB to RS485 and so on. Cases of coexistence data bus, it has great practical significance to develop an equipment for protocol conversion among different buses.Based on the reasons above, a high-speed RS485-based multi-bus communication system is presented in this paper. The entire system which is used to realize the three categories of bus communication protocol conversion consists of someRS485 nodes, each node contains the communication interfaces including RS232, RS485 and USB. In the practical application, the number of nodes can be changed as required to formsystem, for achievement of data fusion between a variety of bus communication protocol.Key wordsRS485 bus; Serial Bus; Protocol Conversion; Communication protocol⽬录摘要............................................................................................................................. I Abstract .....................................................................................................................II 第⼀章绪论 (1)1.1 研究背景及意义 (1)1.2 RS485总线通信系统研究现状 (2)第⼆章RS485介绍 (4)2.1 RS485标准 (4)2.2 MAX485芯⽚介绍 (4)2.3 RS485总线组⽹⽅式 (5)2.4 RS485⽅式构成的多机通信原理 (5)第三章系统协议及硬件设计 (7)3.1 RS485通信协议设计 (7)3.1.1 物理层设计 (7)3.1.2 数据链路层设计 (8)3.1.3 应⽤层设计 (8)3.1.4 通信协议 (8)3.2 系统硬件设计 (10)3.2.1 PC与RS485总线的接⼝ (10)3.2.2 RS485⽅式构成的多机通信 (10)3.2.3 单⽚机与PC机串⾏通信系统构成 (11)第四章系统的软件实现 (12)4.1 上下位机的关系 (13)4.2 下位机通信软件的设计 (14)4.3 上位机通信软件的设计 (16)4.3.1 通信协议设计 (16)4.3.2 多机传输 (17)4.3.3 差错控制 (18)4.4 程序设计 (19)第五章系统问题解决措施 (20)5.1 总线隔离 (20)5.2 失效保护 (20)5.3 电磁⼲扰问题 (20)结论 (22)参考⽂献 (23)致 (24)第⼀章绪论所谓通信,不仅仅要实现数据的传输,更应该体现准确性,也称可靠性传输,最好具有⼀定的纠错和检错能⼒。

RS485通信协议

RS485通信协议协议名称:RS485通信协议一、介绍RS485通信协议是一种用于实现多节点通信的串行通信协议,广泛应用于工业自动化、仪器仪表等领域。

本协议旨在规范RS485通信的物理层和数据链路层,确保数据的可靠传输和通信的稳定性。

二、物理层规范1. 电气特性RS485通信使用差分信号进行数据传输,要求传输线路采用平衡的双绞线,其中A线和B线分别为正负极性信号线。

通信设备的发送端应具备驱动能力,接收端应具备较高的抗干扰能力。

2. 传输速率RS485通信支持多种传输速率,常见的有9600bps、19200bps、38400bps等。

通信双方应事先约定并设置相同的传输速率。

三、数据链路层规范1. 帧格式RS485通信采用固定长度的数据帧进行数据传输。

数据帧包括起始位、数据位、校验位和停止位。

起始位为逻辑低电平,用于表示数据帧的开始;数据位为8位,用于传输数据;校验位为奇偶校验位或循环冗余校验位,用于检测数据传输的错误;停止位为逻辑高电平,用于表示数据帧的结束。

2. 数据传输RS485通信采用半双工通信方式,即通信双方可以交替发送和接收数据。

发送端将数据按照帧格式发送到传输线路上,接收端接收到数据后进行校验,并发送确认信号给发送端。

发送端在接收到确认信号后才能发送下一帧数据。

3. 多节点通信RS485通信支持多节点通信,每个节点都有一个唯一的地址。

通信时,发送端在数据帧中指定接收端的地址,只有地址匹配的节点才会接收到数据。

其他节点应将传输线路上的数据忽略。

四、错误处理1. 帧错误如果接收端在接收数据帧时发现帧格式错误或校验错误,应发送错误信号给发送端,发送端应重新发送数据帧。

2. 超时处理如果发送端在发送数据帧后一定时间内未收到确认信号,应认为数据传输失败,需要重新发送数据帧。

五、应用示例以下是一个简单的RS485通信协议应用示例:1. 确定通信双方的地址和传输速率。

2. 发送端将待发送的数据按照帧格式封装,并指定接收端的地址。

基于RS485的多主机对等通信系统的设计与实现

基于RS485的多主机对等通信系统的设计与实现一、引言现代社会对通信技术的要求越来越高,无线通信技术的应用广泛,然而在某些特定环境下,无线通信可能会受到干扰或信号弱等问题影响。

为了解决这个问题,基于RS485的多主机对等通信系统应运而生。

这种系统可以实现多主机之间的高效、可靠的通信,具有广泛的应用前景。

本文将介绍基于RS485的多主机对等通信系统的设计与实现。

二、RS485通信协议简介RS485是一种串行通信协议,可实现远距离高速数据传输。

它采用差分信号传输,在抗干扰能力和传输距离方面具有优势。

RS485通信协议定义了电气特性、物理层规范、通信帧格式等内容,为多主机对等通信系统的设计与实现提供了基础。

三、多主机对等通信系统的设计1. 系统框架设计多主机对等通信系统由主机、从机和总线组成。

主机之间可以进行双向通信,彼此平等地参与通信过程。

总线通过RS485通信协议连接主机和从机,实现数据的传输和交换。

2. 硬件设计(1)选择合适的RS485通信模块,该模块需要支持多主机对等通信的功能,并提供相应的接口。

(2)确定主机和从机的配置数量和位置,根据实际需求设计电路板布局。

(3)为每个主机和从机分配唯一的地址,以便在通信过程中进行识别和区分。

3. 软件设计(1)主机软件设计:主机负责发起通信请求、接收、解析和处理数据。

软件需要实现主机之间的通信协议,确保数据的正确传输和处理。

(2)从机软件设计:从机负责接收主机发送过来的数据,并做出相应的响应。

软件需要实现从机之间的通信协议,确保数据的正确接收和响应。

四、多主机对等通信系统的实现1. 硬件实现(1)按照设计要求,搭建多主机对等通信系统的硬件电路。

(2)连接RS485通信模块和其他硬件设备,搭建通信网络。

2. 软件实现(1)编写主机软件代码,实现主机之间的通信功能。

(2)编写从机软件代码,实现从机之间的通信功能。

(3)进行系统调试和测试,确保数据的正确传输和处理。

rs485电路原理

rs485电路原理RS485电路原理RS485是一种串行通信协议,它定义了电平、传输速率、传输距离和通信规范等方面的要求,广泛应用于工业自动化、建筑物自动化和数据采集等领域。

RS485电路原理是指通过合理的电路设计实现RS485通信的基本原理和方法。

RS485通信采用差分信号传输,即通过两根线分别传输正负两个信号来表示数据。

这种差分信号传输方式能够有效抵抗噪声干扰,提高通信的可靠性和稳定性。

RS485电路中,通常包含了驱动器和接收器两个部分。

驱动器是RS485电路中的发送端,它负责将逻辑电平的数据转换为差分电平信号,并将信号发送到总线上。

驱动器的输出电路通常采用差分放大器,它能够将输入信号放大并提供足够的驱动能力,以保证信号的传输距离和质量。

驱动器还包含了发送使能控制电路,用于控制数据的发送和停止。

接收器是RS485电路中的接收端,它负责将差分电平信号转换为逻辑电平的数据,并将数据发送到接收器的输出端。

接收器的输入电路通常采用差分放大器和比较器,它能够对输入信号进行放大和判断,以确保正确识别出数据。

接收器还包含了接收使能控制电路,用于控制数据的接收和停止。

在RS485电路中,为了保证通信的可靠性和稳定性,通常会采取一些措施。

首先是对总线进行终端电阻匹配,即在总线两端分别连接一个电阻,以匹配总线的特性阻抗,减少信号的反射和干扰。

其次是进行数据的校验和差错检测,以确保数据的准确传输。

常见的校验方式有奇偶校验、循环冗余校验等。

最后是通过控制线实现通信的控制和同步,常用的控制线有使能线、复位线和时钟线等。

RS485电路的设计需要考虑多个因素,例如通信速率、总线长度、总线拓扑结构和终端设备的数量等。

通信速率越高,对驱动器和接收器的要求就越高;总线长度越长,对终端电阻和信号衰减的要求就越高;总线拓扑结构越复杂,对通信协议的要求就越高;终端设备数量越多,对总线的负载能力就越高。

RS485电路原理是通过合理的电路设计实现RS485通信的基本原理和方法。

rs485通讯协议

rs485通讯协议RS485是一种常用的串行通信协议,广泛应用于工业自动化领域。

它是一种差分信号传输方式,可以实现远距离、高速、抗干扰的通信。

RS485通信协议定义了物理层和数据链路层的规范,确保了设备之间的稳定通信。

首先,RS485定义了通信的物理层,包括电气特性和连接方式。

电气特性规定了通信线路的电压范围和电平差异,通常使用正负两个信号线传输数据。

连接方式有两种,一种是点对点连接,即一个主设备和一个从设备之间的连接;另一种是多点连接,即一个主设备与多个从设备之间的连接。

在RS485通信中,数据链路层是关键。

它定义了帧格式、传输控制和错误检测等内容。

帧格式包括起始位、数据位、停止位和校验位,确保数据的正确传输。

传输控制定义了主设备与从设备之间的通信规则,例如主设备发送请求,从设备回应应答等。

错误检测使用循环冗余校验(CRC)算法,检测并纠正传输过程中产生的误码。

RS485通信具有以下优点。

首先,它可以实现长距离通信,最远可达1200米,适用于分布式控制系统。

其次,RS485可以支持多个设备之间的通信,灵活且方便。

再次,RS485具有高速传输能力,传输速率可达10Mbps,满足实时性要求。

此外,RS485还能够抵抗电磁干扰和噪声干扰,提高通信的可靠性。

在实际应用中,RS485通信广泛应用于各种工控设备之间的通信。

例如,工业自动化领域中的PLC、传感器、伺服驱动器等设备常使用RS485通信协议进行数据交互。

此外,RS485通信协议也被广泛应用于配电系统、楼宇自动化系统、视频监控系统等领域。

总之,RS485通信协议是一种可靠、高效的串行通信协议,适用于工业自动化等领域。

它通过定义物理层和数据链路层规范,实现了长距离、高速、抗干扰的通信。

在实际应用中,RS485通信协议发挥着重要作用,推动着工业自动化技术的发展。

RS485串口通信原理

RS485串口通信原理一、RS485串口通信协议原理与特点1.电平传输特点:RS485通信使用差分信号进行传输,即通过正负两个信号线分别传输高低电平,抵消了电磁干扰对信号的影响,提高了传输的抗干扰性能。

2.单主多从:RS485通信存在一个主机和多个从机,主机负责向从机发送指令,而从机接收指令并返回数据。

3.半双工通信:RS485通信只能在一个方向上进行通信,即由主机发送指令到从机,或者从机发送数据到主机,无法同时进行双向通信。

4.多层级网络:RS485通信可以通过多级网络实现跨越更长的距离和更多设备的通信,每级网络之间通过中继器进行连接。

二、RS485通信方式1.同步方式:同步通信是指主机和从机之间在时钟方面进行同步的通信方式。

主机发送时钟信号给从机,从机根据时钟信号进行数据发送和接收,确保数据的完整性和准确性。

同步通信的优点是数据传输速度快,但对时钟同步要求较高。

2.异步方式:异步通信是指主机和从机之间不需要进行时钟同步的通信方式。

主机和从机之间通过控制字符进行数据传输和接收,可以自由控制数据传输速度和时钟精度。

异步通信的优点是适用性广,不需要严格的时钟同步,但数据传输速度较慢。

三、RS485通信协议1.物理层:RS485通信采用差分传输的物理层信号,正负两个信号线分别传输高低电平数据。

通信时需进行数据电平转换,将逻辑高电平和逻辑低电平转换为物理层的高电平和低电平信号。

2.数据链路层:RS485通信的数据链路层采用帧结构进行数据的传输和接收。

数据帧包括起始位、数据位、校验位和停止位。

起始位用于表示数据帧的开始,数据位用于存储实际传输的数据,校验位用于验证数据的准确性,停止位用于表示数据帧的结束。

四、RS485通信应用场景1.工业自动化控制:RS485通信可用于PLC控制系统、工业仪表传感器等设备之间的通信,可实现工业自动化控制和数据采集。

2.楼宇自控系统:RS485通信可用于楼宇自控系统中的空调、照明、电梯等设备之间的通信,实现楼宇设备的集中控制和管理。

rs485通讯

RS485通讯1. 引言RS485是一种串行通信协议,用于在多个设备之间进行双向数据传输。

它是一种高性能的通讯协议,常用于工业自动化、仪器仪表、门禁系统等领域。

本文将介绍RS485通讯的基本原理、使用方法以及常见的应用场景。

2. 基本原理RS485通讯使用差分信号传输,可以抵抗电磁干扰和噪声。

它采用两条相对独立的传输线(A线和B线),通过不同的电平表示逻辑1或逻辑0。

其中,逻辑1对应线A为高电平,线B为低电平;逻辑0对应线A为低电平,线B为高电平。

通过这种方式,数据可以在多个设备之间进行可靠的传输。

3. 硬件连接在使用RS485通讯时,需要将所有设备连接到一个共享的总线上。

每个设备都需要两条连接线(A线和B线)以及一个共享的地线。

通常,可以使用终端电阻来匹配总线阻抗并提高信号质量。

4. 传输方式RS485通讯可以采用两种传输方式:全双工和半双工。

4.1 全双工通讯在全双工通讯中,设备可以同时发送和接收数据。

发送数据的设备需要将数据发送到总线上,并通过差分信号传输给其他设备。

同时,接收数据的设备可以监听总线上的数据并将其解析。

4.2 半双工通讯在半双工通讯中,设备的发送和接收操作是交替进行的。

设备在发送数据时,需要先将总线设置为发送模式,并将数据发送到总线上。

其他设备在接收数据时,将总线设置为接收模式,并监听数据。

5. 通讯协议RS485通讯可以使用多种协议进行数据交换,常见的有MODBUS、DMX512等。

这些协议定义了数据的传输格式、通讯方式和功能码等。

5.1 MODBUS协议MODBUS是一种常用的通讯协议,适用于工业自动化领域。

它定义了数据的传输格式,并提供了读写寄存器等功能。

MODBUS协议支持点对点和多点通讯。

5.2 DMX512协议DMX512是一种用于舞台灯光控制的通讯协议。

它定义了数据的传输格式和通讯方式。

DMX512通讯一般采用全双工方式进行。

6. 应用场景RS485通讯在许多领域都有广泛的应用。

rs485接口设计要点和调试方法

rs485接口设计要点和调试方法一、RS485接口设计要点:1.基本电气参数:RS485接口是一种基于差分传输的串行通信接口,能够实现远距离和高速传输。

在设计RS485接口时,需要考虑以下基本电气参数:a.差分电平:RS485采用差分信号传输,所以需要在接口电路中设置一个电平变换器,将逻辑电平转换为差分电平。

通常差分电平为正负两个电平,例如:+5V和-5V。

b.带宽:RS485接口的带宽决定了其传输速率和信号质量。

在设计时需要根据实际需求选择合适的带宽。

c.驱动能力:RS485接口通常需要驱动一定数量的设备,因此需要考虑驱动电流和输出功率等参数,以确保信号传输稳定和可靠。

2.线路特性:a.线路长度:RS485接口支持较长的通信距离,但实际可靠距离受到多种因素的影响,如传输速率、电缆类型和环境干扰等。

因此,在设计RS485接口时需要考虑通信距离的限制,并根据需求选择合适的电缆类型和衰减补偿方法。

b.终端电阻:RS485通信线路需要在两端分别加上120欧姆的终端电阻,以确保信号有效的传输和防止信号反射。

c.屏蔽和抗干扰措施:RS485接口在电气环境中可能会受到较强的干扰,如电磁辐射和电磁感应等。

为了提高信号质量和抗干扰能力,可以采用屏蔽电缆、引入滤波电路和设置适当的接地措施。

3.通信协议:a.数据格式:RS485接口支持多种数据格式,包括:ASCII码、二进制码和Modbus等。

在设计接口时需要根据实际应用场景选择合适的数据格式。

b.通信速率:RS485接口支持多种通信速率,通常为几百kbps至几Mbps。

在设计接口时,需要根据实际需求选择合适的通信速率,并确保接口电路的传输带宽足够以支持所选择的速率。

c.错误检测和纠正:RS485接口在数据传输过程中可能会出现错误,例如位错误、校验错误和帧错误等。

为了提高通信的可靠性,可以采用差错检测和纠正机制,如CRC校验等。

二、RS485接口调试方法:1.硬件调试:a.接线检查:首先需要检查接线是否正确连接,包括数据传输线、终端电阻和供电电路等。

rs485内部电路工作原理

RS485是一种常用的串行通信协议,广泛应用于工业自动化、安防监控和数据采集等领域。

其内部电路设计精妙,能够实现远距离高速数据传输,并具备抗干扰能力强的特点。

RS485采用差分信号传输方式,通过发送方将逻辑高电平与逻辑低电平分别映射为正负电平,接收方则通过检测电平差值来恢复数据。

这种差分信号传输方式使得RS485在长距离传输时能够有效抵抗电磁干扰和传输线路上的噪声干扰,提高了通信可靠性。

RS485的内部电路主要包括发送器和接收器。

发送器通过一个驱动电路将逻辑电平转换为差分电平输出,驱动能力强,能够推动较长的传输线路。

而接收器则通过一个差分输入电路来检测接收到的差分电平,并将其恢复为逻辑电平。

在RS485的发送器中,常用的电路结构是差分驱动电路。

这种电路采用了双晶体管结构,通过控制两个晶体管的导通与截止状态,实现了逻辑电平到差分电平的转换。

同时,发送器还包括了一个电流限制电路,用于控制发送电流的大小,保护线路不受损坏。

接收器部分,一般采用差分比较器电路和电平转换电路。

差分比较器用于检测接收到的差分信号,并输出对应的逻辑电平。

电平转换电路则负责将差分信号转换为标准的逻辑电平,以供后续处理。

除了发送器和接收器,RS485的内部电路还包括了电源电路、时钟电路和控制电路等。

电源电路提供工作电压给发送器和接收器,时钟电路提供时序控制信号,控制电路用于控制发送器和接收器的工作状态,以保证数据传输的正常进行。

总之,RS485的内部电路设计精妙,通过差分信号传输方式实现了远距离高速数据传输,并具备抗干扰能力强的特点。

发送器和接收器的设计使得RS485能够在工业自动化等领域中稳定可靠地工作。

了解其内部电路工作原理,有助于我们更好地理解和应用RS485通信技术。

无极性rs485接口芯片的研究与实现

第1章绪论1.1 RS485简介及应用RS485是一种对于数据传输制定的标准,主要针对接口制定了一些电气规定,数据的主要传输方式是差分形式。

RS485接口标准的英文全称为“Electrical Characteristics of Generators and Receivers for Use in Balanced Digital Multipoint Systerms”,为方便起见,人们将全称简化为了RS485。

由于RS485是在RS422和RS232上面演变出来的,所以相对它们有较多优点。

例如以前RS232的总线节点数为1发1收,RS422的总线节点数为1发10收,而目前RS485的总线节点数为1发至少32收[2];带负载能力变强,RS232可以驱动3KΩ~7KΩ的负载,RS422可以驱动100Ω的负载,而RS485可以驱动54Ω的负载。

除举例的几点外RS485还有其他相对的优点,像驱动器的共模电压范围等等。

RS485总线对于数据通信存在一些不能兼容的问题,其传输的最大速率和最大距离不能同时达到最大,也就是说当RS485总线的数据传输速率最大时其传输距离为最小,这时如果想要达到远距离传输[3],应在传输总线上增加RS485中继器来达到[4]。

同样,当数据通信为最远时,这时数据传输速率又处于最小。

所以对于不一样的使用领域需要设计相应的RS485接口芯片[5]。

本文设计的无极性RS485接口芯片适用于中等通信速率及中等通信距离场所。

目前已有的RS485接口芯片上限可以达到10Mbps的数据率,传输距离超过1200米[6]。

RS485接口标准得到广大用户青睐的一个主要原因是RS485使用起来方便,而且如果用户有其他特别需求可以在RS485标准的基础上设立自己额外的标准。

比如PROFIBUS-DP、CAN、FF、Modbus及INTERBUS-S的物理层协议都是构建在RS485标准协议的基础上,或是与RS485标准协议保持兼容[7]。

RS-485和Modbus通信协议及工作原理

RS-485和Modbus通信协议及工作原理在(工业控制)、电力通讯、(智能)仪表等领域,通常情况下是采用串口(通信)的方式进行数据交换。

最初采用的方式是(RS)232接口,由于(工业)现场比较复杂,各种(电气)设备会在环境中产生比较多的电磁千扰,会导致(信号)传输错误。

1979年施耐德电气制定了一个用于工业现场的总线协议Modbus协议,现在工业中使用RS485通信场合很多都采用Modbus 协议,所以今天我们来了解下RS485通信和Modbus通信协议。

什么是串口通信串口通信(Serial Communication),是指外设和计算机间,通过数据信号线、地线、控制线等,按位进行传输数据的一种通讯方式。

这种通信方式使用的数据线少,在远距离通信中可以节约通信成本,但其传输速度比并行传输低。

由于串行通信是在一根传输线上一位一位的传送信息,所用的传输线少,并目可以借助现成的电话网进行信息传送,因此,特别适合于远距离传输。

(RS-485)协议概述RS-485和RS-232一样,都是审行通信标准,现在的标准名称是(TI)A485/EIA-485-A,但是人们会习惯称为RS485标准,RS-485常用在工业、自动化、汽车和建筑物管理等领域。

RS-485总线弥补了RS-232通信距离短,速率低的缺点,RS-485的速率可高达10Mbit/s,理论通讯距离可达1200米;RS-485和RS-232的单端传输不一样是差分传输,使用一对双绞线,其中一根线定义为A,另一个定义为B。

通常情况下,RS485的信号在传送出去之前会先分解成正负对称的两条线路(即我们常说的A、B信号线),当到达接收端后,再将信号相减还原成原来的信号。

拓扑结构RS485有两线制和四线制两种接线,四线制只能实现点对点的通信方式,现很少采用,多采用的是两线制接线方式,这种接线方式为总线拓扑结构,在同一总线上最多可以挂接32个节点RS-485总线同12C总线一样支持主从模式,支持点对点单从机模式,也支持多从机模式,不支持多主机模式。

rs485设计标准 -回复

rs485设计标准-回复什么是RS-485设计标准?RS-485是一种串行通信标准,广泛应用于工业自动化、建筑控制、智能仪表等领域。

它定义了电气和功能方面的规范,以确保可靠的数据传输和高速通信。

1. RS-485的电气特性:RS-485采用差分传输方式,即同时传输正负两个信号。

这样做的好处是可以抵消传输线路中的电磁干扰,提高信号的抗干扰能力。

RS-485的电平范围为-7V至+7V,适用于传输较长距离的信号。

2. RS-485的信号传输方式:RS-485支持全双工和半双工传输方式。

全双工传输允许同时发送和接收数据,而半双工传输则只能在某一时刻发送或接收数据。

这种灵活性使RS-485适用于多种应用场景。

3. RS-485的通信协议:RS-485没有明确规定通信协议,因此可以根据应用需求选择不同的协议,如Modbus、Profibus等。

这些协议定义了数据的格式、传输速率、错误检测等,以保证数据的可靠传输和正确解析。

4. RS-485的网络拓扑结构:RS-485支持多节点连接,可以形成多主多从的网络拓扑结构。

在这种结构中,每个节点都可以发送和接收数据,节点之间通过电缆连接。

这种结构灵活,可以满足不同应用场景的需求。

5. RS-485的硬件要求:RS-485通信线路需要特定的硬件支持,包括驱动芯片、接收器、电缆等。

驱动芯片负责将逻辑信号转换为电气信号,接收器负责将电气信号转换为逻辑信号。

同时,电缆的选择和布线也对RS-485通信的可靠性影响很大。

6. RS-485设计的考虑因素:在RS-485的设计中,需要考虑多个因素来确保稳定的通信。

首先是通信距离,通常RS-485的传输距离可以达到1200米,但距离越长,电缆和驱动芯片的要求就越高。

其次是传输速率,根据应用的需求选择合适的传输速率,通常可以支持最高10Mbps的速率。

最后是抗干扰能力,RS-485需要具备一定的抗干扰能力,以保证数据的可靠性。

总结起来,RS-485是一种广泛应用于工业自动化领域的串行通信标准,它具有较高的抗干扰能力和较长的传输距离,适用于多节点、全双工或半双工的通信需求。

基于RS485的数据通信协议的设计与实现

( 1 . 模 式 识 别 与 智 能信 息 处 理 四 川 省 高 校 重 点 实验 室 四 川 成 都 6 1 0 1 0 6 ; 2 . 成 都 大 学 信 息 科 学 与技 术 学 院 ,四 J I 1成 都 6 1 0 1 0 6 ; 3 . 成 都 大 学 电子 信 息 工 程 学 院 ,四 川 成 都 6 1 0 1 0 6 ) 摘要: 基 于现 场 可 编程 门 阵 列 ( F P G A) , 设 计 了采 用 R S 4 8 5标 准 的数 据 通 信 协 议 。 其 中 , 高速 信 号接 收 , 采 用同步 4 8 5 通信协议 , 高速 接 口 包括 时 钟 和 数 据 两个 信 号 , 时钟速率 3 . 6 8 6 4 MHz , 利 用 同步 时钟 上 升 沿检 测数 据 。低 速 信 号 接 收 采用异步 4 8 5通 信 协 议 , 波特率 l l 5 . 2 k b p s , 每 字 节 1个起 始 位 , 8个数 据 位 , 1 个 截 止 位 。针 对 高速 数 据 接 收 时 的 情 况. 加入 1 M B 容 量 的静 态存 储 器 S R A M 作为缓存 。 保 证 接 收数 据 的 可 靠 性 。 关键词 : R S 4 8 5 ;现 场 可 编 程 门阵 列 ( F P G A) ;同步 通 信 ; 异步通信 ; S R A M 中 图分 类 号 : T N 9 1 文献标识码 : A 文 章 编 号 :1 6 7 4 — 6 2 3 6 ( 2 0 1 3 ) 1 7 — 0 0 l 9 — 0 4

De s i g n a n d i mp l e me n t o f RS 4 8 5 d a t a c o mmu n i c a t i o n p r o t o c o l

基于RS485的多主机对等通信系统的设计与实现

软件优化:提高 通信效率,降低 资源消耗

主从机连接与通信流程实现

硬件连接:RS485 总线连接多个主机, 实现数据传输

通信协议:制定并 实现通信协议,保 证数据传输的准确 性和可靠性

数据传输:实现数 据的发送和接收, 保证数据的完整性 和实时性

错误处理:实现错 误检测和恢复机制 ,保证通信的可靠 性和稳定性

A

B

C、以太网等

降低功耗:优化硬件设 计,降低系统功耗,提

高能源利用率

增强安全性:采用加密 技术,提高通信数据的

安全性

提高兼容性:支持多种 硬件平台和操作系统,

提高系统的通用性

总结与展望

系统特点与优势总结

基于RS485的多主机对等通信系统,实 现了多主机之间的实时通信和数据共享。

03

测试方案:功能测试、性能测试、兼容性 测试等

02

软件环境:操作系统、测试软件、驱动程 序等

04

测试结果分析:测试数据、测试报告、问 题定位等

测试过程及结果分析

测试环境搭建:搭建 测试环境,包括硬件

和软件

测试方法:选择合适 的测试方法,如黑盒 测试、白盒测试等

测试数据准备:准备 测试数据,包括正常

度

增强系统稳定 性:优化系统 设计,提高系 统抗干扰能力

降低功耗:采 用低功耗器件, 降低系统能耗

扩展应用领域: 将RS485技术 应用于更多领 域,如工业自 动化、智能家

居等

THANK YOU

0 终端电阻:在总线两端添加终端 4 电阻,防止信号反射和干扰

0 硬件测试:通过测试验证硬件设 6 计的正确性和可靠性

通信软件设计

01

02

03

04

RS485通讯协议

RS485通讯协议RS485是一种常用的串行通信协议,它能够实现多个设备之间的高速数据传输和远距离通信。

RS485通信协议主要用于工业自动化领域,例如工厂自动化、楼宇自动化、安防系统等。

RS485通信协议具有可靠性高、传输速率快、抗干扰能力强等优点,下面将详细介绍RS485通信协议的原理和应用。

RS485通信协议是一种差分信号通信方式,它使用两根信号线进行数据传输,分别为A线和B线。

传输数据时,A线的电平和B线的电平总是相互互补,即一个为高电平时另一个为低电平,这样可以减小干扰对数据传输的影响。

RS485通信协议还增加了一个控制线,即控制线用于进行数据传输的控制,例如数据发送和结束等。

RS485通信协议支持半双工通信方式,即同一时刻只能有一个设备进行数据的发送,但任何一个节点都可以作为发送器和接收器。

它采用了“主从”模式,一个主节点可以连接多个从节点,主节点负责控制通信的开始和结束,从节点负责接收和发送数据。

这种通信方式可以很好地实现多个设备之间的数据交换和共享。

RS485通信协议的传输速率可以达到几百kbps甚至Mbps级别,这使得它在工业自动化领域具有广泛的应用前景。

同时,RS485通信协议的抗干扰能力很强,可以有效地抑制来自外部环境的干扰信号,保证数据传输的可靠性。

这使得RS485通信协议可以在电磁干扰较大的工业环境中稳定地工作。

RS485通信协议的应用范围很广,例如在工厂自动化领域,可以用于控制和监控各个设备的状态和参数。

在楼宇自动化领域,可以用于集中管理各个楼层的空调、照明、安防等设备。

在安防系统中,可以用于实现多个监控摄像头之间的视频传输和控制。

此外,RS485通信协议还可以应用于电力系统、交通系统、能源管理系统等领域。

综上所述,RS485通信协议是一种可靠性高、传输速率快、抗干扰能力强的串行通信协议。

它的原理是使用差分信号进行数据传输,支持半双工通信方式并采用“主从”模式。

RS485通信协议在工业自动化、楼宇自动化、安防系统等领域的应用广泛,并且具有较高的稳定性和可靠性。

RS485通信协议

RS485通信协议协议名称:RS485通信协议一、引言RS485通信协议是一种用于串行通信的标准协议,广泛应用于工业自动化、数据采集和仪器仪表等领域。

本协议旨在规范RS485通信的数据传输格式、物理层特性以及通信协议的实现方式,以确保通信的稳定性和可靠性。

二、协议版本本协议的当前版本为1.0,后续版本的更新将根据实际需求进行修订和发布。

三、通信物理层1. 电气特性RS485通信采用差分信号传输方式,具有较强的抗干扰能力和较长的传输距离。

通信线路应符合以下要求:- 信号线采用双绞线或屏蔽线,保证信号的稳定传输;- 通信线路长度应根据具体情况确定,一般不超过1200米;- 通信线路两端应加入终端电阻,阻值为120欧姆。

2. 通信速率RS485通信支持多种通信速率,常用的速率有9600bps、19200bps、38400bps、57600bps和115200bps等。

通信双方应事先约定并设置相同的通信速率。

四、数据传输格式1. 帧结构RS485通信采用帧结构进行数据传输,每一帧包含以下几个部分:- 起始位(1位):逻辑低电平表示帧的开始;- 数据位(8位):用于传输数据,可表示0-255的整数;- 校验位(1位):用于检验数据的正确性,常用的校验方式有奇校验和偶校验;- 停止位(1-2位):逻辑高电平表示帧的结束。

2. 数据格式RS485通信支持多种数据格式,常用的格式有ASCII码、十六进制和BCD码等。

通信双方应事先约定并设置相同的数据格式。

五、通信协议实现1. 数据传输方式RS485通信可以采用点对点方式或多点方式进行数据传输。

在点对点方式下,一对通信设备之间建立一条专用的通信线路;在多点方式下,多个通信设备共享同一条通信线路。

2. 通信协议协商在通信开始之前,通信双方应进行通信协议的协商,包括通信速率、数据格式、地址分配等。

通信协议的协商可以通过人工设置、自动协商或者主从模式进行。

3. 数据传输流程RS485通信的数据传输流程如下:- 发送方发送起始位;- 发送方发送数据位;- 发送方发送校验位;- 发送方发送停止位;- 接收方接收起始位;- 接收方接收数据位;- 接收方接收校验位;- 接收方接收停止位。

rs485协议的编程方法

rs485协议的编程方法1.什么是r s485协议?r s485协议是一种常用的串行通信协议,用于在多个设备之间进行数据传输。

它具有高速传输、长距离通信和多节点连接的特点,广泛应用于工业自动化领域。

本文将介绍如何使用rs485协议进行编程。

2.硬件准备在使用r s485协议进行编程之前,需要进行一些硬件准备工作。

主要包括:R S485转U A R T模块-:用于将r s485信号转换为与M CU或计算机通信的UA RT信号。

M C U或计算机-:用于与rs485转UA R T模块进行数据交互。

外设设备-:如传感器、执行器等,通过r s485协议与M CU或计算机进行通信。

3.软件编程3.1选择编程语言在进行r s485协议的编程时,可以选择多种编程语言,如C语言、P y th on等。

根据实际需求和项目环境选择合适的编程语言。

3.2使用串口库使用rs485协议进行通信时,需要通过串口与外设设备进行数据交互。

因此,需要在编程中使用相应的串口库来实现串口的打开、配置和读写操作。

3.3配置串口参数在使用r s485协议进行通信之前,需要对串口进行正确的配置。

主要包括波特率、数据位、停止位和校验位等参数的设置。

这些参数应与外设设备的参数相匹配,否则通信将无法正常进行。

3.4发送和接收数据使用rs485协议进行通信时,需要明确发送和接收数据的格式。

根据外设设备的通信协议,编写相应的数据发送和接收函数。

在发送数据时,需要将数据按照协议格式进行打包;在接收数据时,需要根据协议格式解析接收到的数据。

3.5错误处理在r s485通信中,可能会出现各种错误情况,如传输错误、超时等。

在编程过程中,需要预先考虑这些错误情况,并编写相应的错误处理代码,保证程序的稳定性和可靠性。

4.实例演示以下是一个使用C语言编写的简单示例,演示了如何使用r s485协议进行通信:#i nc lu de<s td io.h>#i nc lu de<s td in t.h>#i nc lu de<s td li b.h>#i nc lu de<u ni st d.h>#i nc lu de<f cn tl.h>#i nc lu de<t er mi os.h>#d ef in eR S485_D EVI C E"/d ev/t ty US B0"v o id in it_r s485(in t fd){s t ru ct te rm io st io;t c ge ta tt r(fd,&tio);t i o.c_cf la g|=C REA D|C LO CA L;t i o.c_cf la g&=~CSI Z E;t i o.c_cf la g|=C S8;t i o.c_cf la g&=~PAR E NB;t i o.c_cf la g&=~CST O PB;t i o.c_cc[V MI N]=0;t i o.c_cc[V TI ME]=10;t c se ta tt r(fd,T CSA N OW,&ti o);}i n tm ai n(){i n tf d=op en(R S485_D EV IC E,O_RD WR|O_N OC TT Y);i f(f d==-1){p e rr or("op en");e x it(1);}i n it_r s485(f d);u n si gn ed ch ar da ta[]={0x01,0x02,0x03};w r it e(fd,d at a,siz e of(d at a));u n si gn ed ch ar bu f[10];s s iz e_tn=r ea d(fd,b uf,s iz eo f(bu f));i f(n>0){//解析接收到的数据f o r(in ti=0;i<n;i++){p r in tf("%02x",buf[i]);}p r in tf("\n");}c l os e(fd);r e tu rn0;}5.总结本文介绍了使用r s485协议进行编程的方法。

rs485总线工作原理

rs485总线工作原理RS485总线是一种串行通信协议,用于在远距离、高干扰环境下传输数据。

在很多工业自动化系统中,RS485总线应用十分广泛,尤其是在工控领域。

RS485总线的工作原理如下:1. RS485总线结构RS485总线结构一般包括主控制器和从节点。

主控制器负责控制和管理整个系统的通信,而从节点则用于接收和发送数据。

在RS485总线中,主从节点之间通过一个双绞线传输信号,该信号以平衡回路方式传输。

2. 差分信号在RS485总线中,传送的是差分信号。

差分信号是由两个相邻的信号线构成的一对线路,当信号传输时,其中一个线路发射正向信号,而另一个线路发射反向信号。

接收端采用差分方式对信号进行解码,可以有效减小外界干扰的影响,提高信号的可靠性和稳定性。

3. 线路长度和传输速率的选择RS485总线的线路长度和传输速率的选择关系十分密切。

一般来说,线路长度越短,传输速率可以越高;而线路长度越长,则传输速率要相应降低。

这是由信号传输的特性决定的,RS485总线最长的传输距离可以达到1200米,但在实际应用中,建议不超过1000米,具体应由具体情况而定。

4. 总线终端控制在RS485总线中,总线终端控制十分重要。

总线终端控制以线缆两端为界,由主控制器和从节点分别接入总线,并通过终端电阻进行控制。

总线中最多只能存在两个终端电阻。

当主控制器发送一个命令时,从节点接收到该命令并做出响应后,主控制器会在一定时间内关闭命令信号,此时从节点必须确保命令信号已被完全接收并撤销响应。

如果从节点没有完全接收信号或没有及时撤销响应,总线的状态可能会出现错误。

5. 总结RS485总线是一种高可靠性、高抗干扰能力的串行通信协议,适用于在远距离和高干扰环境下进行数据通信。

要在实际应用中充分利用RS485总线的优势,需要掌握RS485总线的工作原理,了解线路长度和传输速率的选择关系,掌握总线终端控制等重要知识点。

6. 电气特性RS485总线的电气特性也是其能够实现高可靠性和高性能的重要原因。

rs485通讯协议

rs485通讯协议RS485通信协议简介RS485(Recommended Standard 485)是一种串行通信协议,可以实现多点通信和远距离传输数据。

它的特点是可靠性高、抗干扰能力强,适用于在工业自动化、建筑控制、电力监控等领域中进行可靠通信的应用。

RS485通信协议基于电气特性差分信号传输,采用两条线进行双向通信。

其中一条线为传输线(A线),另一条线为接收线(B线)。

这样的架构使得减少了串信的问题,提高了传输稳定性。

RS485通信协议支持多点通信,可以连接多个设备,使其能够同时接收和发送数据。

在RS485总线上,设备可以处于主设备模式或从设备模式。

主设备可主动向从设备发送数据请求,而从设备只能在主设备请求时才能发送数据。

在RS485通信协议中,数据通信是通过波特率来确定的,常用的波特率有9600、19200、38400等。

数据的传输格式通常以字节为单位,每个字节包含起始位、数据位、校验位和停止位。

除了具备可靠性和高抗干扰特点,RS485通信协议还具备灵活性。

一方面,它可以灵活选择485传输模式,可采用全双工或者半双工模式,根据实际需要选择;另一方面,可以根据通信需求,自定义通信协议,实现更加高效的数据传输。

RS485通信协议的应用十分广泛。

在工业自动化领域,RS485常用于控制设备之间的通信,如PLC和HMI之间的通信。

在建筑控制中,RS485通信协议可用于智能楼宇系统的各种设备之间的通信,如照明控制、温度控制等。

在电力监控领域,RS485通信协议可以实现电能表和监控系统之间的通信,实现用电信息的采集和管理。

总之,RS485通信协议作为一种可靠性高且抗干扰能力强的串行通信协议,在各个领域都有着广泛的应用。

它的多点通信特性、可靠性和灵活性使其成为众多设备之间进行可靠通信的理想选择。

随着科技的不断进步和应用领域的不断拓展,相信RS485通信协议的应用将会更加广泛和深入。

rs485 协议原理

rs485 协议原理

RS-485协议是一种串行通信协议,用于在多个设备之间实现数据传输。

它采用差分信号传输方式,能够在长距离通信中提供较高的抗干扰能力。

RS-485协议的原理如下:

1. 物理层:RS-485协议使用差分传输方式,即发送和接收使用两条线,分别为A和B线。

通过在两条传输线上分别发送正转和反转的电压信号,可以有效抵消噪声干扰,提高信号质量。

同时,RS-485支持多个设备使用同一组通信线,通过配置不同的地址,可以实现设备之间的互相通信。

2. 信号编码:RS-485协议使用NRZ(非归零)编码方式,即将0表示为低电平,将1表示为高电平。

这种编码方式简单且易于实现,可以保证数据的正确传输。

3. 数据帧格式:RS-485协议将数据划分为多个数据帧进行传输。

每个数据帧包括起始位、数据位、校验位和停止位。

起始位用于标志一个数据帧的开始,数据位用于传输实际的数据,校验位用于检测数据的错误,停止位用于标志一个数据帧的结束。

通过这些位的组合,可以确保数据能够正确地被接收方解析。

4. 数据传输方式:RS-485协议支持全双工和半双工两种传输方式。

全双工方式可以同时进行发送和接收,通信速率较高;半双工方式同一时刻只能进行发送或接收,通信速率较低。

总的来说,RS-485协议通过差分传输、NRZ编码和数据帧格式等技术手段,实现了多个设备之间的可靠数据传输。

它广泛应用于工业自动化、仪器仪表等领域,具有抗干扰能力强、传输距离远等优点。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

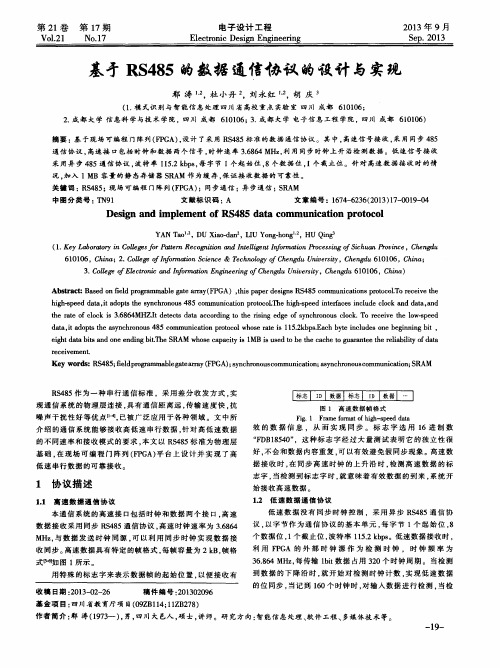

ISSN 1000-0054CN 11-2223/N 清华大学学报(自然科学版)J T singh ua Un iv (Sci &Tech ),2008年第48卷第8期2008,V o l.48,N o.8w 22http://qhx bw.chinajo RS 485高速数据传输协议的设计与实现耿立中, 王 鹏, 马 骋, 贾惠波(清华大学精密仪器与机械学系,精密测试技术及仪器国家重点实验室,北京100084)收稿日期:2008-01-03作者简介:耿立中(1985—),男(汉),山东,博士研究生。

通讯联系人:贾惠波,教授,E-mail:jiah b@tsingh 摘 要:为实现远距离的高速基带信号传输,该文设计了一种以RS 485标准为物理层基础,在现场可编程门阵列(F PG A )平台上实现的数据传输协议。

该协议利用串行信号的跳变沿作为高速时钟检测的起点实现位同步,可以有效地解决信号码间干扰问题;利用8B /10B 编码实现帧同步,可以保证位同步的准确性和帧同步控制字符的可靠性。

该文利用F PG A 平台对协议进行了实验测试,测试结果表明该协议可以实现220m 距离上的14.5M b /s 的有效数据传输,为长距离的高速数据传输提供了可靠的实现方法。

关键词:传输协议;R S485总线;现场可编程门阵列(FP GA )中图分类号:T N 913.8文献标识码:A文章编号:1000-0054(2008)08-1311-04Design and implement of RS485high speed data communications protocolG ENG Lizhong ,WANG Peng ,MA Cheng ,JIA Hu ibo (S tate K ey Laboratory of Precision Measurement Technology &Instruments ,Department of Precision Instruments and Mechanology ,Tsinghua Univers ity ,Beijing 100084,China )Abstract :Th is paper des crib es a RS485commun ication s protocol for high -speed baseb and commu nications.T he inter symb ol inter feren ce (ISI)is reduced by an efficient bit s ynch ronization signal detection schem e.Samplin g begins at th e begin ning of the inpu t signals to get ex act digital r esu lts.T he frame synchronization us es 8B/10B coding an d guaran tees bit syn chroniz ation.T he protocol w as implemented on a field programmable gate array (FPGA)w ith test res ults indicating that th e protocol achieves 14.5M b /s along a 220meters line.Key words :com munication protocol;RS485bus ;fieldprogrammable gate array (FPGA)RS485作为一种串行通信的接口,具有传输距离长、速度较高、电平兼容性好、使用灵活方便、成本低廉和可靠度高等优点,在智能管理[1]、在线控制[2]、地质勘探[3-4]等许多领域都有着广泛的应用[5]。

目前Pro fibus -DP 、Arcnet 和CAN 等总线标准的物理层均是RS 485规范,这些总线标准不能同时保证长距离(200m 以上)和高的传输速度,其中性能较好的Profibus 只能在100m 距离上实现12M b /s 的数据传输[6-7]。

由于RS485传输为基带信号传输,没有单独的时钟线,所以时钟提取成为整个高速数据传输协议的关键。

现有的串行数据时钟提取技术中,同步方式复杂度较高[8],异步方式中通用异步收发器(U ART )[9]以字为传输协议的基本单元,一般不适应太高的速率,传输效率也较低。

本文以RS 485标准为物理层基础,在现场可编程门阵列(FPGA)平台上设计并实现了一种基于特殊的时钟提取方法的传输协议,可以用于串行数据的高速远距离传输。

该协议利用串行信号的跳变沿作为高速时钟检测的起点实现位同步,有效地解决信号码间干扰问题;采用8B/10B 编码实现帧同步,保证位同步的准确性和帧同步控制字符的可靠性。

1 协议描述1.1 位同步设计本设计的位同步方法是以波特率的10倍频时钟作为检测时钟,信号的上升沿和下降沿作为位同步采样的起点。

建立2个采样寄存器R H 、R L ,当高频时钟检测到输入信号为高电平时,开始对检测时钟计数,并存入寄存器R H ,同时将R L 置零,当R H 为5时产生第一个采样点,而后每隔10个时钟周期产生采样点,采得的数字信号为“1”;相应的当高频时钟检测到输入信号为低电平的时候,开始对时钟计数,并存入寄存器R L ,同时将R H 置零,当R L 为5时产生第一个采样点,而后每隔10个时钟周期产生采样点,采得的数字信号为“0”。

图1 信号跳变沿作为检测起点的位同步示意图 由于检测时钟和数据信号的发送时钟并不同源,必然会有误差,假设认为判断信号的第1个下降沿没有误差,第1个采样点相对起始位中间位置有t 的偏差;由于积累,第2个采样点相对H2中间位置则会有3t的偏差;同理第3个采样点会有5t的误差。

当误差积累到超过5个检测时钟的宽度时,误码就产生了。

为了避免误码的产生,计算产生误码的临界条件。

假定检测时钟和数据信号发送时钟的精度均为1×10-4,由于发送时钟频率为检测时钟的10倍,那么检测时钟相对于数据信号(假定传输中未失真)的误差在1.1×10-3之内,则出现误码的高电平或低电平的最小长度为l s=5t d1.1×10-3.(1)其中t d为检测时钟的时钟周期。

也就是说传输基带信号含有450个以上连续的“0”或者“1”时会出现误码,采用此协议的传输必须游程受限在(0,450)之间。

RS485传输是基带信号通过双绞线传输的,占空比容易发生变化,产生码间干扰,尤其是在传输距离比较长的时候。

这种基于信号跳变进行检测起始的位同步设计方法对这种问题有一定的解决能力。

信号在连续长“1”之间的短“0”很容易受到码间干扰影响变短,但本文的位同步设计只需要5个高频时钟的有效检测就可以读到该数据位,也就是短“0”的长度在原始信号长度的一半以上就可以保证得到正确数据。

1.2 帧同步的设计帧同步是在位同步的基础上识别出包含有效数字信息帧的起止时刻,从而得到有效的数据信息[10]。

本设计采用了插入式帧同步的方法,利用特定的帧头和帧尾表示数据帧的起始位置。

由于位同步中对信号是游程受限的,所以采用了8B/10B编码为基础对数据帧进行设计。

帧结构如图2所示。

图2 数据传输链路帧结构帧头采用8B/10B编码中的K28.5字符“010*******”,帧尾采用K28.1字符“1001111100”,这两组控制字在8B/10B编码中是独一无二的,任何数据位的组合都不可能产生这两组字符,可以有效地避免帧同步的假同步现象。

控制位1个字节也属于8B/10B编码的控制字符,当数据帧被读入主控FPGA时帧尾是被抛掉的,可以利用该控制位来表示有效数据的结束。

FCS为CRC-32校验,用来校验数据帧的正确与否。

如图3所示,串行数据经过移位寄存器变为并行信号后进入帧头帧尾判决器进行判决,判决的阈值可以进行调控以避免漏同步的现象出现。

由于错误数据帧对上位用户机是无意义的,必须出错重传,而在同一传输信道中,帧头出错的概率和数据位出错的概率是大体相同的,所以本协议将阈值置为0,即数据与帧头或帧尾数据完全一致时方认定检测到帧头或帧尾,并发送控制信号到数据解码模块。

并行信号经过数据解码后得到原始用户数据,并对其进行CRC校验,如果数据验证正确,则可将用户数据输出给上位用户机。

基于8B/10B码的帧同步设计,在实现帧同步的同时,保证了位同步的准确性,使得通信链路中不会随着时间推移而出现DC偏移。

8B/10B码冗余的编码方式提供了特殊字符作为帧控制字符。

CRC校验用以检测传输过程中的错误。

图3 帧同步检测结构示意图2 基于FPGA系统的协议实现传输协议是基于Altera公司的Quar tus7.2开发环境利用超高速集成电路硬件描述语言(VHDL)1312清华大学学报(自然科学版)2008,48(8)设计。

如图4所示,data -code -send 模块为数据的编码和发送模块,利用2M Hz 和20MHz 的时钟驱动,产生19.07M b/s 左右的码流,在端口sel -out 输出,端口framenum (31..0)为发送的总帧数。

模块dat 485-fifo -recv 利用200M Hz 高速时钟对串行信号sel -in 进行位同步,得到串行数据,经过串并转换和帧同步得到有效帧数据,再经过8B /10B 的解码得到数据,逻辑状态控制时钟为20M Hz,端口recv -8b (7..0)为收到的解码数据,端口right -num (31..0)为收到的正确帧数,端口err -num (31..0)为收到的出错帧数。

传输协议逻辑占用了2413个逻辑单元,并利用Altera 公司提供的Log iclock 技术对传输协议进行了优化和锁定,使逻辑的时序要求可以满足225M Hz ,保证了程序的稳定性。

而后,对传输协议逻辑进行了仿真,得到仿真结果,见图5。

图4 传输协议FPGA 顶层结构图图5 基于FPGA 的传输协议仿真结果 send -8b 为发送端编码前的链路数据帧,send -10b 为发送端编码后的链路帧,从仿真结果中可以看到,编码过程有2个2M Hz 时钟周期的延迟,8B 数据“BC ”对应的10B 数据“17C ”(10B 数据“0B9”是8B 数据“00”的编码)。

sel -out 为编码后的数据并串转换后的串行信号。

r ecv -10b 是接收端经过位同步后收到的未解码数据,位同步需要的延时为1.5个2M Hz 时钟周期,recv -8b 为接收端收到的解码后数据,解码过程由帧同步时钟frame -clk 驱动,基本为实时过程。