bandgap电路设计报告

无运放带隙基准电路设计

无运放带隙基准电路设计

运放带隙基准电路(opamp bandgap reference circuit)是一种基于运放的电路,用于提供稳定的参考电压。

它的设计基于运放的放大特性和电压反馈机制,通过差分放大和反馈调整,产生一个相对稳定的参考电压。

下面是一种常见的运放带隙基准电路的设计:

1. 选择一个适当的运放芯片,具有低噪声、高增益和低温漂移等特性。

2. 将运放芯片的非反相输入端与反相输入端相连,形成一个差分输入。

3. 将一个稳定的参考电压Vref1与非反相输入端相连。

4. 将运放芯片的反相输入端与一个电阻R1相连,然后将R1与一个稳流二极管D1的阴极相连。

5. 通过调整R1的值,使得二极管D1的电流可以产生一个正向电压降,并且与稳定的参考电压Vref1相等。

6. 将运放芯片的输出端与R1与D1的连接处相连,形成一个反馈回路。

7. 调整运放芯片的反馈电阻R2的值,使得输出电压与稳定的参考电压Vref2相等。

通过以上设计,运放正向反馈的放大特性和电压反馈机制可以保证输出电压与参考电压的稳定性。

同时,稳定的参考电压Vref1的产生通过差分放大和反馈调整的方式可以减少温度、电源等参数的影响。

需要注意的是,具体的设计参数需要根据具体的应用要求来确定,比如参考电压的稳定性要求、输出电压的范围等。

同时,在实际设计过程中,还需要考虑电源稳定性、电路布局和滤波等因素,以确保设计的稳定性和可靠性。

bandgap设计及仿真介绍

5.温度补偿结构

R3

R2

I1

I2

V R1

R

1

Q2

V REF

Q1

此结构是在一个负反馈运 算放大器的两个输入端各 接一个稳压电路。两路稳 压电路并联。它们并联的 总电压作为我们所要的参 考电压,连接到运放的输 出端输出。电源电压包含 在运放里。下面分析一下 它的工作原理。

R

3

R

2

I I

2

1

V

R 1

R

> 0

6.关于K的两点讨论

R3

R2

I1

I2

VR1

• 1.K必须独立于温度(用电阻之 比) • 2.K必须独立于电源电压

VREF = VEB 2 + KT

VREF

R k R A K = 2 ln 2 E 1 R q R A 1 3 E 2 > 0

1

V

Q

R E F

2

Q

1

V REF = V BE 2 + V R 3

(VR3即是我们要构造的KT项)

VR 3

R2 = I 2 R3 = I 1 R2 = VR1 ∗ R1

VR1 = VEB 2 − VEB1

kT J 2 kT J 1 k I 2 AE1 = ln J − q ln J = q ln I A ∗ T q I

∆V

V

这种结构的稳压性能虽好,但是它的温度特 性仍然没有得到改善。VBE具有负的温度系数,在 室温时大约是-2.2mV/℃。我们可以通过补偿的 方法来改善参考电压源的温度特性。我们期望构 造出具有正温度系数的KT项,其中K为正常数, T T为热力学温标,使

bandgap带隙基准源电路

bandgap带隙基准源电路Bandgap带隙基准源电路是一种用于产生带隙基准电压的电路,它在模拟电路设计和集成电路设计中具有重要的作用。

带隙基准电压是一种与温度和电源电压无关的直流电压,它可以用于电路的偏置、ADC的基准、温度传感器等。

带隙基准源电路的设计原理是基于硅材料的带隙能量,它的带隙能量为1.12eV,对应于温度为273.15K。

带隙基准源电路的核心思想是将带隙能量转化为直流电压,并通过一定的放大和调节电路,得到温度和电源电压无关的基准电压。

带隙基准源电路的基本结构包括三个部分:偏置电路、带隙电压产生电路和放大电路。

其中,偏置电路用于产生一个与电源电压无关的直流电流,带隙电压产生电路用于将带隙能量转化为直流电压,并且放大电路用于调节带隙基准电压的大小和精度。

偏置电路通常采用一个PNP晶体管和一个电阻组成,PNP晶体管的基极-发射极电压作为偏置电压。

这个偏置电压具有负的温度系数,即随着温度的升高,它的值会减小。

为了使整个电路的温度系数为零,需要将这个偏置电压与一个具有正温度系数的电压进行补偿。

带隙电压产生电路通常采用两个晶体管和电阻组成,其中一个晶体管的基极-发射极电压作为带隙电压,另一个晶体管的基极-发射极电压具有正的温度系数。

通过调节两个晶体管的发射极电流比值,可以得到一个与温度无关的带隙电压。

放大电路用于调节带隙基准电压的大小和精度。

通常采用一个高精度、低噪声的放大器,将带隙基准电压进行放大和调节。

放大器的增益和带宽需要满足一定的要求,以确保带隙基准电压的精度和稳定性。

在实际应用中,带隙基准源电路还需要考虑一些其他的因素,如电源噪声、温度范围、功耗等。

为了实现高精度的带隙基准电压,需要采用一些优化设计方法,如低噪声电源、温度补偿技术、自偏置电路等。

在实际应用中,带隙基准源电路有着广泛的应用。

它可以用于各种类型的模拟电路和数字电路中,如运算放大器、比较器、ADC、DAC、PLL等。

它可以提供高精度的基准电压,帮助这些电路实现高精度、低噪声、稳定的性能。

bandgap设计及仿真介绍

Q1

7.功能的进一步优化

R2

R3

I1 I2

VR1

在这个图中,将上图中 的R2和R3两个普通电阻 分别换成了由两个MOS 管串连,其中一管栅极 接地的结构。此结构称 为cascode结构。

R1

Q2

Q1

8.下面来看开始提出来的实际的电路结构

• 1.为上面一排P管提供栅极偏置电压的电压是 二极管的偏置电压,所以是稳定电压。 • 2.此处相当于原型的R2=R3(比较一下R2所代 表之cascode结构和R3所代表之cascode结构 其各端点电压和几何结构参数完全相同,所以 静态和动态阻抗也完全相同)。由前面VR3上 压降表达式可知,VR3上压降与电源电压无关。 所以运放输出端对地电压=二极管上压降+ VR3上压降,也是一个稳定电压。

R1

Q 2

Q1

KT项其实是两只稳压管的be结电压

R3

R2

之差,这个电压我们是通过负反馈 运放虚短用R1电阻取得的。我们又 通过负反馈的作用使得I1/I2固定于

I1

I2

VR1

R1

R2/R3,从而使得K值独立于温度和

Q 2

VREF

电源电压。最后,通过R1与R3的电 压线性比例关系得到在R3上的温度 补偿电压。

1

V

Q

R E F

2

Q

1

V REF = V BE 2 + V R 3

(VR3即是我们要构造的KT项)

VR 3

R2 = I 2 R3 = I 1 R2 = VR1 ∗ R1

VR1 = VEB 2 − VEB1

kT J 2 kT J 1 k I 2 AE1 = ln J − q ln J = q ln I A ∗ T q S2 1 E2 S1

Bandgap集成电路掩模版图设计

摘要集成电路掩模版图设计是实现集成电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、本钱与功能。

模拟版图设计对电路的性能有更高的要求,要求模拟版图设计者使用更多的方法去优化电路,减小电路的寄生参数,提高电路的稳定性。

本论文首先介绍半导体制造技术、模拟IC版图设计的根本流程,然后通过bandgap 的单元版图设计到整体版图设计流程具体介绍模拟版图设计的一些细节和一些问题的解决方法,最后介绍一些平面布局与封装技术。

本设计使用cadence 全定制设计工具IC610进展bandgap的版图设计,其后使用diva对版图进展物理验证。

关键词:版图;bandgap;cadence;ICAbstractIC mask layout are essential to achieve the design of integrated circuit manufacturing sectors, it is not only related to the IC's functions are correct, but also great extent affect IC performance, cost and functionality. Simulate the performance of the circuit layout have higher demands to analog layout designers to use more methods to optimize the circuit, reducing the parasitic circuit parameters, to improve the stability.This paper first introduces the semiconductor manufacturing technology, analog IC layout design of the basic flow, then bandgap of the cell layout to the overall layout design process specific analog layout design introduced some of the details and some solution to the problem, and finally introduce some layout and packaging technology. The design of full custom design using cadence tools IC610 for bandgap of the layout design, then use the diva of the physical layout verification.Keywords: layout; bandgap; cadence; physical verification目录1 绪论12 工艺简介22.1光刻22.2掺杂42.3淀积42.4CMOS工艺42.5PNP工艺62.6POLY电阻工艺73 CADENCE简介84 BANDGAP版图设计流程104.1原理图104.1.1 原理图信息114.1.2 Bandgap简介114.1.3 Bandgap仿真124.2模块划分134.3单元版图设计144.3.1 模块MP1_MP3版图设计144.3.2 模块MP2_MP4版图设计154.3.3 模块MP9,MP10版图设计164.3.4 模块MN1_MN3版图设计174.3.5 模块MN2_MN4版图设计184.3.6 模块MN5_MN8版图设计194.3.7 模块NCH版图设计204.3.8 模块R1版图设计214.3.9 模块R2版图设计214.3.10 模块Q1_Q2版图设计224.3.11 模块Q3,Q4,Q5版图设计23 4.4整体版图设计244.4.1 平面布局254.4.2 布线264.5验证264.5.1 设计队如此检查〔DRC〕264.5.2 版图与原理图的对照〔LVS〕274.5.3 版图几声参数提取〔LPE〕274.5.4 寄生电阻提取〔PRE〕27结论28致谢28参考文献28附录A 英文文献29附录B 中文译文33附录CBANDGAP的SCHEMATIC网表35附录D BANDGAP的LAYOUT网表381 绪论无论是数字集成电路设计还是模拟、混合集成电路设计,版图设计都是必不可少的重要设计环节。

带隙基准电压源(Bandgap)设计范例

五. 输出输入信号线时序图

VIN 、ENB、 BIAS_EN 、BIAS2_EN 为输入信号,VREF 、 BIAS 、BIAS2 为 输出信号。

图 1.3

BANDGAP 模块输入输出时序关系图

六. 等效架构图原理分析

BANDGAP 模块是一个带隙基准结构。 带隙基准的工作原理是根据硅材料的 带隙电压与电压和温度无关的特性,利用△VBE 的正温度系数与双极型晶体管 VBE 的负温度系数相互抵消,实现低温漂、高精度的基准电压。双极型晶体管提 供发射极偏压 VBE;由两个晶体管之间的△VBE 产生 VT ,通过电阻网络将 VT 放 大 a 倍;最后将两个电压相加,即 VREF=VBE+aVT ,适当选择放大倍数 a ,使两 个电压的温度漂移相互抵消, 从而可以得到在某一温度下为零温度系数的电压基 准。下面详细推导这个原理。 一般二极管上电流和电压的关系为:

Q12 和 Q19 的电流相等;R19、R20、R21 和二极管连接的 Q11 组成分压网络, 将 Q12、Q19 产生的 ? VBE 放大(R19+R20+R21)/R21 倍后与 VBE11 相加,产 生基准电压 VREF ;放大管 QX7 、Q18 和负载管 Q10 组成符合放大电路,将 IC19 和 IC12 的差值放大,反馈到分压网路中的 R21,从而调整 Q12、Q19 的工作点, 保证 IC19 等于 IC12 ;电容 C2 和 R23 用来进行频率补偿。 电流偏置 IBias2 产生电路(图 2(c)) :由 P39、Q3、R8 组成。Q3 的基极连 接 VREF ,其射极电位即 R8 的一端电位 VEQ3=VREF -VBEQ3,与电源电压无关, 从而流过电阻 R8 的电流与电源无关,即 IBias2 与电源无关。 1.使能原理: ENB 高电平时,使能关断有效。当 ENB 为高电平时,使能管 N15、N18、 N17 工作,则 N19 的漏极电压、P8 的漏极电压、VREF 被拉到低电平,电路关 断。 BIAS_EN 低电平时,使能关断有效。当 BIAS2_EN 低电平时,使能管 P13 工作,P7、P1 的栅极即 Bias 为高电平,电流偏置为 0,同时,基准电压 VREF 为零电平。 BIAS2_EN 低电平时,使能关断有效。当 BIAS_EN 低电平时,使能管 P34 工作,Bias2 为高电平,电流偏置 IBias2 为 0。 2.启动原理 P14、R15、N19、N16 组成启动电路。启动过程:ENB 为低电平,当未启 动时,P7、P8 两支路的电流为 0,此时 P8 的漏极电压为 0 电位,N19 不通,N19 的漏极为高电位,此时 N16 管导通,形成从电源到地的通路 R12、P7、N16,使 P7 有电流流过,从而打破 0 电流的状态;之后 P8 漏极电位上升, N19 导通, N16 截止,启动过程结束。

带隙基准电压源BandGap的调节与理论分析

ln nI0 IS1

VT

ln I0 IS2

VT

ln n

VBE k ln n T q

VBE的差值就表现出正温度系数。

零温度系数的基准电压

利用双极晶体管的正,负温度系数电压,可设计出 一个零温度系数的基准。 VREF VBE (VT ln n)

令 =1,VBE T =-1.5mV 。K VT T 0.087对上式 两边分别对温度T求导,得到零温度系数的基准:

带隙电压基准的基本原理:将两个拥有相反温度系 数的电压以合适的权重相加,最终获得具有零温度 系数的基准电压。

负温度系数电压

双极晶体管的基极-发射极或者说是pn结二极管具 有负温度系数。

VBE T

VT T

ln IC IS

(4 m) VT T

Eg kT 2

VT

VBE

VBE

ln n 17.2 VREF VBE 17.2VT 1.25V

BandGap电路原理图

与电源无关的偏置电路

BandGap偏置电路主要通过改变电阻R1 的值使得电流稳定在18uA左右,NM12采用二 极管的连接方式得到一个对电源Vdd不敏感的 偏置电流Iref,通过NM13的尺寸比例将Iref自 举到Iout,使得Iref和Iout满足一定的比例关系 并与Vdd的变化无关。

产生一个和绝对温度成正比的PTAT电流。

这里的Cascode结构主要是近似为一个电路源使

得流过Q4,Q5这两条电路的电流相等使得Vo1

VO1

VO2与Vo2稳定在近似相等的电压,所以在调试

cascode电路时要使输出电阻尽可能的大。

BandGap电压的产生

产生的PTAT电流通过由PM23-PM26组 成的电流镜电路复制到到基准电压输出 端,可以得到:

BandGap设计心得

Bandgap也算模拟电路里的重要角色了,差不多可以说有模拟电路的地方就有Bandgap。

从原理上说,目前用的bandgap都离不开两个东西,一个是deltaVbe,一个是Vbe。

前者产生的是一个kt/q形式电压,后者产生的是一个随温度准线性的电压。

而bandgap的输出就则由这两个电压线性组合决定。

至于为什么有温度系数,从最大的因素上说,就来自于Vbe,VBe只是随温度准线性,而另一个电压则是线性度很好的。

原理上知道了,在实际中怎么设计?Vbe好说,就是给二极管(或者说三极管)一个电流。

deltaVbe则离不开一定形式的反馈。

从大的角度讲,一种是用opa设计的,一种是用镜像电流镜设计的,从反馈的角度看,这两种电路是完全不同的。

用opa设计的是一个负反馈,更严格的说,是有两个反馈支路,一正一负,而一定要负反馈强于正反馈,保证整个系统是负反馈。

另一种上面一个电流镜,下面一个电流镜,只是下面电流镜加了diode做degeneration。

这个从系统的角度讲是正反馈,正反馈如果用在电路里,就一定要保证环路增益小于1才能稳定.由于稳定性的要求,所以这两种电路都不能随便把左右互换。

至于仿真稳定性,对于用opa设计的负反馈电路,我的观点很明确,必须把正负反馈两个支路合起来仿真稳定性,否则仿真结果没有任何意义(如果有人争辩说,不是已经理论分析得出了正反馈弱于负反馈吗?那我就要反问仿真的意义是什么?)。

对于正反馈,我不是很清楚稳定的判据,所以一般都是看看增益是否会超过1.在实际的应用中,我很少碰到有很强调温度系数的设计,这似乎和学校里的要求刚好相反。

这也许是因为我设计的电路中ADC和DAC很多都不是测量用的。

偶尔碰到那么几个,其指标也在10bit左右,看了看别人产品的datasheet,也只要求30-60ppm。

与其强调温度系数,反倒不如强调随工艺变化造成的静态输出变化。

所以对于如何在工程上实现一个很好温度系数的bandgap我很感兴趣。

CMOS模拟集成电路实训-Bandgap

R3

ln n

R2

VDD

Y

A1

R3

n

Q2

VREF

电路实现

VDD M2

R1

R2

M1

M0

R3

M3

M4

Q1

n Q2

M6

M7

VREF

IBIAS M5

两种结构的性能比较

1.驱动能力 PTAT基准不能直接为后续电路提供电流,需要在带隙电压基准和后

续电路中加入缓冲器才能提供电流。 2.面积

运放输出基准需要使用3个电阻,并且在Q1和Q2的比值n较小的时候, 需要使用更大阻值的R1和R2。因此消耗更多的芯片面积。

M R2 17.2 R1 ln n

VDD

M5

M6

M

M8

I1

A 1

I2

I3

X

Y

VREF

R1

R2

n

Q2

Q3

Q1

电路实现

VDD M5

M3

M4

M0

M1

R1

M2 Q1

M6

M7

M8

VREF R2

M9

Q2

Q3

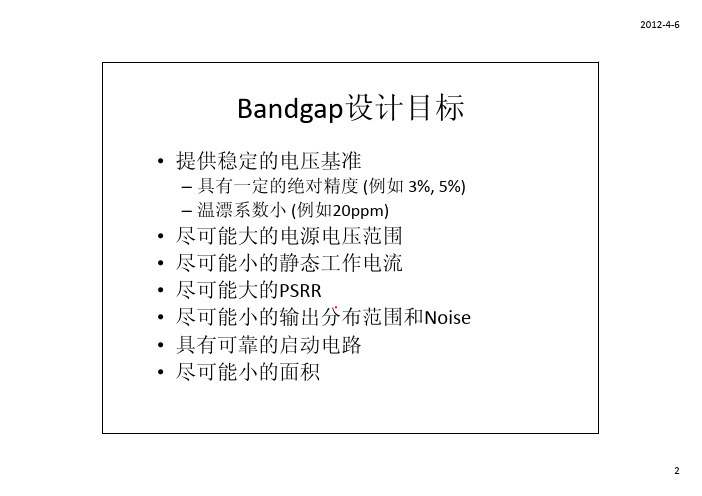

内容

• 带隙电压基准的基本原理 • 常用带隙电压基准结构

– PTAT带隙电压基准 – 运放输出电压基准

射极电压的差值(ΔVBE)与绝对温度成正比 双极型晶体管构成了带隙电压基准的核心

负温度系数电压

·双极型晶体管,其集电极电流(IC)与基极-发射极电压(VBE)关系为

IC IS exp(VBE VT )

其中,VT kT q 。利用此公式推导得出VBE电压的温度系数为

VBE VBE (4 m)VT Eg q

bandgap

BandgapBandgap电路原理如下:V BE1=V T ln(I/(n*Is))V BE2=V T ln(I/Is)V R1=V BE1-V BE2=V T ln(n)I=V R1/R1=V T ln(n)/R1Vref=(R2/R1)V T ln(n)+V BE3选用一个一级运放,运放测试电路图如图所示。

bias电流设置为227nA,输入端输入电压分别为700mV、699mV,即V in=1mV。

仿真波形见下图。

V out=4.08V,即该运放的开环增益为4080倍。

?Bandgap电路原理图如下图所示对r2设置不同值仿真,当r2为460k时vref最稳定。

1、电容在图示位置放置一个100p的电容。

当电容断路时,当电源接通,电路即刻开始工作。

当电容接入时,电路在70s后开始正常工作。

为消除电容影响,设计了如图所示的启动电路,启动电路的构成为一个反相器接一个N管。

当电路未开始正常工作,Vref电压低,N管导通拉低D点电压,各管导通电路可以开始正常工作。

Vref电压升高,启动电路关断。

下图中图一是未加启动电路时的仿真波形,图二是加启动电路后的仿真波形,图三是未接电容时的仿真波形。

可见电容影响基本被消除。

2.电路功率测如图六处电流P=IU=(0.134+0.134+1.85+1.85+1.6+1.8)uA*5V=36.84uW4.管子宽长设置如图,下方蓝色曲线是宽1.1um、长550nm的管子,当电源从4变化到6时的电流曲线。

上方曲线是当宽分别取值2、3、4、11um时的电流曲线。

综合管子大小和电流平稳程度考虑,选择3/1.5um。

(电压值需提升到12V?疑问,暂未使用)。

bandgap电路原理

bandgap电路原理

bandgap电路,也称为压控稳压器,又称特性电路,它是一个电路,能够使任意的欧

姆容量(Ohm's Law)负载保持一个恒定的电压。

它是一种二极管放大电路,一般用于作

为电池或电压源,当给定电池耗尽时它可以保护电路免受电池变化和供电抖动的影响。

Bandgap电路由两个特殊部件组成:漏极稳压器(Shunt Regulator)和反馈电阻(Feedback Resistor).

漏极稳压器是一种开关电路,它可以把负载与供电电源分开,当负载电压到达预定的

最大值时,它会自动断开负载及供电电源的连接,从而稳定电源电压。

反馈电阻是一种电路,它能够把负载电压与漏极稳压器的开关的工作状态关联起来,

当负载电压下降,反馈电阻就会开关,把电源电压稳定下来,在负载电压上升时,反馈电

阻会关闭,以阻止过载保护电路。

Bandgap电路有许多优点,它可以提供高精度的输出电压,即使它所处在的电路有较

大的负载变化,它也能给出可靠的输出,并且电路设计简单、可靠,维护无需费力,功耗小,只需安装在小封装内,因此在电源设计中有广泛的应用。

综上所述,bandgap电路是一种可靠的电路,用于对电源电压提供良好的输出稳定性。

它的原理是通过混合漏极稳压器和反馈电阻来调节负载电压,确保电路工作正常,具有许

多优点。

带隙基准电压源(Bandgap)设计范例

图 1.1

Bandgap 模块线路图

二. 等效架构图

(a)

(b)

(c) 图 1.2 Bandgap 模块等效原理图

三. 电路功能描述

正常工作时,Bandgap 模块为系统提供稳定、高精度的 1.28v 的基准电压, 并为其它电路模块提供稳定的偏置电流。

四. 输出、输入信号线功能描述

I = I S (e qVB E / kT − 1)

(1.1) 当 VBE >> kT / q 时, I ≈ I S e q.VBE / k .T

VBE = VT . ln( I ) IS

(1.2) 其中 VT = kT 为热电压,k 是 Boltzmann 常数,q 是电荷量。 q

图 1.2(b) 是参考电压产生的实际等效架构电路, R19 、R20 、R21 、Q11 和 Q12、Q19 构成带隙电压产生器的主题部分,由 Qx10 、Qx8 、 Q19、 Qx7 、 Q10 以及 Q18 组成了放大器及补偿电路,保证了参考电压输出的稳定。 由运算放大器的性质,得:

Q12 和 Q19 的电流相等;R19、R20、R21 和二极管连接的 Q11 组成分压网络, 将 Q12、Q19 产生的 ? VBE 放大(R19+R20+R21)/R21 倍后与 VBE11 相加,产 生基准电压 VREF ;放大管 QX7 、Q18 和负载管 Q10 组成符合放大电路,将 IC19 和 IC12 的差值放大,反馈到分压网路中的 R21,从而调整 Q12、Q19 的工作点, 保证 IC19 等于 IC12 ;电容 C2 和 R23 用来进行频率补偿。 电流偏置 IBias2 产生电路(图 2(c)) :由 P39、Q3、R8 组成。Q3 的基极连 接 VREF ,其射极电位即 R8 的一端电位 VEQ3=VREF -VBEQ3,与电源电压无关, 从而流过电阻 R8 的电流与电源无关,即 IBias2 与电源无关。 1.使能原理: ENB 高电平时,使能关断有效。当 ENB 为高电平时,使能管 N15、N18、 N17 工作,则 N19 的漏极电压、P8 的漏极电压、VREF 被拉到低电平,电路关 断。 BIAS_EN 低电平时,使能关断有效。当 BIAS2_EN 低电平时,使能管 P13 工作,P7、P1 的栅极即 Bias 为高电平,电流偏置为 0,同时,基准电压 VREF 为零电平。 BIAS2_EN 低电平时,使能关断有效。当 BIAS_EN 低电平时,使能管 P34 工作,Bias2 为高电平,电流偏置 IBias2 为 0。 2.启动原理 P14、R15、N19、N16 组成启动电路。启动过程:ENB 为低电平,当未启 动时,P7、P8 两支路的电流为 0,此时 P8 的漏极电压为 0 电位,N19 不通,N19 的漏极为高电位,此时 N16 管导通,形成从电源到地的通路 R12、P7、N16,使 P7 有电流流过,从而打破 0 电流的状态;之后 P8 漏极电位上升, N19 导通, N16 截止,启动过程结束。

bandgap电路设计报告

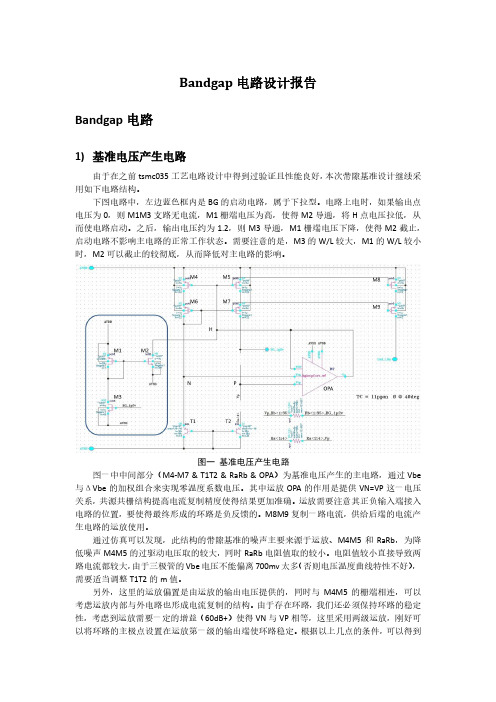

Bandgap电路设计报告Bandgap电路1)基准电压产生电路由于在之前tsmc035工艺电路设计中得到过验证且性能良好,本次带隙基准设计继续采用如下电路结构。

下图电路中,左边蓝色框内是BG的启动电路,属于下拉型。

电路上电时,如果输出点电压为0,则M1M3支路无电流,M1栅端电压为高,使得M2导通,将H点电压拉低,从而使电路启动。

之后,输出电压约为1.2,则M3导通,M1栅端电压下降,使得M2截止,启动电路不影响主电路的正常工作状态。

需要注意的是,M3的W/L较大,M1的W/L较小时,M2可以截止的较彻底,从而降低对主电路的影响。

图一基准电压产生电路图一中中间部分(M4-M7 & T1T2 & RaRb & OPA)为基准电压产生的主电路,通过Vbe 与ΔVbe的加权组合来实现零温度系数电压。

其中运放OPA的作用是提供VN=VP这一电压关系,共源共栅结构提高电流复制精度使得结果更加准确。

运放需要注意其正负输入端接入电路的位置,要使得最终形成的环路是负反馈的。

M8M9复制一路电流,供给后端的电流产生电路的运放使用。

通过仿真可以发现,此结构的带隙基准的噪声主要来源于运放、M4M5和RaRb,为降低噪声M4M5的过驱动电压取的较大,同时RaRb电阻值取的较小。

电阻值较小直接导致两路电流都较大,由于三极管的Vbe电压不能偏离700mv太多(否则电压温度曲线特性不好),需要适当调整T1T2的m值。

另外,这里的运放偏置是由运放的输出电压提供的,同时与M4M5的栅端相连,可以考虑运放内部与外电路也形成电流复制的结构。

由于存在环路,我们还必须保持环路的稳定性,考虑到运放需要一定的增益(60dB+)使得VN与VP相等,这里采用两级运放,刚好可以将环路的主极点设置在运放第一级的输出端使环路稳定。

根据以上几点的条件,可以得到运放的结构如下图二所示。

其中的两个P管电流源可以看成是与图一中M4和M5成电流复制结构。

带隙基准电路设计与仿真设计报告(西安邮电大学)

一、研究现状总结分析1.题目:带隙基准电压源设计2.小组成员:3.所选课题电路系统的研究现状总结和分析基准源是模拟和混合信号集成电路的重要组成部分,它广泛的用于电源管理芯片、温度传感器、数据转换器(包括模数转换器ADC和数模转换器DAC)、电压稳压器和存储器中。

作为整个电路或者系统的“基准”,其性能直接影响整个电路或者系统的性能。

基准源应该具有良好的抗干扰能力,如:在整个工作温度内,受温度变化影响很小;在一定的电源电压变化范围内的变化很小;受工艺影响较小等。

事实上,由于大多数工艺参数都是随着温度变化的,所以如果-一个基准是与温度无关的,那么通常它也是与工艺无关的。

所以,一般而言基准源最重要的两个参数指标即温度特性和电源抑制特性。

随着集成电路规模的不断扩大,电路的结构和功能也日趋复杂,片上系统(SoC)必将成为大势所趋,而将如此多的电路模块集成到一起,对基准源的抗干扰能力提出了更加苛刻的要求。

与此同时,集成电路的特征尺寸伴随着工艺的进步越来越小,相应的电源电压也越来越低,然而,阈值电压的降低却滞后于电源电压的降低,因此对基准源的设计提出了更大的挑战。

不仅如此,越来越多的高精度数据转换器的广泛使用,无疑也大大提高了基准源的设计难度。

综上所述,随着电路规模、精度的提高和尺寸的减小,对基准源的设计提出了越来越大的挑战。

因此,研究在深亚微米条件下的高性能基准源电路具有十分重要的意义。

1.低温度系数的带隙基准源低温度系数的基准源在高精度系统中具有广泛应用,如:高精度的模数转换器、数模转换器和线性稳压器等。

一般只采用一阶温度补偿策略的基准源能达到20-50ppm/C""l,要进一步降低温度系数,就必须采用高阶温度补偿策略。

可通过分段线性补偿的方法,它将基准源的工作温度分为若干个子区间,对每个区间分别进行补偿,从而在整个工作温度内获得较低的温度系数。

曲率补偿的方法是通过在基准源输出电压上叠加一个温度的指数函数,从而实现高阶补偿的目的。

带隙基准电压源电路设计

带隙基准电压源电路设计英文回答:Bandgap Voltage Reference Circuit Design.Bandgap voltage reference circuits are a critical component in many electronic systems, providing a stableand accurate voltage reference against which other circuits can be calibrated. They are particularly useful in applications where low power consumption, a wide operating temperature range, and high accuracy are required.The design of a bandgap voltage reference circuit typically involves the following steps:Choosing a suitable bandgap voltage: The bandgap voltage is the voltage difference between the base and emitter of a bipolar junction transistor (BJT) operating in the forward-active region. It is typically around 1.2 V at room temperature and has a positive temperature coefficient,meaning that it increases with increasing temperature.Designing a temperature-compensated circuit: The temperature dependence of the bandgap voltage can be compensated by using a combination of BJTs, resistors, and capacitors. The goal is to create a circuit that has a constant output voltage over a wide temperature range.Adding additional features: Depending on the specific application, additional features such as low-power operation, low noise, or voltage trimming may be required. These features can be implemented using additionalcircuitry or by carefully choosing the components used in the design.中文回答:带隙基准电压源电路设计。

Bandgap(带隙)_Circuit

BroadGalaxy Confidential

43

课后练习要求

指标要求: VREF直流范围:0.7V~0.9V; IREF直流范围:10uA~50uA VREF温度系数:<16ppm,-40DEG~120DEG; VREF 1mV VREF电源电压扫描: ,VDD=1.6V~2V IREF温度扫描: I REF 1A I REF 1A IREF电源电压扫描: 闭环STB仿真:phase margin>60degree gain margin>10dB

闭环电路的稳定性判据

AV s As As 1 As s 1 T s

As A(s j ) -1,thegain goes to infinityand the amplifiercan oscillate In other word s, oscillatio n can occur when A(j1 ) 1 A(j1 ) -1800

R2

R1

VREF

V VR1 VR 2

VR1 VR 2 I I rR1 rR 2 I I I

BroadGalaxy Confidential 6

电压基准结构选择

这说明 V 在R1、R2上的分 配与R1、R2的动态电阻成 正比。如果我们能让R1的动 态电阻很小,R2的动态电阻 很大,则 V 大部分落在R2 上,一小部分落在R1上, 对电源电压的灵敏度会大大 降低,稳压性能就会得到很 大提高。

s ( VREF V DD V REF V DD )

(

)

动态电阻:对于一个二端元件,当其端电压变化时,端 电压微小增量与端电流微小增量的比值。动态电阻等于 I—V曲线上参考点处曲线斜率的倒数。

bandgap设计教程.

1 : 1V REF∂V 考虑版图,N可取8R3=R0, R4=R2, M3=M2,R3R0R4R2M3M2运放的失调必须控制好具体设计请参考基准电压与电流201R R V V V BEBE REF ⋅Δ+=Ref:sansen 0ln 21R R N q kT V V BE REF ⋅⋅+=−~m1156mVchapter 16()T C T V V g BE +=λ00For I DS T ln qR N kT I BG⋅=Is PTAT0qVBG 通常在1.2左右结合电阻的温度系数,IBG 在高温与低温下其值变化可能较大,若用它直接去偏置其他电路,这一点须特别注意IBG~T 注意到:IBG T 时,gm constant二次补偿:VBG 的温度特性包含抛物线型非线性项,设计中令顶点位于常温附近,更高精度要求可采用二次补偿电路(例sansen ppt 1626)简单的电阻补偿:ln NkT I BG ⋅=若采用负温度系数的电阻,有可能降低非线性,实现更小的温度系数qR 例:设置不同的电阻温度系数,并在每个系数下调整电阻比例至最佳输出状态Tr1 = 1m Tr1 = ‐2m Tr1 = ‐3m温度系数——不同的Corner下,会有不同的温度系数,希望通过调整电阻比例,将温度系数调整至最佳状态调整至最佳状态;输出电压值:由于失配,或工艺起伏,输出电压会在一个范围内变化,系统通过调整电阻比例,将变化的范围控制得小一些。

电路设计:将电阻分段,并加开关控制;校准策略:批校准;每个校准校准策略批校准每个校准启动与稳定性启动:这个电路有两个稳定工作点,其中一个是两个支正反馈负反馈启动电路回路回路静态损耗:VDD/RESOpa RC VBG MOSCAPVREF ‐Vos +抑制/噪声采1/f噪声还可采用chopping技术V/I转换V/V转换R1=R2VBG的大小可通过整, 不影响温度系数IBG=VBG/R3,由IBG温漂较小,主要取决于电阻温度系数最低电源电压可正反馈环负反馈环MOSResistor正常输出下VBG>VTn, 否则应采用其他形式的启动电路MOSCAPPMOS采用folded结构采用PMOS输入差分对, 减少1/f噪声, 并适合于低输入共模的情况VGS‐VT小, 其他电流镜VGS‐VT大, 晶体管的L要大一些, 减输入差分对GS GS要大些少失调, 1/f噪声, 以及沟道调制效应自便置设计启动时,vb1若为高,则无法启动,故需增加拉低vb1低压设计将R1, R2由两个电阻串联,取中间点接运放输入,可降低输共模步降低压压入共模,进一步降低电压电压要求运放采用PMOS输入的folded‐cascode结构或symmetrical结构可进一步采用电路设计技术来降低运放对电源电压的要求‐BandgapSub1V ExampleRef: Ka Nang Leung, JSSC2002采用symmetrical结构和电平移位(level shifting)来降低输入共模要求ip inPhase 1in ipPhase 2。

bandgap

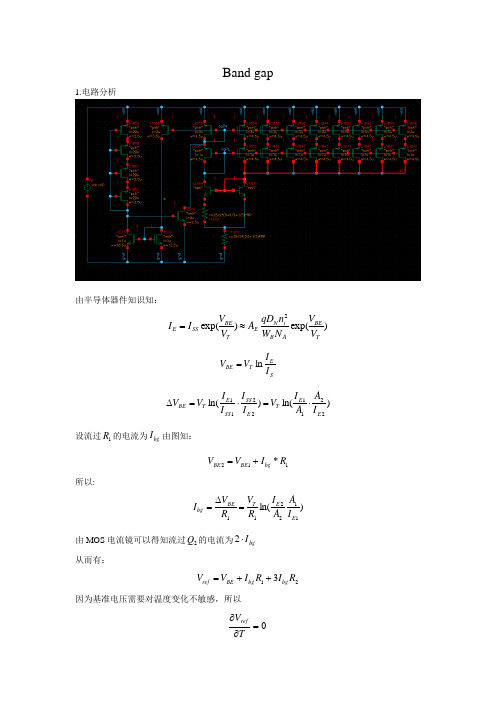

Band gap1.电路分析由半导体器件知识知:)exp()exp(2TBE A B i N E T BE SS E V VN W n qD A V V I I ≈=SET BE I I V V ln= )ln()ln(22112211E E T E SS SS E T BE I A A I V I I I I V V ⋅=⋅=∆ 设流过1R 的电流为bg I 由图知:112*R I V V bg BE BE +=所以:)ln(112211E E T BE bg I AA I R V R V I =∆=由MOS 电流镜可以得知流过2Q 的电流为bg I ⋅2 从而有:213R I R I V V bg bg BE ref ++=因为基准电压需要对温度变化不敏感,所以0=∂∂TV ref因为C mV TV BE2-≈∂∂C mV TV T086.0+≈∂∂带入可以求得1122E E I A A I ∙=8 所以421=A A2.仿真分析2.1启动时间的仿真阶跃激励:t=1us,vdd=5V仿真设置:仿真结果:仿真结论:由图知道基准启动时间为20ns。

2.2 DC 温度仿真 仿真条件:仿真波形:由以上数据可以得到:在-20℃~40℃,℃mVT V ref 2.0≈∂∂在40℃~150℃,℃mVTV ref 19.0-≈∂∂2.3 Q1发射极面积的参数扫描在DC 温度仿真中扫描Q1发射极面积。

仿真条件:仿真波形:仿真结论:图中白色曲线为设计使用参数,可见X=4时基准的温度特性最好。

2.4 电源电压仿真在瞬态仿真中扫描VDD电压。

仿真条件:仿真波形:2.5 电源抑制比的仿真仿真设置:仿真波形:。

bandgap电路原理

bandgap电路原理

Bandgap电路原理是一种创新的电路设计方法,它利用了开关电源的原理来提供一种有效的电源调节方式。

它可以提供低噪声、低抖动、高精度和高稳定性的电源调节。

它可以在线性电路和开关电源之间提供一种灵活的调节。

Bandgap电路的主要原理是通过利用热噪声的基本原理来调节电源输出电压。

它利用温度稳定的二极管来产生固定的参考电压,然后通过比较二极管的输出电压与电源输出电压的不同来调节电源的输出电压。

Bandgap电路的核心组件是二极管,它具有非常低的漂移特性,可以提供稳定的参考电压。

二极管的输出电压通过放大器来放大,然后与电源输出电压进行比较,以此调节电源的输出电压。

Bandgap电路具有许多优点,它可以输出低噪声、低抖动、高精度的电源调节,而且它的漂移性能很好,可以提供高稳定性。

此外,它还具有低成本、低功耗、小尺寸等特点,可以在多种电子设备中应用。

总之,Bandgap电路原理是一种非常有效的电源调节方式,它具有低噪声、低抖动、高精度、高稳定性等特点,可以大大提高电子设备的性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Bandgap电路设计报告

Bandgap电路

1)基准电压产生电路

由于在之前tsmc035工艺电路设计中得到过验证且性能良好,本次带隙基准设计继续采用如下电路结构。

下图电路中,左边蓝色框内是BG的启动电路,属于下拉型。

电路上电时,如果输出点电压为0,则M1M3支路无电流,M1栅端电压为高,使得M2导通,将H点电压拉低,从而使电路启动。

之后,输出电压约为1.2,则M3导通,M1栅端电压下降,使得M2截止,启动电路不影响主电路的正常工作状态。

需要注意的是,M3的W/L较大,M1的W/L较小时,M2可以截止的较彻底,从而降低对主电路的影响。

图一基准电压产生电路

图一中中间部分(M4-M7 & T1T2 & RaRb & OPA)为基准电压产生的主电路,通过Vbe 与ΔVbe的加权组合来实现零温度系数电压。

其中运放OPA的作用是提供VN=VP这一电压关系,共源共栅结构提高电流复制精度使得结果更加准确。

运放需要注意其正负输入端接入电路的位置,要使得最终形成的环路是负反馈的。

M8M9复制一路电流,供给后端的电流产生电路的运放使用。

通过仿真可以发现,此结构的带隙基准的噪声主要来源于运放、M4M5和RaRb,为降低噪声M4M5的过驱动电压取的较大,同时RaRb电阻值取的较小。

电阻值较小直接导致两路电流都较大,由于三极管的Vbe电压不能偏离700mv太多(否则电压温度曲线特性不好),需要适当调整T1T2的m值。

另外,这里的运放偏置是由运放的输出电压提供的,同时与M4M5的栅端相连,可以考虑运放内部与外电路也形成电流复制的结构。

由于存在环路,我们还必须保持环路的稳定性,考虑到运放需要一定的增益(60dB+)使得VN与VP相等,这里采用两级运放,刚好可以将环路的主极点设置在运放第一级的输出端使环路稳定。

根据以上几点的条件,可以得到

运放的结构如下图二所示。

其中的两个P管电流源可以看成是与图一中M4和M5成电流复制结构。

电路工作时1.2v基准源处连接一个10uF的大电容,因此整个带隙基准部分电压和电流基本不会变动,所以图二运放的带宽要求很低。

图二基准电压电路中运放的电路图

最终运放和带隙基准电路形成的环路的stb仿真(连接所有后续相关电路)结果如下图三所示。

从图中可看出,环路增益为71dB,GBW为365K,PM为69°。

需要注意的是,如果外部电路的变化能直接耦合到基准产生电路,则上述环路的带宽需要做的较大,使其能快速恢复。

图三基准电压电路中环路stb仿真结果

整个带隙基准电压产生电路的电压温度仿真结果如下图四所示。

因为芯片功耗较大,预估芯片工作温度为40度左右,所以零温度系数点被设置在约40°的位置。

由图中显示数据可算得-40~85°范围内的温度系数为:TC = (1.20744-1.20578)/1.20744/(40+85)*10e6 = 10.98ppm,符合<15ppm的设计要求。

在调整零温度系数点位置的时候,主要调节RaRb的比例。

为减小版图匹配对这一比值的影响,RaRb的单元电阻值必须设置为同一值,且最小

边的长度不能太小,最好能设置成4u+。

本次设计由于面积限制,最终取了w=4u。

后面涉及到电阻比值的地方也应符合上述要求。

图四基准电压随温度变化曲线

2)基准电流产生电路

由于电路工作的温度范围较大,且电路性能指标要求较高,需要产生对温度变化不太敏感的电流基准。

可以仿真图一所示电路产生的电流随温度变化的关系作为对比,如图五所示。

可发现,该电流在工作温度范围内从8.4uA变化到了11.67uA,与预计的10uA相比变化了16%,变化幅度很大。

图五基准电压电路中电流随温度变化图

此次设计的基准电流产生电路如下图六所示。

通过运放的虚短特性,将温度系数很小的基准电压传递到运放负输入端,然后通过电阻产生一个温度系数较小的电流。

仿真得到的电流温度系数的结果如图七所示。

图中可见,电流在整个温度范围内从19.17uA变化到了21.35uA,与预计的20uA的基准电流相比,变化了6.75%。

这一结果与图五中所示结果相比,有了明显的改善。

但是,由于电阻有一定的温度系数,使得在电压温度系数很小的情况下,得到的电流温度系数还是不能达到很小。

因此在以后的改进中,可以将图六中的电阻换成两个温度系数符号相反的电阻串联,通过调整串联的加权值,使得总电阻的温度系数较小,从而可以得到一个温度系数很小的基准电流。

图六中运放由于需要用到虚短的特性,其增益需要较大。

运放与其后端的MOS管及电阻构成的环路需要保持稳定,可在运放的输出端接一个电容使得该点成为环路的主极点。

由于外部电路的变化可以耦合到电流复制的节点,这里环路的带宽不能太小。

运放设计采用一级折叠共源共栅的结构,仿真环路stb得到的结果为:环路增益=84dB,GBW=1.33M,PM=85°。

图六基准电流产生电路

图七基准电流随温度变化图

3)其它电路

在Bandgap总体电路中,我们还需要产生一个振荡器所需要的基准电压和一个中间电平的参考电压VREF。

振荡器的基准电压需要与模拟通道的基准电压隔离开来,而参考电压VREF 需要为整个电路提供参考。

其电路图如下图八所示。

图八其它电路结构图

其中左边的运放继续采用一级折叠共源共栅的结构,仿真环路stb得到LoopGain=63.8dB,GBW=3M,PM=81°。

右边电路通过电阻升压,产生2.5V的参考电压。

由于VREF在片外会接一个10uF的大电容,这里环路的主极点必须设计在运放的最终输出点。

为保证工艺偏差对输出结果的影响较小,要求运放的增益较高。

综合上述要求,这里运放采用两级结构,第一级为折叠共源共栅,第二级为共源级。

值得注意的是,在第一级与第二级之间不加密勒补偿电容,这样既能提供较高增益,又能保证环路的稳定性。

仿真环路稳定性,得到结果为LoopGain=89.85dB,GBW=41K,PM=81°。

因为有大电容存在,电压不会波动,这里的GBW 可以做的非常小而不影响电路性能。