xilinx vivado的五种仿真模式和区别

XilinxVivado的使用详细介绍(3):使用IP核--转载

XilinxVivado的使⽤详细介绍(3):使⽤IP核--转载IP核(IP Core)Vivado中有很多IP核可以直接使⽤,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。

IP核类似编程中的函数库(例如C语⾔中的printf()函数),可以直接调⽤,⾮常⽅便,⼤⼤加快了开发速度。

⽅式⼀:使⽤Verilog调⽤IP核这⾥简单举⼀个乘法器的IP核使⽤实例,使⽤Verilog调⽤。

⾸先新建⼯程,新建demo.v顶层模块。

(过程参考上篇⽂档)添加IP核点击Flow Navigator中的IP Catalog。

选择Math Functions下的Multiplier,即乘法器,并双击。

将弹出IP核的参数设置对话框。

点击左上⾓的Documentation,可以打开这个IP核的使⽤⼿册查阅。

这⾥直接设置输⼊信号A和B均为4位⽆符号型数据,其他均为默认值,点击OK。

稍后弹出的窗⼝,点击Generate。

⽣成的对话框直接点Ok。

综合选项中的Global表⽰只⽣成RTL代码,然后与整个⼯程⼀起参与综合,Out of context per IP表⽰⽣成后⽴即综合。

调⽤IP核选择IP Sources,展开并选择mult_gen_0 - Instantiation Template - mult_gen_0.veo,可以打开实例化模板⽂件。

如图,这段代码就是使⽤Verilog调⽤这个IP核的⽰例代码。

将⽰例代码复制到demo.v⽂件中,并进⾏修改,最终如下。

代码中声明了⽆符号型的4位变量a和b,分别赋初值7、8,作为乘数使⽤;⽆符号型的8位变量p,⽤于保存计算结果。

clk为Testbench编写的周期20ns的时钟信号;mult_gen_0 Mymult_gen_0 (...)语句实例化了mult_gen_0类型的模块对象Mymult_gen_0,并将clk、a、b、p作为参数传⼊。

vivado使用手册

Vivado是一款由Xilinx公司开发的集成开发环境(IDE),主要用于FPGA的设计和开发。

以下是Vivado的基本使用手册:

1. 打开Vivado软件,创建一个新工程:点击“Create New Project”,在弹出的界面上填写工程名并选择保存位置。

在选择工程类型时,选择RTL Project(一般为RTL工程)。

2. 在新工程中添加源文件:在新建的工程中,右键点击工程名,选择“Add Sources”来添加Verilog源文件。

在弹出的对话框中选择“OK”和“Yes”完成设计文件的新建。

3. 编写代码:在Sources文件夹中双击新建的设计文件,即可在右边的代码编辑区进行代码的编写。

4. 运行仿真:在编写完代码后,需要进行仿真测试。

在工程名上右键选择“New Run Block”,选择仿真语言为混合语言,然后点击“OK”。

在仿真界面中设置仿真参数,然后点击“Run”开始仿真。

5. 生成比特流:在仿真通过后,需要生成比特流文件以便将设计烧录到FPGA芯片中。

在工程名上右键选择“Generate Bitstream”,在弹出的界面中选择目标语言为Verilog,然后点击“OK”。

等待生成比特流文件的完成。

6. 下载到FPGA:将生成的比特流文件下载到FPGA芯片中进行实际测试。

可以使用Vivado提供的Tcl命令或者第三方工具进行下载。

以上是Vivado的基本使用流程,具体操作可能会根据不同的版本和实际需求有所不同。

建议参考Xilinx提供的官方文档和教程进行学习。

FPGA从串加载模式概述

1.FPGA从串加载模式概述基带板上采用的FPGA是Xilinx公司Virtex-II系列XC2V3000,其配置文件的下载模式有5种:主串模式(master serial)、从串模式(slave serial)、主并模式(master selectMAP)、从并模式(slave selectMAP)、JTAG模式。

其中,JTAG模式在开发调试阶段使用。

其余四种下载模式,可分为串行下载方式和并行下载方式。

串行下载方式和并行下载方式都有主、从2种模式。

主、从模式的最大区别在于:主模式的下载同步时钟(CCLK)由FPGA提供;从模式的下载同步时钟(CCLK)由外部时钟源或者外部控制信号提供。

主模式对下载时序的要求比从模式严格得多。

因此从处理机易于控制下载过程的角度,一般选择使用从串模式或从并模式。

本设计采用从串模式进行FPGA配置,可以使实现相对简单,并且能够减少占用MPC8260的资源。

在从串模式下,进行FPGA程序加载仅需要使用五个信号引脚,此外还需要设置M[2:0]信号以选择配置模式。

所使用引脚的详细描述见下表2.从串模式下载时序和过程从串模式的配置过程将配置比特流载入到FPGA,有四个主要阶段:清除配置内存初始化载入配置数据设备启动1.上电:The V CCINT power pins must be supplied with a 1.5 V source. (Refer to the Virtex-II DataSheet for DC characteristics.) The IOB voltage input for Bank 4 (V CCO_4) and the auxiliaryvoltage input (V CCAUX) are also used as a logic input to the Power-On-Reset (POR)circuitry. Even if this bank is not being used, V CCO_4 must be connected to a 1.5 V or greater source.2.清除配置内存在内存清除阶段,非配置I/O管脚为带有可选上拉电阻的三态。

VIVADO下ILA使用指南

VIVADO下ILA使用指南1000字VIVADO(Vivado Integrated Development Environment)是Xilinx公司推出的一种集成化开发环境,它可以帮助工程师更快地开发、测试和部署FPGA设计。

ILA(Integrated Logic Analyzer)是Vivado中的一个调试工具,可以用于验证设计中的逻辑。

本文将针对Vivado中的ILA工具的使用方法进行详细介绍。

一、创建ILA核1. 在Vivado的工具栏中,选择“打开系统”并打开设计文件。

2. 打开工具栏的“IP目录管理器”,然后单击“添加IP”按钮。

3. 在“添加或创建IP”的弹出窗口中,选择“创建新的IP”。

4. 在“创建新IP”的弹出窗口中,输入IP名称、IP版本和分类。

5. 单击“下一步”按钮,在“IP的核选项”窗口中选择“可编辑的调试核”,然后单击“下一步”。

6. 在“IP的端口和接口”窗口中设定输入和输出端口的名称、宽度和方向。

7. 单击“下一步”,输入IP的注册信息,然后单击“完成”按钮。

8. 完成后,Vivado会在当前设计项目的IP目录中生成新的ILA核。

二、添加到设计中1. 在源代码窗口右键单击需要添加ILA的模块,选择“加入调试核”。

2. 在“ILAv1_0”核的实例化窗口中,输入该模块的名称和实例化名称,然后单击“完成”。

3. 完成后,Vivado会为模块实例自动添加模块实例的ILAv1_0模块。

三、设置ILA1. 单击 ILA 组件名,在组件配置窗口中配置以下参数:2. Trigger port:避免浪费显示缓存器的空间。

3. Trigger阈值:指定何时开始捕获跟踪信息。

4. Capture Mode:捕获模式分为“单次”和“连续”。

5. Trigger Condition:触发条件定义为何时捕获跟踪信息。

6. Probe列表:这是将要跟踪的变量列表。

四、生成bit文件1. 选择“生成精简综合设计”。

vivado implementation策略

Vivado Implementation 策略Vivado 是由赛灵思公司(Xilinx)推出的一款集成电路开发工具,专门用于 FPGA/CPLD 的设计、仿真、调试和实现。

Vivado Implementation 策略指的是在使用 Vivado 进行 FPGA 设计时,针对不同的项目需求和目标硬件评台,制定合适的实现策略,以优化设计的性能、功耗和资源利用率。

下面我们来探讨一些常见的 Vivado Implementation 策略。

一、时序约束优化在 FPGA 设计中,时序约束的准确性对于设计的性能至关重要。

通过合理地设置时序约束,可以确保设计在目标时钟频率下能够正常工作,并且最大化地利用 FPGA 资源。

时序约束还可以帮助 Vivado 在实现过程中更好地优化逻辑综合和布局布线,进而提高设计的时序稳定性和抗干扰能力。

在进行 Vivado Implementation 时,需要仔细分析设计中的关键路径,准确设置时序约束,并根据需要进行时序优化,以达到设计的性能指标。

二、资源利用率优化在 FPGA 设计中,资源利用率优化是指在实现过程中最大化地利用FPGA 提供的逻辑单元、存储单元和 DSP 资源,以及减少设计对资源的竞争和冲突。

为此,在进行 Vivado Implementation 时,可以采取一些策略来优化资源利用率,例如合并逻辑、减少冗余逻辑、优化存储器结构、合理分配 DSP 资源等。

通过合理的资源利用率优化,可以有效降低设计的成本和功耗,提高设计的可靠性和稳定性。

三、功耗优化随着移动设备、物联网、人工智能等应用的不断发展,对于 FPGA 设计的功耗要求也越来越高。

在 Vivado Implementation 过程中,需要采取一些策略来优化设计的功耗。

可以通过减少逻辑单元、优化时钟管理、采用低功耗 IP 核等方式来降低设计的功耗。

还可以利用Vivado 提供的功耗分析工具来评估设计的功耗情况,进一步优化设计的功耗性能。

vivado仿真库编译

vivado仿真库编译Vivado是一种常用的FPGA设计工具,它提供了丰富的库资源,可以用于仿真和编译。

本文将介绍如何使用Vivado仿真库进行编译。

我们需要了解Vivado仿真库的基本概念和用途。

Vivado仿真库是一组预先编译好的模块和函数,用于在仿真环境中模拟FPGA设计的功能和行为。

它们提供了各种常用的功能模块,如时钟生成器、计数器、存储器等,以及各种常用的函数库,如数学函数、字符串处理函数等。

使用这些库可以方便地构建和测试FPGA设计。

在Vivado中,编译仿真库非常简单。

首先,我们需要打开Vivado 软件,并创建一个新的工程。

然后,在工程导航器中选择“仿真”选项,并打开仿真设置。

在仿真设置中,我们可以选择要使用的库文件,并将其添加到工程中。

Vivado提供了许多不同类型的仿真库,包括VHDL库、Verilog库、IP库等。

我们可以根据需要选择适合的库文件。

例如,如果我们使用VHDL语言进行设计,就可以选择VHDL库文件。

同样,如果我们使用Verilog语言进行设计,就可以选择Verilog库文件。

此外,Vivado还提供了许多常用的IP库,如AXI接口库、DDR存储器库等,可以方便地在设计中使用。

在选择库文件后,我们需要将其添加到工程中。

在Vivado的工程导航器中,右键单击“仿真”选项,并选择“添加仿真库”。

然后,我们可以选择要添加的库文件,并将其导入到工程中。

导入后,Vivado会自动将库文件编译为仿真模型,并将其添加到仿真库中。

一旦库文件添加到工程中,我们就可以在设计中使用这些库了。

例如,如果我们需要使用时钟生成器模块,可以在设计中实例化该模块,并通过仿真库调用其功能。

类似地,如果我们需要使用数学函数库,可以在设计中引用该库,并调用其中的函数。

编译仿真库后,我们可以使用Vivado的仿真工具进行测试。

首先,我们需要创建一个仿真测试台,并将设计和仿真库添加到该测试台中。

然后,我们可以设置仿真参数,并运行仿真。

[Xilinx]Modelsim独立仿真Vivado生成的PLL核

![[Xilinx]Modelsim独立仿真Vivado生成的PLL核](https://img.taocdn.com/s3/m/c59eb1c4b04e852458fb770bf78a6529647d350d.png)

--

Vivado更为便捷的是直接提供GUI按钮来一键编译Modelsim仿真所需的库(当然,并非所有都编译)。

-----------------------------------------------------------------------------------

喜欢使用Modelsim工具独立进行代码的仿真。也不是Vivado自带的不好(至少目前的小代码没啥影响)

只是在一个vivado工程进行仿真时,添加文件的功能没用太明白,好烦!

--

大前提:和Altera一样,也是需要先将底层的模块编译为库。这个步骤其实是一劳永逸。编译一次,以后

仿真用到时,只需添加使用到的编译库的目录即可,节省时间成本。

EDA Tools: 1、Vivado 2015.1(64-bit) 2、Modelsim SE-64 10.1c

[Xilinx]Modelsim独立仿真 Vivado生成的 PLL核

Time:

2016.05.26

-------------------------------------------------------

试验过程:

1、最开始tb里面是没有第18行的。

然后,源码添加tb.v、pll_name.v和pll_name_clk_wiz.v这三个模块。

这时,会提示pll_name_clk_wiz模块里面例化到的一些底层模块找不到。

具体是:

Instantiation of 'PLLE2_ADV' failed.

接着,再切换到Design标签,展开work,选择tb(最顶层模块),然后选择ok。 3、但发现还是有问题!截图如下:

Xilinx Vivado zynq7000 入门笔记

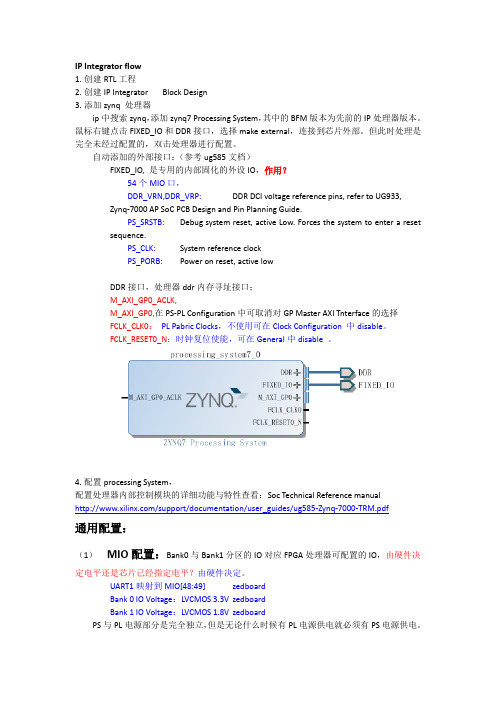

IP Integrator flow1.创建RTL工程2.创建IP Integrator Block Design3.添加zynq 处理器ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FIXED_IO, 是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide.PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence.PS_CLK: System reference clockPS_PORB: Power on reset, active lowDDR接口,处理器ddr内存寻址接口;M_AXI_GP0_ACLK,M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择FCLK_CLK0:PL Pabric Clocks,不使用可在Clock Configuration 中disable。

FCLK_RESET0_N:时钟复位使能,可在General中disable 。

4.配置processing System,配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

Vivado使用误区与进阶

我一直在问我自己到底有没有一种简便的方法能够让更多V i v a d o的用户从我们的新技术新产品中受益,从而帮助他们更好更快地完成自己的设计?A d v a n c e d D e s i g n T i p s作者:A l l y Z h o u,X i l i n x 工具与方法学应用专家Vivado UltraFAST 想到要写这一系列关于工具和方法学的小文章是在半年多前,那时候Vivado ®已经推出两年,陆续也接触了不少客户和他们的设计。

我所在的部门叫做“Tools & Methodology Applications ”,其实也是专为Vivado 而设的一个部门,从Vivado 的早期计划开始,我和我的同事们就投入到了Xilinx ©和Vivado 的客户们的推广和支持中,我们给客户做培训,在市场活动上做报告,培训和考核代理商,也去现场支持客户的设计。

两年的时间,Vivado 不断成熟,客户们也从最初的焦虑抗拒到全面接受,但随着与用户更深层次的技术交流。

接触了一些客户的设计后,我渐渐发现其实很多Vivado 的用户并没有真正了解它的好处,或者说,要么不够深入,要么就是有很多认识的偏差。

也许是语言的限制,也许是对各种各样动辄上百页的PDF 文档的无所适从,我能感觉到他们需要一些更直接,更有针对性的指引。

我一直在问我自己,到底有没有一种简便的方法,能够让更多Vivado 的用户从我们的新技术新产品中受益,从而帮助他们更好更快地完成自己的设计? 下定决心后,我便开始从日常工作和大家的反馈中寻找普遍感兴趣的话题,分门别类、挑选实例、尽量用简洁明快的文字和一目了然的插图叙事,把一篇文章控制在十页以内。

阅读这样一篇文章也许只需要你一顿午饭的时间,当你碰到一个技术问题,可以快速用关键字索引到对应的文章。

作为工程师,应该比较欢迎这样的小文章吧。

在此要特别感谢我的很多同事,这些文章中的不少实例和配图就是从他们创建的PPT 中挑选的,我能做的就是把更多Xilinx 技术专家们的经验之谈用大家熟悉的语言传播出去,传递下去。

Vivado教程之Vivado的对比不同Design Runs功能

ቤተ መጻሕፍቲ ባይዱ

有时我们需要对比不同情形下的各类报告,以侦测这些“不同”对设计的影 响。所谓的“不同情形”通常有以下几类: -RTL 代码不同 -约束不同 -综合策略不同 -实现策略不同 对比的报告可能包括: -log 文件

查看不同。一旦选择了比较内容,就会显示出两个比较文件之间的差异, 以高亮部分显示,如图 3 所示。 图3 结论 Vivado 提供了对比不同 Design Runs 生成的各种报告的功能,可方便用户 查看其中的差异,明确这些差异对设计造成的影响。

在 Vivado 2018.2 版本中,可通过如下几个步骤实现“对比”。 1 选择需要比较的两个 Runs,点击右键,选择 Diff Selected Runs Report。 这里只能选择两个,多了无法对比。Runs 可以是综合,可以是实现,但两者 必须是同一类型。换言之,如果一个 Run 是综合,另一个 Run 是实现,这种 情形是不支持的。如图 1 所示。 图1 2 选择比较的内容。如图 2 所示,以 Route Design 为例,可比较的选项既包 括 log 文件,也包括时序报告、资源利用率报告等。 图2 3

-资源利用率报告 -时序报告 -UFDM 报告 -Control Set 报告 -布线状态报告 -功耗报告 一旦涉及到“对比”就要用到一些工具,例如 Beyondcompare,但这个工具 不是开源的;或者 vimdiff,这个是开源的,但是脱离了 Vivado,需要首先打 开 vim,再通过 vimdiff 命令加载待比较的两个文件。这就要求工程师对 vim 有一定的了解。好在 Vivado 提供了这个功能。

FPGAxilinx开发环境Vivado介绍

FPGAxilinx开发环境Vivado介绍Zynq7000中PS和PL进⾏协同⼯作,其性能架构需要更好的开发⼯具和⼿段。

为提⾼设计效率,简化设计流程,Xilinx推出了以知识产权((Intellectual Property,IP)和系统为中⼼的Vivado设计套件[25-27]。

该套件包括硬件平台设计和开发⼯具Vivado IDE(Vivado Itegrated Development),嵌⼊式开发⼯具Xilinx SDK(Software Development Kit)以及⾼层次综合Vivado HLS(High-Level Synthesis)。

为更好的理解基于Zynq7000的软硬件协同设计流程,⾸先对上述开发⼯具进⾏介绍:(1)Vivado IDE:Vivado IDE将寄存器传输级(Register-Transfer Level,RTL)的电路设计和基于IP核的系统级设计集成在⼀个设计环境中,并且提供了IP集成器和IP封装器等⾼效的设计⼯具,⽤户可以直接调⽤套件提供的IP核,也可以根据⾃⾝需求编写RTL代码,利⽤IP封装器封装后直接例化使⽤。

为⽅便⽤户设计,Vivado IDE⽀持MicroBlaze软处理器的总线接⼝和IP端⼝⾃动连接,编译综合后可直接⽣成PS配置⽂件和PL⽐特流⽂件。

(2)Xilinx SDK:SDK是基于Eclipse平台开发的软件设计⼯具,⽀持Zynq7000系列器件。

SDK⽀持C或C++语⾔,为所有IP核提供驱动程序。

并且SDK内部配备各种软件调试⼯具,⽀持断点设置、单步调试以及内存监控等功能,可以与Vivado IDE内部的集成逻辑分析仪(Integrated Logic Analyzer,ILA)协同调试,提⾼了软硬件协同处理系统的设计效率。

(3)Vivado HLS:Vivado HLS是⼀种算法级的设计⼯具,⽀持C或C++等⾼级编程语⾔。

该⼯具可将实现算法的⾼级编程语⾔转化为RTL 级硬件电路。

vivado中各个资源模块的意思

vivado中各个资源模块的意思Vivado是Xilinx公司推出的一款集成设计环境,广泛应用于数字信号处理、数字逻辑设计等领域。

在使用Vivado进行FPGA设计时,了解各个资源模块的含义对于高效利用FPGA内部资源具有重要意义。

本文将详细介绍Vivado中各个资源模块的意思,帮助您更好地进行FPGA设计。

一、逻辑资源模块1.LUT(查找表):LUT是FPGA中基本的逻辑资源,可以用来实现组合逻辑或时序逻辑。

在Vivado中,LUT可以配置为不同大小的查找表,如6输入LUT、5输入LUT等。

2.FF(触发器):触发器是实现时序逻辑的基本单元。

在Vivado中,触发器可以配置为D触发器、T触发器等。

3.Carry Chain(进位链):进位链用于实现算术逻辑单元(ALU)中的加法器、减法器等。

在Vivado中,进位链可以提高运算速度和资源利用率。

二、存储资源模块1.Block RAM(块RAM):块RAM是FPGA中的存储资源,可用于实现数据存储、缓存等功能。

Vivado支持不同大小的块RAM配置,如18K、36K 等。

2.Distributed RAM(分布式RAM):分布式RAM是一种较小的存储资源,可用于实现小型缓存、寄存器等功能。

与块RAM相比,分布式RAM的访问速度更快,但容量较小。

三、数字信号处理资源模块1.DSP48(数字信号处理单元):DSP48是FPGA中用于实现数字信号处理功能的资源。

在Vivado中,DSP48可以配置为乘法器、累加器、滤波器等。

2.FFT(快速傅里叶变换):FFT是数字信号处理中常用的算法,Vivado提供了FFT IP核,方便用户在FPGA上实现高速的FFT运算。

四、时钟资源模块1.PLL(锁相环):锁相环是FPGA中的时钟管理资源,用于生成、分频、倍频等时钟信号。

Vivado提供了丰富的PLL IP核,以满足不同设计需求。

2.MMCM(混合模式时钟管理):MMCM是FPGA中的一种高级时钟管理资源,具有更低的相位噪声和更高的频率稳定性。

直击关于Xilinx UltraScale架构、Virtex和Kintex UltraScale架构

直击关于Xilinx UltraScale架构、Virtex和Kintex UltraScale架构FPGA 和最新的Vivado开发工具的9大要点Steve Leibson, 赛灵思战略营销与业务规划总监上周出版的最新一期的Xcell Journal杂志中刊载了由Nick Mehta主笔的一篇文章(“Productivity Skyrockets with Xilinx’s UltraScale Architecture”)(Xilinx UltraScale 架构能够快速提升生产力),下面是我们从Metha的文章中提取出了关于Virtex和Kintex UltraScale架构的FPGA 和Vivado开发工具的一些主要的看点:基于UltraScale架构的FPGA实现数据传输机制是通过将高性能的并行专用IO接口和高速的串行收发器结合起来实现的,UltraScale架构的串行收发器传送数据的速率能够达到16.3Gbps,满足主流的串行协议要求,当然传输速率也能够达到32.75Gbps,允许25G+比特位的地板设计,而且相对以前的收发器而言,能够大大降低每比特位传输的功耗。

UltraScale架构的FPGA芯片中的收发器都兼容PCIe3.0和PCIe4.0,专用的PCIe集成模块支持PCIe3.0 X8型端口和根端口的设计需求。

UltraScale架构包含了功能强大的可重配置时钟管理电路,主要包括时钟综合,缓存模块和布局组件,共同协作组成了高性能的时钟框架,能够满足各种设计的要求。

这个时钟网络允许在FPGA内部灵活的对时钟信号进行布局布线,来降低时钟偏差、功耗和延迟,将时钟信号的传输误差降到最小。

与以往的FPGA相比,UltraScale架构的FPGA中的时钟分割和门控间隔技术能够提供对时钟功耗的额外控制。

如今的FPGA结构包含很多组件,例如可配置逻辑块(CLB),CLB中又包含六输入查找表(LUTS)和触发器;带有27x18乘法器的DSP;36Kbit的块RAM存储单元,支持内置FIFO和ECC。

vivado参数定义 -回复

vivado参数定义-回复“vivado参数定义”是指在Xilinx Vivado设计套件中,用来配置和控制FPGA设计流程的一系列参数。

这些参数可以帮助设计工程师在设计过程中灵活地调整设置,以满足特定的设计需求。

本文将逐步回答有关vivado 参数定义的问题,帮助读者更好地理解和应用这些参数。

第一步:什么是Vivado及其作用?Vivado是Xilinx公司的一款综合性的FPGA设计套件,旨在帮助设计工程师在FPGA设计过程中实现高效、高质量的设计。

Vivado提供了一系列的工具、选项和参数,以支持从设计到验证的所有步骤。

第二步:为什么需要配置Vivado参数?在进行FPGA设计时,需要根据项目的具体要求来配置Vivado参数。

这些参数包括延迟、功耗、资源利用率等方面的设置,可以对设计结果产生很大的影响。

合理配置这些参数可以帮助设计工程师优化设计,提高性能,并且确保设计满足规格要求。

第三步:Vivado中常见的参数有哪些?Vivado中有很多可配置的参数,以下是一些常见的参数:1. 目标设备类型:可以选择目标FPGA的具体型号,以便Vivado能够根据该型号的资源和特性进行优化。

2. 约束文件:约束文件用于指定设计的限制条件,如时钟频率、接口协议等。

在这个参数中,可以指定约束文件的路径和文件名。

3. 合成策略:合成的目标是将综合代码转换为逻辑网表。

Vivado提供了多种合成策略,例如面向速度优化、面向面积优化或平衡。

根据设计需求,可以选择不同的合成策略以满足性能或资源利用率的要求。

4. 实现策略:实现的目标是将逻辑网表映射到目标FPGA设备的查找表、寄存器和其他资源上。

Vivado提供了不同的实现策略,例如智能引导实现、区域推导等。

5. 时序约束设置:时序约束用于确保设计在时钟频率、数据传输时序等方面满足要求。

Vivado中可以设置时钟频率、同步类型、时序约束文件等相关参数。

6. 物理优化配置:Vivado还提供了一系列用于优化布局和布线的参数。

玩转Vivado之Simulation

玩转Vivado之Simulation特权同学,版权所有1. 可用于Testbench分类管理的Simulation Sets关于Simulation的文件管理,ISE和Vivado的视窗大同小异。

ISE可以添加多个不同的testbench文件,也可以自动识别和被测试源文件的层次关系,如图1所示。

图1 ISE中testbench文件管理Vivado中对于testbench的管理,增加了一个sets的概念,类似不同的文件夹,如同图2中的sim_1和sim_2,这对于管理不同的testbench,如行为仿真用一个testbench、时序仿真用一个testbench,或者不同的子模块都需要分别由各自的testbench,分类管理更一目了然。

图2 Vivado中testbench文件管理2. Vivado自带的Simulation/Simulator工具与Altera索性放弃自己的内置simulation工具转而直接与Modelsim合作推出Altera-Modelsim作为首选的第三方仿真工具不同,Xilinx还在用心的维护着自己的simulation (Simulator)工具,虽然从感受上看,有Modelsim的影子,但还是略显“单薄”了,做些入门实验或简单的逻辑功能还凑合,稍微复杂些的应用用它simulation可能就难以招架了。

当然,既然如此,Xilinx为什么还要留着这个“鸡肋”,恐怕有他自己的考虑,咱就不多加揣测了。

图3Vivado自带的Simulation/Simulator工具2. 第三方仿真工具支持关于第三方仿真工具的支持,官方ug中提到能够支持以下工具,但是实测Modelsim SE 也能够支持。

The following third-party tools are supported:• QuestaSim• ModelSim (PE and DE)• IES• VCS• Riviera PRO simulator (Aldec)使用Modelsim作为第三方仿真工具,设置也很简单,基本上3步搞定,即设置Modelsim 路径、设置Modelsim作为仿真工具、编译器件库。

vivado 仿真代码

vivado 仿真代码

对于Vivado仿真代码,通常是指使用Xilinx Vivado工具进行FPGA设计时的仿真部分代码。

在Vivado中,您可以使用Verilog 或VHDL等硬件描述语言编写代码来描述您的设计。

然后,您可以使用Vivado自带的仿真工具来验证您的设计是否按预期工作。

在编写Vivado仿真代码时,您需要考虑以下几个方面:

1. 模块化设计,将设计划分为多个模块,每个模块负责特定的功能。

这有助于提高代码的可重用性和可维护性。

2. 时序和组合逻辑,确保您的代码中包含正确的时序和组合逻辑,以确保设计在FPGA中正常工作。

3. 仿真测试台,编写仿真测试台来验证您的设计。

这包括编写测试向量以及检查仿真结果是否符合预期。

在Vivado中,您可以使用Vivado自带的仿真工具(如XSIM)来进行仿真。

您可以创建仿真配置文件,设置仿真时钟周期,添加仿真波形等。

此外,还可以利用Vivado中的IP集成来加速设计和仿真过程。

Vivado提供了丰富的IP核库,您可以直接使用这些IP核来构建您

的设计,并进行仿真验证。

总之,Vivado仿真代码是指使用Vivado工具进行FPGA设计时

的仿真部分代码,编写这部分代码需要考虑模块化设计、时序和组

合逻辑以及仿真测试台等方面。

通过Vivado自带的仿真工具和IP

集成,您可以高效地进行设计验证和仿真。

xilinx Vivado工具使用技巧

xilinx Vivado工具使用技巧综合属性在Vivado Design Suite中,Vivado综合能够合成多种类型的属性。

在大多数情况下,这些属性具有相同的语法和相同的行为。

•如果Vivado综合支持该属性,它将使用该属性,并创建反映已使用属性的逻辑。

•如果工具无法识别指定的属性,则Vivado综合会将属性及其值传递给生成的网表。

1.ASYNC_REGASYNC_REG是影响Vivado工具流中许多进程的属性。

此属性的目的是通知工具寄存器能够在D输入引脚中接收相对于源时钟的异步数据,或者该寄存器是同步链中的同步寄存器。

当遇到此属性时,Vivado综合会将其视为DONT_TOUCH属性,并在网表中向前推送ASYNC_REG属性。

此过程可确保具有ASYNC_REG属性的对象未进行优化,并且流程中稍后的工具会接收属性以正确处理它。

您可以将此属性放在任何寄存器上; 值为FALSE(默认值)和TRUE。

可以在RTL或XDC 中设置此属性。

ASYNC_REG Verilog Example:(*ASYNC_REG = “TRUE”*) reg [2:0] sync_regs;2.CLOCK_BUFFER_TYPE在输入时钟上应用CLOCK_BUFFER_TYPE以描述要使用的时钟缓冲器类型。

默认情况下,Vivado综合使用BUFG作为时钟缓冲器。

支持的值是“BUFG”,“BUFH”,“BUFIO”,“BUFMR”,“BUFR”或“无”。

CLOCK_BUFFER_TYPE属性可以放在任何顶级时钟端口上。

它可以在RTL和XDC中设置。

CLOCK_BUFFER_TYPE Verilog Example(* clock_buffer_type = “none”*) input clk1;CLOCK_BUFFER_TYPE XDC Example。

xilinxvivado的五种仿真模式和区别

xilinxvivado的五种仿真模式和区别

xilinx vivado的五种仿真模式和区别

本文介绍一下xilinx的开发软件vivado 的仿真模式,vivado的仿真暂分为五种仿真模式。

分别为:

1. run behavioral simulaTIon-----行为级仿真,行为级别的仿真通常也说功能仿真。

2. post-synthesis funcTIon simulaTIon-----综合后的功能仿真。

3. post-synthesis TIming simulation-----综合后带时序信息的仿真,综合后带时序信息的仿真比较接近于真实的时序。

4. post-implementation function simulation-----布线后的功能仿真。

5. post-implementation timing simulation-----(布局布线后的仿真)执行后的时序仿真,该仿真时最接近真实的时序波形。

下面小编来详细介绍一下不同仿真模式的区别。

让FPGA初学者头疼的各种仿真

学习FPGA,被它的各种仿真弄的晕头转向。

前仿真、后仿真、功能仿真、时序仿真、行为级仿真、RTL级仿真、综合后仿真、门级仿真、布局布线后仿真……好吧,反正我是晕了。

先说一下Quartus和Modelsim软件的仿真形式:Quartus ii的两种仿真:1、功能仿真2、时序仿真;Quartus ii调用Modelsim的两种仿真:1、RTL级仿真2、Gate-level仿真。

查阅了各种资料如下:资料一:1.当用quartus进行仿真时,分为功能仿真(al)和时序仿真(Timing)。

2.当用Modelsim-Altera时,分为功能仿真(RTL)、综合后仿真(post-synthesis)和布局布线仿真(Gate-level)。

其中,功能仿真又称为前仿真,布局布线仿真又称为后仿真。

注:此处的功能仿真(RTL)与1中的功能仿真(al)是不一样的,前者是HDL级仿真,后者是门级网表的功能仿真。

(1)当在quartus中调用Modelsim-Altera进行RTL仿真时(前提是在第三方仿真工具中选择Modelsim-Altera),步骤如下:a) 编写源文件和测试文件;b) Assignment->setting->simulation->不选中run gate leve simulation.....,选中nativelink->添加测试文件,填写文件名;c) start analysis&elabration;d) Tools->start RTL simulation;(2)综合后仿真一般不做。

(3)当在quartus中调用Modelsim-Altera进行Gate-level仿真时(前提是在第三方仿真工具中选择Modelsim-Altera),步骤如下:a) 编写源文件和测试文件;b)Assignment->setting->simulation->选中run gate leve simulation.....,选中nativelink->添加测试文件,填写文件名;c)全编译;评价:对于Assignment->setting->simulation->"run gate leve simulation automatically after comlilation"选不选中根本没必要说明,完全可以不用选中,需要在设置处把测试文件testbench添加就可以了(不添加的话到时候quartus调用出modelsim软件后需要手动添加编译,下面补充了)。

vivado布线参数

vivado布线参数

Vivado是Xilinx公司推出的一款集成化的FPGA设计软件,其中包含了布线功能。

在Vivado中,布线参数通常包括了一系列设置和选项,用于控制FPGA的布线过程以达到设计的性能、功耗和面积等要求。

以下是一些常见的Vivado布线参数:

1. 约束文件,约束文件是描述设计约束的文件,其中包括时序约束、布局约束等。

在Vivado中,可以通过约束文件来指定布线的一些参数,如时钟频率、时序要求等。

2. 布线策略,Vivado提供了多种布线策略,如快速布线、综合布线、时序驱动布线等。

不同的布线策略会影响到布线的速度和质量,设计者可以根据实际需求选择合适的布线策略。

3. 布线优化选项,Vivado中还提供了一些布线优化选项,如时序优化、布局优化、功耗优化等。

这些选项可以帮助设计者在布线过程中优化设计的性能和功耗。

4. 布线约束,除了约束文件外,Vivado还提供了一些布线约束选项,如布线分区约束、时序分组约束等。

这些约束可以帮助设

计者更精细地控制布线的过程。

5. 布线报告,Vivado会生成布线报告,其中包括了布线结果、时序分析、资源利用情况等信息。

设计者可以通过布线报告来评估

设计的性能和资源利用情况,从而调整布线参数以达到更好的设计

效果。

总的来说,Vivado的布线参数涵盖了约束文件、布线策略、布

线优化选项、布线约束和布线报告等方面,设计者可以通过合理设

置这些参数来控制和优化FPGA的布线过程,从而达到设计的性能和

功耗要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

器件库,对仿真器进行一些必要的配置,不然仿真器并不认识其中的底层元 件,无法进行仿真。Xilinx 公司的集成开发环境 ISE 中并不支持综合后仿 真,而是使用映射前门级仿真代替,对于 Xilinx 开发环境来说,这两个仿真 之间差异很小。 三、时序仿真 (后仿真) 在设计流程中的最后一个仿真是时序仿真。在设计布局布线完成以后可以 提供一个时序仿真模型,这种模型中也包括了器件的一些信息,同时还会提 供一个 SDF 时序标注文件(Standard Delay format Timing Anotation)。SDF 时 序标注最初使用在 Verilog 语言的设计中,现在 VHDL 语言的设计中也引用 了这个概念。对于一般的设计者来说并不需知道 SDF。 总结 行为级仿真时必须的,能够确保你所设计功能是正确的,综合后时序仿真 是有必要的,能够排除大部分的时序问题,至于后仿真,只能是解决疑难杂 症时再采取的大招,非常费时间,一般不建议做后仿真。

数字电路设计中一般包括 3 个大的阶段:源代码输入、综合和实现,而电 路仿真的切入点也基本与这些阶段相吻合,根据适用的设计阶段的不同仿真 可以分为 RTL 行为级仿真、综合后门级功能仿真和时序仿真。这种仿真轮廓 的模型不仅适合 FPGA/CPLD 设计,同样适合 IC 设计。 一、RTL 行为级仿真 在大部分设计中执行的第一个仿真将是 RTL 行为级仿真。这个阶段的仿 真可以用来检查代码中的语法错误以及代码行为的正确性,其中不包括延时 信息。如果没有实例化一些与器件相关的特殊底层元件的话,这个阶段的仿 真也可以做到与器件无关。因此在设计的初期阶段不使用特殊底层元件即可 以提高代码的可读性、可维护性,又可以提高仿真效率,且容易被重用。(绝 大部分设计人员将这个阶段的仿真叫功能仿真!) 二、综合后门级功能仿真 (前仿真) 一般在设计流程中的第二个仿真是综合后门级功能仿真。绝大多数的综合 工具除了可以输出一个标准网表文件以外,还可以输出 Verilog 或者 VHDL 网表,其中标准网表文件是用来在各个工具之间传递设计数据的,并不能用 来做仿真使用,而输出的 Verilog 或者 VHDL 网表可以用来仿真,之所以叫 门级仿真是因为综合工具给出的仿真网表已经是与生产厂家的器件的底层元 件模型对应起来了,所以为了进行综合后仿真必须在仿真过程中加入厂家的