试验二16位算术逻辑运算试验

实验二运算器实验解读

实验⼆运算器实验解读实验⼆运算器实验1.算术逻辑运算实验⼀.实验⽬的1.了解简单运算器的数据传输通路。

2.验证运算功能发⽣器的组合功能。

3.掌握算术逻辑运算加、减、与的⼯作原理。

4.验证实验台运算的8位加、减、与、直通功能。

5.按给定数据,完成⼏种指定的算术和逻辑运算。

⼆.实验内容1.实验原理算术逻辑单元ALU的数据通路如图2-1所⽰。

其中运算器ALU181根据74LS181的功能⽤VHDL硬件描述语⾔编辑⽽成,构成8位字长的ALU。

参加运算的两个8位数据分别为A[7..0]和B[7..0],运算模式由S[3..0]的16种组合决定,⽽S[3..0]的值由4位2进制计数器LPM_COUNTER产⽣,计数时钟是Sclk(图2-1;此外,设M=0,选择算术运算,M=1为逻辑运算,C N为低位的进位位;F[7..0]为输出结果,C O 为运算后的输出进位位。

两个8位数据由总线IN[7..0]分别通过两个电平锁存器74373锁⼊,ALU功能如表2-1所⽰。

表2-1 ALU181的运算功能注1、* 表⽰每⼀位都移⾄下⼀更⾼有效位, “+”是逻辑或,“加”是算术加注2、在借位减法表达上,表2-1与标准的74181的真值表略有不同。

三.实验步骤(1设计ALU元件在Quartus II 环境下,⽤⽂本输⼊编辑器Text Editor输⼊ALU181.VHD算术逻辑单元⽂件,编译VHDL⽂件,并将ALU181.VHD⽂件制作成⼀个可调⽤的原理图元件。

(2以原理图⽅式建⽴顶层⽂件⼯程选择图形⽅式。

根据图2-1输⼊实验电路图,从Quartus II的基本元件库中将各元件调⼊图形编辑窗⼝、连线,添加输⼊输出引脚。

将所设计的图形⽂件ALU.bdf保存到原先建⽴的⽂件夹中,将当前⽂件设置成⼯程⽂件,以后的操作就都是对当前⼯程⽂件进⾏的。

(3器件选择选择Cyclone系列,在Devices中选择器件EP1C6QC240C8。

实验二 算术运算类操作实验 (基础与设计)

实验二算术运算类操作实验 (基础与设计)一、实验要求和目的1、了解汇编语言中的二进制、十六进制、十进制、BCD 码的表示形式;2、掌握各类运算类指令对各状态标志位的影响及测试方法;3、熟悉汇编语言二进制多字节加减法基本指令的使用方法;4、熟悉无符号数和有符号数乘法和除法指令的使用;5、掌握符号位扩展指令的使用。

6、掌握BCD 码调整指令的使用方法二、软硬件环境1、硬件环境:计算机系统 windows;2、软件环境:装有MASM、DEBUG、LINK、等应用程序。

三、实验涉及的主要知识本实验主要进行算术运算程序设计和调试,涉及到的知识点包括:1.加减法处理指令主要有加法指令ADD,带进位加法ADC,减法指令SUB,带进位减法指令SBB。

2.乘除法指令和符号位扩展指令主要有无符号数乘法指令MUL,带符号数乘法指令IMUL,无符号数除法指令DIV,带符号数除法指令IDIV,以及符号位从字节扩展到字的指令CBW 和从字扩展到双字的指令CWD。

3.BCD 码的调整指令主要有非压缩的BCD 码加法调整指令DAA,压缩的BCD 码减法调整指令DAS,非压缩的BCD 码加法调整指令AAA,非压缩的BCD 码减法调整指令AAS,乘法的非压缩BCD码调整指令AAM,除法的非压缩BCD 码调整指令AAD。

8088/8086 指令系统提供了实现加、减、乘、除运算的上述基本指令,可对下表所示的数据类型进行数据运算。

四、实验内容与步骤1、对于两组无符号数,087H 和034H,0C2H 和5FH,试编程求这两组数的和差积商,并考虑计算结果对标志寄存器中状态标志位的影响。

设计流程:源代码:DATAS SEGMENTARRAY DW 087H,034H,0C2H,05FHJIA DW 2 DUP(?) ;储存两组加法结果JIAN DW 2 DUP(?) ;储存两组减法结果CHENG DW 2 DUP(?) ;储存两组乘法结果CHU DW 2 DUP(?) ;储存两组除法结果DATAS ENDSSTACKS SEGMENTSTACKS ENDSCODES SEGMENTASSUME CS:CODES,DS:DATAS,SS:STACKSSTART:MOV AX,DATASMOV DS,AXMOV SI,0MOV BX,0SUB BX,2SUB SI,4L1:ADD SI,4ADD BX,2MOV AX,ARRAY[SI] ;第一个运算数ADD AX,ARRAY[SI+2] ;加法运算MOV JIA[BX],AX ;储存加法结果MOV AX,ARRAY[SI]SUB AX,ARRAY[SI+2] ;减法运算MOV JIAN[BX],AX ;储存减法结果MOV AX,ARRAY[SI]MUL ARRAY[SI+2] ;乘法运算MOV CHENG[BX],AX ;储存乘法结果MOV AX,ARRAY[SI]MOV CX,ARRAY[SI+2]DIV CL ;除法运算MOV CHU[BX],AX ;储存除法结果CMP BX,2JNZ L1MOV AH,4CHINT 21HCODES ENDSEND START程序结果:通过-t逐步运行程序,逐步查看每次运算后标志位的状态,结果如下:2、在数据段定义了两个多精度的有符号16 进制数,FIRST 和SECOND ,1)求两数的和与差,并将结果存放在THIRD 为首地址的缓冲区中;2)如果把两组数据当作十进制数据来处理,再次求两数的和与差,并将结果存放在FORTH 为首地址的缓冲区中。

ALU实验报告

算术逻辑单元实验报告一、实验目的1、掌握运算器的工作原理。

2、验证运算器的功能。

二、实验原理算术逻辑单元的主要功能是对二进制数据进行定点算术运算、逻辑运算和各种移位操作。

算术运算包括定点加减乘除运算;逻辑运算主要有逻辑与、逻辑或、逻辑异或和逻辑非操作。

ALU通常有两个数据输入端A和B,一个数据输出端Y 以及标志位等。

三、实验要求1、实验设计目标设计一个16位算术逻辑单元,满足以下要求。

(1)16位算术逻辑单元能够进行下列运算:加法、减法、加1、减1、与、或、非和传送。

用3位运算操作码OP[2..0]进行运算,控制方式如下表所示。

(2)设立两个标志寄存器Z和C。

当复位信号reset为低电平时,将这两个标志寄存器清零。

当运算结束后,在时钟clk的上升沿改变标志寄存器Z和C的值。

运算结果改变标志寄存器C、Z的情况如下:加法、减法、加1、减1运算改变Z、C;与、或、非运算改变Z,C保不变;传送操作保持Z、C不变。

因此在运算结束Z、C需要两个D触发器保存。

(3)为了保存操作数A和B,设计两个16位寄存器A和B。

当寄存器选择信号sel=0时,如果允许写信号write=1.,则在诗中clk的上升沿将数据输入dinput送入A 寄存器;当寄存器选择信号sel=1时,如果允许写信号write=1.,则在诗中clk的上升沿将数据输入dinput送入B寄存器。

(4)算术逻辑单元用一个设计实体完成。

2.顶层设计实体的引脚要求(1)clk对应试验台上的时钟(单脉冲)。

(2)reset对应实验台上的CPU复位信号CPU-RST。

(3)数据输入dinput对应试验台开关SD15~SD0。

(4)允许写信号write对应试验台开关SA5.(5)OP[2..0]对应试验台开关SA2~SA0.(6)寄存器选择信号sel对应试验台开关SA4.(7)16为运算结果result对应实验台上的指示灯A15~A0.(8)Z、C标志位对应试验台上的Z、C指示灯。

《计算机组成原理》学生实验报告

《计算机组成原理》学生实验报告(2011~2012学年第二学期)专业:信息管理与信息系统班级: A0922学号:10914030230姓名:李斌目录实验准备------------------------------------------------------------------------3 实验一运算器实验-----------------------------------------------------------7 实验二数据通路实验-------------------------------------------------------13 实验三微控制器实验--------------------------------------------------------18 实验四基本模型机的设计与实现------------------------------------------22实验准备一、DVCC实验机系统硬件设备1、运算器模块运算器由两片74LS181构成8位字长的ALU。

它是运算器的核心。

可以实现两个8位的二进制数进行多种算术或逻辑运算,具体由74181的功能控制条件M、CN、S3、S2、S1、S0来决定,见下表。

两个参与运算的数分别来自于暂存器U29和U30(采用8位锁存器),运算结果直接输出到输出缓冲器U33(采用74LS245,由ALUB信号控制,ALUB=0,表示U33开通,ALUB=1,表示U33不通,其输出呈高阻),由输出缓冲器发送到系统的数据总线上,以便进行移位操作或参加下一次运算。

进位输入信号来自于两个方面:其一对运算器74LS181的进位输出/CN+4进位倒相所得CN4;其二由移位寄存器74LS299的选择参数S0、S1、AQ0、AQ7决定所得。

触发器的输出QCY就是ALU结果的进位标志位。

QCY为“0”,表示ALU结果没有进位,相应的指示灯CY灭;QCY为“1”,表示ALU结果有进位,相应的指示灯CY点亮。

实验2 算术与逻辑运算指令实验

实验2 算术与逻辑运算指令实验一、实验目的1. 学习算术与逻辑运算的原理及指令的用法;2. 进一步学习emu8086调试程序的用法,并学会emu8086下编写简单应用程序的方法;3. 掌握BCD码加、减法以及ASCII码加减法。

二、实验内容1. 用emu8086执行各加减法指令以及不同编码方式的运算方法,记录执行结果,进行分析、比较,掌握各功能类似的指令之间的差别。

2. 用emu8086编写一个COM文件,其功能是检查自身的长度以及代码检查和。

如果自身的长度改变或检查和改变,则显示“VIRUS”,否则显示“OK”。

三、实验步骤(一) 加法、减法以及逻辑运算指令练习1. 启动emu8086;2. 用单步按钮命令调试以下程序段(分号后注释部分不用输入);-Axxxx:0100 XOR AX,AX ;AX= , C=____, Z=____xxxx:0102 MOV AX,89AB ;AX= , C=____, Z=____xxxx:0105 MOV BX,AX ;BX=xxxx:0107 INC AX ;AX= , C=____, Z=____xxxx:0108 DEC AX ;AX= , C=____, Z=____xxxx:0109 ADD AX,SI ;AX= , C=____, Z=____xxxx:010B SUB AX,SI ;AX= , C=____, Z=____xxxx:010D ADC AX,SI ;AX= , C=____, Z=____xxxx:010F SBB AX,SI ;AX= , C=____, Z=____xxxx:0111 NOPxxxx:0112 MOV AX,0808xxxx:0115 MOV BX,0080xxxx:0118 MOV CX,0880 ;CX=___________xxxx:011B OR AX,BX ;AX=___________ , C=____, OV=____xxxx:011D MOV AX,0808 ;AX=___________, BX=___________xxxx:0120 AND AX,CX ;AX=___________, C=____, S=____xxxx:0122 MOV AX,0808 ;AX=___________, CX=___________xxxx:0125 XOR AX,BX ;AX=___________, BX=___________xxxx:0127 NOT AX ;AX=___________xxxx:0129 NEG AX ;AX=___________xxxx:012B3. 分析上述程序段,用铅笔填写指令依次执行后寄存器和标志位的值,观察它们的变化。

16位超前进位加法器实验报告

实验名称:十六位超前进位加法器一、实验目的设计、验证并优化16位超前进位加法器的逻辑功能。

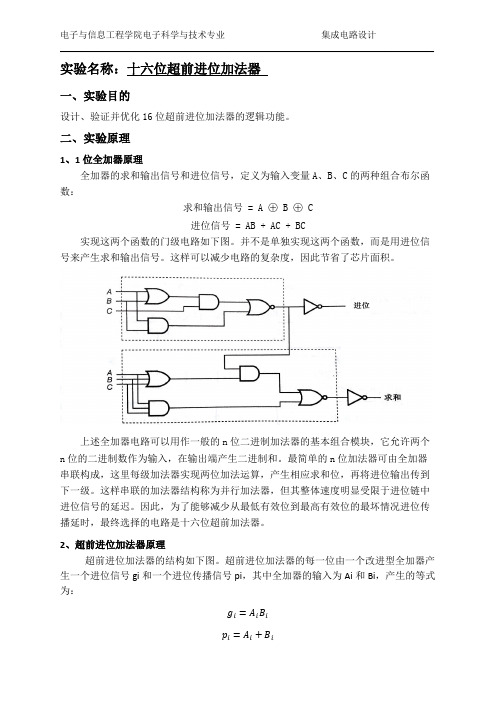

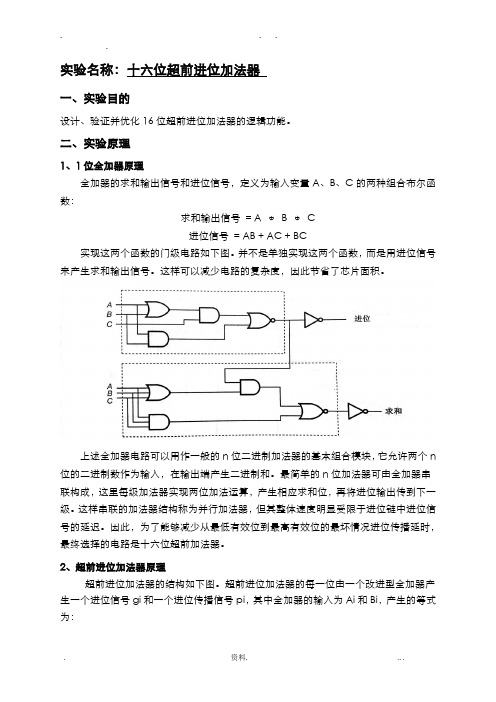

二、实验原理1、1位全加器原理全加器的求和输出信号和进位信号,定义为输入变量A、B、C的两种组合布尔函数:求和输出信号 = A ⊕ B ⊕ C进位信号 = AB + AC + BC实现这两个函数的门级电路如下图。

并不是单独实现这两个函数,而是用进位信号来产生求和输出信号。

这样可以减少电路的复杂度,因此节省了芯片面积。

上述全加器电路可以用作一般的n位二进制加法器的基本组合模块,它允许两个n 位的二进制数作为输入,在输出端产生二进制和。

最简单的n位加法器可由全加器串联构成,这里每级加法器实现两位加法运算,产生相应求和位,再将进位输出传到下一级。

这样串联的加法器结构称为并行加法器,但其整体速度明显受限于进位链中进位信号的延迟。

因此,为了能够减少从最低有效位到最高有效位的最坏情况进位传播延时,最终选择的电路是十六位超前加法器。

2、超前进位加法器原理超前进位加法器的结构如下图。

超前进位加法器的每一位由一个改进型全加器产生一个进位信号gi和一个进位传播信号pi,其中全加器的输入为Ai和Bi,产生的等式为:改进的全加器的进位输出可由一个进位信号和一个进位传输信号计算得出,因此进位信号可改写为:式中可以看出,当gi = 1(Ai = Bi = 1)时,产生进位;当pi = 1(Ai =1或Bi = 1)时,传输进位输入,这两种情况都使得进位输出是1。

近似可以得到i+2和i+3级的进位输出如下:下图为一个四位超前进位加法器的结构图。

信号经过pi和gi产生一级时延,经过计算C产生一级时延,则A,B输入一旦产生,首先经过两级时延算出第1轮进位值C’不过这个值是不正确的。

C’再次送入加法器,进行第2轮2级时延的计算,算出第2轮进位值C,这一次是正确的进位值。

这里的4个4位超前进位加法器仍是串行的,所以一次计算经过4级加法器,一级加法器有2级时延,因此1次计算一共经过8级时延,相比串行加法器里的16级时延,速度提高很多。

十六位运算器ALU实验报告

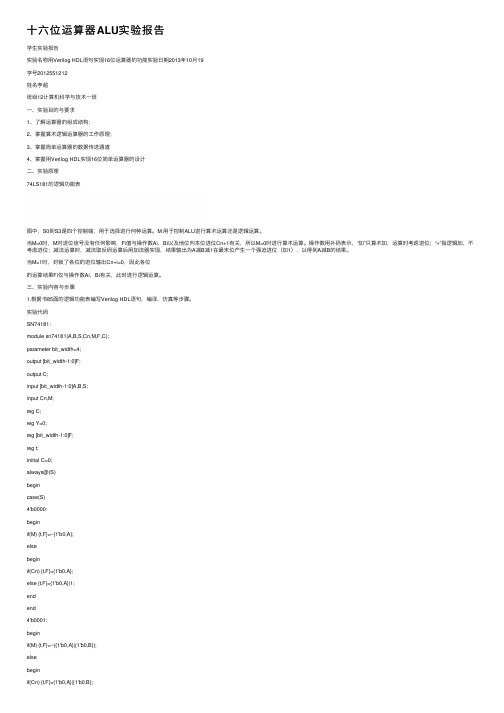

⼗六位运算器ALU实验报告学⽣实验报告实验名称⽤Verilog HDL语句实现16位运算器的功能实验⽇期2013年10⽉19学号2012551212姓名李超班级12计算机科学与技术⼀班⼀、实验⽬的与要求1、了解运算器的组成结构;2、掌握算术逻辑运算器的⼯作原理;3、掌握简单运算器的数据传送通道4、掌握⽤Verilog HDL实现16位简单运算器的设计⼆、实验原理74LS181的逻辑功能表图中,S0到S3是四个控制端,⽤于选择进⾏何种运算。

M ⽤于控制ALU进⾏算术运算还是逻辑运算。

当M=0时,M对进位信号没有任何影响,Fi值与操作数Ai,Bi以及地位向本位进位Cn+1有关,所以M=0时进⾏算术运算。

操作数⽤补码表⽰,“加”只算术加,运算时考虑进位;“+”指逻辑加,不考虑进位;减法运算时,减法取反码运算后⽤加法器实现,结果输出为A减B减1在最末位产⽣⼀个强迫进位(加1),以得到A减B的结果。

当M=1时,封锁了各位的进位输出Cn+i=0,因此各位的运算结果Fi仅与操作数Ai,Bi有关,此时进⾏逻辑运算。

三、实验内容与步骤1.根据书85⾯的逻辑功能表编写Verilog HDL语句,编译,仿真等步骤。

实验代码SN74181:module sn74181(A,B,S,Cn,M,F,C);parameter bit_width=4;output [bit_width-1:0]F;output C;input [bit_width-1:0]A,B,S;input Cn,M;reg C;reg Y=0;reg [bit_width-1:0]F;reg t;initial C=0;always@(S)begincase(S)4'b0000:beginif(M) {t,F}=~{1'b0,A};elsebeginif(Cn) {t,F}={1'b0,A};else {t,F}={1'b0,A}|1;endend4'b0001:beginif(M) {t,F}=~({1'b0,A}|{1'b0,B});endend4'b0010:beginif(M) {t,F}=~{1'b0,A}&{1'b0,B};elsebeginif(Cn) {t,F}={1'b0,A}|({1'b0,~B});else {t,F}=({1'b0,A}|({1'b0,~B}))+1;endend4'b0011:beginif(M) {t,F}=0;elsebeginif(Cn) {t,F}={t,F}-1;else {t,F}=0;endend4'b0100 :beginif(M) {t,F}=~({1'b0,A}&{1'b0,B});elsebeginif(Cn) {t,F}={1'b0,A}+({1'b0,A}&({1'b0,~B}));else {t,F}={1'b0,A}+({1'b0,A}&({1'b0,~B}))+1;endend4'b0101 :beginif(M) {t,F}={1'b0,~B};elsebeginif (Cn) {t,F}=({1'b0,A}&({1'b0,~B}))+({1'b0,A}|{1'b0,B}); else{t,F}=({1'b0,A}&({1'b0,~B}))+({1'b0,A}|{1'b0,B})+1; endend4'b0110 :beginif(M) {t,F}={1'b0,A}^{1'b0,B};elsebeginif(Cn) {t,F}={1'b0,A}-{1'b0,B}-1;else {t,F}={1'b0,A}-{1'b0,B};endend4'b0111 :beginelse {t,F}={1'b0,A}&({1'b0,~B});endend4'b1000 :beginif(M) {t,F}={1'b0,~A}|{1'b0,B};elsebeginif(Cn) {t,F}={1'b0,A}+({1'b0,A}&{1'b0,B});else {t,F}={1'b0,A}+({1'b0,A}&{1'b0,B})+1;end4'b1001 :beginif(M) {t,F}={1'b0,~(A^B)};elsebeginif(Cn) {t,F}={1'b0,A}+{1'b0,B}+1;else {t,F}={1'b0,A}+{1'b0,B};endend4'b1010 :beginif(M) {t,F}={1'b0,B};elsebeginif(Cn){t,F}=({1'b0,A}&{1'b0,B})+({1'b0,A}|({1'b0,~B})); else{t,F}=({1'b0,A}&{1'b0,B})+({1'b0,A}|({1'b0,~B}))+1; end4'b1011 :beginif(M) {t,F}={1'b0,A}&{1'b0,B};elsebeginif(Cn) {t,F}={1'b0,A}&{1'b0,B}-1;else {t,F}={1'b0,A}&{1'b0,B};endend4'b1100 :beginif(M) {t,F}=1;elsebeginif(Cn) {t,F}={1'b0,A}+{1'b0,A};else {t,F}={1'b0,A}+{1'b0,A}+1;endend4'b1101:beginelse {t,F}={1'b0,A}+({1'b0,A}|{1'b0,B})+1; endend4'b1110 :beginif(M) {t,F}={1'b0,A}|{1'b0,B};elsebeginif(Cn) {t,F}={1'b0,A}+({1'b0,A}|({1'b0,~B})); else {t,F}={1'b0,A}+({1'b0,A}|({1'b0,~B}))+1; endend4'b1111 :beginif(M) {t,F}={1'b0,A};elsebeginif(Cn) {t,F}={1'b0,A}-1;else {t,F}={1'b0,A};endendendcaseC=t;endEndmoduleSHIFT:module shift(A,choose,result); parameter bit_width=16;input [bit_width-1:0]A;input[1:0] choose;output [bit_width-1:0] result;reg [bit_width-1:0]result;always@(A or choose)begincase(choose)2'b01:beginresult=A<<1;end2'b10:beginresult={A[0],A[15:1]};end2'b11:beginresult=$signed(A)>>>1;endendcaseendEndmoduleinput [width-1:0] r;input [1:0]x;output [width-1:0] result; output overflow,z,c,p,n;reg [width-1:0] a,b;reg [3:0]s;reg [1:0]sh;reg cn,m,ov;wire co1,co2,co3;wire [width-1:0]co,re1,re2; always@ (x or r)begincase(x)2'b11: begina=r;end2'b10: beginb=r;end2'b00: begins=r[3:0];sh=r[5:4];m=r[8];cn=r[12]; endendcaseendsn74181 u_sn74181_1(.A(a[3:0]),.B(b[3:0]),.S(s),.M(m),.Cn(cn),.C(co1),.F(re1[3:0]));sn74181 u_sn74181_2 (.A(a[7:4]),.B(b[7:4]),.S(s),.M(m),.Cn(co1),.C(co2),.F(re1[7:4]));sn74181 u_sn74181_3 (.A(a[11:8]),.B(b[11:8]),.S(s),.M(m),.Cn(co2),.C(co3),.F(re1[11:8]).B(b[15:12]),.S(s),.M(m),.Cn(co3),.C(overflow),.F(re1[15:12]));shift u_shift(.A(a),.choose(sh),.result(re2[15:0]));assign result=(sh?re2:re1);assign z=~|result;assign n=result[15];Endmodule仿真波形图按照模式⼀电路图结构图设置对应的引脚参数。

实验二 算术逻辑运算及移位操作

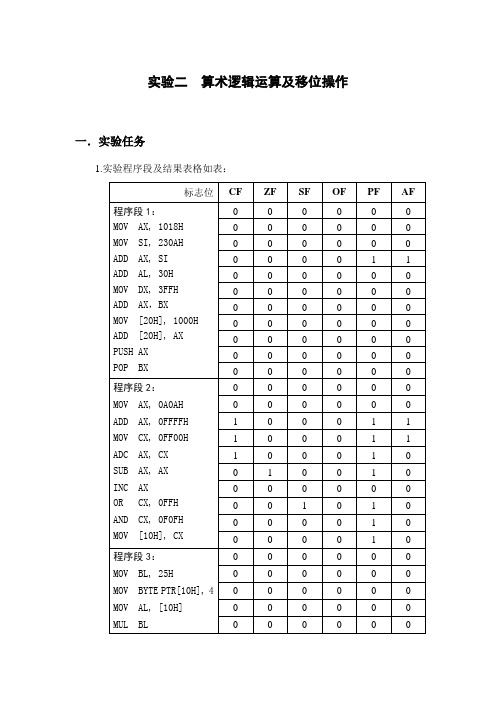

实验二算术逻辑运算及移位操作一.实验任务1.实验程序段及结果表格如表:分析:程序段1:MOV AX, 1018H ;AX←1018HMOV SI, 230AH ;SI←230AHADD AX, SI ;AX=3322H,低8位为00100010B,1的个数;为偶数,PF=1,同时D3向D4有进位发生,AF=1 ADD AL, 30H ;AX=3352H,低8位1个个数为奇数,PF=0 MOV DX, 3FFH ;DX←3FFHADD AX,BX ;AX=3352H,MOV [20H], 1000H ;[20H]←1000HADD [20H], AX ;[20H]=4352HPUSH AX ;POP BX ;BX=3352H程序段2:MOV AX, 0A0AH ;AX←0A0AHADD AX, 0FFFFH ;AX=0A09H,最高位进位CF=1,低8位1的;个数为偶数PF=1;D3向D4进位AF=1 MOV CX, 0FF00H ;CX←0FF00HADC AX, CX ;AX=090AH,最高位进位CF=1,低8位1的个;数为偶数PF=1SUB AX, AX ;AX=0,运算结果为零ZF=1INC AX ;AX=1HOR CX, 0FFH ;CX=0FFFFH,最高位为1,ZF=1,低8位1的;个数为偶数PF=1AND CX, 0F0FH ;CX=0F0FH,低8位1的个数为偶数PF=1MOV [10H], CX ;[10H]←0F0FH程序段3:MOV BL, 25H ;BL←25HMOV BYTE PTR[10H], 4 ;[10H]←04HMOV AL, [10H] ;AL←04HMUL BL ;AL=94H程序段4:MOV WORD PTR[10H],80H ;[10H]←0080HMOV BL, 4 ;BL←04HMOV AX, [10H] ;AX←0080HDIV BL ;AX=0020H程序段5:MOV AX, 0 ;AX←0000HDEC AX ;AX=0FFFFH,最高位为1,SF=1,低8;位1的个数为偶数PF=1,最高位向前、;D3向D4有借位,CF=1,AF=1 ADD AX, 3FFFH ;AX=3FFEH,D3向D4有进位,AF=1 ADD AX, AX ;AX=7FFCH,低8位1的个数为偶数,PF=1;D3向D4有进位,AF=1NOT AX ;AX=8003HSUB AX, 3 ;AX=8000H,低8位1的个数为偶数,PF=1;最高位为1,SF=1OR AX, 0FBFDH ;AX=0FBFDH,最高位为1,SF=1AND AX, 0AFCFH ;AX=0ABCDH,最高位为1,SF=1SHL AX,1 ;AX=579AH,低8位1的个数为偶数,PF=1,;算数结果溢出OF=1,最高位进位CF=1 RCL AX,1 ;AX=0AF35H,低8位1的个数为偶数,;PF=1,算数结果溢出OF=12.用BX寄存器作为地址指针,从BX所指的内存单元(0010H)开始连续存入三个无符号数(10H、04H、30H),接着计算内存单元中的这三个数之和,和放在0013H单元中,再求出这三个数之积,积放0014单元中。

基于CPLD的16位算术逻辑运算单元的设计

基于CPLD的16位算术逻辑运算单元的设计(EPM7128扩充选配类)一、实验目的1、掌握运算器的数据传输方式。

2、掌握74LS181的功能和应用。

3、学习并掌握利用CPLD器件通过原理图进行算术逻辑单元的设计。

二、实验要求1、完成16位不带进位位算术、逻辑运算实验。

按照实验步骤完成实验项目,了解算术逻辑运算单元的运行过程。

2、通过原理图配置EPM7128的内部电路结构,使其替代分离的算术逻辑运算单元的设计。

三、实验说明1、ALU单元实验构成(1)运算器由4片74LS181构成16位字长的ALU单元。

(2)4片74LS374作为2个数据锁存器(DR1、DR2),4片74LS244作为2个数据驱动器(DR1、DR2),两个8芯插座作为数据输入端,可通过长8芯扁平电缆,把数据输入端连接到二进制开关上。

运算器的数据输出由两片74LS244(输出缓冲器)来控制,两个8芯插座作为数据输出端,由开关控制显示16位输出结果。

可通过8芯扁平电缆线把数据输出端连接到微指令LED灯上。

图2-1-22、ALU单元的工作原理(如图2-1-2)数据输入锁存器DR1的EDR1为低电平,并且CLK有上升沿时,把来自数据总线的数据打入锁存器DR1。

同样使EDR2为低电平、CLK有上升沿时把数据总线上的数据打入数据锁存器DR2。

算术逻辑运算单元的核心是由4片74LS181组成,它可以进行2个16位二进制数的算术逻辑运算,74LS181的各种工作方式可通过设置其控制信号来实现(S0、S1、S2、S3、M、CN)。

当实验者正确设置了74LS181的各个控制信号,74LS181会运算数据锁存器DR1、DR2内的数据。

由于DR1、DR2已经把数据锁存,只要74LS181的控制信号不变,那么74LS181的输出数据也不会发生改变。

输出缓冲器采用两片74LS244,当控制信号ALU-O为低电平时,两片74LS244导通,把74LS181的运算低位结果输出到数据总线,并在微指令单元LED上显示。

实验二 算术运算实验

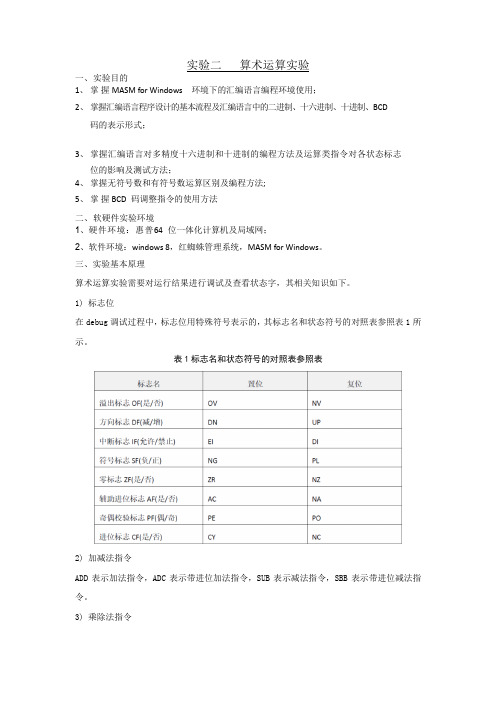

实验二算术运算实验一、实验目的1、掌握MASMforWindows环境下的汇编语言编程环境使用;2、掌握汇编语言程序设计的基本流程及汇编语言中的二进制、十六进制、十进制、BCD码的表示形式;3、掌握汇编语言对多精度十六进制和十进制的编程方法及运算类指令对各状态标志位的影响及测试方法;4、掌握无符号数和有符号数运算区别及编程方法;5、掌握BCD码调整指令的使用方法二、软硬件实验环境1、硬件环境:惠普64位一体化计算机及局域网;2、软件环境:windows8,红蜘蛛管理系统,MASMforWindows。

三、实验基本原理算术运算实验需要对运行结果进行调试及查看状态字,其相关知识如下。

1) 标志位在debug调试过程中,标志位用特殊符号表示的,其标志名和状态符号的对照表参照表1所示。

表1标志名和状态符号的对照表参照表2) 加减法指令ADD表示加法指令,ADC表示带进位加法指令,SUB表示减法指令,SBB表示带进位减法指令。

3) 乘除法指令MUL表示无符号数乘法指令,IMUL表示带符号数乘法指令,DIV表示无符号数除法指令,IDIV表示带符号数除法指令。

4) 符号位扩展指令CBW表示从字节扩展到字的指令,CWD表示从字扩展到双字的指令。

5) BCD码的调整指令在进行十进制加减运算时,需要将数据用BCD码表示,还要考虑到是组合BCD码还是非组合BCD码,组合BCD码是用一个字节表示两位十进制数,非组合BCD码是用一个字节表示一位十进制数,对于组合的BCD码加减法运算其结果存放在AL中。

组合的BCD码加法调整指令DAA;组合的BCD码减法调整指令DAS;非组合的BCD码加法调整指令AAA;非组合的BCD码减法调整指令AAS;乘法的非组合BCD码调整指令AAM;除法的非组合BCD码调整指令AAD。

8088/8086指令系统提供了实现加、减、乘、除运算指令,可参照表2所示内容。

表2数据类型的数据运算表四、实验步骤与内容1)对于表格中三组无符号数,试编程求这三组数的指定运算结果,并考虑计算结果对标志寄存器中状态标志位的影响:①实验分析本实验要求简单,仅对指定三组数进行基本运算。

16位超前进位加法器实验报告

实验名称:十六位超前进位加法器一、实验目的设计、验证并优化16位超前进位加法器的逻辑功能。

二、实验原理1、1位全加器原理全加器的求和输出信号和进位信号,定义为输入变量A、B、C的两种组合布尔函数:求和输出信号= A ⊕B ⊕C进位信号= AB + AC + BC实现这两个函数的门级电路如下图。

并不是单独实现这两个函数,而是用进位信号来产生求和输出信号。

这样可以减少电路的复杂度,因此节省了芯片面积。

上述全加器电路可以用作一般的n位二进制加法器的基本组合模块,它允许两个n 位的二进制数作为输入,在输出端产生二进制和。

最简单的n位加法器可由全加器串联构成,这里每级加法器实现两位加法运算,产生相应求和位,再将进位输出传到下一级。

这样串联的加法器结构称为并行加法器,但其整体速度明显受限于进位链中进位信号的延迟。

因此,为了能够减少从最低有效位到最高有效位的最坏情况进位传播延时,最终选择的电路是十六位超前加法器。

2、超前进位加法器原理超前进位加法器的结构如下图。

超前进位加法器的每一位由一个改进型全加器产生一个进位信号gi和一个进位传播信号pi,其中全加器的输入为Ai和Bi,产生的等式为:改进的全加器的进位输出可由一个进位信号和一个进位传输信号计算得出,因此进位信号可改写为:式中可以看出,当gi = 1(Ai = Bi = 1)时,产生进位;当pi = 1(Ai =1或Bi = 1)时,传输进位输入,这两种情况都使得进位输出是1。

近似可以得到i+2和i+3级的进位输出如下:下图为一个四位超前进位加法器的结构图。

信号经过pi和gi产生一级时延,经过计算C产生一级时延,则A,B输入一旦产生,首先经过两级时延算出第1轮进位值C’不过这个值是不正确的。

C’再次送入加法器,进行第2轮2级时延的计算,算出第2轮进位值C,这一次是正确的进位值。

这里的4个4位超前进位加法器仍是串行的,所以一次计算经过4级加法器,一级加法器有2级时延,因此1次计算一共经过8级时延,相比串行加法器里的16级时延,速度提高很多。

计算机组成原理实验二算术逻辑运算实验

实验二算术逻辑运算实验一、实验目的(1)了解运算器芯片(74LS181)的逻辑功能。

(2)掌握运算器数据的载入、读取方法,掌握运算器工作模式的设置。

(3)观察在不同工作模式下数据运算的规则。

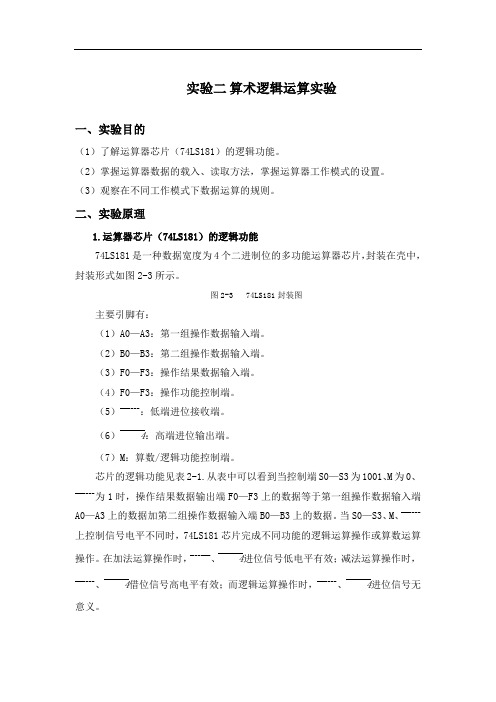

二、实验原理1.运算器芯片(74LS181)的逻辑功能74LS181是一种数据宽度为4个二进制位的多功能运算器芯片,封装在壳中,封装形式如图2-3所示。

图2-3 74LS181封装图主要引脚有:(1)A0—A3:第一组操作数据输入端。

(2)B0—B3:第二组操作数据输入端。

(3)F0—F3:操作结果数据输入端。

(4)F0—F3:操作功能控制端。

̅̅̅̅̅̅:低端进位接收端。

(5)CC(6)CC4:高端进位输出端。

(7)M:算数/逻辑功能控制端。

芯片的逻辑功能见表2-1.从表中可以看到当控制端S0—S3为1001、M为0、CC̅̅̅̅̅̅为1时,操作结果数据输出端F0—F3上的数据等于第一组操作数据输入端̅̅̅̅̅̅A0—A3上的数据加第二组操作数据输入端B0—B3上的数据。

当S0—S3、M、CC 上控制信号电平不同时,74LS181芯片完成不同功能的逻辑运算操作或算数运算̅̅̅̅̅̅、CC4进位信号低电平有效;减法运算操作时,操作。

在加法运算操作时,CCCC̅̅̅̅̅̅、CC4进位信号无̅̅̅̅̅̅、CC4借位信号高电平有效;而逻辑运算操作时,CC意义。

2.运算器实验逻辑电路试验台运算器实验逻辑电路中,两片74LS181芯片构成一个长度为8位的运算器,两片74LS181分别作为第一操作数据寄存器和第二操作数据寄存器,一片74LS254作为操作结果数据输出缓冲器,逻辑结构如图2-4所示。

途中算术运算操作时的进位Cy判别进位指示电路;判零Zi和零标志电路指示电路,将在实验三中使用。

第一操作数据由B-DA1(BUSTODATA1)负脉冲控制信号送入名为DA1的第一操作数据寄存器,第二操作数据由B-DA2(BUSTODATA2)负脉冲控制信号送入名为̅̅̅̅̅̅̅̅̅̅(ALUTOBUS)低DA2的第二操作数据寄存器。

实验二16位算术逻辑运算实验

实验三16位算术逻辑运算实验一、实验目的1、掌握16位运算器的数据传送通路组成原理。

2、进一步验证算术逻辑运算功能发生器74LS181的组合功能。

3、按要求和给出的数据完成几种指定的算术逻辑运算。

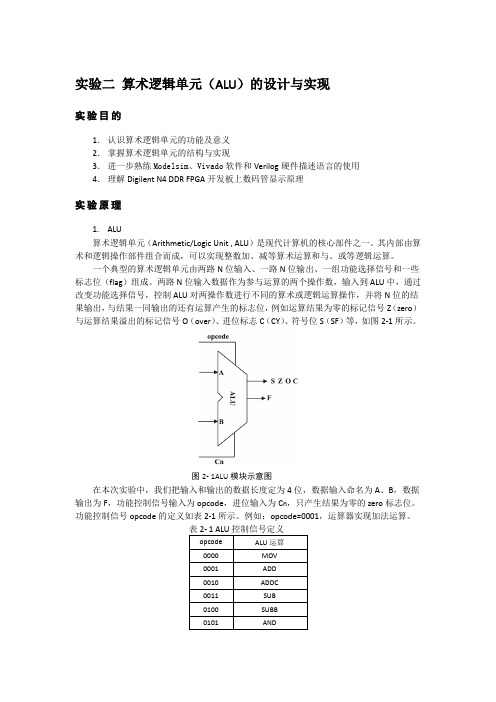

二、实验内容1、实验原理16位运算器数据通路如图2-1所示,其中运算器由四片74LS181以并/串形成16位字长的ALU构成。

低8位运算器的输出经过一个三态门74LS245(U33)到ALUO1插座,实验时用8芯排线和内部数据总线BUSD0~D7插座BUS1~6中的任一个相连,低8位数据总线通过LZD0~LZD7显示灯显示;高8位运算器的输出经过一个三态门74LS245(U33`)到ALUO1`插座,实验时用8芯排线和高8位数据总线BUSD8~D15插座KBUS1或KBUS2相连,高8位数据总线通过LZD8~LZD15显示灯显示;参与运算的四个数据输入端分别由四个锁存器74LS273(U29、U30、U29`、U30、)锁存,实验时四个锁存器的输入并联后用8芯排线连至外部数据总线EXD0~D7插座EXJ1~EXJ3中的任一个;参与运算的数据源来自于8位数据开并KD0~KD7,并经过一三态门74LS245(U51)直接连至外部数据总线EXD0~EXD7,输入的数据通过LD0~LD7显示。

2、实验接线本实验需用到6个主要模块:①低8位运算器模块;②数据输入并显示模块;③数据总线显示模块;④功能开关模块(借用微地址输入模块);⑤高8位运算器模;,⑥高8位(扩展)数据总线显示模块。

根据实验原理详细接线如下(接线①~⑤同实验一):①ALUBUS连EXJ3;②ALUO1连BUS1;③SJ2连UJ2;④跳线器J23上T4连SD;⑤LDDR1、LDDR2、ALUB、SWB四个跳线器拨至左侧(手动方式);⑥AR跳线器拨至左侧,同时开关AR拨至“1”电平;⑦ALUBUS`连EXJ2;⑧ALUO1`连KBUS1;⑨跳线器J19、J25拨至左侧(16位ALU状态);⑩高8位运算器区跳线器ZI2、CN0、CN4连上短路套。

算术逻辑运算实验报告

置入暂存器B中,暂存器B的值通过ALU单元的B7…B0八位LED灯显示。

(6) 改变运算器的功能设置,观察运算器的输出。

置ALU_B=0、LDA=0、LDB=0,然后按表1-1-1置S3、S2、S1、S0和Cn的数值,并观察数据总线LED显示灯显示的结果。

如置S3、S2、S1、S0为0010,运算器作逻辑与运算,置S3、S2、S1、S0为1001,运算器作加法运算。

如果实验箱和PC联机操作,则可通过软件中的数据通路图来观测实验结果(软件使用说明请看附录一),方法是:打开软件,选择联机软件的“【实验】—【运算器实验】”,打开运算器实验的数据通路图,如图1-1-6所示。

进行上面的手动操作,每按动一次ST按钮,数据通路图会有数据的流动,反映当前运算器所做的操作,或在软件中选择“【调试】—【单节拍】”,其作用相当于将时序单元的状态开关KK2置为‘单拍’档后按动了一次ST按钮,数据通路图也会反映当前运算器所做的操作。

重复上述操作,并完成表1-1-2。

然后改变A、B的值,验证FC、FZ的锁存功能。

图1-1-6 数据通路图

五、实验结果及分析

在CON单元的SD27…SD20数据开关中输入01100101,置LDA=1,LDB=0,连续按动时序单元的ST按钮,将二进制数01100101置入暂存器A中。

在CON单元的SD27…SD20数据开关中输入10100111,置LDA=0,LDB=1,连续按动时序单元的ST按钮,将二进制数10100111置入暂存器B中。

置ALU_B=0、LDA=0、LDB=0,置S3、S2、S1、S0为0010,运算器作逻辑与运算。

实验二-算术逻辑单元实验

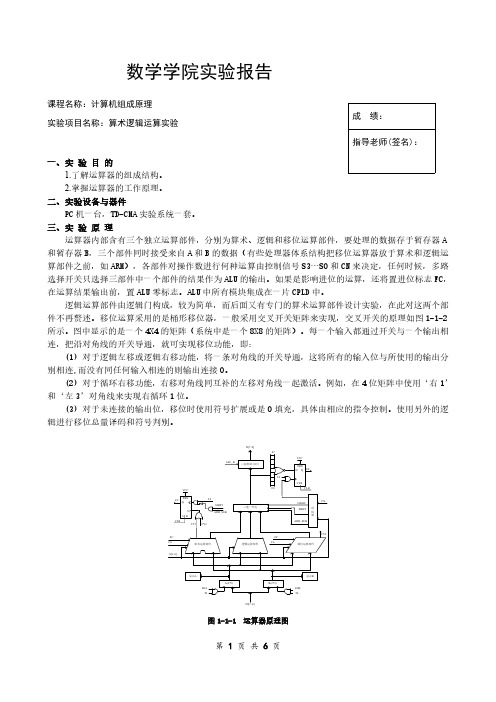

实验二算术逻辑单元(ALU)的设计与实现实验目的1.认识算术逻辑单元的功能及意义2.掌握算术逻辑单元的结构与实现3.进一步熟练Modelsim、Vivado软件和Verilog硬件描述语言的使用4.理解Digilent N4 DDR FPGA开发板上数码管显示原理实验原理1.ALU算术逻辑单元(Arithmetic/Logic Unit , ALU)是现代计算机的核心部件之一。

其内部由算术和逻辑操作部件组合而成,可以实现整数加、减等算术运算和与、或等逻辑运算。

一个典型的算术逻辑单元由两路N位输入、一路N位输出、一组功能选择信号和一些标志位(flag)组成。

两路N位输入数据作为参与运算的两个操作数,输入到ALU中,通过改变功能选择信号,控制ALU对两操作数进行不同的算术或逻辑运算操作,并将N位的结果输出,与结果一同输出的还有运算产生的标志位,例如运算结果为零的标记信号Z(zero)与运算结果溢出的标记信号O(over)、进位标志C(CY)、符号位S(SF)等,如图2-1所示。

图2- 1ALU模块示意图在本次实验中,我们把输入和输出的数据长度定为4位,数据输入命名为A、B,数据输出为F,功能控制信号输入为opcode,进位输入为C n,只产生结果为零的zero标志位。

功能控制信号opcode的定义如表2-1所示。

例如:opcode=0001,运算器实现加法运算。

2.数码管显示关于N4 DDR开发板上数码管的显示原理,参见前面的实验准备部分内容。

实验内容1.基础实验。

用实验调试软件验证ALU的功能,并操作分析、记录结果。

图2- 2 ALU虚拟实验示意图(1)运算功能和控制信号①输入输出对于的开关指示灯分配如下:输入信号A:SW(4-7) B:SW(3-0) Cn:SW8 opcode:SW(12-9)输出信号F:LD(12-15) 标志位S :LD(3) Z LD(2) O: LD(1) C: LD(0)②各种运算对应的控制信号及功能,如下表。

实验二 算术逻辑运算实验报告

计算机组成原理实验报告专业:计算机+自动化姓名:桑超强(201126100416)陆黎明(201126100412)实验二算术逻辑运算实验一、实验目的:·了解运算器的组成结构·掌握运算器的工作原理·掌握简单运算器的数据传输通路·验证运算功能发生器74LS181的组合功能二、实验设备•TDN-CM++教学实验系统一套三、实验原理1、运算器芯片(74LS181)的逻辑功能74LS181 是一种数据宽度为4个二进制的多功能运算器芯片,封装在24引脚的封装壳中,封装型式如图2.1所示。

图2.1 74LS181封装图主要引脚有:(1)A0-A3:第一组操作数据输入端。

(2)B0-B3:第二组操作数据输入端。

(3)F0-F3:操作结果数据输出端。

(4)S0-S3:操作功能控制端。

(5)Cn :低端进位接收端。

(6)4Cn :高端进位输出端。

(7)M :算术/逻辑功能控制端。

芯片的逻辑功能见表2.1。

从表中可看到当控制端S0-S3为1001、M 为0、Cn 为1时,操作结果数据输出端F0-F3上的数据等于第一组操作数据输入端A0-A3上的数据加第二组操作数据输入端B0-B3上的数据。

当S0-S3、M 、Cn 上的控制信号电平不同时,74LS181芯片完成不同功能的逻辑运算操作或算术逻辑运算。

在加法运算操作时,Cn 、4Cn 进位信号低电平有效;减法运算操作时,Cn 、4Cn 借位信号高电平有效;而逻辑运算操作时,Cn 、4Cn 进位信号无意义。

图2.1数据逻辑运算部件原理图2、运算器实验逻辑电路试验台运算器实验逻辑电路中,两片74LS181芯片构成一个长度为8位的运算器,两片74LS373分别作为第一操作数据寄存器和第二操作数据寄存器,一片74LS245作为操作结果数据输出缓冲器,逻辑结构如图2.2所示。

图中算术逻辑操作时仅为Cy 判别进位只是电路;判零Zi 和零标志电路指示电路。

算术逻辑运算实验报告

置入暂存器B中,暂存器B的值通过ALU单元的B7…B0八位LED灯显示。

(6) 改变运算器的功能设置,观察运算器的输出。

置ALU_B=0、LDA=0、LDB=0,然后按表1-1-1置S3、S2、S1、S0和Cn的数值,并观察数据总线LED显示灯显示的结果。

如置S3、S2、S1、S0为0010,运算器作逻辑与运算,置S3、S2、S1、S0为1001,运算器作加法运算。

如果实验箱和PC联机操作,则可通过软件中的数据通路图来观测实验结果(软件使用说明请看附录一),方法是:打开软件,选择联机软件的“【实验】—【运算器实验】”,打开运算器实验的数据通路图,如图1-1-6所示。

进行上面的手动操作,每按动一次ST按钮,数据通路图会有数据的流动,反映当前运算器所做的操作,或在软件中选择“【调试】—【单节拍】”,其作用相当于将时序单元的状态开关KK2置为‘单拍’档后按动了一次ST按钮,数据通路图也会反映当前运算器所做的操作。

重复上述操作,并完成表1-1-2。

然后改变A、B的值,验证FC、FZ的锁存功能。

图1-1-6 数据通路图

五、实验结果及分析

在CON单元的SD27…SD20数据开关中输入01100101,置LDA=1,LDB=0,连续按动时序单元的ST按钮,将二进制数01100101置入暂存器A中。

在CON单元的SD27…SD20数据开关中输入10100111,置LDA=0,LDB=1,连续按动时序单元的ST按钮,将二进制数10100111置入暂存器B中。

置ALU_B=0、LDA=0、LDB=0,置S3、S2、S1、S0为0010,运算器作逻辑与运算。

实验二 运算器逻辑设计实验

实验二运算器逻辑设计实验实验所属系列:计算机系统与软件实验教学—硬件系列实验对象:本科生相关课程及专业:计算机组成原理课程,计算机应用专业实验类型:课程设计实验时数(学分): 8学时一、实验目的通过部件级的实验设计和调试,培养学生分析和解决实际问题的能力,并增强学生的动手能力。

具体目的如下:1)掌握用硬件描述语言设计逻辑部件的方法。

2)了解运算器的设计过程。

3)掌握组内和组间并行进位技术。

4)验证运算器的功能。

二、实验内容与要求利用ALTERA公司的EPF10K10LC84-4的内部可编程资源,设计一个16 bit的运算器;要求该运算器具有加、减算术运算功能和基本逻辑(与、或、非、异或、求补)运算功能。

1)实验基础(必要的基础知识)熟悉运算器部件结构;熟悉硬件描述语言VHDL。

2)实验步骤第一步:画出寄存器级的ALU框图,标明端口、引脚及其含义;第二步:用MAX+PLUS II建立代码工程,用VHDL定义并描述各部件及整体功能;第三步:模块级仿真、系统级仿真;第四步:模拟合成并验证;第五步:编写详细的实验报告。

3)实验注意事项(1) ALU结构及各端口正确;(2)先模块级仿真验证正确后,才进行系统级仿真。

(3)由于实验面板的输入,输出有限,所以对ALU模块进行了封装。

文件见附件;学生只需完成CPU_ALU模块;然后将cpu_alu_extra作为顶层文件和工程文件进行编译,仿真,下载。

三、实验开设方式1)分组实验,每组3人。

2)实验授课2学时,介绍实验开发平台和实验板的使用。

3)实验占有时间估计需14学时。

四、实验设备与环境1)基本环境要求①宽敞整洁专用硬件实验室②必备的基本实验工具2)最低设备要求①计算机CPU不小于800MHZ;②计算机内存不小于128M;③其他标准配置。

3)系统平台要求windows984)软件、硬件及相应工具要求①开发工具:MAX+plus II 9.6②仿真工具:ModelSim SE5.6③电子EDA实验开发系统五、实验评分标准1)评分标准(A优秀、B良好、C中等、D及格、E不及格)2)测评方式A:程序下载到实验板上,功能正确、结构优化。

实验一:十六位数据总线实验

十六位机运算器实验一、实验目的1. 熟悉Dais-CMX16+达爱思教仪的各部分功能和使用方法。

2. 掌握十六位机字与字节运算的数据传输格式,验证运算功能发生器及进位控制的组合功能。

了解运算器的工作原理。

3. 完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运用。

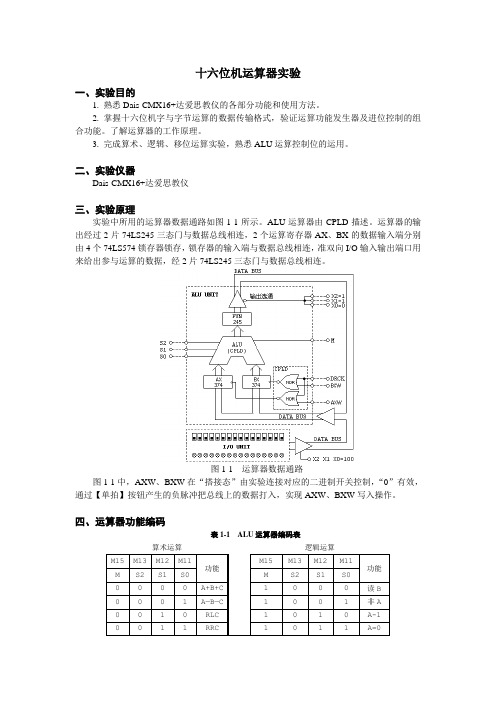

二、实验仪器Dais-CMX16+达爱思教仪三、实验原理实验中所用的运算器数据通路如图1-1所示。

ALU运算器由CPLD描述。

运算器的输出经过2片74LS245三态门与数据总线相连,2个运算寄存器AX、BX的数据输入端分别由4个74LS574锁存器锁存,锁存器的输入端与数据总线相连,准双向I/O输入输出端口用来给出参与运算的数据,经2片74LS245三态门与数据总线相连。

图1-1运算器数据通路图1-1中,AXW、BXW在“搭接态”由实验连接对应的二进制开关控制,“0”有效,通过【单拍】按钮产生的负脉冲把总线上的数据打入,实现AXW、BXW写入操作。

四、运算器功能编码表1-1 ALU运算器编码表算术运算逻辑运算表1-2移位编码表五、实验连线将实验系统设置为手动/搭接状态,K23~K0置“1”,灭M23~M0控位显示灯。

然后按下表要求“搭接”部件控制电路。

六、实验步骤 (一)算术运算1. 字算术运算 (1) 字写操作W XP OP=000BXW(M18)=1 按【单拍】按钮BXW(M18)=0 按【单拍】按钮(2) 字读操作(3) 字加法与减法运算(不带进位加、不带错位减)令M S2 S1 S0(K15 K13~K11)=0100,FUN 及总线单元显示AX+BX 的结果。

令M S2 S1 S0(K15 K13~K11)=0101,FUN 及总线单元显示AX -BX 的结果。

2. 字节算术运算(1) 偶字节写(置数操作)通过I/O 单元“S15~S0”开关向累加器AL 和暂存器BL 置数,具体操作步骤如下:(2) 偶字节读操作(运算寄存器AL 和BL 内容送总线)关闭AL 、BL 写使能,令AXW(M18)=BXW(M17)=1,按下流程分别读AL 、BL 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三16位算术逻辑运算实验

一、实验目的

1、掌握16位运算器的数据传送通路组成原理。

2、进一步验证算术逻辑运算功能发生器74LS181的组合功能。

3、按要求和给出的数据完成几种指定的算术逻辑运算。

二、实验内容

1、实验原理

16位运算器数据通路如图2-1所示,其中运算器由四片74LS181以并/串形成16位字长的ALU构成。

低8位运算器的输出经过一个三态门74LS245(U33)到ALUO1插座,实验时用8芯排线和内部数据总线BUSD0~D7插座BUS1~6中的任一个相连,低8位数据总线通过LZD0~LZD7显示灯显示;高8位运算器的输出经过一个三态门74LS245(U33`)到ALUO1`插座,实验时用8芯排线和高8位数据总线BUSD8~D15插座KBUS1或KBUS2相连,高8位数据总线通过LZD8~LZD15显示灯显示;参与运算的四个数据输入端分别由四个锁存器74LS273(U29、U30、U29`、U30、)锁存,实验时四个锁存器的输入并联后用8芯排线连至外部数据总线EXD0~D7插座EXJ1~EXJ3中的任一个;参与运算的数据源来自于8位数据开并KD0~KD7,并经过一三态门74LS245(U51)直接连至外部数据总线EXD0~EXD7,输入的数据通过LD0~LD7显示。

2、实验接线

本实验需用到6个主要模块:

①低8位运算器模块;②数据输入并显示模块;③数据总线显示模块;

④功能开关模块(借用微地址输入模块);⑤高8位运算器模;,

⑥高8位(扩展)数据总线显示模块。

根据实验原理详细接线如下(接线①~⑤同实验一):

①ALUBUS连EXJ3;

②ALUO1连BUS1;

③SJ2连UJ2;

④跳线器J23上T4连SD;

⑤LDDR1、LDDR2、ALUB、SWB四个跳线器拨至左侧(手动方式);

⑥AR跳线器拨至左侧,同时开关AR拨至“1”电平;

⑦ALUBUS`连EXJ2;

⑧ALUO1`连KBUS1;

⑨跳线器J19、J25拨至左侧(16位ALU状态);

⑩高8位运算器区跳线器ZI2、CN0、CN4连上短路套。

图2-1 16位运算器数据通路图

3、实验步骤

(1)连接线路,仔细查线无误后,接通电源。

(2)用二进制数码开关KD7~KD0向DR1、DR2、DR3、DR4寄存器置数。

方法:关闭ALU输出三态门应使ALUB`=1(即开关ALUB=1),开启输入三态门应使SWB`=0(即开关SWB=0),选通哪一个寄存器用对应开关LDDR1~LDDR4(高电平有效),其中LDDR3、LDDR4开关在高8位运算器上部,输入脉冲T4按手动脉冲发生按钮。

设置数据开关具体操作步骤图示如下:

说明:LDDR1、LDDR2、ALUB`、SWB`、LDDR3、LDDR4六个信号电平由对应的开关LDDR1、LDDR2、ALUB 、SWB 、LDDR3、LDDR4给出,拨至上面为“1”,拨至下面为“0”,电平值由对应显示灯显示;T4由手动脉冲开关给出。

(3) 验证74LS181的16位算术运算和逻辑运算功能(采用正逻辑)。

·开关SWB=1,关闭输入三态门; ·开关ALUB=0,打开输出三态门;

·LDDR1~LDDR4四个开关全拨至“0”电平。

说明:如果要实现16位带进位控制算术逻辑运算,只需在实验二的基础上将开关AR=1置成AR=0即可。

·根据下表2—1,置功能开关S3、S2、S1、S0、M 、CN 改变74LS181的算术运算和逻辑运算功能设置,观察运算器输出,将观察结果填入表中,并将理论计算结果 写入表2—2,进行比较验证。

LDDR1=1 LDDR1=0

LDDR1=0

LDDR2=0 LDDR3=1 LDDR2=0 LDDR3=0 LDDR1=0

表2—1 实验结果

注意:本实验做完后,拔掉连线ALUBUS`和ALUO1`,去掉短路套ZI2、CN0、CN4。

表2—2 理论计算结果

三、设计内容

1、若有两个16位二进制数:00FFH和2D5AH,要求通过74LS181的运算,计算这两数相与的结果。

2、若有两个16位二进制数:FF00H和01BAH,要求通过74LS181的运算,计算这两数相与的结果。

3、若有两个16位二进制数:1234H和A987H,要求通过74LS181的运算,计算这两数之和。

4、若被减数为7C69H和减数为1234H,要求通过74LS181的运算,计算这两数之差。

5、若被减数为1234 H和减数为7C69H,要求通过74LS181的运算,计算这两数之差。

和题4结果比较。