实验一 8位算术逻辑运算实验(信软)

八数码问题求解实验报告

八数码问题求解(一)实验软件TC2.0或VC6.0编程语言或其它编程语言(二)实验目的1.熟悉人工智能系统中的问题求解过程;2.熟悉状态空间的盲目搜索和启发式搜索算法的应用;3.熟悉对八数码问题的建模,求解及编程语言的应用。

(三)实验内容八数码问题:在3×3的方格棋盘上,摆放着1到8这八个数码,有一个方格是空的,要求对空格执行空格左移,空格右移,空格上移,空格下移这四个操作使得棋盘从初始状态到目标状态。

输入初始状态和目标状态,输出从初始状态到目标状态的路径。

(四)实验代码#include"stdafx.h"#include<iostream>#include<ctime>#include<vector>using namespace std;const int ROW = 3;const int COL = 3;const int MAXDISTANCE = 10000;const int MAXNUM = 10000;typedef struct_Node{int digit[ROW][COL];int dist; // distance between one state and the destination int dep; // the depth of node// So the comment function = dist + dep.int index; // point to the location of parent} Node;Node src, dest;vector<Node> node_v; // store the nodesbool isEmptyOfOPEN() {for (int i = 0; i < node_v.size(); i++) {if (node_v[i].dist != MAXNUM)return false;}return true;}bool isEqual(int index, int digit[][COL]) {for (int i = 0; i < ROW; i++)for (int j = 0; j < COL; j++) {if (node_v[index].digit[i][j] != digit[i][j])return false;}return true;}ostream& operator<<(ostream& os, Node& node) {for (int i = 0; i < ROW; i++) {for (int j = 0; j < COL; j++)os << node.digit[i][j] << ' ';os << endl;}return os;}void PrintSteps(int index, vector<Node>& rstep_v) { rstep_v.push_back(node_v[index]);index = node_v[index].index;while (index != 0) {rstep_v.push_back(node_v[index]);index = node_v[index].index;}for (int i = rstep_v.size() - 1; i >= 0; i--)cout << "Step " << rstep_v.size() - i<< endl << rstep_v[i] << endl;}void Swap(int& a, int& b) {int t;t = a;a = b;b = t;}void Assign(Node& node, int index) {for (int i = 0; i < ROW; i++)for (int j = 0; j < COL; j++)node.digit[i][j] = node_v[index].digit[i][j];}int GetMinNode() {int dist = MAXNUM;int loc; // the location of minimize nodefor (int i = 0; i < node_v.size(); i++) {if (node_v[i].dist == MAXNUM)continue;else if ((node_v[i].dist + node_v[i].dep) < dist) {loc = i;dist = node_v[i].dist + node_v[i].dep;}}return loc;}bool isExpandable(Node& node) {for (int i = 0; i < node_v.size(); i++) {if (isEqual(i, node.digit))return false;}return true;}//扩展int Distance(Node& node, int digit[][COL]) {int distance = 0;bool flag = false;for (int i = 0; i < ROW; i++)for (int j = 0; j < COL; j++)for (int k = 0; k < ROW; k++) {for (int l = 0; l < COL; l++) {if (node.digit[i][j] == digit[k][l]) {distance += abs(i - k) + abs(j - l);//abs()求得是正数的绝对值。

计算机组成实验报告二8位算术逻辑运算

1、目的与要求1、验证带进位控制的算术逻辑运算发生器74LSl8l 的功能。

2、按指定数据完成几种指定的算术运算。

实验性质:验证性参见《计算机组成原理实验指导书》2、实验设备DVCC 计算机组成原理实验箱,排线若干。

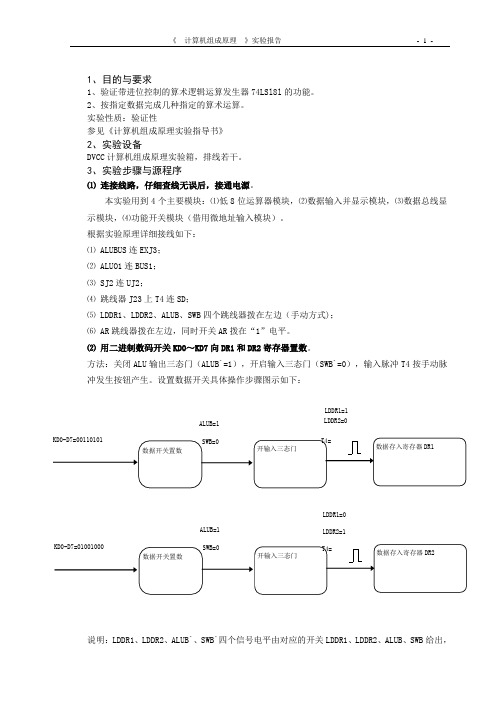

3、实验步骤与源程序⑴ 连接线路,仔细查线无误后,接通电源。

本实验用到4个主要模块:⑴低8位运算器模块,⑵数据输入并显示模块,⑶数据总线显示模块,⑷功能开关模块(借用微地址输入模块)。

根据实验原理详细接线如下: ⑴ ALUBUS 连EXJ3; ⑵ ALUO1连BUS1; ⑶ SJ2连UJ2;⑷ 跳线器J23上T4连SD ;⑸ LDDR1、LDDR2、ALUB 、SWB 四个跳线器拨在左边(手动方式); ⑹ AR 跳线器拨在左边,同时开关AR 拨在“1”电平。

⑵ 用二进制数码开关KD0~KD7向DR1和DR2寄存器置数。

方法:关闭ALU 输出三态门(ALUB`=1),开启输入三态门(SWB`=0),输入脉冲T4按手动脉冲发生按钮产生。

设置数据开关具体操作步骤图示如下:说明:LDDR1、LDDR2、ALUB`、SWB`四个信号电平由对应的开关LDDR1、LDDR2、ALUB 、SWB 给出,ALUB=1 LDDR1=1 LDDR2=0 ALUB=1 LDDR2=1 LDDR1=0拨在上面为“1”,拨在下面为“0”,电平值由对应的显示灯显示,T4由手动脉冲开关给出。

⑶检验DR1和DR2中存入的数据是否正确,利用算术逻辑运算功能发生器 74LS181的逻辑功能,即M=1。

具体操作为:关闭数据输入三态门SWB`=1,打开ALU输出三态门ALUB`=0,当置S3、S2、S1、S0、M为1 1 1 1 1时,总线指示灯显示DR1中的数,而置成1 0 1 0 1时总线指示灯显示DR2中的数。

⑷验证74LS181的算术运算和逻辑运算功能(采用正逻辑)在给定DR1=35、DR2=48的情况下,改变算术逻辑运算功能发生器的功能设置,观察运算器的输出,填入表2.1.1中,并和理论分析进行比较、验证。

计算机组成原理实验报告-八位补码加减法器的设计与实现

计算机科学与技术学院计算机组成原理实验报告书实验名称八位补码加/减法器的设计与实现班级学号姓名指导教师日期成绩实验1八位补码加/减法器的设计与实现一、实验目的1.掌握算术逻辑运算单元(ALU)的工作原理。

2.熟悉简单运算器的数据传送通路。

3.掌握8位补码加/减法运算器的设计方法。

4.掌握运算器电路的仿真测试方法二、实验任务1.设计一个8位补码加/减法运算器(1)参考图1,在QUARTUS II里输入原理图,设计一个8位补码加/减法运算器。

(2)创建波形文件,对该8位补码加/减法运算器进行功能仿真测试。

(3)测试通过后,封装成一个芯片。

2.设计8位运算器通路电路参考下图,利用实验任务1设计的8位补码加/减法运算器芯片建立运算器通路。

3.利用仿真波形,测试数据通路的正确性。

设定各控制信号的状态,完成下列操作,要求记录各控制信号的值及时序关系。

(1)在输入数据IN7~IN0上输入数据后,开启输入缓冲三态门,检查总线BUS7~BUS0上的值与IN0~IN7端输入的数据是否一致。

(2)给DR1存入55H,检查数据是否存入,请说明检查方法。

(3)给DR2存入AAH,检查数据是否存入,请说明检查方法。

(4)完成加法运算,求55H+AAH,检查运算结果是否正确,请说明检查方法。

(5)完成减法运算,分别求55H-AAH和AAH-55H,检查运算结果是否正确,请说明检查方法。

(6)求12H+34H-56H,将结果存入寄存器R0,检查运算结果是否正确,同时检查数据是否存入,请说明检查方法。

三、实验要求(1)做好实验预习,掌握运算器的数据传送通路和ALU的功能特性。

(2)实验完毕,写出实验报告,内容如下:①实验目的。

②实验电路图。

③按实验任务3的要求,填写下表,以记录各控制信号的值及时序关系。

表中的序号表示各控制信号之间的时序关系。

要求一个控制任务填一张表,并可用文字对有关内容进行说明。

⑤实验体会与小结。

四、实验预习内容1.实验电路设计原理及思路说明本实验利用基本逻辑门电路设计一位全加器(FA),如表1:加法又可以实现减法,所以使用了一个M输入来进行方式控制加减。

八数码实验报告

八数码实验报告实验名称:八数码实验目的:通过使用搜索算法和启发式算法,解决八数码问题,深入理解搜索算法原理和应用。

实验环境:使用Python语言进行编程实现,操作系统为Windows。

实验过程:1. 定义八数码问题的状态和目标状态,分别以列表的形式表示。

* 初始状态:[2, 8, 3, 1, 6, 4, 7, 0, 5]* 目标状态:[1, 2, 3, 8, 0, 4, 7, 6, 5]2. 实现深度优先搜索算法,运行程序得到结果。

通过深度优先搜索算法,得到了八数码问题的解法。

但是,由于深度优先搜索算法过于盲目,搜索时间过长,而且容易陷入无解状态,因此需要改进算法。

3. 改进算法——广度优先搜索。

在深度优先搜索的基础上,改用广度优先搜索算法,实现代码如下:```def bfs(start, target):queue = [(start, [start])]seen = {tuple(start)}while queue:node, path = queue.pop(0)for move, i in direction.items():new_node = [j for j in node]if i not in range(0, 9):continuenew_node[0], new_node[i] = new_node[i], new_node[0] if tuple(new_node) in seen:continueif new_node == target:return path + [new_node]seen.add(tuple(new_node))queue.append((new_node, path + [new_node]))```4. 改进算法——A*算法。

在广度优先搜索的基础上,使用A*算法进行优化。

进行了以下改进:* 引入估价函数,加快搜索速度;* 遍历过程中对结点进行评估,保留最优的结点。

计算机组成原理实验报告

计算机组成原理实验报告实验报告运算器实验⼀、实验⽬的掌握⼋位运算器的数据传输格式,验证运算功能发⽣器及进位控制的组合功能。

⼆、实验要求完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运⽤。

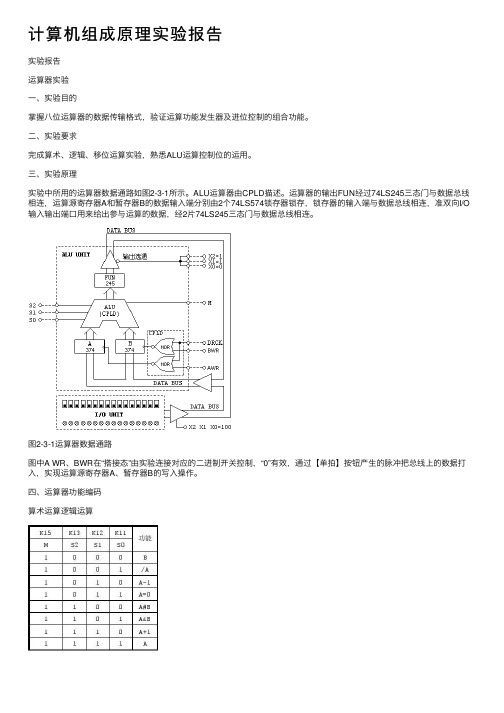

三、实验原理实验中所⽤的运算器数据通路如图2-3-1所⽰。

ALU运算器由CPLD描述。

运算器的输出FUN经过74LS245三态门与数据总线相连,运算源寄存器A和暂存器B的数据输⼊端分别由2个74LS574锁存器锁存,锁存器的输⼊端与数据总线相连,准双向I/O 输⼊输出端⼝⽤来给出参与运算的数据,经2⽚74LS245三态门与数据总线相连。

图2-3-1运算器数据通路图中A WR、BWR在“搭接态”由实验连接对应的⼆进制开关控制,“0”有效,通过【单拍】按钮产⽣的脉冲把总线上的数据打⼊,实现运算源寄存器A、暂存器B的写⼊操作。

四、运算器功能编码算术运算逻辑运算K23~K0置“1”,灭M23~M0控位显⽰灯。

然后按下表要求“搭接”部件控制路。

表2.3.2 运算实验电路搭接表算术运算1.运算源寄存器写流程通过I/O单元“S7~S0”开关向累加器A和暂存器B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K18=K17=“1”,按下流程分别读A、B。

3.加法与减法运算令M S2 S1 S0(K15 K13~K11=0100),为算术加,FUN及总线单元显⽰A+B的结果令M S2 S1 S0(K15 K13~K11=0101),为算术减,FUN及总线单元显⽰A-B的结果。

逻辑运算1.运算源寄存器写流程通过“I/O输⼊输出单元”开关向寄存器A和B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K17= K18=1,按下流程分别读A、B。

①若运算控制位设为(M S2 S1 S0=1111)则F=A,即A内容送到数据总线。

②若运算控制位设为(M S2 S1 S0=1000)则F=B,即B内容送到数据总线。

计算机组成原理运算器实验—算术逻辑运算实验

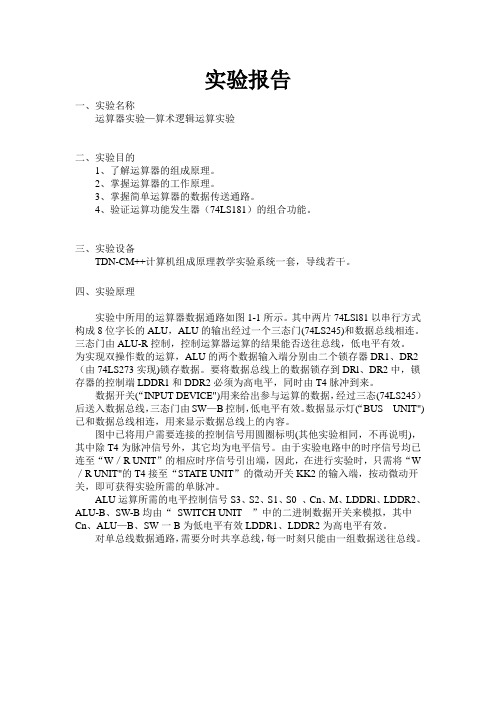

实验报告一、实騎名称运算器实騎一算术遐辑运算实騎二、实豔目的1、了解运算器的组成原理。

2、掌握运算器的工作原理。

3、掌握简单运算器的数据传送通路。

4、验证运算功能发生器(74LS181 )的组合助能。

三、实豔设备TDN-CM++it算机组成原理教学实验系统一套,导线若干。

实验中所用的运算器数据通路如图1"所示。

其中两片74LSI81以串行方式沟成8位字长的ALU, ALU的输出经il 一个三态门(74LS245)和数据总线相连。

三态门由ALU-R控制,控制运算器运算的绪果能否送往总线,低电平有效。

为实现双操作数的运算,ALU的两个数据输入端分别由二个锁存器DR1、DR2(由74LS273实现)锁存数据。

要稱数据总线上的数据锁存到DRk DR2中,锁存器的控制S LDDR1和DDR2必须为高电平,同时由T4脉冲到来。

数据开关(“INPUT DEVICE")用来给出参与运算的数摇,经过三态(74LS245 ) 后送人数据总线,三态门由SW-B控朝低电平有效。

数据显示灯(“BUS UNIT-) 已和数播总线相连,用来显示数据总线上的内容。

图中已将用户需要连接的腔制信号用冏IS标明(其他实騎相同,不再说明),其中除T4为脉冲信号外,其它均为电平信号。

由于实騎电路中的时序信号均已连至“W/RUNIT”的相应时序信号引岀端,因此,在进行实验时,只需将“W / R UNIT"的T4接至“STATEUNIT”的fit动开关KK2的输入竭,按动微动开关, 即可获得实酚所需的单脉冲。

ALU运算所需的电平控制信号S3、S2、S1、SO、Cn、M、LDDRk LDDR2、ALU-B、SW-B均由M SWITCH UNIT ”中的二进制数摇开关来模81,其中Cn、ALU—B s SW-B为低电平有效LDDRk LDDR2为高电平有效。

对单总线数据通路,需要分时共享总线,每一时刻只能由一组数弼送往总线。

顺序结构与逻辑运算实验报告(最终定稿)

顺序结构与逻辑运算实验报告(最终定稿)第一篇:顺序结构与逻辑运算实验报告实验 2顺序结构与逻辑运算1.实验目的和要求(1)掌握数据输入/输出函数的使用,能正确使用各种格式转换符。

(2)熟悉顺序结构程序中语句的执行过程,并学会基本调试程序方法。

(3)能够正确使用逻辑运算符和逻辑表达式。

(4)学会运用逻辑表达式或关系表达式等表示条件。

(5)熟练掌握 if 语句和 switch 语句,掌握条件表达式构成的选择结构。

(6)熟练掌握跟踪调试程序,针对具体数据组织输入测试数据,观察程序运行能否得到预期的输出结果。

(7)学会编写简单程序。

2.实验内容:实验指导书中的实验三和实验四3.实验步骤及结果实验三部分:3-1-1 该程序正确的源程序代码(或窗口截图):程序运行结果画面如下:3-1-2 该程序正确的源程序代码(或窗口截图):程序运行结果画面如下:3-2-1 该程序完整的源程序代码(或窗口截图):程序运行结果画面如下:3-2-2 该程序完整的源程序代码(或窗口截图):程序运行结果画面如下:3-3 注意:这道程序我们不按书中提示进行,而在 VC 环境下进行调试。

语法错误和逻辑错误的区别何在?语法了错误是指编译的程序中破坏了 C 语言固有的语法规则,比如缺少或者多添了一个字母符号,一个标点符号,或者缺少群头文件等,导致程序合无法编译和运行;逻辑错误是指代码符合C 语言规范,程序可以运行,但是结果有误,通常是语句逻辑有误。

如何启动单步调试?点击【组建】按钮下的【开始调试】选项,在新出现的对话框中点击【【step into 】按钮,每条语句便可单独执行。

要使程序运行到“ss=(k…”这一行暂停下来,该如何操作? 光标放在目标行前,点击项目栏的【remove breakpoint 】程序便可在目标处暂停。

怎样终止调试状态(程序复位)?点击【【step over 】程序便可在目标处暂停调试。

单步调试状态下,向下运行一条语句的操作方法(分两种情况回答,第一种,跟踪到自定义函数内部,第2 种,不跟踪到自定义函数内部):1.单击调试菜单中的【step into 】跟踪到自定义函数内部。

8位运算器课程设计

8位运算器课程设计一、课程目标知识目标:1. 学生能理解8位运算器的原理与功能,掌握二进制与十进制的转换方法。

2. 学生能运用8位运算器进行基本的算术运算,如加、减、乘、除,并理解运算过程中的溢出与进位现象。

3. 学生了解8位运算器在计算机硬件中的作用,及其在信息技术中的应用。

技能目标:1. 学生能够独立完成8位运算器的模拟操作,解决实际问题。

2. 学生通过8位运算器的操作,提高逻辑思维和问题解决能力。

3. 学生能够运用所学知识,对简单的计算机程序进行初步的分析与设计。

情感态度价值观目标:1. 学生培养对计算机硬件及编程的兴趣,激发学习信息技术的热情。

2. 学生通过学习8位运算器,认识到科技发展对生活的影响,增强创新意识。

3. 学生在团队协作中培养沟通与合作的意识,提高团队荣誉感。

课程性质:本课程为信息技术学科的教学内容,旨在帮助学生掌握计算机硬件基础知识,提高编程技能。

学生特点:考虑到学生所在年级,已具备一定的逻辑思维和问题解决能力,对信息技术有较高的兴趣。

教学要求:结合学生特点,通过实例教学,使学生在实践中掌握8位运算器的相关知识,提高学生的动手操作能力和团队协作能力。

将课程目标分解为具体的学习成果,以便于教学设计和评估。

二、教学内容1. 引言:介绍8位运算器的基本概念,引出二进制与十进制的转换,让学生初步了解8位运算器的原理。

- 教材章节:第一章 计算机硬件基础,第1节 计算机硬件概述2. 二进制与十进制的转换方法:- 教材章节:第一章 计算机硬件基础,第2节 数字逻辑基础3. 8位运算器的算术运算:- 加法、减法、乘法、除法的运算规则及运算过程- 溢出与进位现象的分析- 教材章节:第一章 计算机硬件基础,第3节 算术逻辑单元4. 8位运算器在实际应用中的案例分析:- 简单计算机程序的初步分析与设计- 教材章节:第二章 计算机指令与编程,第1节 计算机指令概述5. 8位运算器在计算机硬件中的作用:- 介绍CPU中的算术逻辑单元(ALU)- 教材章节:第一章 计算机硬件基础,第4节 中央处理器6. 实践操作:- 使用模拟软件进行8位运算器的操作- 解决实际问题,提高逻辑思维和问题解决能力- 教材章节:第三章 计算机操作实践,第1节 计算机操作基础教学进度安排:本章节内容共需6个课时,其中理论教学4课时,实践操作2课时。

八位算术逻辑运算

实验1 八位算术逻辑运算

一、实验目的和要求

1、掌握运算器的基本组成结构;

2、掌握运算器的工作原理。

二、实验原理图

实验采用的运算器数据通路如图1-1所示,其中74HC18是4位算数逻辑运算单元,本实验采用2片构成8位的算数逻辑运算单元。

两个操作数从最下面的8个乒乓开关输入,分别锁存在两个锁存器74273中,分别作为ALU的两个操作数。

74HC18有16种算数逻辑运算,控制端由S3、S2、S1、S0控制,在电路中由SWS3、SWS2、SWS1、SWS0四个开关控制。

M=1,逻辑运算,M=0算数运算,CN为进位位。

运算的结果显示在上方的8个LED灯。

图1-1运算器原理图

逻辑功能表如表1-1所示。

表5-1 ALU逻辑功能表

三、实验要求完成: 1、实验要求

(1)在暂存器A 中设置操作数A=65H ;在暂存器B 中设置操作数B=A7H 。

(2)通过对ALU 操作控制端S3、S2、S1、S0、CN 、M 的设置,完成两个操作数的算术、逻辑运算,并将运算结果填入表1-2中。

最后将运算结果同74HC181逻辑功能表(表1-1)对比分析,判断运算结果是否正确。

四

、实验数据记录

验证74HC181的逻辑功能,将运算结果记录在表1-2中。

六、实验结果分析

1、对比分析表1-1和表1-2,判断运算结果是否正确,并分析原因。

2、暂存器A置数完成后,如果操作控制信号 wA仍保持有效电平(wA=0),在对暂存器B置数时会出现什么情况?。

计算机组成原理实验实验一运算器实验(一)算术逻辑运算实验一

计算机组成原理实验实验一运算器实验(一)算术逻辑运算实验一、实验目的1、掌握简单运算器的数据传送通路。

2、验证运算功能发生器(74LS181)的组合功能。

二、实验原理1、实验中所用的运算器数据通路图1所示。

三、实验步骤1、用二进制数码开关向DR1和DR2寄存器置数。

具体操作步骤图2所示。

2、验证74LS181的算术运算和逻辑运算功能(二) 进位控制实验一、实验目的1、验证带进位控制算术运算功能发生器的功能。

2、按指定数据完成几种算术运算。

二、实验原理实验原理图如图3所示。

三、实验步骤1、用二进制数码开关向DR1和DR2寄存器置数向DR1存入01010101,向DR2存入10101010。

具体操作步骤图4所示。

图2图3 进位控制实验原理图2、进位标志清零S3 S2 S1 S0 M 的状态置为00000,AR 状态置为0,按动微动开关KK2。

进位标志指示灯CY 亮时表示无进位,进位标志为“0” ;指示灯CY 灭时表示有进位,进位标志为“1”。

3、验证带进位运算及进位锁存功能时,使Cn=1, Ar=0, SW-B=1。

T4脉冲到来时,将本次运算的进位结果锁存到进位锁存器中。

注意观察进位标志显示灯CY 。

(三) 移位运算实验一、实验目的验证移位运算控制的组合功能。

二、实验原理移位运算实验原理图如图5所示, 74LS299功能表如表1所示图4表1 74LS299功能表三、实验步骤1、移位操作:(1)置数,具体步骤如图6所示。

2、移位,参照功能表改变S0 S1 T4 299-B 的状态,按动微动开关KK2,观察移位的结果。

实验二 存储器实验一、实验目的掌握静态随机存储器的工作特性及数据的读写方法。

二、实验原理图5 移位运算实验原理图图6实验所用的静态存储器电路原理图如图7所示。

三、实验步骤1、写操作。

给存储器的00、01、02、03、04地址单元中分别写入数据11、12、13、14、15,具体操作步骤图8所示(以向0号单元写入数据11为例)。

8位ALU(算术逻辑单元)verilog语言

大连理工大学城市学院FPGA实验报告实验内容:8位ALU系别班级:电子1004班学号:姓名:日期:2013.4.14一.设计概述:一种基于可编程逻辑器件FPGA和硬件描述语言的8位的ALU的设计方法。

该ALU采用层次设计方法,有寄存器模块、控制模块和显示模块组成,能实现8位无符号数的取值、加减和4种逻辑运算(与、或、异或、同或)。

该ALU在QuartusII软件环境下进行功能仿真,通过DE2验证。

二.设计功能:1、该处理器的数据宽度为8bit,可以实现算术加法、减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。

2、用选择端opcode [2:0] 选择8种运算,2个操作数分别是a_r [7:0]和b_r[7:0],运算结果是alu_out[7:0];并定义选择如下。

3、使用DE2板上的3个拨码开关设置当前ALU的运算功能,再由8个拨码开关给定数据A 和数据B,由一个按键key手动提供脉冲。

三.设计方案:本设计共有5个模块。

1)脉冲输出器(key手动脉冲),计数依次产生4个脉冲到各个部件,第一个脉冲启动信号。

2)寄存器A,第二个脉冲来时锁存数据A,并在数码管上显示。

3)寄存器B,第三个脉冲来时锁存数据B,并在数码管上显示。

4)8位ALU,第四个脉冲来时进行运算,并锁存结果alu_out。

5)结果显示器,将结果显示通过DE2上的数码管显示。

四.程序分析:主程序模块:module alu8(clk,clk_r,rst,a,b,alu_out,opcode,sw_ab,HEX1, HEX0, HEX7, HEX6, HEX5, HEX4);input clk,rst,clk_r;input [7:0] sw_ab;input [2:0] opcode;output [6:0] HEX1, HEX0, HEX7, HEX6, HEX5, HEX4;output [7:0] a;output [7:0] b;output [7:0] alu_out;rega U1(.clk(clk),.rst(rst),.sw_ab(sw_ab),.a_r(a),.clk_r(clk_r),.HEX7(HEX7),. HEX6(HEX6));regb U2(.clk(clk),.rst(rst),.sw_ab(sw_ab),.b_r(b),.clk_r(clk_r),.HEX5(HEX5),. HEX4(HEX4));alur U3(.clk(clk),.rst(rst),.a_r(a),.b_r(b),.alu_out(alu_out),.opcode(opcode)); digital U4(.clk_r(clk_r),.rst(rst),.alu_out(alu_out),.HEX1(HEX1),. HEX0(HEX0)); endmodule第一位数A模块:module rega (clk,clk_r,rst,sw_ab,a_r,HEX7,HEX6);input [7:0] sw_ab;input clk,clk_r,rst;output [7:0] a_r;reg [7:0] a_r;output reg[6:0] HEX7,HEX6;reg [3:0] cnt;always @(posedge clk or negedge rst)if(!rst) cnt<=1'd0;else if(cnt==5) cnt<=1'd0;else cnt<=cnt+1'd1;always @(posedge clk or negedge rst)if(!rst) a_r=0;else if(cnt==1) a_r=sw_ab;else a_r=a_r;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010 ,seg6=7'b0000010,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b0000011 ,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always @(posedge clk_r)case(a_r[3:0])4'h0: HEX6[6:0]=seg0;4'h1: HEX6[6:0]=seg1;4'h2: HEX6[6:0]=seg2;4'h3: HEX6[6:0]=seg3;4'h4: HEX6[6:0]=seg4;4'h5: HEX6[6:0]=seg5;4'h6: HEX6[6:0]=seg6;4'h7: HEX6[6:0]=seg7;4'h8: HEX6[6:0]=seg8;4'h9: HEX6[6:0]=seg9;4'ha: HEX6[6:0]=sega;4'hb: HEX6[6:0]=segb;4'hc: HEX6[6:0]=segc;4'hd: HEX6[6:0]=segd;4'he: HEX6[6:0]=sege;4'hf: HEX6[6:0]=segf;default:HEX6[6:0]=seg0;endcasealways @(posedge clk_r)case(a_r[7:4])4'h0: HEX7[6:0]=seg0;4'h1: HEX7[6:0]=seg1;4'h2: HEX7[6:0]=seg2;4'h3: HEX7[6:0]=seg3;4'h4: HEX7[6:0]=seg4;4'h5: HEX7[6:0]=seg5;4'h6: HEX7[6:0]=seg6;4'h7: HEX7[6:0]=seg7;4'h8: HEX7[6:0]=seg8;4'h9: HEX7[6:0]=seg9;4'ha: HEX7[6:0]=sega;4'hb: HEX7[6:0]=segb;4'hc: HEX7[6:0]=segc;4'hd: HEX7[6:0]=segd;4'he: HEX7[6:0]=sege;4'hf: HEX7[6:0]=segf;default:HEX7[6:0]=seg0;endcaseendmodule第二位数B模块:module regb (clk,clk_r,rst,sw_ab,b_r,HEX5,HEX4); input [7:0] sw_ab;input clk,clk_r,rst;output [7:0] b_r;reg [7:0] b_r;output reg[6:0] HEX5,HEX4;reg [3:0] cnt;always @(posedge clk or negedge rst)if(!rst) cnt<=1'd0;else if(cnt==5) cnt<=1'd0;else cnt<=cnt+1'd1;always @(posedge clk or negedge rst)if(!rst) b_r=0;else if(cnt==2) b_r=sw_ab;else b_r=b_r;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010,seg6=7'b0000010 ,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b0000011 ,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always @(posedge clk_r)case(b_r[3:0])4'h0: HEX4[6:0]=seg0;4'h1: HEX4[6:0]=seg1;4'h2: HEX4[6:0]=seg2;4'h3: HEX4[6:0]=seg3;4'h4: HEX4[6:0]=seg4;4'h5: HEX4[6:0]=seg5;4'h6: HEX4[6:0]=seg6;4'h7: HEX4[6:0]=seg7;4'h8: HEX4[6:0]=seg8;4'h9: HEX4[6:0]=seg9;4'ha: HEX4[6:0]=sega;4'hb: HEX4[6:0]=segb;4'hc: HEX4[6:0]=segc;4'hd: HEX4[6:0]=segd;4'he: HEX4[6:0]=sege;4'hf: HEX4[6:0]=segf;default:HEX4[6:0]=seg0;endcasealways @(posedge clk_r)case(b_r[7:4])4'h0: HEX5[6:0]=seg0;4'h1: HEX5[6:0]=seg1;4'h2: HEX5[6:0]=seg2;4'h3: HEX5[6:0]=seg3;4'h4: HEX5[6:0]=seg4;4'h5: HEX5[6:0]=seg5;4'h6: HEX5[6:0]=seg6;4'h7: HEX5[6:0]=seg7;4'h8: HEX5[6:0]=seg8;4'h9: HEX5[6:0]=seg9;4'ha: HEX5[6:0]=sega;4'hb: HEX5[6:0]=segb;4'hc: HEX5[6:0]=segc;4'hd: HEX5[6:0]=segd;4'he: HEX5[6:0]=sege;4'hf: HEX5[6:0]=segf;default:HEX5[6:0]=seg0;endcaseendmodule运算模块:module alur(clk,rst,alu_out,a_r,b_r,opcode,zero);output [7:0] alu_out;output zero;input [7:0] a_r,b_r;input [2:0] opcode;input clk,rst;reg [7:0] alu_out;reg [3:0] cnt;parameterquA=3'b000,quB=3'b001,ADD=3'b010,DEC=3'b011,ANDD=3'b100,XORR=3'b101,XOR=3'b110, NXOP=3'b111;assign zero=!a_r;always @(posedge clk or negedge rst)if(!rst) cnt<=1'd0;else if(cnt==5) cnt<=1'd0;else cnt<=cnt+1'd1;always @(posedge clk or negedge rst)if(!rst) alu_out=0;else if(cnt==3) begincasex(opcode)quA: alu_out<=a_r;quB: alu_out<=b_r;ADD: alu_out<=a_r+b_r;DEC: alu_out<=a_r-b_r;ANDD: alu_out<=a_r&b_r;XORR: alu_out<=a_r|b_r;XOR: alu_out<=a_r^b_r;NXOP: alu_out<=a_r^~b_r;default: alu_out<=8'bxxxx_xxxx;endcaseendelse alu_out=0;endmodule结果显示模块:module digital(clk_r,rst,alu_out,HEX1,HEX0);input [7:0] alu_out;input clk_r,rst;output reg[6:0] HEX1,HEX0;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010,seg6=7'b0000010 ,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b0000011 ,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always @(posedge clk_r)case(alu_out[3:0])4'h0: HEX0[6:0]=seg0;4'h1: HEX0[6:0]=seg1;4'h2: HEX0[6:0]=seg2;4'h3: HEX0[6:0]=seg3;4'h4: HEX0[6:0]=seg4;4'h5: HEX0[6:0]=seg5;4'h6: HEX0[6:0]=seg6;4'h7: HEX0[6:0]=seg7;4'h8: HEX0[6:0]=seg8;4'h9: HEX0[6:0]=seg9;4'ha: HEX0[6:0]=sega;4'hb: HEX0[6:0]=segb;4'hc: HEX0[6:0]=segc;4'hd: HEX0[6:0]=segd;4'he: HEX0[6:0]=sege;4'hf: HEX0[6:0]=segf;default: HEX0[6:0]=seg0;endcasealways @(posedge clk_r)case(alu_out[7:4])4'h0: HEX1[6:0]=seg0;4'h1: HEX1[6:0]=seg1;4'h2: HEX1[6:0]=seg2;4'h3: HEX1[6:0]=seg3;4'h4: HEX1[6:0]=seg4;4'h5: HEX1[6:0]=seg5;4'h6: HEX1[6:0]=seg6;4'h7: HEX1[6:0]=seg7;4'h8: HEX1[6:0]=seg8;4'h9: HEX1[6:0]=seg9;4'ha: HEX1[6:0]=sega;4'hb: HEX1[6:0]=segb;4'hc: HEX1[6:0]=segc;4'hd: HEX1[6:0]=segd;4'he: HEX1[6:0]=sege;4'hf: HEX1[6:0]=segf; default: HEX1[6:0]=seg0; endcaseendmodule五.仿真实现:整体图:波形图:六.硬件实现:1.引脚图:2.分析结果说明:开关0~2是算法选择,具体算法类型见设计功能第2项开关10~17数字输入,用8位二进制数表示两个十六进制数,每四位表示一位按键0是锁存及运算,当开关10~17输入一个数A时,按下按键0,数据就是锁存,再输入数就是数B,而当数据B也锁存后,再次按下按键0,就会显示运算结果按键1是复位键七.总结:通过这次FPGA实验课让我明白了真正的编程不像是那些C语言小程序那么简单,为了这次实验算是绞尽脑汁,最后为了读懂程序,还去专门找了Verilog语言辅导书,不管过程再怎么复杂曲折,总算是顺利的完成了实验任务,到了现在回顾为期6周的学习过程,也有一些时候是因为上课不认真,为后来的程序设计增加了难度,也有一些原因是因为自己本身能力不足导致设计接连失败,不得不说,也有一部分原因是因为学习实验室的器件不足,限制了实验设计的范围,也使实验难度增加。

试验一8位算术逻辑运算试验

实验一8位算术逻辑运算实验一、实验目的1、掌握算术逻辑运算器单元ALU(74LS181)的工作原理2、掌握简单运算器的数据传送通路组成原理。

2、验证算术逻辑运算功能发生器74LSl8l的组合功能。

4、按给定数据,完成实验指定书中的算术/逻辑运算二、实验内容1、实验原理实验中所用的运算器数据通路如图所示。

其中运算器由两片74LSl81以并/串形成8位字长的ALU构成。

运算器的输出经过一个三态门74LS245(U33)到ALUO1插座,实验时用8芯排线和内部数据总线BUSD0~D7插座BUSl~6中的任一个相连,内部数据总线通过LZDO~LZD7显示灯显示;运算器的两个数据输入端分别由二个锁存器74LS273(U29、U30)锁存,两个锁存器的输入并联后连至插座ALUBUS,实验时通过8芯排线连至外部数据总线EXD0~D7插座EXJl~EXJ3中的任一个;参与运算的数据来自于8位数据开并KD0~KD7,并经过一三态门74LS245(U51)直接连至外部数据总线EXD0~EXD7,通过数据开关输入的数据由LD0~LD7显示。

图中算术逻辑运算功能发生器74LS18l(U3l、U32)的功能控制信号S3、S2、Sl、S0、CN、M并行相连后连至SJ2插座,实验时通过6芯排线连至6位功能开关插座UJ2,以手动方式用二进制开关S3、S2、S1、S0、CN、M来模拟74LSl8l (U31、U32)的功能控制信号S3、S2、S1、S0、CN、M;其它电平控制信号LDDRl、LDDR2、ALUB’、SWB’、以手动方式用二进制开关LDDRl、:LDDR2、ALUB、SWB来模拟,这几个信号有自动和手动两种方式产生,通过跳线器切换,其中ALUB’、SWB’、为低电平有效,LDDRl、LDDR2为高电平有效。

另有信号T4为脉冲信号,在手动方式下进行实验时,只需将跳线器J23上T4与手动脉冲发生开关的输出端SD相连,按动手动脉冲开关,即可获得实验所需的单脉冲。

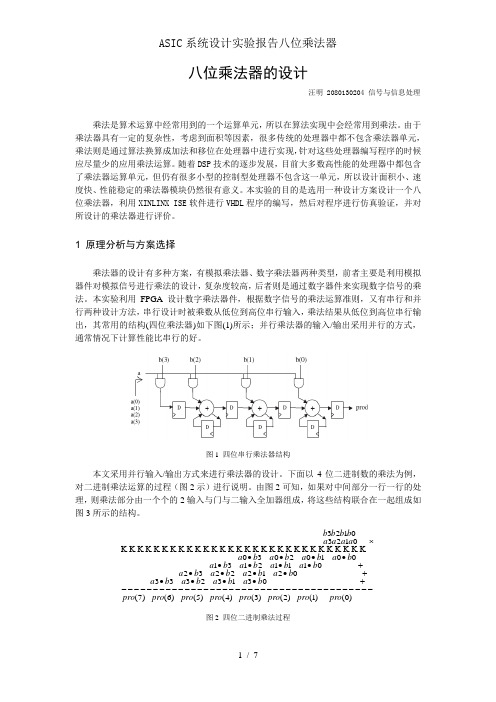

ASIC系统设计实验报告八位乘法器

八位乘法器的设计汪明 2080130204 信号与信息处理 乘法是算术运算中经常用到的一个运算单元,所以在算法实现中会经常用到乘法。

由于乘法器具有一定的复杂性,考虑到面积等因素,很多传统的处理器中都不包含乘法器单元,乘法则是通过算法换算成加法和移位在处理器中进行实现,针对这些处理器编写程序的时候应尽量少的应用乘法运算。

随着DSP 技术的逐步发展,目前大多数高性能的处理器中都包含了乘法器运算单元,但仍有很多小型的控制型处理器不包含这一单元,所以设计面积小、速度快、性能稳定的乘法器模块仍然很有意义。

本实验的目的是选用一种设计方案设计一个八位乘法器,利用XINLINX ISE 软件进行VHDL 程序的编写,然后对程序进行仿真验证,并对所设计的乘法器进行评价。

1 原理分析与方案选择乘法器的设计有多种方案,有模拟乘法器、数字乘法器两种类型,前者主要是利用模拟器件对模拟信号进行乘法的设计,复杂度较高,后者则是通过数字器件来实现数字信号的乘法。

本实验利用FPGA 设计数字乘法器件,根据数字信号的乘法运算准则,又有串行和并行两种设计方法,串行设计时被乘数从低位到高位串行输入,乘法结果从低位到高位串行输出,其常用的结构(四位乘法器)如下图(1)所示;并行乘法器的输入/输出采用并行的方式,通常情况下计算性能比串行的好。

图1 四位串行乘法器结构本文采用并行输入/输出方式来进行乘法器的设计。

下面以4位二进制数的乘法为例,对二进制乘法运算的过程(图2示)进行说明。

由图2可知,如果对中间部分一行一行的处理,则乘法部分由一个个的2输入与门与二输入全加器组成,将这些结构联合在一起组成如图3所示的结构。

)0()1()2()3()4()5()6()7(0313233302122232011121310010203001230123pro pro pro pro pro pro pro pro b a b a b a b a b a b a b a b a b a b a b a b a b a b a b a b a a a a a b b b b ----------------------------------------+••••+••••+••••••••⨯K K K K K K K K K K K K K K K K K K K K K K K K K K K K K K 图2 四位二进制乘法过程图3 四位二进制乘法结构图从图3可以看出,上述结构中顶层、底层、中间层分别采用不同的结构,而且中间层的三个层结构完全相同。

8位ALU算术逻辑单元verilog语言

理工大学城市学院FPGA实验报告实验容:8位ALU系别班级:电子1004班学号::日期:2013.4.14一.设计概述:一种基于可编程逻辑器件FPGA和硬件描述语言的8位的ALU的设计方法。

该ALU 采用层次设计方法,有寄存器模块、控制模块和显示模块组成,能实现8位无符号数的取值、加减和4种逻辑运算(与、或、异或、同或)。

该ALU在QuartusII软件环境下进行功能仿真,通过DE2验证。

二.设计功能:1、该处理器的数据宽度为8bit,可以实现算术加法、减法、逻辑与、逻辑或、逻辑非、逻辑与非、逻辑或非和逻辑异或等8种运算。

2、用选择端opcode [2:0] 选择8种运算,2个操作数分别是a_r [7:0]和b_r[7:0],运算结果是alu_out[7:0];并定义选择如下。

3、使用DE2板上的3个拨码开关设置当前ALU的运算功能,再由8个拨码开关给定数据A和数据B,由一个按键key手动提供脉冲。

三.设计方案:本设计共有5个模块。

1)脉冲输出器(key手动脉冲),计数依次产生4个脉冲到各个部件,第一个脉冲启动信号。

2)寄存器A,第二个脉冲来时锁存数据A,并在数码管上显示。

3)寄存器B,第三个脉冲来时锁存数据B,并在数码管上显示。

4)8位ALU,第四个脉冲来时进行运算,并锁存结果alu_out。

5)结果显示器,将结果显示通过DE2上的数码管显示。

四.程序分析:主程序模块:module alu8(clk,clk_r,rst,a,b,alu_out,opcode,sw_ab,HEX1, HEX0, HEX7, HEX6, HEX5, HEX4);input clk,rst,clk_r;input [7:0] sw_ab;input [2:0] opcode;output [6:0] HEX1, HEX0, HEX7, HEX6, HEX5, HEX4;output [7:0] a;output [7:0] b;output [7:0] alu_out;rega U1(.clk(clk),.rst(rst),.sw_ab(sw_ab),.a_r(a),.clk_r(clk_r),.HEX7(HEX7),. HEX6(HEX6)); regb U2(.clk(clk),.rst(rst),.sw_ab(sw_ab),.b_r(b),.clk_r(clk_r),.HEX5(HEX5),. HEX4(HEX4)); alur U3(.clk(clk),.rst(rst),.a_r(a),.b_r(b),.alu_out(alu_out),.opcode(opcode));digital U4(.clk_r(clk_r),.rst(rst),.alu_out(alu_out),.HEX1(HEX1),. HEX0(HEX0)); endmodule第一位数A模块:module rega (clk,clk_r,rst,sw_ab,a_r,HEX7,HEX6);input [7:0] sw_ab;input clk,clk_r,rst;output [7:0] a_r;reg [7:0] a_r;output reg[6:0] HEX7,HEX6;reg [3:0]t;always (posedge clk or negedge rst)if(!rst)t<=1'd0;else if(cnt==5)t<=1'd0;elset<=cnt+1'd1;always (posedge clk or negedge rst)if(!rst) a_r=0;else if(cnt==1) a_r=sw_ab;else a_r=a_r;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010, seg6=7'b0000010,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b00000 11,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always (posedge clk_r)case(a_r[3:0])4'h0: HEX6[6:0]=seg0;4'h1: HEX6[6:0]=seg1;4'h2: HEX6[6:0]=seg2;4'h3: HEX6[6:0]=seg3;4'h4: HEX6[6:0]=seg4;4'h5: HEX6[6:0]=seg5;4'h6: HEX6[6:0]=seg6;4'h7: HEX6[6:0]=seg7;4'h8: HEX6[6:0]=seg8;4'h9: HEX6[6:0]=seg9;4'ha: HEX6[6:0]=sega;4'hb: HEX6[6:0]=segb;4'hc: HEX6[6:0]=segc;4'hd: HEX6[6:0]=segd;4'he: HEX6[6:0]=sege;4'hf: HEX6[6:0]=segf;default:HEX6[6:0]=seg0;endcasealways (posedge clk_r)case(a_r[7:4])4'h0: HEX7[6:0]=seg0;4'h1: HEX7[6:0]=seg1;4'h2: HEX7[6:0]=seg2;4'h3: HEX7[6:0]=seg3;4'h4: HEX7[6:0]=seg4;4'h5: HEX7[6:0]=seg5;4'h6: HEX7[6:0]=seg6;4'h7: HEX7[6:0]=seg7;4'h8: HEX7[6:0]=seg8;4'h9: HEX7[6:0]=seg9;4'ha: HEX7[6:0]=sega;4'hb: HEX7[6:0]=segb;4'hc: HEX7[6:0]=segc;4'hd: HEX7[6:0]=segd;4'he: HEX7[6:0]=sege;4'hf: HEX7[6:0]=segf;default:HEX7[6:0]=seg0;endcaseendmodule第二位数B模块:module regb (clk,clk_r,rst,sw_ab,b_r,HEX5,HEX4); input [7:0] sw_ab;input clk,clk_r,rst;output [7:0] b_r;reg [7:0] b_r;output reg[6:0] HEX5,HEX4;reg [3:0]t;always (posedge clk or negedge rst)if(!rst)t<=1'd0;else if(cnt==5)t<=1'd0;elset<=cnt+1'd1;always (posedge clk or negedge rst)if(!rst) b_r=0;else if(cnt==2) b_r=sw_ab;else b_r=b_r;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010,seg6=7'b000001 0,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b00000 11,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always (posedge clk_r)case(b_r[3:0])4'h0: HEX4[6:0]=seg0;4'h1: HEX4[6:0]=seg1;4'h2: HEX4[6:0]=seg2;4'h3: HEX4[6:0]=seg3;4'h4: HEX4[6:0]=seg4;4'h5: HEX4[6:0]=seg5;4'h6: HEX4[6:0]=seg6;4'h7: HEX4[6:0]=seg7;4'h8: HEX4[6:0]=seg8;4'h9: HEX4[6:0]=seg9;4'ha: HEX4[6:0]=sega;4'hb: HEX4[6:0]=segb;4'hc: HEX4[6:0]=segc;4'hd: HEX4[6:0]=segd;4'he: HEX4[6:0]=sege;4'hf: HEX4[6:0]=segf;default:HEX4[6:0]=seg0;endcasealways (posedge clk_r)case(b_r[7:4])4'h0: HEX5[6:0]=seg0;4'h1: HEX5[6:0]=seg1;4'h2: HEX5[6:0]=seg2;4'h3: HEX5[6:0]=seg3;4'h4: HEX5[6:0]=seg4;4'h5: HEX5[6:0]=seg5;4'h6: HEX5[6:0]=seg6;4'h7: HEX5[6:0]=seg7;4'h8: HEX5[6:0]=seg8;4'h9: HEX5[6:0]=seg9;4'ha: HEX5[6:0]=sega;4'hb: HEX5[6:0]=segb;4'hc: HEX5[6:0]=segc;4'hd: HEX5[6:0]=segd;4'he: HEX5[6:0]=sege;4'hf: HEX5[6:0]=segf;default:HEX5[6:0]=seg0;endcaseendmodule运算模块:module alur(clk,rst,alu_out,a_r,b_r,opcode,zero);output [7:0] alu_out;output zero;input [7:0] a_r,b_r;input [2:0] opcode;input clk,rst;reg [7:0] alu_out;reg [3:0]t;parameterquA=3'b000,quB=3'b001,ADD=3'b010,DEC=3'b011,ANDD=3'b100,XORR=3'b101,XOR =3'b110,NXOP=3'b111;assign zero=!a_r;always (posedge clk or negedge rst)if(!rst)t<=1'd0;else if(cnt==5)t<=1'd0;elset<=cnt+1'd1;always (posedge clk or negedge rst)if(!rst) alu_out=0;else if(cnt==3) begincasex(opcode)quA: alu_out<=a_r;quB: alu_out<=b_r;ADD: alu_out<=a_r+b_r;DEC: alu_out<=a_r-b_r;ANDD: alu_out<=a_r&b_r;XORR: alu_out<=a_r|b_r;XOR: alu_out<=a_r^b_r;NXOP: alu_out<=a_r^~b_r;default: alu_out<=8'bxxxx_xxxx;endcaseendelse alu_out=0;endmodule结果显示模块:module digital(clk_r,rst,alu_out,HEX1,HEX0);input [7:0] alu_out;input clk_r,rst;output reg[6:0] HEX1,HEX0;parameter seg0=7'b1000000,seg1=7'b1111001,seg2=7'b0100100,seg3=7'b0110000,seg4=7'b0011001,seg5=7'b0010010,seg6=7'b000001 0,seg7=7'b1111000,seg8=7'b0000000,seg9=7'b0010000,sega=7'b0001000,segb=7'b00000 11,segc=7'b1000110,segd=7'b0100001,sege=7'b0000110,segf=7'b0001110;always (posedge clk_r)case(alu_out[3:0])4'h0: HEX0[6:0]=seg0;4'h1: HEX0[6:0]=seg1;4'h2: HEX0[6:0]=seg2;4'h3: HEX0[6:0]=seg3;4'h4: HEX0[6:0]=seg4;4'h5: HEX0[6:0]=seg5;4'h6: HEX0[6:0]=seg6;4'h7: HEX0[6:0]=seg7;4'h8: HEX0[6:0]=seg8;4'h9: HEX0[6:0]=seg9;4'ha: HEX0[6:0]=sega;4'hb: HEX0[6:0]=segb;4'hc: HEX0[6:0]=segc;4'hd: HEX0[6:0]=segd;4'he: HEX0[6:0]=sege;4'hf: HEX0[6:0]=segf;default: HEX0[6:0]=seg0;endcasealways (posedge clk_r)case(alu_out[7:4])4'h0: HEX1[6:0]=seg0;4'h1: HEX1[6:0]=seg1;4'h2: HEX1[6:0]=seg2;4'h3: HEX1[6:0]=seg3;4'h4: HEX1[6:0]=seg4;4'h5: HEX1[6:0]=seg5;4'h6: HEX1[6:0]=seg6;4'h7: HEX1[6:0]=seg7;4'h8: HEX1[6:0]=seg8;4'h9: HEX1[6:0]=seg9;4'ha: HEX1[6:0]=sega;4'hb: HEX1[6:0]=segb;4'hc: HEX1[6:0]=segc;4'hd: HEX1[6:0]=segd;4'he: HEX1[6:0]=sege;4'hf: HEX1[6:0]=segf; default: HEX1[6:0]=seg0; endcaseendmodule五.仿真实现:整体图:波形图:六.硬件实现:1.引脚图:2.分析结果说明:开关0~2是算法选择,具体算法类型见设计功能第2项开关10~17数字输入,用8位二进制数表示两个十六进制数,每四位表示一位按键0是锁存及运算,当开关10~17输入一个数A时,按下按键0,数据就是锁存,再输入数就是数B,而当数据B也锁存后,再次按下按键0,就会显示运算结果按键1是复位键七.总结:通过这次FPGA实验课让我明白了真正的编程不像是那些C语言小程序那么简单,为了这次实验算是绞尽脑汁,最后为了读懂程序,还去专门找了Verilog语言辅导书,不管过程再怎么复杂曲折,总算是顺利的完成了实验任务,到了现在回顾为期6周的学习过程,也有一些时候是因为上课不认真,为后来的程序设计增加了难度,也有一些原因是因为自己本身能力不足导致设计接连失败,不得不说,也有一部分原因是因为学习实验室的器件不足,限制了实验设计的围,也使实验难度增加。

计算机组成原理实验报告-八位补码加减法器的设计与实现

计算机科学与技术学院计算机组成原理实验报告书实验名称八位补码加/减法器的设计与实现班级学号姓名指导教师日期成绩实验1八位补码加/减法器的设计与实现一、实验目的1.掌握算术逻辑运算单元(ALU)的工作原理。

2.熟悉简单运算器的数据传送通路。

3.掌握8位补码加/减法运算器的设计方法。

4.掌握运算器电路的仿真测试方法二、实验任务1.设计一个8位补码加/减法运算器(1)参考图1,在QUARTUS II里输入原理图,设计一个8位补码加/减法运算器。

(2)创建波形文件,对该8位补码加/减法运算器进行功能仿真测试。

(3)测试通过后,封装成一个芯片。

2.设计8位运算器通路电路参考下图,利用实验任务1设计的8位补码加/减法运算器芯片建立运算器通路。

3.利用仿真波形,测试数据通路的正确性。

设定各控制信号的状态,完成下列操作,要求记录各控制信号的值及时序关系。

(1)在输入数据IN7~IN0上输入数据后,开启输入缓冲三态门,检查总线BUS7~BUS0上的值与IN0~IN7端输入的数据是否一致。

(2)给DR1存入55H,检查数据是否存入,请说明检查方法。

(3)给DR2存入AAH,检查数据是否存入,请说明检查方法。

(4)完成加法运算,求55H+AAH,检查运算结果是否正确,请说明检查方法。

(5)完成减法运算,分别求55H-AAH和AAH-55H,检查运算结果是否正确,请说明检查方法。

(6)求12H+34H-56H,将结果存入寄存器R0,检查运算结果是否正确,同时检查数据是否存入,请说明检查方法。

三、实验要求(1)做好实验预习,掌握运算器的数据传送通路和ALU的功能特性。

(2)实验完毕,写出实验报告,内容如下:①实验目的。

②实验电路图。

③按实验任务3的要求,填写下表,以记录各控制信号的值及时序关系。

表中的序号表示各控制信号之间的时序关系。

要求一个控制任务填一张表,并可用文字对有关内容进行说明。

⑤实验体会与小结。

四、实验预习内容1.实验电路设计原理及思路说明本实验利用基本逻辑门电路设计一位全加器(FA),如表1:法又可以实现减法,所以使用了一个M输入来进行方式控制加减。

计算机组成原理 运算器实验—算术逻辑运算实验

实验报告一、实验名称运算器实验—算术逻辑运算实验二、实验目的1、了解运算器的组成原理。

2、掌握运算器的工作原理。

3、掌握简单运算器的数据传送通路。

4、验证运算功能发生器(74LS181)的组合功能。

三、实验设备TDN-CM++计算机组成原理教学实验系统一套,导线若干。

四、实验原理实验中所用的运算器数据通路如图1-1所示。

其中两片74LSl81以串行方式构成8位字长的ALU,ALU的输出经过一个三态门(74LS245)和数据总线相连。

三态门由ALU-R控制,控制运算器运算的结果能否送往总线,低电平有效。

为实现双操作数的运算,ALU的两个数据输入端分别由二个锁存器DR1、DR2(由74LS273实现)锁存数据。

要将数据总线上的数据锁存到DRl、DR2中,锁存器的控制端LDDR1和DDR2必须为高电平,同时由T4脉冲到来。

数据开关(“INPUT DEVICE")用来给出参与运算的数据,经过三态(74LS245)后送入数据总线,三态门由SW—B控制,低电平有效。

数据显示灯(“BUS UNIT")已和数据总线相连,用来显示数据总线上的内容。

图中已将用户需要连接的控制信号用圆圈标明(其他实验相同,不再说明),其中除T4为脉冲信号外,其它均为电平信号。

由于实验电路中的时序信号均已连至“W/R UNIT”的相应时序信号引出端,因此,在进行实验时,只需将“W /R UNIT"的T4接至“STATE UNIT”的微动开关KK2的输入端,按动微动开关,即可获得实验所需的单脉冲。

ALU运算所需的电平控制信号S3、S2、S1、S0 、Cn、M、LDDRl、LDDR2、ALU-B、SW-B均由“SWITCH UNIT ”中的二进制数据开关来模拟,其中Cn、ALU—B、SW一B为低电平有效LDDR1、LDDR2为高电平有效。

对单总线数据通路,需要分时共享总线,每一时刻只能由一组数据送往总线。

五、实验内容1.输入数据通过三态门74LS245后送往数据总线,在数据显示灯和数码显示管LED上显示。

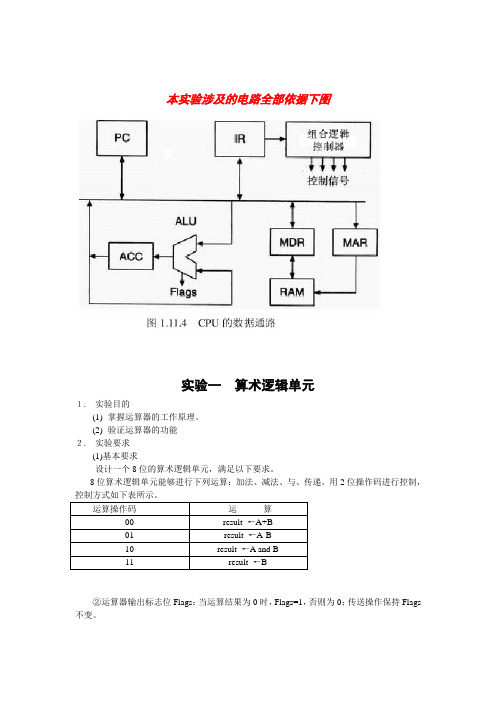

本实验涉及的电路全部依据下图

本实验涉及的电路全部依据下图实验一算术逻辑单元1.实验目的(1)掌握运算器的工作原理。

(2)验证运算器的功能2.实验要求(1)基本要求设计一个8位的算术逻辑单元,满足以下要求。

8位算术逻辑单元能够进行下列运算:加法、减法、与、传递。

用2位操作码进行控制,控制方式如下表所示。

运算操作码运算00 result ←A+B01 result ←A-B10 result ←A and B11 result ←B②运算器输出标志位Flags:当运算结果为0时,Flags=1,否则为0;传送操作保持Flags 不变。

实验二累加器与运算器的集成1.实验目的(1)了解累加器的用途。

(2)掌握将电路模块集成在一起的设计方法。

2.实验要求组,满足以下要求:①设计一个8位的累加器ACC,控制信号有异步复位信号reset和脉冲信号load_ACC②当复位信号reset=0时,将累加器ACC清零。

当load_ACC信号为上升沿时累加器接受数据。

③单独设计累加器,调试通过后再与实验1的运算器集成在一起。

④为观察仿真结果,在总模块中将累加器ACC的输出作为外部输出。

说明:仿真时要考虑输入数据、运算、累加器接受数据的时间先后顺序。

实验三寄存器组3.实验目的(1)了解寄存器组的用途及对CPU的重要性。

(2)掌握寄存器组的设计方法。

4.实验要求设计一个寄存器组,满足以下要求:①寄存器组中包括1个8位的PC寄存器(脉冲信号load_PC)和1个8位的MDR寄存器(脉冲信号load_MDR)、1个8位的MAR寄存器(脉冲信号load_MAR)、1个8位的IR寄存器(脉冲信号load_IR),每个寄存器都有异步复位信号reset和脉冲信号。

除MDR寄存器和PC寄存器外,其他寄存器可以直接使用实验1 的累加器器件。

②对于PC寄存器还有一个控制信号INC_PC,当脉冲信号有效时,若INC_PC=1则寄存器自动加1, 若INC_PC=0则寄存器接受数据。

DVCC-C8JH计算机组成原理实验指导书print

计算机组成原理实验指导书李翠玉主编沈阳工业大学2010年8月前言计算机组成原理是计算机科学与技术及相关专业的一门专业基础课,是工程性、技术性和实践性都非常强的一门课程,不仅在开展理论教学中讲授计算机的基本组成与工作原理的基础知识的同时,还要重视实践教学环节以训练学生一定的硬件实践动手能力。

计算机组成原理实验是利用中大规模集成电路等器件,对组成计算机的各相关部件进行逻辑设计、连线及测试。

在实验过程中,通过对各部件的实现原理进行逻辑设计,经过对器件的选择及连线、编译、仿真等工作后,对于设计出的各个部件进行正确性测试。

本实验实践环节在课程教学内容基础上提出基础实验和深度更广、综合性更强的设计性实验,要求学生通过基本实验验证运算器的算术逻辑运算、存储器的读写操作和寄存器、存储器、外设之间的数据传送通路等内容。

在设计性实验中给出设计要求和设计思路,由学生自行设计和调试,独立完成,加深学生对计算机的组成原理和指令在计算机中运行过程的理解,学生可体验设计一个简单计算机模型的方案、通过微指令、微程序的设计实现计算机的基本功能、不断调试最终达到设计要求的全过程。

课程实验环节的目的是帮助学生系统地掌握计算机中的运算器、寄存器、译码电路、存储器、和存储微指令的控制存储器等硬件组成的相关知识,实现知识融会贯通的目的。

通过实验使学生在实际操作中加深对计算机硬件组成与设计、指令的调试和运行维护等多方面的技能,同时训练一定的实验动手能力。

也使学生系统科学地受到分析问题和解决问题的训练,制定了一些实验项目。

本书由李翠玉主编,由于作者水平有限,加之时间紧迫,书中难免有疏漏之处,请广大读者批评指正。

作者2010年8月目录DVCC系列计算机组成原理系统概述 (1)第二章调试软件简介 (5)实验一 8位算术逻辑运算实验 (8)实验二带进位控制8位算术逻辑运算实验 (14)实验三 16位算术逻辑运算实验 (20)实验四移位运算器实验 (26)实验五存储器实验 (30)实验六数据通路实验 (35)实验七微控制器实验 (38)第一章DVCC系列计算机组成原理系统概述一、DVCC系列计算机组成原理系统简介DVCC系列计算机组成原理系统是江苏启动计算机公司研制的。

算术逻辑运算实验

算术逻辑运算实验实验目的:(1)了解运算器的组成与结构。

(2)掌握运算器的工作原理。

(3)学习运算器的设计方法。

(4)掌握简单运算器的数据传输通路。

(5)验证运算功能发生器74LS181的组合功能。

实验仪器设备:TDN-CM+或者TDN-CM++教学试验系统一套和导线若干。

实验原理:图1 运算器通路图运算器数据通路图如图1。

图中运算器主要由两片74LS181(功能见表1)芯片并/串形式构成,实现数据的运算,是运算器核心部件为。

图中是8位字长的运算器,其中左边为高4位,右边为低4位。

低位片的进位输出端Cn+4与高位的Cn相连,使进位可以输入高位片。

数据存储由DR1与DR2两个寄存器分别寄存,由锁存器74LS273实现。

高电平有效。

其控制端分别为LDDR1与LDDR2。

当T4脉冲到达时总线上的数据就被锁存进DR1与DR2中。

数据输出是在输出端连接一个三态门(用74LS245实现),当三态门控制端ALU-B为低电平的时候,运算结果即可以输出到总线。

否则为高阻态。

数据输入(实验板上INPUT DEVICE部分)用以给出参与运算的数据。

由一个三态门(74LS245)控制输入。

输入开关经三态门与内总线相连,当其控制信号SW-B为低电平的时,数据通过三态门送入内总线。

T4为脉冲信号,需要连接到“STATE UNIT”单元中的微动开关KK2。

S3、S2、S1、S0、Cn、M、LDDR1、LDDR2、ALU-B、SW-B各电平控制信号使用“SWITCH UNIT”单元中的二进制数据开关模拟,其中Cn、ALU-B、SW-B为低电平有效,LDDR1、LDDR2为高电平有效。

对于单总线的数据通路,实验时要分时控制总线,即当数据输入时(DR1、与DR2工作寄存器送入数据时),数据开关三态门打开(SW-B=0),同时保证运算输出三态门关闭(ALU-B=1);同样,当输出结果至总线时,数据输出三态门处于打开(ALU-B=0),同时保证数据输入三态门处于关闭(SW-B=1)状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3. 检验DR1和DR2置入的数据是否正确。

4. 验证74LS181的算术和逻辑运算功能。

5. 填写实验报告表3-1中的空白数据。

步骤2. 8位运算数据的置入

20/25

① 开始实验时,右下方的“停止运行控制”开关向上设置为 运行 状态;

② 调拨8位数据开关KD7-KD0为00110101(35H) ,准备向DR1送二 进制数据。

数据显示灯(BUS UNIT)已和数据总线相连, 用来显示数据总线内容。

6/25

74LS181芯片外特性

74LS181功能表

7/25

4位ALU

S3 S2 S1 S0

0 00 0 0 00 1 0 01 0 0 01 1 0 10 0 0 10 1 0 11 0 0 11 1 1 00 0 1 00 1 1 01 0 1 01 1 1 10 0 1 10 1 1 11 0 1 11 1

③ 数据输出三态缓冲器门控信号ALUB=1(关闭)。

④ 数据输入三态缓冲器门控信号 SWB=0(打开)。 ⑤ 数据锁存DRi控制信号LDDR1=1(打开),同时,LDDR2=0(关

闭)。 ⑥ 打入脉冲信号T4 ,将数据35H置入DR1。 ⑦ 重复步骤2-6,其中的步骤5 将LDDR1与LDDR2互换,即可将数据

48H置入DR2。

步骤2. 8位运算数据的置入

通过8位数据开关 KD0-KD7输入3458H

打 关关 打开 闭闭 开D输R出 入12控三制态信门号 LASDLWDUBRB==120=110

21/25

按下“复位”键 发出总清信号

打入脉冲信号T4

步骤3.检验DR1和DR2置入的数据

22/25

① 数据输出三态缓冲器门控信号ALUB=0(打开);

LASDLWDURBB跳12跳跳线线线拨拨拨左左左边边边

AR跳线器拨在左边,同时开关AR拨在“1”电平 17/25

AR开关拨“1”

AR跳线拨左边

四、实验连线-连线及跳线完毕

18/25

五、实验步骤

19/25

1. 连接线路,仔细检查核对后接通电源。

2. 用二进制数据开关KD7-KD0向DR1和DR2寄存 器置入8位运算数据。

23/25

验证DRபைடு நூலகம்2置入数据

打 关关开闭闭输D出入R12三控态制门 LASDLWDURBB=12==100

设置功能选择开关M=1 S3S2S1S0=101110,验证DR12置入数据

24/25

步骤4、5.验证74LS181的算术和逻辑运算功能

二、实验设备(平台)DVCC实验机平面图4/25

三、实验原理

5/25

运算器由两片74LS181以并/串形式构成8位字长 的ALU。

运算器的输出经过一个三态门(74LS245)和数 据总线相连。

运算器的两个数据输入端分别由两个锁存器 (74LS273)锁存。

锁存器的输入连至数据总线,数据开关(INPUT DEVICE)用来给出参与运算的数据,并经过一 三态门(74LS245)和数据总线相连。

F=A

M=1 (逻辑运算)

F=/A F=/(A+B) F=/A*B F=0 F=/(A*B) F=/B F=(A B) F=(A*/B) F=/A+B F=/(A B) F=B F=AB F=1 F=A+/B F=A+B F=A

运算器数据通路图(图3-1)

8/25

运算器的输入 由两个锁存器 74LS273锁存 并送入运算器

M=0(算术运算)

Cn=1 无进位

F=A

F=A+B

F=A+/B F=2的补 F=A加(A*/B) F=(A+B)加(A*/B) F=A减B减1 F=(A*/B)减1 F=A加A*B F=A加B F=(A+/B)加A*B F=A*B减1 F=A加A F=(A+B)加A F=(A+/B)加A F=A减1

运算器的数据来 源由8位数据开关

KD0-KD7输入

内部数据线通过 LZD0-D7显示灯显示

DR1 运算器的输出经过三态门 74LS245到BUSD0-D7

运算器的输入经过三态 门74LS245到外部数据 总线并送入锁存器锁存

DR2

运算器由两片 74LS181并/串而成

数据输入三态缓冲器门控信号 SWB ,数据输出三态缓冲器门控信号ALUB 数据锁存DR1打入脉冲信号 LDDR1 ,数据锁存DR2打入脉冲信号 LDDR2

运算器数据通路图(简化版)

9/25

四、实验连线

10/25

仔细查看试验箱,按以下步骤连线 1)ALUBUS连EXJ3 2) ALU01连BUS1 3) SJ2连UJ2 4) 跳线器J23上T4连SD 5) LDDR1,LDDR2,ALUB,SWB四个跳线器拨 在左边 6) AR跳线器拨在左边,同时开关AR拨在 “1”电平

四、实验连线-未连线

11/25

四、实验连线-ALUBUS连EXJ3

12/25

四、实验连线- ALU01连BUS1

13/25

四、实验连线- SJ2连UJ2

14/25

四、实验连线-跳线器J23上T4连SD

15/25

J23上的T4连SD

LDDR1,LDDR2,ALUB,SWB四个跳线器拨在左边 16/25

1/25

计算机组成原理实验

实验一

2/25

8位算术逻辑运算实验

一、实验目的 二、实验设备

三、实验原理 四、实验连线 五、实验步骤

一、实验目的

3/25

1. 掌握算术逻辑运算器单元ALU(74LS181) 的工作原理。

2. 掌握模型机运算器的数据传送通路组成原理。

3. 验证74LS181的组合功能。

4. 按给定数据,完成实验指导书中的算术/逻 辑运算。

Cn=0 有进位

F=A加1 F=(A+B)加1 F=(A+/B)加1

F=0 F=A加(A*B)加1 F=(A+B)加(A*/B)加1 F=A减B F=(A*/B) F=A加AB加1 F=A加B加1 F=(A+/B)加A*B加1

F=AB F=A加A加1 F=(A+B)加A加1 F=(A+/B)加A加1

② 数据输入三态缓冲器门控信号SWB=1(关闭);

③ 数据锁存DRi控制信号LDDR1、LDDR2=0(关闭)

④ 设置开关M 、开关S3、S2、S1、S0 相应值

如M=1,S3、S2、S1、S0=1111,验证8位数据 DR1;S3、S2、S1、S0=1010验证8位数据DR2。

步骤3.检验DR1和DR2置入的数据