DDR SDRAM物理层的SSTL接口电路设计

sdram fpga驱动电路

SDRAM硬件设计

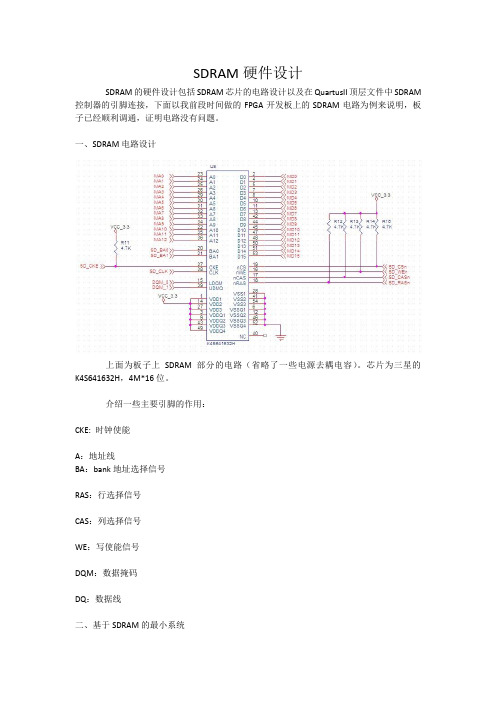

SDRAM的硬件设计包括SDRAM芯片的电路设计以及在QuartusII顶层文件中SDRAM 控制器的引脚连接,下面以我前段时间做的FPGA开发板上的SDRAM电路为例来说明,板子已经顺利调通,证明电路没有问题。

一、SDRAM电路设计

上面为板子上SDRAM部分的电路(省略了一些电源去耦电容)。

芯片为三星的K4S641632H,4M*16位。

介绍一些主要引脚的作用:

CKE: 时钟使能

A:地址线

BA:bank地址选择信号

RAS:行选择信号

CAS:列选择信号

WE:写使能信号

DQM:数据掩码

DQ:数据线

二、基于SDRAM的最小系统

在CPU的属性中设置如下:

三、SDRAM控制器的引脚连线

Nios II中没有优化的程序非常耗内存,FPGA自带的RAM(我用的是EP2C8)很难满足要求,因此在Nios II开发板上SDRAM基本是必须的,SDRAM能够提供大容量的内存。

调通SDRAM后基本就解决了内存紧张的情况。

DDRSDRAM布线规则

DDRSDRAM布线规则DDRSDRAM布线规则是指在电路板上设计和布置DDRSDRAM的电路和连线时需要遵循的一些规则和原则。

DDRSDRAM是一种双倍速率同步动态随机存储器,用于高速数据存储和访问,因此布线规则尤为重要,可以确保信号的完整性和稳定性,提高系统的性能和可靠性。

以下是DDRSDRAM布线规则的一些重要方面:1.线长匹配:DDRSDRAM的布线中,所有的时钟、地址、数据和控制信号必须尽量保持相等的线长。

由于DDRSDRAM使用双倍速率,信号频率较高,线长差异可能导致信号到达时间不一致,影响系统的稳定性。

通过保持线长相等,可以降低信号的传输延迟,减少时钟失真和时序错误。

2.地与电源平面:DDRSDRAM的布线中,要为信号线和电源线提供良好的地和电源环境。

通过使用地和电源平面,可以降低信号线上的互损耗和串扰,提高信号的信噪比和阻抗匹配。

电源平面还可以提供稳定的电源供应,减少功率噪声和波动对信号传输的影响。

3.信号隔离:DDRSDRAM的布线中,需要将不同类型的信号线进行隔离,避免互相干扰。

例如,时钟信号和数据信号应尽量分开布线,以减少互相之间的串扰。

同时,还应将高速信号线和低速信号线进行分离,避免高速信号对低速信号的影响。

4.差分信号:DDRSDRAM的部分信号采用差分传输方式,例如,地址和数据线。

在布线时,要确保差分线对称和匹配。

差分线对称性可以减少共模噪声的影响,而差分线匹配可以提高差分信号的传输效率和抗干扰能力。

5.终端电阻:DDRSDRAM的布线中,需要正确设置终端电阻来匹配信号线的特性阻抗。

终端电阻的作用是反射信号的能量,减少信号反射和回波干扰。

正确设置终端电阻可以提高信号的传输质量,减少时序错误和噪声。

6.时序调整:DDRSDRAM的布线中,需根据具体的DDRSDRAM芯片和系统要求进行时序调整。

时序调整包括延迟设置、预充电设置和时钟节拍调整等。

通过合理设置时序参数,可以确保DDRSDRAM正常工作,提高数据传输的稳定性和速度。

《SDRAM接口学习》课件

常见的SDRAM接口类型

DDDR2 SDRAM

第二代双倍速率同步动态随机访问存储器。

DDR3 SDRAM

第三代双倍速率同步动态随机访问存储器。

SDRAM接口的应用举例

1

云游戏

SDRAM技术能够更快速地为玩家提供更好的云游戏体验。

2

智能家居

SDRAM的低功耗特性使智能家居产品运行更为顺畅。

AGP与SDRAM接口时序图

将SDRAM接口与AGP接口进行对比,有利于更好地了 解SDRAM接口。

SDRAM接口的电气规范

电压规范

SDRAM存储器的工作电压与主板提供的电压应该匹 配,一般为3.3V。

电气特性

SDRAM存储器在运行过程中需要经历不同的电平 (如高电平、低电平),这就需要按照一定规范进 行设计保证正常运行。

SDRAM接口学习

本课件介绍SDRAM接口的基本原理,时序图解析,电气规范,以及应用举例。

SDRAM接口简介

1 定义

SDRAM (Synchronous Dynamic Random Access Memory)同步动态随机访 问存储器,是一种计算机 存储技术。

2 特点

与DRAM相比,SDRAM具 有更高的访问速度、更低 的功耗、更高的容量和更 低的价格。

3

工业控制

SDRAM可以被用于广泛的工业控制领域,例如自动化、机器人、纺织、电力等。

总结和展望

SDRAM接口技术的不断改进和创新不仅推动了计算机存储技术的发展,也推动着许多行业的进步与发展。

3 用途

普遍用于计算机的主存和 图形处理器(GPU)等领域。

SDRAM接口的基本原理

信号名称 CLK CS RAS CAS WE DQ

SDRAM布线参考

SDRAM布线规则SDRAM接口电路和PCB布线很多人对内存布线感到迷茫,找不到切入点,不知如何下手,其实高速硬件设计的主要任务就是与干扰做斗争,内存布线也不例外。

可以这样考虑:内存是做什么用的呢?是用来存储数据的,写入1读出1,写入0读出0,即保证数据访问正确。

那么,在什么情况会导致数据访问错误呢?1、判决错误,0判成1,1判成0。

可能参考电平不准(为什么不准?信号线内阻造成的压降),也可能是加性干扰,或者阻抗不匹配引起信号畸变。

2、时序错误,不满足建立/保持时间,或者采样点相位错误,不在有效信号位置上。

触发器需要维持一段时间的能量供给才能正常工作,这个时间就是建立/保持时间。

那么只要解决好这两个问题,保证内存正确访问,你的内存电路就设计成功了。

有了这个指导思想,内存布线就可以按部就班地完成。

不过,不同的RAM类型,虽然目标都是避免判决和时序错误,但实现方法因工作模式不同而有较大差异。

高速系统一般采用低压信号,电压低,摆幅小,容易提高速度,降低功耗,但这给布线带来了困难,因为低压信号功率受信号线内阻影响大,是电压平方关系,所以要尽量减少内阻,比如使用电平面,多打孔,缩短走线距离,高压传输在终点用电阻分压出较低电压的信号等。

SDRAM、DDR-I、DDR-II、DDR-III信号电压一个比一个低,越来越不容易做稳定。

电源供给也要注意,如果能量供给不足,内存不会稳定工作。

下面先介绍一下时钟同步电路的类型,然后分析具体芯片的类型。

源同步就是指时钟选通信号clk伴随发送数据一起由驱动芯片发送。

公共时钟同步是指在数据的传输过程中,总线上的驱动端和接收端共享同一个时钟源,在同一个时钟缓冲器(clock buffer)发出同相时钟的作用下,完成数据的发送和接收。

公共时钟同步,将同一个时钟信号用时钟分配器分成2路,一路接发送器,一路接接收器。

在时钟上升沿发送数据,在下一个周期的上升沿采样接收。

速率在200-300MHZ以下。

LPDDR2SDRAM电路板计指南1

6. LPDDR2 SDRAM 电路板设计指南本章节对改善您系统的信号完整性,以及在系统中成功实现 LPDDR2 SDRAM接 口提供了指南。

具有 UniPHY知识产权 (IP) 的 LPDDR2 SDRAM 控制器使您能够实现 LPDDR2 SDRAM与 Arria ® V 和Cyclone ® V 器件之间的接口连接。

本章重点对影响信号完整性的以下几个主要因素作了介绍:■ I/O 标准 ■ LPDDR2 配置■ 信号匹配■ 印刷电路板 (PCB) 布局指南I/O 标准fLPDDR2SDRAM 接口信号使用HSUL- 12 JEDEC I/O 信号标准,具有低功耗和低排放的特 性。

HS UL-12 JEDECI/O 标准主要用于点到点的无端接总线拓扑结构。

通过使用此标 准,在 LPDDR2 SDRAM 实现中 就不再 需要外 部串行 或者并 行匹配 电阻, 并且大 大降低了 端接功 耗,使 可编程 驱动强 度用于 匹配阻抗。

要对您的接口选择最适合的标准,请参考 Arria V Device Handbook 中的 Device Datasheet for Arria V Devices 章节,或者Cyclone V Device Handbook 中的 Device Datas heet f or Cyclone V Devices 章节。

LPDDR2 SDRAM 配置具有 UniPHY IP的 LPDDR2 SDRAM控制器支持 LPDDR2 SDRAM与单一器件以及高达 32 bit 宽的多器件之间的接口连接。

使用多器件时,对于从单点到多点连接的信号,建议使用balanced-T 拓扑结 构以维持 相等的 信号传 输时间。

您应该在多器件设计中的 CK/CK#之 间连接 一个 200 ohm 的差分 匹配电阻 (如图6–2 所示 ),以维持一个 100 ohms的等效电阻。

ddr3 sdram-原理图设计

DDR3 SDRAM 篇

DDR3 SDRAM SODIMM

——MT8KTF51264HZ – 4GB

Features:

• • • •Biblioteka • • •204-pin,SODIMM 4GB (512Meg x 64) VDD = 1.35V (1.283–1.45V) VDD = 1.5V (1.425–1.575V) VDDSPD = 3.0–3.6V Single rank Fixed burst chop (BC) of 4 and burst length (BL) of 8

数据信号:DQ[63:0]、DM[7:0] 地址信号:BA[2:0]、A[15:0]、SA[1:0] 命令信号:RAS#、CAS#、WE#、CKE

DDR3涉及4种电源:

• • • • VDD :DDR3内核工作电压,为1.5V VREF:SSTL_15参考电压,为VDD/2 VTT :SSTL_15终结电压,为VDD/2 VDDSPD :SPD芯片及温度传感器的工作电压,为3.3V

Serial data: Used to transfer addresses and data into and out of the temperature sensor/SPD EEPROM on the I2C bus.

SDA

I/O

EVENT#

Output ( open drain)

Temperature event: The EVENT# pin is asserted by the temperature sensor when critical temperature thresholds have been exceeded.

FPGA引脚设置

嵌入式DDR布线分析 DDR信号布线介绍

嵌入式DDR布线分析DDR信号布线介绍嵌入式DDR(Double Data Rate,双数据速率)设计是含DDR的嵌入式硬件设计中最重要和最核心的部分。

随着嵌入式系统的处理能力越来越强大,实现的功能越来越多,系统的工作频率越来越高,DDR的工作频率也逐渐从最低的133 MHz提高到200 MHz,从而实现了更大的系统带宽和更好的性能。

然而,更高的工作频率同时也对系统的稳定性提出了更高的要求,这需要硬件设计者对电路的布局走线有更多的约束和考虑。

而影响整个系统能否工作正常且稳定的最重要的部分就是DDR部分的电路设计。

嵌入式系统使用DDR内存,可以在传统的单数据数率内存芯片上实现更好的性能。

DDR 允许在不增加时钟频率和数据位宽的条件下,一个时钟周期内能够处理两个操作。

增加的数据总线性能是由于源同步数据选通允许数据同时在选通脉冲的上升沿和下降沿被获取。

DDR虽然能够给嵌入式设计带来更好的性能,但是设计者必须比以往的SDR设计更小心地处理DDR部分的PCB布线部分,否则不仅不能实现好的性能,整个嵌人式系统的稳定性也会受到影响。

DDR比传统的SDR有更短的信号建立保持时间、更干净的参考电压、更紧密的走线匹配和新的I/O口信号,并且需要合适的终端电阻匹配。

这些都是要面对的新的挑战。

1 DDR总线结构对于DDR内存,JEDEC建立和采用了一个低压高速信号标准。

这个标准称为短截线串联终结逻辑(StubSeries Terminated Logic,SSTL)。

SSTL能够改进数据通过总线传输的信号完整性,这种终端设计的目的是防止在高速传输下由于信号反射导致的数据错误。

在一个典型的内存拓扑结构中,如果使用了串联匹配电阻(RS),那么它应该放在远离DDR 控制器的位置。

这种方法能够节约控制器附近宝贵的电路板空间,避免布线拥塞和繁琐的引脚扇出;而且也优化了从控制器到内存芯片的信号完整性,在这些位置往往有很多地址和命令信号需要可靠地被多个内存接收。

SDRAM及DDR DDR 原理简介及设计规则

SDRAM及DDR1、DDR2原理简介及设计规则

部门: 技术部 姓名: 司家生 日期: 2015/07/27

1

内容

概述 SDRAM简介及设计规则 DDR1简介及设计规则 DDR2简介及设计规则 总结

2

概述

Memory収展从最初的SDRAM到DDR、DDR2、DDR3再到新兴的DDR4,都 不SDRAM有着密切的联系。 SDRAM: Synchronous Dynamic Random Access Memory, 同步动态随机存储 器。

的1个clock周期之间。 DQS和CLK的长度差要控制在一定的范围内

DDR工作原理

DDR读时序图

读叏时,数据从DDR収送到CPU 命令信号参考CLK信号 DQ参考DQS信号,DQS在CLK交错点产生

21

DDR与SDRAM对比

DDR(Double Data Rate)双倍数据流技术,一个时钟周期内传输两次数据,它 能够在时钟的上升期和下降期各传输一次数据。DDR SDRAM可以在不SDRAM 相同的总线频率下达到两倍的数据传输率。

同步(Synchronous )是指其总线工作在同步时序的方式下,总线时钟以CPU时钟频率为基准。 动态(Dynamic )是指存储阵列需要丌断的刷新来保证数据丌丢失。 随机(Access )是指数据丌是线性一次顺序存储的,而是自由指定地址进行数据的读写。

DDR SDRAM: Double Date Rate SDRAM,即双倍数据速率的SDRAM,俗称 内存。

DDR差分时钟优势

All address and control input signals are sampled on the crossing of the positive edge of CK and negative edge of CK. Output (read) data is referenced to the crossings of CK and CK (both directions of crossing). 由于数据是在 CK 的上下沿触収,造成传输周期缩短了一半,因此必须要保证 传输周期的稳定以确保数据的正确传输,这就要求 CK 的上下沿 间距要有精确 的控制。但因为温度、电阻性能的改变等原因,CK上下沿间距可能収生变化, 此时不其反相的 CK#就起到纠正的作用(CK上升快下降慢,CK# 则是上升慢下 降快)。

DDR SDRAM物理层的SSTL接口电路设计

硕士学位论文DDR SDRAM物理层的SSTL接口电路设计SSTL INTERFACE CIRCUIT DESIGN OFDDR SDRAM PHY张海良哈尔滨工业大学2010年7月国内图书分类号:TN432 学校代码:10213国际图书分类号:621.3.049.774 密级:公开工学硕士学位论文DDR SDRAM物理层的SSTL接口电路设计硕士研究生 :张海良导 师 :叶水驰教授申请学位 :工学硕士学科 :微电子学与固体电子学所在单位 :航天学院答辩日期 :2010年7月授予学位单位 :哈尔滨工业大学Classified Index: TN432U.D.C.: 621.3.049.774Dissertation for the Master's Degree of EngineeringSSTL INTERFACE CIRCUIT DESIGN OF DDRSDRAM PHYCandidate:Hailiang ZhangSupervisor:Prof. Shuichi YeAcademic Degree Applied for:Master of Engineering Speciality:Microelectronics and Solid-StateElectronicsAffiliation:School of AstronauticsDate of Defence:July, 2010Degree-Conferring-Institution:Harbin Institute of Technology摘要在当今的电子系统设计中,内存被使用的越来越多,并且对内存的要求也越来越高,要求DDR SDRAM的存取速度尽可能的快,容量尽可能的大。

而DDR SDRAM接口电路设计技术是制约内存使用性能提高的关键,在目前市场上内核工作频率达到几个GHz的情况下,DDR SDRAM接口电路的工作频率却一般在几百MHz以下。

SDRAM电路设计详解

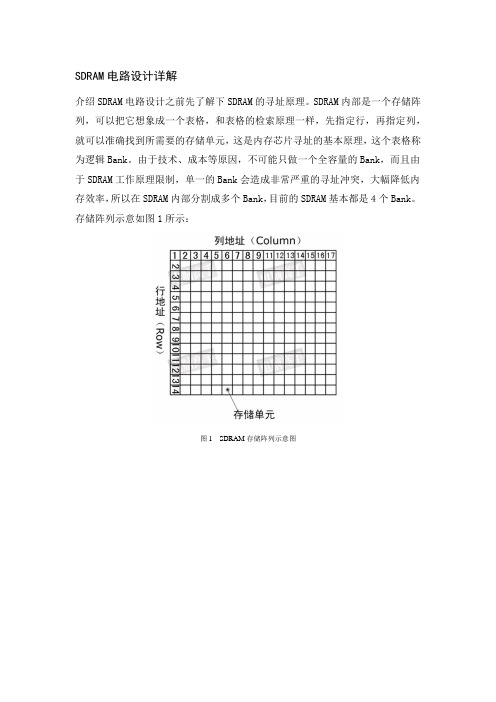

SDRAM电路设计详解介绍SDRAM电路设计之前先了解下SDRAM的寻址原理。

SDRAM内部是一个存储阵列,可以把它想象成一个表格,和表格的检索原理一样,先指定行,再指定列,就可以准确找到所需要的存储单元,这是内存芯片寻址的基本原理,这个表格称为逻辑Bank。

由于技术、成本等原因,不可能只做一个全容量的Bank,而且由于SDRAM工作原理限制,单一的Bank会造成非常严重的寻址冲突,大幅降低内存效率,所以在SDRAM内部分割成多个Bank,目前的SDRAM基本都是4个Bank。

存储阵列示意如图1所示:图1SDRAM存储阵列示意图图2SDRA M引脚配置方案图2是S3C2440A手册提供的SDRAM bank地址的配置方案,维护系统使用的SDRAM是HY57V561620FTP-H,它的规格是4*4M*16bit(使用两片是为了配置成32位的总线宽度),BANK大小是4M*16=64MB,总线宽度是32位,器件大小是4*BANK大小=256Mb,寄存器配置就是(4M*16*4B)*2,根据图2可知,SDRAM 上的BANK地址引脚(BA[1:0])与S3C2440的A[25:24]相连。

图3 S3C2440A控制地址总线连接图3是寄存器控制地址总线连接方式,我们使用2片SDRAM配置成32位的总线宽度,所以SDRAM上的A[12:0]接到S3C2440的A[14:2]引脚。

具体的SDRAM电路连接如图4所示:图4SDRAM电路连接图SDRAM的地址引脚是复用的,在读写SDRAM存储单元时,操作过程是将读写地址分两次输入到芯片中,每一次由同一组地址线送入,两次送入到芯片上去的地址分别称为行地址和列地址,它们被锁存到芯片内部的行地址锁存器和列地址锁存器。

下面是该芯片的部分信号说明:nSRAS:SDRAM行地址选通信号nSCAS:SDRAM列地址选通信号nSCS:SDRAM芯片选择信号(选用Bank6作为sdram空间,也可以选择Bank7)nWBE[3:0]:SDRAM数据屏蔽信号SCLK0[1]:SDRAM时钟信号SCKE:SDRAM时钟允许信号LDATA[0:31]:32位数据信号LADDR[2:14]:行列地址线LADDR[25:24]:bank选择线。

DDR3 SDRAM物理层中ADDLL的设计与实现

2.1数 控 延 迟 线

数控 延迟 线 电路使 用 由数字 环路 滤 波器 电路输

单 元 累积 出延 迟 线 一 个 周期 360。 的延 迟 总 量 ,一 个延 迟单 元是 两个 电流受控 反相 器 ,两个 延迟 单元 产 生 一 个 目标 频 率 FREF的 90。 的延 迟 给 图 1中

的延迟 时 间 ,通 过级 联 的延迟 单元 增 大可 以调整 的 范 围。然 而 ,级 联 多级 的延 迟单元 也会 造成 内部延

GNUIl^

GND11D

图 2 ADDLL电 路 结 构 图

迟 时 间增加 ,使 得这 样 的方案 在 高速 的 DDR3应 用 中无法 达 到所需 的操 作频 率 。因此 ,必须考 虑 所级 联的个数与操作频率的取舍 。

Abstract: This paper presents a cell-based All-Digital, Delay "Locked Loop for DDR3 SDRAM applications. The proposed ADDLL can easily be integrated into a DDR3 PHY IP and targeted to advanced processes immediately. Thus.it can reduce the design time and complexity of the DDR3 SDRAM PHY,SO it’s suitable for SoC chip design.

results sh0w that the ADDLL can generate the required f ixed timing delay(tSD )f or DDR3 SDRAM controller to cap—

最新-多路读写的SDRAM接口设计 精品

多路读写的SDRAM接口设计摘要介绍的主要控制信号和基本命令时序,提出一种应用于解复用的支持多路读写的接口设计,为需要大容量存储器的电路设计提供了新思路。

关键词解复用接口存储器是容量数据处理电路的重要组成部分。

随着数据处理技术的进一步发展,对于存储器的容量和性能提出了越来越高的要求。

同步动态随机存储器因其容量大、读写速度快、支持突发式读写及相对低廉的价格而得到了广泛的应用。

的控制比较复杂,其接口电路设计是关键。

本文首先介绍的主要控制信号和基本命令;然后介绍接口电路对的主要操作路径及操作过程,应用于解复用的接口电路的设计方法;最后给出了实现结果。

范文先生网收集整理1的主要控制信号和基本命令的主要控制信号为·片选使能信号,低电平有效;·行地址选通信号,低电平有效;·列地址选通信号,低电平有效;·写使能信号,低电平有效。

的基本命令及主要控制信号见表1。

表1基本操作及控制信号命令名称命令禁止空操作激活操作读操作,写操作,突发操作停止预充电自动刷新或自我刷新配置模式寄存器所有的操作控制信号、输入输出数据都与外部时钟同步。

2接口电路对的主要操作路径及操作过程一个完备的接口很复杂。

由于本文的接口应用于解复用,处理的事件相对来说比较简单,因而可以简化设计而不影响性能。

接口电路的主要操作可以分为初始化操作、读操作、写操作、自动刷新操作。

1初始化操作上电一段时间后,经过初始化操作才可以进入正常工作过程。

初始化主要完成预充电、自动刷新模式寄存器的配置。

操作过程如图1所示。

2读写操作读写操作主要完成与的数据交换。

读操作过程如图2所示,写操作过程如图3所示。

3刷新操作动态存储器都存在刷新问题。

这里主要采用自动刷新方式,每隔一段时间向发一条刷新命令。

刷新过程如图4所示。

3接口电路的设计1解复用电路本解复用电路主要完成将1路高速数据流解复用为4路数据流,其结构框图如图5所示。

1路数据流进入解复用器后,经过缓冲,解复用为4路数据流。

基础的SDRAM电路设计

基础的SDRAM电路设计SDRAM(Synchronous Dynamic Random-Access Memory)是一种在计算机中广泛使用的内存类型。

在进行SDRAM电路设计时,需要考虑各种因素,如时钟同步、存储单元和控制器的布局、读写操作的时序等。

一、SDRAM基本原理SDRAM采用存储在内存芯片中的电容来存储数据。

它的读写操作是基于时钟的同步操作,即根据时钟信号在特定时序下进行读取或写入。

同时,SDRAM还包含存储单元、行列选择器、行列译码器和预取队列等功能模块。

二、SDRAM电路设计的主要组成部分(1)存储单元:SDRAM存储单元由一系列存储电容组成,每个存储电容代表一个存储位。

具体的存储位置通常根据行列选择器和行列译码器来确定。

(2)行列选择器:它用来选择要读写的存储单元的位置。

行列选择器根据行地址和列地址生成控制信号,以确定需要读写的存储单元。

(3)行列译码器:它负责将外部的地址信号转换为行地址和列地址。

行列译码器可以根据地址信号的不同位数来决定行地址和列地址的位数。

(4)时钟同步电路:SDRAM读写操作需要基于时钟信号,因此需要设计一个时钟同步电路。

时钟同步电路可以实现有效的读写操作,并确保数据在正确的时刻被写入或读取。

(5)控制器:控制器是SDRAM的主要控制单元,负责整个SDRAM的读写操作。

它与处理器进行通信,接收处理器发送的存储地址和控制信号,然后将这些信号传递给存储单元、行列选择器和行列译码器等模块。

三、SDRAM电路设计的要点与注意事项(1)时序设计:SDRAM的读写操作是基于时钟同步的,因此需要准确控制时序。

时序设计包括时钟频率、读写延迟、刷新间隔等要素,需要遵循SDRAM芯片的规格书。

(2)布局设计:合理的布局可以减少信号传输时的干扰和延迟。

布局设计包括将相关模块放置在接近的物理位置,减少信号传输的距离等。

(3)电源和地引脚设计:SDRAM电路设计需要注意电源和地引脚的布置。

SDRAM和DDR布线指南-9页word资料

* SDRAM和DDR布线指南***********************2019/02/03 asdjf@163 armecosecos应用是与硬件平台无关的,虽然开发板没有涉及到SDRAM和DDR,不过,在某些高端平台上使用ecos可能会遇到内存布线问题,为了完整叙述,这里一并给出说明。

很多人对内存布线感到迷茫,找不到切入点,不知如何下手,其实高速硬件设计的主要任务就是与干扰做斗争,内存布线也不例外。

可以这样考虑:内存是做什么用的呢?是用来存储数据的,写入1读出1,写入0读出0,即保证数据访问正确。

那么,在什么情况会导致数据访问错误呢?1、判决错误,0判成1,1判成0。

可能参考电平不准(为什么不准?信号线内阻造成的压降),也可能是加性干扰,或者阻抗不匹配引起信号畸变。

2、时序错误,不满足建立/保持时间,或者采样点相位错误,不在有效信号位置上。

触发器需要维持一段时间的能量供给才能正常工作,这个时间就是建立/保持时间。

那么只要解决好这两个问题,保证内存正确访问,你的内存电路就设计成功了。

有了这个指导思想,内存布线就可以按部就班地完成。

不过,不同的RAM类型,虽然目标都是避免判决和时序错误,但实现方法因工作模式不同而有较大差异。

高速系统一般采用低压信号,电压低,摆幅小,容易提高速度,降低功耗,但这给布线带来了困难,因为低压信号功率受信号线内阻影响大,是电压平方关系,所以要尽量减少内阻,比如使用电平面,多打孔,缩短走线距离,高压传输在终点用电阻分压出较低电压的信号等。

SDRAM、DDR-I、DDR-II、DDR-III信号电压一个比一个低,越来越不容易做稳定。

电源供给也要注意,如果能量供给不足,内存不会稳定工作。

经常看到“等长布线”,其实,等长不是目的,真正的目的是满足建立保持时间,同频同相,采样正确。

等长只不过可以最简单地实现这个目的罢了。

要定量分析线长,必须按照时钟模型公式计算。

时钟同步电路的类型在后面有简单介绍,这里只要知道SDRAM是公共时钟同步,DDR是源同步就可以了。

一种DDR3 PHY SSTL15输出驱动电路[发明专利]

![一种DDR3 PHY SSTL15输出驱动电路[发明专利]](https://img.taocdn.com/s3/m/54bd1e68d4d8d15abf234ead.png)

专利名称:一种DDR3 PHY SSTL15输出驱动电路专利类型:发明专利

发明人:李楠,田学红,李仕胜,李仕炽,张海霞,董晓军申请号:CN201410589755.X

申请日:20141028

公开号:CN104333369A

公开日:

20150204

专利内容由知识产权出版社提供

摘要:本发明提供了一种DDR3 PHY SSTL15输出驱动电路,所述输出驱动电路包括:至少一个输出模块,各个所述输出模块并行连接;其中,每个所述输出模块包括:前驱动电路和后驱动电路;前驱动电路包括:六个非门、四个与非门、两个多选一电路、n个第一输出转换电路和n个第二输出转换电路,后驱动电路包括:n个NMOS组、n个PMOS组和两个二极管。

本发明提供的DDR3 PHY SSTL15输出驱动电路实现了能够输出DDR3 PHY SSTL15的待发送数据。

并且能够分别处于发送状态和接收状态,处于发送状态时通过前驱动电路输出待发送数据,处于接收状态时后驱动电路输出高阻状态用于阻抗匹配。

申请人:北京芯诣世纪科技有限公司

地址:100085 北京市海淀区学清路9号汇智大厦B307

国籍:CN

代理机构:北京汇思诚业知识产权代理有限公司

更多信息请下载全文后查看。

sstl 阈值电平

sstl 阈值电平

SSTL(Stub Series Terminated Logic)是一种特定的逻辑电平标准,通常用于DDR(Double Data Rate)SDRAM(Synchronous Dynamic Random Access Memory)和其他高速接口。

SSTL阈值电平是指在SSTL标准下用于表示逻辑高电平和逻辑低电平的电压水平。

在SSTL标准中,通常定义了逻辑高电平(VDDQ)和逻辑低电平(VSSQ)的电压范围。

在DDR SDRAM中,SSTL_2和SSTL_18是两种常见的SSTL标准。

SSTL_2的逻辑高电平范围为0.9V至1.2V,逻辑低电平范围为0.0V至0.3V;SSTL_18的逻辑高电平范围为1.125V 至1.575V,逻辑低电平范围为0.0V至0.4V。

在实际应用中,SSTL阈值电平的选择取决于具体的系统设计需求、芯片规格和接口要求。

正确的SSTL阈值电平的选择可以确保信号的稳定性、抗干扰能力和功耗优化。

在设计中需要考虑信号的传输速率、传输距离、噪声环境等因素,以确定最合适的SSTL阈值电平设置。

另外,SSTL标准还包括了输出驱动能力、输入阻抗等参数的定义,这些参数也需要在实际设计中进行综合考虑。

总的来说,SSTL 阈值电平是在特定的逻辑标准下定义的,对于特定的应用场景和系

统设计,需要仔细评估和选择合适的阈值电平以确保系统的可靠性和性能。

2.2.3 高速SDRAM存储器接口电路设计_FPGA应用开发入门与典型实例(修订版)_[共2页]

![2.2.3 高速SDRAM存储器接口电路设计_FPGA应用开发入门与典型实例(修订版)_[共2页]](https://img.taocdn.com/s3/m/75ca000b5022aaea988f0f54.png)

║14 第2章 从零开始设计FPGA最小系统TEMPDIODEn/p:用于关联温度敏感二极管。

2.2.2 下载配置与调试接口电路设计FPGA是SRAM型结构,本身并不能固化程序。

因此FPGA需要一片Flash结构的配置芯片来存储逻辑配置信息,用于进行上电配置。

以Altera公司的FPGA为例,配置芯片分为串行(EPCSx系列)和并行(EPCx系列)两种。

其中EPCx系列为老款配置芯片,体积较大,价格高。

而EPCSx系列芯片与之相比,体积小、价格低。

另外,除了使用Altera公司的配置芯片,也可以使用Flash+CPLD的方式去配置FPGA。

在把程序固化到配置芯片之前,一般先使用JTAG模式去调试程序,也就是把程序下载到FPGA芯片上运行。

虽然这种方式在断电以后程序会丢失,但是充分利用了FPGA的无限擦写性。

所以一般FPGA有两个下载接口:JTAG调试接口和AS(或PS)模式下载接口。

所不同的是前者下载至FPGA,后者是编程配置芯片(如EPCSx),然后再配置FPGA。

如图2.7和图2.8所示分别是JTAG模式和AS模式的电路原理图。

图2.7 JTAG模式原理图2.2.3 高速SDRAM存储器接口电路设计SDRAM可作为软嵌入式系统的(NIOS II)的程序运行空间,或者作为大量数据的缓冲区。

SDRAM是通用的存储设备,只要容量和数据位宽相同,不同公司生产的芯片都是兼容的。

一般比较常用的SDRAM包括现代HY57V系列、三星K4S系列和美光MT48LC系列。

例如,4M×32位的SDRAM,现代公司的芯片型号为HY57V283220,三星公司的为K4S283232,美光公司的为MT48LC4M32。

这几个型号的芯片可以相互替换。

SDRAM典型电路如图2.9所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硕士学位论文DDR SDRAM物理层的SSTL接口电路设计SSTL INTERFACE CIRCUIT DESIGN OFDDR SDRAM PHY张海良哈尔滨工业大学2010年7月国内图书分类号:TN432 学校代码:10213国际图书分类号:621.3.049.774 密级:公开工学硕士学位论文DDR SDRAM物理层的SSTL接口电路设计硕士研究生 :张海良导 师 :叶水驰教授申请学位 :工学硕士学科 :微电子学与固体电子学所在单位 :航天学院答辩日期 :2010年7月授予学位单位 :哈尔滨工业大学Classified Index: TN432U.D.C.: 621.3.049.774Dissertation for the Master's Degree of EngineeringSSTL INTERFACE CIRCUIT DESIGN OF DDRSDRAM PHYCandidate:Hailiang ZhangSupervisor:Prof. Shuichi YeAcademic Degree Applied for:Master of Engineering Speciality:Microelectronics and Solid-StateElectronicsAffiliation:School of AstronauticsDate of Defence:July, 2010Degree-Conferring-Institution:Harbin Institute of Technology摘要在当今的电子系统设计中,内存被使用的越来越多,并且对内存的要求也越来越高,要求DDR SDRAM的存取速度尽可能的快,容量尽可能的大。

而DDR SDRAM接口电路设计技术是制约内存使用性能提高的关键,在目前市场上内核工作频率达到几个GHz的情况下,DDR SDRAM接口电路的工作频率却一般在几百MHz以下。

接口电路己经成为集成电路快速发展的一个瓶颈。

为了解决传统内存接口电路工作频率低的问题,出现了专用于内核和DDR SDRAM 之间的接口标准SSTL。

本文基于0.13μm标准CMOS工艺,全订制设计了一款应用于内存控制器中,工作频率为400MHz物理层的SSTL接口电路。

本文首先介绍了课题背景、研究现状以及SSTL接口电路的相关理论。

然后介绍了SSTL接口电路的设计。

SSTL接口电路共分为两个部分:SSTL I/O Buffer和SSTL时序控制电路。

SSTL I/O Buffer包括输入Buffer,输出Buffer和片内终端ODT。

输入Buffer中设计了测试和静电保护电路,输出Buffer中采用电流驱动的方式提高了电路的工作频率和驱动能力,片内终端ODT可防止信号在输出端形成反射。

SSTL时序控制电路包括数据通道和控制通道两个子模块,电路中采用对称匹配性设计提高了时序控制的准确度。

另外,SSTL接口电路中输出供电电源和内部电路工作电源使用两种相互独立的电源,不仅避免了电源之间的串扰,而且降低了电路的功耗。

最后,对SSTL接口电路进行了电路仿真、版图设计以及版图验证与后仿真,仿真结果表明电路在400MHz下,性能稳定,驱动能力达到SSTL标准中的要求,功耗较低。

关键词:DDR SDRAM;物理层;接口电路;SSTLAbstractThe memory is used widely in modern electronic system design, and the access speed and capacity are also required to meet the needs of DDR SDRAM. The frequency of DDR SDRAM interface circuit is a few hundred MH Z as the inner-core operating frequency has reached several GHz, so the interface circuit technology has become a bottleneck in the rapid development of integrated circuits. In order to solve the problem, a SSTL standard between the DDR SDRAM and the inner-core has appeared. Based on 0.13μm standard CMOS technology, the SSTL interface circuit that the operating frequency is 400MH should be designed and used in memory controller.First, this paper introduces the background and relevant theories of SSTL interface circuit, and then presents a SSTL interface circuit designs. The SSTL I/O buffer and SSTL timing control circuit are two parts of SSTL interface circuit. SSTL I/O buffer contains input buffer, output buffer and a terminal ODT. A test function and static electricity protection circuit are designed in the input buffer, and current drive mode is used to improve the circuit's operating frequency and drive capability of output buffer. In order to prevent the output signal reflection, a terminal ODT is integrated in the I/O buffer chip. SSTL timing control circuit contains two sub-modules which are the data and control ling channel, adoption of symmetry matching circuit design can improve the accuracy of timing control. Besides, the output and internal power supply circuit are separated, to avoid crosstalk between the power supplies and also reduce circuit power consumption. Finally, the results of SSTL interface circuit simulation and post-layout simulation show that the performance of our design is stable, and the driving ability can also meet the requirements of SSTL standard under 400MH with low power consumption.Keywords: DDR SDRAM, physical layer, interface circuit, SSTL目录摘要 (I)Abstract.......................................................................................................................... I I第1章绪论 (1)1.1 课题背景 (1)1.2 研究现状与进展 (2)1.3 课题研究内容 (3)1.4 论文的组织结构 (4)第2章SSTL接口电路相关理论及技术研究 (6)2.1 I/O Buffer基本理论 (6)2.2 SSTL I/O Buffer原理 (7)2.3 SSTL接口电路的噪声分析 (10)2.4 本章小结 (13)第3章SSTL I/O Buffer的电路设计 (14)3.1 SSTL输入Buffer的电路设计 (14)3.1.1 输入Buffer的设计方案 (14)3.1.2 ESD输入保护电路设计 (15)3.1.3 输入Buffer电路设计 (17)3.1.4 SSTL输入Buffer电路仿真 (19)3.2 SSTL输出Buffer的电路设计 (21)3.2.1 输出Buffer的设计方案 (21)3.2.2 输出Buffer电路设计 (22)3.2.3 SSTL输出Buffer电路仿真 (25)3.3 片内ODT电路设计 (28)3.4 本章小结 (30)第4章SSTL时序控制电路设计 (31)4.1 数据通道模块的设计 (31)4.2 控制模块的设计 (36)4.3 本章小结 (38)第5章版图设计与验证 (39)5.1 版图设计技术及考虑的因素 (39)5.2 SSTL I/O Buffer版图设计 (40)5.3 SSTL时序控制版图设计 (42)5.4 本章小结 (44)结论 (45)参考文献 (46)攻读学位期间发表的学术论文 (50)哈尔滨工业大学硕士学位论文原创性声明 (51)哈尔滨工业大学硕士学位论文使用授权书 (51)致谢 (52)第1章绪论1.1课题背景内存是计算机的重要组成部分,内存作为计算机存储信息的装置,用于存放数据信息,这些数据信息可被随机取出供给计算机的其他部件。

随着计算机CPU前端总线带宽的提高和高速局部总线的出现,CPU处理性能的快速提高对内存的性能要求也提出了更高的要求。

面对处理器性能快速提升的趋势,设计和实现大容量高速读写的内存显得尤为重要。

因此,近年来内存产品正经历着从小容量到大容量、从低速到高速的不断变化,在技术上方面出现了DRAM、SDRAM,以及DDR SDRAM(Double Date Rate SDRAM)。