计算机原理与设计-CH1-2005

北京科技大学_计算机组成原理及计算机系统结构_2005年_考研真题

(2) :6ë3Cachekktijtlêst,#li'>Hy.'#J#:/YJiQl;(2iV)

(3) HI:I1TiY-$CacheZI'TJ#4-$#YJë#X4.1:.%-.A;(3+V)

1

(;E.. jLt-(1,40R)#J#)6J1Jt.IF*#tilJl'..i>.>l.ir'-?'Fuqt#f74t/l$if,Dkk/4Brft7ltY%io1sC4ta0'Ac0hM,WeHj/tzl4sI/tJîxSN-/'jXs.1àtCsNA#l'f4#.XtNlzt,l7i.rï$k'j+2Y$,-:l/ï1@1$0-Cha#>.cFhW1Jel.$BJ1$##1C1X/7';DXSPA1I)$.%(i#.'?E@;,(q/5f/!#i5lViîj)j#s#4ifk#iA#@#J,!$#'/:#ï#E1JJ%L:BikT>.t*fil.j

(l) lqipnjtlïlkf 15*,.#.jtkkàlùvifqxr%skiz+/4kxl;8)c1'pf2J,r'ri.#-ikllhlk.st'amifltàlk/.lfg;p

微机原理与接口技术CH1

教学重点

微机系统结构,计算机中的数据表示方法

教学难点:

数制转换和浮点数表示方法

中国科学技术大学电子工程与信息科学系 中国科学技术大学电子工程与信息科学系

1-1、计算机发展简史

谁是现代电子计算机之父?

英国天才的科学家、思想家:阿兰.图灵(Alan Turing,1912-54) 1936年发表阐明现代计算机原理的开山之作: “论数字计算在决断难题中的应用”,给出了 “可计算性”的严格数学定义,并提出著名的 “图灵机(Turing Machine)”的设想。 “图灵机” 是思想模型,证明了可制造一种十分 简单但运算能力极强的计算装置,用来计算所 有能想像得到的可计算函数。

1950年10月,图灵发表了划时代之作: “机器能思考吗”,又为图灵赢得了“人 工智能之父”的桂冠。

中国科学技术大学电子工程与信息科学系 中国科学技术大学电子工程与信息科学系

冯.诺依曼的提问

-超短悬疑剧 第一幕:邂逅

时间:1944年夏的一天 地点:美国内华达州, 美国陆军弹道试验场附近阿伯丁火车站候车室 人物1:ENIAC设计组成员戈尔斯坦 人物2:洛斯·阿拉莫斯实验室的冯·诺依曼博 士,当时已蜚声国际的数理大师。

中国科学技术大学电子工程与信息科学系 中国科学技术大学电子工程与信息科学系

Intel微处理器家族(IA-64除外)

4位处理器 4004、4040 x86前 8位处理器 8008、8080、8085 IA-16 8086、8088、80286 x86架构 IA-32 Pentium Pentium前 80386、80486 早期架构 Pentium、Pentium MMX P6架构 Pentium Pro、Pentium II、Pentium III、Pentium II/III Xeon/Celeron NetBurst架构 Pentium 4、Pentium D、 Pentium Extreme Edition、Xeon 其中Pentium D 和Pentium Extreme Edition支持Dual-Core技术、Extended Memory 64 Technology(EM64T),Pentium Extreme Edition还支持HyperThreading (HT-超线程)技术

ch05_大学计算机应用技术_[共26页]

![ch05_大学计算机应用技术_[共26页]](https://img.taocdn.com/s3/m/9a1f639b2e3f5727a4e96205.png)

第5章Internet网络应用技术【本章重点】计算机网络的定义与功能;计算机网络的组成与分类;OSI参考模型与TCP/IP参考模型;Internet基础知识;物联网技术。

【本章难点】OSI参考模型与TCP/IP参考模型;计算机网络拓扑结构;IP地址的构成与分类;物联网技术原理与体系结构。

【学习目标】掌握计算机网络的定义与功能;掌握计算机网络的分类与拓扑结构;掌握计算机网络的体系结构;掌握IP地址的构成与分类;熟悉Internet基础知识;掌握IE的使用与设置。

5.1 计算机网络概述在信息化社会中,计算机已经从单一使用发展成集群使用,越来越多的应用领域需要计算机在一定的地域范围内协同工作,从而促进了计算机技术和通信技术紧密地结合,形成了计算机网络这门学科。

随着计算机技术的快速发展,计算机网络的应用也越来越普及和广泛,已渗透到国民经济和人们日常生活的各个领域。

我们可以通过计算机网络来获取所需要的各种信息,也可以通过它向全社会发布各种经济信息、科研情报、技术资料等。

当今的时代就是一个以网络为核心的信息时代,它最主要的特征就是数字化、信息化与网络化。

现在人们的生活、工作、学习都已离不开计算机网络。

没有网络我们无法到银行存钱或者取钱,没有网络我们无法预订火车票、飞机票,没有网络我们无法上网查询自己需要的相关资料,没有网络我们更无法在网上与朋友及时交流信息。

由此可见人们已经越来越依赖于网络,那么计算机网络到底是什么?它由哪些部分组成?为什么我们可以使两台相距那么远的主机进行通信,它的工作原理又是什么呢?接下来,我们一点点来看。

5.1.1 计算机网络的定义及功能什么是计算机网络?计算机网络的精确定义并未统一,最简单的定义就是:一些互相连接的、自治的计算机的集合。

从定义中看出一个计算机网络涉及3个方面的问题。

(1)至少两台计算机互联。

(2)通信设备与线路介质。

(3)包括相应的网络软件,通信协议。

167168按照此定义两台计算机和连接它们的一条链路,就可以构成一个最简单的计算机网络,世界上最大、最复杂的网络就是我们通常所说的因特网Internet。

ch1计算机原理

2

假设有相同指令级的两种不同实现方式:

计算机A的时钟周期为250ps,对某程序的CPI为2.0

计算机B的时钟周期为500ps,对同样程序的CPI为1.2

请问:对于该程序,请问哪台计算机执行的速度更快?快多少?

3

一个编译器设计者试图在两个代码序列之间进行选择,硬件设计者给出了如下数据:

对于某行高级语言语句的实现,两个代码序列所需的指令数量如下:

哪个代码序列执行的指令数更多?哪个执行速度更快?每个代码序列的CPI是多少?

3

解: 序列1 有5条指令; 序列2 有 6条 序列1 需 2×1+1×2+2×3=10 cycles 序列2 需 4×1+1×2+1×3=9 cycles

序列1 的 CPI=10/5=2; 序列2 的CPI=9/6=1.5 虽然序列2的指令条数多,但速度却更快! 一个编译器设计者试图在两个代码序列之间进行选择,硬件设计者给出了如下数据:对于某行高级语言语句的实现,两个代码序列所需的指令数量如下:

哪个代码序列执行的指令数更多?哪个执行速度更快?每个代码序列的CPI是多少?

p☐ 基准测试程序集是专门进行性能评价的一组程序

n⏹ 用户希望基准测试程序能够预测机器在运行实际负载时的性能SPEC INTC2006基准程序在AMD Opteron x4 2356(Barcelona)的运行结果:。

计算机操作系统ch1

参考网站

操作系统原理教案: 操作系统原理教案:/ 清华开放学习资料库: 清华开放学习资料库:/study/study.htm 中大操作系统CAI: 中大操作系统 /os/ 浙江师范大学课件: 浙江师范大学课件: /kofbobo/czxt/ 湖南农大操作系统 CAI:/elong/main.asp 操作系统 CAI: http://202.194.116.12/lessons/computer/os/cai.htm 东华大学操作系统 CAI: http://219.228.69.94/os/oscai/instruction.asp 操作系统疑难问题讨论: 操作系统疑难问题讨论:/archive/8/1355094.htm 北大操作系统课件: 北大操作系统课件: /Soft_Show.asp?SoftID=288 各种操作系统的网址: 各种操作系统的网址:/technology/os.htm

计算机操作系统

Operating System of Computer

教材与参考书 教材与参考书

计算机操作系统.汤子瀛 ,哲凤屏. 西安电子科技 大学出版社 操作系统教程—原理和实例分析.孟静. 高等教 育出版社 操作系统原理.庞丽萍. 华中理工大学出版社 现代操作系统.陈向群等译.机械工业出版社 Applied Operating System Concepts. Abrraham Silberschatz、Peter Galvin、Greg Gagne. 机械工业出版社 操作系统原理.何炎祥. 华中科技大学出版社

OS为用户提供虚拟计算机(5)

4) 例2 ,如果加上一层I/O设备 管理软件,用户就可使用I/O命 令来进行数据的I/O,不必涉及 显示器、打印机、扫描仪、键 盘和鼠标等的物理细节。

计算机组成与设计ch05

计算机组成原理- CH05 指令系统体系结构5.1 概述计算机指令由操作码和操作数组成。

操作码指定要执行的操作类型,而操作数指出数据所处的寄存器和内存单元。

本章会对上一章的内容做进一步的展开,深入讨论计算机的指令系统体系结构。

将介绍各种不同的指令类型和操作数类型,以及指令如何访问内存中的数据。

5.2 指令格式每条计算机的指令都有一个操作码和0个或多个操作数.每条指令允许使用的操作数的个数不同,指令的类型和指令处理的操作数的类型也可能不同.更具体地说,各种指令集可能在特征上存在如下差别:操作数在CPU中的存储方式(数据可以存储在堆栈结构或寄存器中)指令作用的操作数的数目(最常用的操作数个数为0,1,2和3) 操作数的位置(如果简单地按照指令适用的操作数的组合,则各种指令可以分为寄存器-寄存器类型,寄存器-存储器类型或存储器-存储器类型)操作(不仅包括操作的类型,而且指出指令是否可以访问存储器) 操作数的类型和长度(操作数可能是地址,数字或字符)5.2.1 指令系统的设计指令系统体系结构(ISA)的效能可以用下面几个因素来衡量:(1) 程序执行指令时占用内存空间的大小;(2) 指令系统的复杂程度, 主要指指令执行所需要的译码数量和指令所执行的任务的复杂性;(3) 指令的长度;(4) 指令系统中指令的总数目.设计指令系统时需要考虑的问题包括:指令一般越短越好,因为较短的指令占用较少的内存空间,并且撮指令的速度也会更快.但是采用短指令会限制指令的数量.固定长度的指令的译码相对比较容易, 但却浪费空间.存储器的组成形式会影响指令的格式.固定长度的指令系统并不表示必须使用固定数量的操作数.存在多种不同类型的寻址方法.如果机器的字由多个字节组成,就需要考虑组成的字的字节是按照怎样的次序存储到按字节的机器存储器中设计的体系结构需要多少个寄存器且这些寄存器应该如何进行组织安排,操作数如何存放在CPU中5.2.2小端和大端的位序问题术语----- 位端(endian)指的是计算机体系结构中的"位序" (byte order).位端是指在计算机中存储一个多字节数据元素时, 各个字节的排列方式.将最低位的字节首先存放到低位地址,然后再将最高位的字节存放到高位地址,采用这种方式的机器称为小端(little endian)机器.先将最高位的字节存放到低位地址,然后再存放最低位的字节. 这种类型的机器称为大端(big endian)机器.大部分的UNIX计算机都是大端机器, 而大多数的PC机则是小端机器.大端位序的存储方式更自然些, 而且更便于阅读十六进制编写的程序段.大端位序的机器存储整数和字符串时使用相同的次序, 并且在某些字符串操作时速度会更快一些. 大部分位图映身格式的图像都是采用"最高位在字符串的左边"的变换方法, 也就是说对于像素大于一个字节的数据可以直接按照大端位序机器自身体系结构的安排顺序进行处理.大端位序的存储方式也有缺点,如果计算机要进行从32位整数地址到16位整数地址的转换操作, 则要求大端机器执行加法运算.高精度的算术运算在小端机器上会更快和更方便一些.计算机网络都是采用大端位序的体系结构.5.2.3 CPU的内部存储机制: 堆栈和寄存器CPU的数据存储方式是区分不同指令系统体系结构(ISA)的最基本的方法. 这里有三种不同的体系结构可供选择.1. 堆栈体系结构2. 累加器体系结构3. 通用寄存器(GPR)体系结构堆栈体系结构(stack architecture)的计算机使用一个堆栈来执行各种指令, 而且指令的操作数就隐含地存放在堆栈的顶部. 这种机器通常具有好的编码密度和一个简单的表达式估值模型,但由于不能对堆栈进行随机访问, 使得采用堆栈结构的机器很难产生高效率的编码.累加器体系结构(Accumulator architecture)的计算机, 比如MARIE, 是将其中一个操作数隐含在累加器中.降低了机器的内部复杂性,而且允许使用非常短的指令. 但由于累加器是临时存储, 所以对存储器的访问非常频繁.通用寄存器体系结构(general purpose register architecture)的计算机, 采用多个通用寄存器组, 这是当今计算机体系结构中最广泛接受的模型.寄存器组的访问速度比存储器快得多,通用寄存器体系结构可以根据指令的操作数所处的位置分成三种类型.存储器-存储器(memory-memory)体系结构可以有两个或三个操作数位于存储器内, 允许有一条执行某种操作而不需要有任何操作数的指令存放在某个寄存器中.寄存器-存储器(register-memory)体系结构则是采用混合方式,这其中至少有一个操作数在寄存器中和一个操作数在存储器中.装入-存储(load-store)式体系结构则需要在任何对数据的操作执行之前,先将数据装入寄存器中.5.2.4 操作数的数目和指令的长度在现在的计算机体系结构中, 指令构成的格式有如下的两种方式:固定长度(fixed length)使用这种格式的指令系统会浪费一些存储空间, 但是指令执行的速度快. 在采用指令层次(instruction-level) 的流水线结构时, 固定长度的指令系统的性能会更好些可变长度(variable length)这种指令的译码会变得比较复杂, 但是却可以节省存储空间.最常用的指令格式包括有零个, 一个, 两个, 或三个操作数. 使用一个堆栈结构也可以允许有不带操作数(零操作数)的指令.只有操作码 (0 地址)操作码 + 1个地址 (通常只有一个存储器地址)操作码 + 2个地址 (通常是两个寄存器地址, 或者是一个寄存器地址加上一个存储器地址)操作码 + 3个地址 (通常是三个寄存器地址, 或者是寄存器和存储器的某种组合形式)不带操作数的机器指令必须使用堆栈来执行在逻辑上需要一个或两个操作数的操作随着每条指令所允许的操作数的数目的减少, 完成相同程序功能所需的指令数目将会增加. 这就是一个典型的在空间和时间之间进行平衡折衷.通常,采用较短的指令需要编写较长的程序5.2.5 扩展操作码扩展操作码 (expanding opcode)代表了一种折衷的方案,就是既要求有尽可能多的操作码的数目, 又要求采用尽可能短的操作码, 所设计的指令长度也比较短.其设计的基本思想是: 选用短操作码, 而当有需要时可以有某种方法将操作码加长采用扩展操作码的方法使指令的译码变得更加复杂5.3 指令类型有些指令的操作对象不是数据, 指令归纳为以下几种类型:数据移动算术运算布尔逻辑运算位操作 (移位和循环换位)输入/输出 (I/O)控制转移专门用途数据移动指令是最常用的指令. 人们常常需要将数据从存储器移到寄存器, 从寄存器移到寄存器, 以及从寄存器移到存储器等.算术运算指令包括有整数和浮点运算的各种指令.布尔逻辑指令执行布尔逻辑运算, 与算术指令的运算方式非常类似位操作指令用来在某个特定的数据字中对一些单独数据位(或者是一些位的集合) 进行置位和复位操作.输入/输入(I/O) 指令随着计算机体系结构的不同而有很大区别. 处理输入输出的基本方式有: 程序控制的I/O, 中断驱动的I/O 和直接存储器访问(DMA) 的I/O 三种方式控制指令包括分支转移(branch), 跳过(skip) 和进程调用(procedure call)等.专用指令包括字符串处理的指令, 高级语言支持的指令, 保护和标志位控制指令, 以及高速缓存(cache) 指令等.5.4 寻址与寻址有关的两个最重要的问题是: 可以进行编址的数据类型和各种各样的寻址方式.5.4.1 数据类型如果指令要引用某个特定的数据类型,必须有相应的硬件对该种类型的数据提供支持指针是被认为与整数和浮点数字不同的数据类型.对于使用指针的指令, 操作数本质上就是一个地址, 并且必须被当成一个地址处理.5.4.2 寻址方式寻址方式是指定指令中操作数的位置的方法立即寻址 (immediate addressing)是指在指令中操作代码后面的数值会被立即引用, 12位的操作数域并不是指定一个地址, 而是表示指令所要求的实际操作数. 但由于加载的数值是固定的, 这种方式非常不灵活直接寻址 (direct addressing) 是指在指令中直接指定要引用的数值的存储器地址. 直接寻址方式比立即寻址方式要灵活得多.寄存器寻址 (register addressing) 方式中, 是采用一个寄存器, 而不是存储器来指定操作数. 寄存器寻址方式中被指定的寄存器中的内容将用作指令的操作数.间接寻址 (indirect addressing)是一种非常有效的寻址方式, 使用起来特别灵活,在间接寻址方式中, 地址域中的二进制数用来指定一个存储器地址, 该地址中的内容将被用作一个指针. 操作数的有效地址是通过访问这个存储器地址来获取的作为间接寻址的一种变化形式操作数域的二进制位也可以用来指定一个寄存器,而不是指定某个存储器地址.这种方式称为寄存器间接寻址 (register indirect addressing).在变址寻址方式(indexed addressing)中, 一个变址寄存器(要么显式地指定, 要么隐式指定)用来存储一个偏移量(offset, 或称为位移量(displacement)基址寻址(based addressing)方式与变址寻址方式非常类似.区别是,基址寻址方式使用的是基地址寄存器,而不是变址寄存器.堆栈寻址(stack addressing)方式,则操作数就假定放在堆栈中.5.5 指令的流水线有些CPU会将取指-译码-执行周期分成一些较小的步骤, 其中的某些较小的步骤可以并行执行. 这种时间上的交叠可以加快CPU的执行速度,这种方法称为流水线(pipeline).不同的步骤可以并行完成不同指令的各个部分.这其中的每一个步骤都称为流水线极(pipeline stage).一旦第一条指令的取指任务完成, 第一条指令就会被送去进行了译码操作.与些同时, 可以开始第二条指令的取指. 当第一条指令取操作数时, 第二条指令被送去译码, 同时开始取第三条指令.这些事可以并行发生并不是所有指令都必须经过管道中的每一级流水线. 有些情况会阻碍计算机实现每个时钟周期执行一条指令的目标资源冲突数据关联条件分支语句资源冲突 (resource conflict)是指令级并行执行过程中要考虑的主要问题.例如一个在读一个在写数据关联 (data dependency)是指当一条指令的执行尚未结束时, 后面某条指令却要求该指令的执行结果作为其操作数.分支转移语句来改变程序的执行流程,但是这样会对流水线造成重大问题. 许多计算机体系结构都设计分支预测(branch prediction) 机构, 利用合理的逻辑来对下一条指令做出最优的预测.超标量 (superscalar) 体系结构是利用多条平行的流水线同时执行多个操作超流水线 (superpipelining) 体系结构则是将超标量体系结构和流水线体系结构的概念组合起来, 把流水线的各个级分割成更小的步骤.IA-64 体系结构却是一个超长指令字 (VLIW) 体系结构, 即每条指令可以指定多个标量操作, 也就是编译器可以把多个操作放到一条指令中.。

计算机操作系统原理 ch1 绪论

多道程序设计

2、共享性(sharing)

共享:多个任务共同使用系统资源。

共享是现代计算机系统的一个最大特点,操作系统的 一个主要目标就是要使各种系统能有效地被共享、最 大限度的提高系统效率,由于共享的实质是并发共享。 故关键仍是在于并发性

3、不确定性(nondeterminacy) 操作系统面对的是不确定的事件,而这些事件发生的 时间和次序是不可预测的。

Serial Processing

No operating system Machines run from a console with display lights and toggle switches, input device, and printer Schedule: one by one Setup: included loading the compiler, source program, saving compiled program, and loading and linking

开关置机器指令,按’装入数据’按钮 开关置程序始址,按’运行’按钮

装入程序的引进

装入程序(Loader)

自动化执行程序装入,必要时进行地址转换 通常存放在ROM中

机器 语言 程序

装入 程序

内存 储器

汇编语言

汇编语言:机器语言的符号化 汇编语句形式:符号化的字符串 汇编语句格式:

Multi-programming …

多道程序设计是指让多个程序同时进入 计算机的主存储器进行计算

多道程序设计的特点

CPU与外部设备充分并行 外部设备之间充分并行

发挥CPU的使用效率

微机原理ch1

第 8 页 共 19 页

《微机原理》讲义 第一章 绪论

输入/输出( 输出(I/O)总线

ቤተ መጻሕፍቲ ባይዱ

CPU

I/O设备

存储总线

I/O设备

I/O设备

主存储器 I/O设备1 I/O设备2

图 1-8 优点:提高了数据传送的效率; 缺点:主存和外设之间必须通过 CPU 进行信息的交换,降低了 CPU 的工作效率。 (3)面向主存储器的双总线结构:面向主存储器的双总线结构如图 1-9(★)所示。它结合 了以上两种总线结构的特点,所有的部件和设备均挂到总线上。 输入/输出( 输出(I/O)总线

奇地址

FFFFFF FFFFFD 8 8MB 000003 000001 D15~D8 000002 000000

偶地址

FFFFFE FFFFFC 8 8MB

位

位

D7~D0

存储体4

FFFFFFFF 8 1GB 00000007 00000003 D32~D24

存储体3

FFFFFFFE 8 1GB 00000006 00000002 D23~D16

地址总线AB I/O总线

CPU

存储器

I/O接口

控制

I/O设备

数据总线DB

控制总线CB

图 1-3 (1)微处理器:取指令,指令译码;算术逻辑运算;和存储器和 I/O 交换数据;控制程序流 向等。 (2)存储器:存放程序和数据,分为 RAM、ROM。 (3)I/O 接口:实现外部设备和计算机的连接通道。 (4)总线:在 CPU、存储器和 I/O 设备之间传输信息的公共通道。 微型计算机必须配备一些输入、输出设备,构成一个系统才能够更好的工作。如:键盘 和显示器。否则数据和程序无法输入,运算结构无法显示。 3、微型计算机系统 以微型计算机为主体,配上外部 I/O 设备及系统软件就构成了计算机系统,其组成如图 1-4(★) 。 (1) 输入设备:把信息送入计算机,如键盘、鼠标、扫描仪等; (2) 输出设备:将计算机处理后的结果输出给用户,如显示器、打印机、绘图仪等; (3) 系统 软 件:计算机 必须配备操作 系统和 应 用程序 才 能 正常工作 , 操作 系统主 要 是 windows 操作系统,应用程序的种类非常多。

ch1-编码与程序设计语言原理_201721913555131

C —· —· L · —· · D—· · E· F · · —· M— — N—· O———

G——·

H· · · · I · ·

P· ——·

Y —· ——

7 ——· · ·

8 ———· ·

[(] — · ——·

[)] — · ——· — [&] · —· · ·

["] · —· · —·

[$] · · · —· · — [@] · ——· —·

PDF417码

Universal Product Code

QR码

条形码的解码

条形码的解码

• 第一个数字(在这里是 0)被称为数字系统字符 , 0的意思是说这是一个规范的条形码。如果是 具有不同重量的货物(像肉类或其他商品),这 个数字是 2;订单、票券的 U P C 编码的第一个 数字通常是 5。 • 紧接着的 5个数字是制造商代码。再后面的 5个数 字( 0 1 2 5 1)是该公司的某种产品的编号。 • 最后的数字(这里是 7)称作模校验字符,这个 字符可用来进行另外一种错误检验。

量子计算的研究

软件

• 微软联合加州大学圣芭芭拉分校Station Q实验室,Redmod的 QuArC团队 • Intel-荷兰戴尔福特理工大学的QuTech实验室 • 普渡大学的Station Q Purdue实验室 • 马里兰大学,悉尼大学,哥本哈根大学的QDev实验室 • 谷歌与加州大学圣芭芭拉分校John M. Martinis团队合作利用超 导体建立量子计算机 • IBM的沃森实验室 • 耶鲁大学Schoelkopf实验室 • NASA量子人工智能实验室 • 中科院量子信息重点实验室等团队均在关注量子计算领域。

布莱叶编码的编码格式 • 共64种编码格式 • 数字、字母和 标点符号—都 被编码成局限 在2×3小格中 一个或多个凸 起的点。

ch1计算机系统概论

课程概述

二、课程的基本要求

计算机系统概述、计算机中的数据表示、运算方法和 运算器、指令系统、随机逻辑和微程序控制原理、存 储系统、输入输出系统、计算机外设讲解, 围绕各自 的功能、组成、设计、实现、使用等知识进行介绍要 求学生掌握计算机的组成和工作原理。强调培养学生 的动手动脑能力、开创与创新意识。

婴幼儿体格生长

ch1计算机系统概论

教材

白中英,计算机组成原理,科学出版社

参考书

唐朔飞 ,计算机组成原理, 高教出版社 罗克露,计算机组成原理, 电子科大出版社

课程概述

一、课程性质与任务

“计算机组成原理”属于专业基础课,必修课。面向应用、 突出实践、偏向硬件和理论。 《计算机组成原理》是计算机教学中的一门核心课程,是 学习计算机课程所要必修的主干课。通过教学,使学生对 计算机的各主要部分(运算期、控制器、存储器、输入输 出设备)的构成及工作原理有一个深刻的、系统的认识和 理解,同时对计算机的发展趋势也有一个较为深入的了解。

❖ “程序控制”,是控制器依据存储程序控制 计算机按规定的顺序逐条执行指令,自动完 成预定的信息处理任务

系统结构

5 控制器的基本任务

基本概念

❖ 按照计算程序所排的指令序列,先从存储器 取出一条指令放到控制器中,对该指令的操 作码由译码器进行分析判别,然后根据指令 性质,执行这条指令,进行相应的操作。接 着从存储器取出第二条指令,再执行第二条 指令,依次类推

系统结构

计算机的基本性能指标 吞吐量:表征一台计算机在某一时间间隔内能

够处理的信息量,单位是字节/秒(B/S)。 响应时间:表征从输入有效到系统产生响应之

间的时间度量,用时间单位来度量。 主频/时钟周期:CPU的工作节拍受主时钟控制,

ch 1

冯.诺依曼计算机结构

存 储 器

输 入 设 备

运 算 器

输 出 设 备

控 制 器

电子计算机发展简史

第一代 电子管计算机时代(1946-1957) 基本器件:电子管,磁鼓做内存

应用对象:军事和国防尖端技术

AB地址总线:单向,位数取决于CPU直接

寻址内存范围。

8位机 16位机 32位机 64KB,16根地址线 1MB, 20根地址线

1MMB, 32根地址线 DB数据总线:三态双向结构。宽度取决于CPU 位数。

数据:运算数据、指令代码、状态量、 控制量 CB控制总线:输入/输出。

功能:传输M 、 I/O的读写、中断请求 /响应等状态控制信息。

1.运算器(算术逻辑运算部件,核心 加法器)

功能:对一个或二个操作数进行 ① 执行各种算术运算,给出相应标志; ② 执行各种逻辑运算,并进行逻辑测试。 构成: ①ALU:算术逻辑运算部件。对操作数进行 加、减、乘、除和与、或、非等算 术逻辑运算。

②TMP、ACC:暂存寄存器及累加器,暂存 两个操作数。ACC通常存放操作结果。只 有一个操作数时只用ACC。 ③F(PSW) :标志寄存器,用来保存数逻指令运 行或测试结果建立的各种状态标志。包括6个 状态标志位,3个控制标志位。如: CF(CY) 进位标志 AF 辅助进位标志 ZF 零标志 OF 溢出标志 PF 奇偶标志 TF 跟踪标志

编程方法:人工接线,准备时间大于计 算时间; 存储容量:20个10位字长的十进制数 是一台无程序存储器采用十进制运 算的计算机。

其先天不足决定没有发展前途。

第1章-计算机设计基本原理(第2讲)

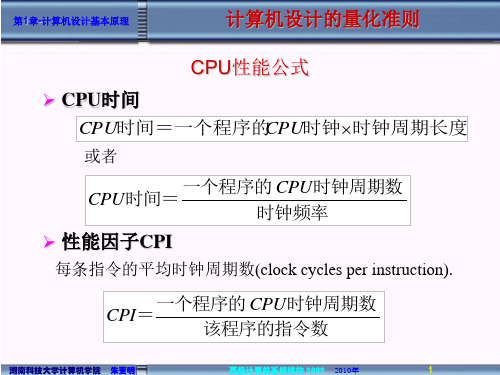

第1章-计算机设计基本原理CPU 性能公式CPU 时间或者时钟频率时钟周期数一个程序的时间=CPU CPU 性能因子CPI每条指令的平均时钟周期数(clock cycles per instruction).该程序的指令数时钟周期数一个程序的=CPU CPI 计算机设计的量化准则时钟周期长度时钟时间=一个程序的 CPU CPUIC:一个程序的指令数时钟周期的长度时间=⨯⨯CPI IC CPU 或者时钟频率时间=CPI IC CPU ⨯时钟周期每条指令的时钟数数时间=一个任务的指令⨯⨯CPU 时钟周期数秒指令数时钟周期数程序数指令数=⨯⨯程序数秒时间=CPU可以改变其中一项来改善CPU 性能,但涉及另外二项,因为这三个因子是相互有关的:时钟周期的长度:由硬件技术和组成技术决定;CPI :与计算机组成和指令集有关;指令数:与指令集结构和编译技术有关;∑=⨯ni ii CPI IC CPU 1时钟周期数=IC i :指令I 在一个程序中的执行次数CPI i :执行指令I 所需的平均时钟周期数时钟周期长度时间=⨯⎪⎭⎫ ⎝⎛⨯∑=ni i i CPI IC CPU 1总的CPI 也可表示成:i n i i ni i i CPI IC CPI IC CPI ⨯⎪⎭⎫ ⎝⎛⨯∑∑==11总的指令数=总的指令数=CPU 性能可表示成:()CPII f CPI CPU CPU ⨯=⨯指令数时钟频率=时间性能=1例题1.5计算机设计的量化准则例1.5设条件转移指令的实现有两种方案可选:机器A:用两条指令完成。

由比较指令建立条件码,再在转移指令中测试条件码。

机器B:只用一条指令。

比较和转移一起进行。

对于这两种机器来说,条件转移指令用2个时钟,所有其他指令用1个时钟。

在机器A上有20%的执行指令是条件转移指令,每个转移都需要比较,有20%是比较指令。

由于机器A在转移指令中没有比较功能,这样时钟频率比机器B快25%,问:哪个机器快?解答:忽略所有等待和系统时间的影响,可用CPU时间来比较机器的性能。

CH1信息技术基础概述

计算机的特点

运算速度快 计算精度高 自动化程度高 具有超强的“记忆”能力 具有逻辑判断能力 通用性强

计算机的应用领域

1.科学计算 科学计算也称为数值计算,用于完成科学研 究和工程技术中提出的数学问题的计算。例如: 天文学、量子化学、空气动力学、核物理学和天 气预报等领域中。其特点是计算量大和数值变化 范围大。 2.数据处理 数据处理也称为非数值计算,是指对信息进 行存储、加工、分类、统计、查询及制表等操作。 计算方法简单,数据量很大。广泛应用于办公自 动化、企业管理、事物处理、情报检索等。

例如 (2AF)16=2×162+A×161+F×160=(687)10

练习

(BE.8)16 =( (1CE.D)16 =(

)10 )10

十进制数转换为二、八、十六进制数

十进制

二进制

规则:除2取余 乘2取整

例如

(139)10=(10001011)2 (0.8125)10=(0.1101)2

八进制

十进制

规则:八进制数每一位上的数码乘以相应位 置上的位权,然后将所得结果相加

例如 (751.64)8=7×82+5×81+1×80+6×8-1 +4×8-2=(489.1875)10 练习

(154.78)8=( (26.25)8=(

)10 )10

十六进制

十进制

规则:十六进制数每一位上的数码乘以相 应位置上的位权,然后将所得结果相加

二、八、十六进制数转换为十进制数

二进制

十进制

规则:二进制数每一位上的数码乘以相应 位置上的位权,然后将所得结果相加

例如:

基于CC2005的“计算机组成原理与结构”课程改革

基于CC2005的“计算机组成原理与结构”课程改革摘要:本文在IEEE/ACM关于计算(Computing)学科本科教学参考计划CC2005(Computing Curricula 2005)指导下,针对我国高校本科计算机专业建设的现状,提出基于CC2005的“计算机组成原理与结构”课程内容体系的改革,采用整体“自顶向下”、细节“自底向上”的方法,从整机到部件、从原理到芯片的方式组织课程内容,并探讨了与课程群内部其他核心课程、选修课程之间的关系。

关键词:计算机组成原理与结构;CC2005;课程改革1引言WTO关于教育服务的条款对高等教育发展将产生直接影响,而经济结构调整与就业结构变化也将对高等教育发展产生更重大的影响。

随着计算机和通信技术近十年来的蓬勃发展,中国开始进入信息化社会,以信息化带动工业化,全面建设小康社会,已经成为我们的基本国策和全国人民共同奋斗的宏伟目标。

在这样的历史背景下,重新审视高等学校本科计算机专业的课程改革具有十分重要的意义。

目前,随着网络化和信息化的发展,计算机的软件领域课程,尤其是网络和网络应用类课程,越来越得到各高校的重视,国内很多高校的计算机专业逐渐转变为“软件工程”和“计算机科学”方向,过分强调软件与应用,而缺乏计算机体系结构、计算机组成与结构等硬件方向的培养。

但是,从就业市场反馈的信息看,计算机软件人才已经供大于求,而熟悉硬件设计的人才则供不应求,年薪也远远高于同等的软件人才。

不熟悉计算机组织与结构、不了解计算机体系结构的软件人才,也尤如建立在空中的楼阁,没有基础,从小而言无法满足人才市场的需求,从大而言无法担负我国科技兴国,在国际信息化竞争中立于不败之地的重任。

“计算机组成原理与结构”课程要求掌握计算机系统各个部件的组成原理,最终达到从系统、整机的角度理解计算机的结构与组成,是国内大多数本科高等学校“计算机科学与技术”专业的专业基础课,是计算机硬件与结构方向非常重要的一门课程,这门课程的建设与改革直接关系到人才培养中计算机硬件与结构方向教育的成败。

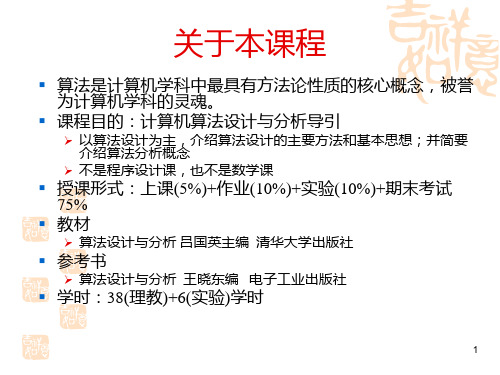

ch1算法概述

15

(3)欧几里德算法

▪ gcd ( m, n ) = gcd ( n, m mod n )

同

➢ gcd ( 24, 18 ) = gcd ( 18, 6 ) = gcd ( 6, 0 ) = 6

一

▪ 输入 正整数m和n

个

输出 m和n的最大公因子

算

1. 如果n = 0, 计算停止返回m, m即为结果;否则继续2。 法

4

算法2 可以运用公式

1 2 3 n n(n 1) 直接计算; 2

第一步 取n=5;

第二步 计算 n(n 1) 2

第三步 输出运算结果。

5

例2:三个牧师和三个野人过河,只有一条能装 下两人的船,在河的任一边或者船上,若野人 人数大于牧师人数,那么牧师就会有被吃掉的 危险。你能不能找出一种安全的渡河算法呢?

错误。 ④ 注意学习和总结。 ⑤ 用大脑“运行”算法是学习算法很好的方法。 ⑥ 解题时要学会择优。简单说择优要考虑四个方面:

可读性、可修改性、时间效率和空间效率。

18

从算法到实现-算法基本技巧举例

▪ a. 算术运算的妙用 ➢ 例1.2 开灯问题

▪ b. 巧用“标志量” ➢ 例1.3 判定输入n个数据互不相等

➢ {d=d*i;

➢ m=m/i;

➢ n=n/i;}

➢ print(d ,“is maximal common divisor”);

➢}

14

(2)计算gcd(m,n)的连续整数检测(枚举)算法

第一步:将min{m,n}的值赋给d。 第二步:m除以d,若余数为0,进入第三步;否则第四步。 第三步:n除以d,若余数为0,返回d值(结果);否则第四步。 第四步:把d的值减1,返回第二步。 例如:对于60和24这两个数,该算法会先尝试24,然后是23,

计算机原理与设计-CH2-2005

2020/8/16

国防科技大学计算机学院

28/109

1.3、字符串数据表示

字符串的存储结构 向量表示法的特点: ➢最简单、最节省存储空间的方法; ➢删除、插入操作代价高; ➢字符串移动时速度较快,前提——硬件支持内 存数据成组移动指令; ➢最常用。 向前串表表示法:字符串中每个字符后有一个链接 字,用以指出下一个字符的地址。

下溢:数据小数的绝对值太小,使得数据无法有效 地表示。与上溢相比,下溢的问题比较小,数据一 旦出现下溢,就可以认为此数据为“0”。

2020/8/16

国防科技大学计算机学院

24/109

1.2、浮点数据表示

浮点数据表示的特点:

二、数据分布变得不均匀

整数数据表示在数轴上是均匀分布的,几乎所有连 续两个数据之间的差为1,仅在原、反码表示中, +0和-0的时候数据出现不均匀。

浮点数据表示的基本原理——科学记数法 一个数N的科学记数法形式可写成:N = M × RE M(Mantissa):尾数 E(Exponent):阶码 R(Radix):基数

2020/8/16

国防科技大学计算机学院

16/109

1.2、浮点数据表示

浮点数据表示=定点数据表示+科学记数法: 注意:浮点数实数;浮点数只是实数的一种近似 表示; 浮点数格式必须兼顾表示范围及表示精度的要求; 浮点数据通常采用的编码: ➢尾数:原码或补码; ➢阶码:移码或补码。

小数:小数点固定于数的左端,在20与2-1之间。

➢小 数 表 示 成 D0.D1…Dn-1 , 其 中 Di 的 权 重 为 2-i 。 小数真值V=D0×20+D1×2-1+…+Dn-1×2-(n-1)。D0 通常用来表示符号位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2020/8/16

国防科技大学计算机学院

19/35

2、计算机系统组成

控制器CU的组成: ➢时序部件:

• 主频CP和时序信号产生器TSG:

CP

TSG

• 节拍和主频周期的关系

➢微操作(Micro-operation)控制部件

• Why? • 微操作与微程序; • 微程序通常固化在ROM(Read Only Memory)中。

➢I/O的特点:速度较慢。

2020/8/16

国防科技大学计算机学院

22/35

2、计算机系统组成

互连结构(Interconnection Structure) ➢作用:数据交换。 ➢BUS:

• 连接简单; • 数据传输率不高; • 微机中大量使用。

➢互连网(Interconnection Network):

10 8 08 8 02 8 08 8 02 8 08 8 02 8 14 8 FF 0

00B01 00B00 00B02 00B00 00B03 00B00 00B04 00B05 00000

00B00

x

00B01

a

00B02

b

00B03

c

00B04

d

00B05

y

说明 取数:R8 a 乘法:R8 a × x 加法:R8 a × x + b 乘法:R8 (a × x + b)× x 加法:R8 (a × x + b)× x + c 乘法:R8 ((a × x + b)× x + c)× x 加法:R8 ((a ×x + b)× x + c)× x + d 存数:(00B05) R8 停机

计算机原理 Computer Principles

国防科技大学计算机学院

About Principle

Definition: ➢A general truth or belief that is used as a base for reasoning, or action, or for the development of further ideas. ➢A law of nature as scientifically discovered and stated.

2020/8/16

国防科技大学计算机学院

9/35

1、计算机及其发展史

计算工具 ➢计算过程:获取数据、存储数据、加工数据。 ➢计算工具的发展就是计算过程自动化程度不断 提高的过程:

• 手工计算 • 机械计算 • 电子计算

电子计算机的分代 ➢以电子器件为标志

2020/8/16

国防科技大学计算机学院

国防科技大学计算机学院

11/35

2、计算机系统组成

计算机的功能 ➢ 数据传送功能 ➢ 数据存储功能 ➢ 数据处理功能 ➢ 操作控制功能 ➢ 操作判断功能

2020/8/16

国防科技大学计算机学院

12/35

2、计算机系统组成

冯.诺依曼体系结构 ➢以二进制表示和存储程序控制为核心。

存储器

输入设备

运算器

➢y=((a*x+b)*x+c)*x+d

• 3次乘法,3次加法

ax 上步结果加 b

ax+b 上步结果乘以 x

ax2+bx 上步结果加 c

ax2+bx+c 上步结果乘以 x

ax3+bx2+cx

上步结果加 d

ax3+bx2+cx+d

2020/8/16

国防科技大学计算机学院

24/35

3、计算机的工作过程

移位器

flag

ALU

2020/8/16

锁存器1

锁存器2

内部总线

国防科技大学计算机学院

寄存器组 R0 R1 ... Rn-1

16/35

2、计算机系统组成

控制器CU(Control Unit)的作用: ➢根据预定的步骤,控制与协调各部件的自动工 作。是计算机的管理机构和指挥中心。 ➢控制器完成的工作实质上就是控制指令执行: 获取指令、译码、产生控制信号。 ➢连续不断、有条不紊地继续上述动作,即所谓 的执行程序。

2020/8/16

国防科技大学计算机学院

31/35

3、性能分析与分类

计算机的分类标准 ➢计算机的用途

• 专用 • 通用

➢计算机的规模

• 巨型机、大型机、小型机、微型机、单片机

2020/8/16

国防科技大学计算机学院

32/35

4、计算机的应用与发展

应用类型 ➢科学计算 ➢数据处理 ➢实时控制 ➢辅助设计 ➢智能模拟

TSG

ID

状态

微操作控制部件

...... 微操作 控制信号

控制器

XR

地址计算

+1

AR

PC

到内存选址系统

存储体 ...... 地址译码器

MAR

存储时序控制线路 内存储器

国防科技大学计算机学院

27/35

3、计算机的工作过程

计算y的源程序

主存地址 指 令 或 数 据

00A00 00A01 00A02 00A03 00A04 00A05 00A06 00A07 00A08

学习内容

➢基本组成(Basic Organization)

➢工作原理(Principle)

➢设计方法(Layout Method)

➢常识性知识(Common Sense )

2020/8/16

国防科技大学计算机学院

3/35

知识点

参见目录: ➢绪论 ➢指令系统 ➢运算方法与运算器 ➢控制器 ➢存储器 ➢输入输出(I/O)控制 ➢计算机模块结构与互连

2020/8/16

国防科技大学计算机学院

28/35

3、性能分析与分类

性能指标: ➢主频:5M~3G+ቤተ መጻሕፍቲ ባይዱ

• 提高主频的方法:工艺

➢速度:

• 吉布森混合法 • 计算各种指令执行速度 • 计算典型程序运算速度Benchmark • 实际测试、模拟分析

2020/8/16

国防科技大学计算机学院

29/35

3、性能分析与分类

2020/8/16

国防科技大学计算机学院

5/35

学习目标及方法

学习目标: ➢花时少、效率高; ➢掌握基础知识,进行创造力训练; ➢培养一流的计算机人才。

学习方法: ➢概念、原理与设计——what? why? how? ➢提倡怀疑; ➢听课时追随老师的思路,积极思考; ➢温故而知新。

2020/8/16

26/35

3、计算机的工作过程

计算机总体框图

运算器

移位器

flag

ALU

锁存器 1 锁存器 2

寄存器组 R0 R1 ... Rn-1

CPU内部总线

输入输出设备 I/O设备 ...... I/O设备

设备控制器

设备控制器

......

I/O控制部件

系统总线

MBR

2020/8/16

CP

IR

节拍信号 指令译码

2020/8/16

国防科技大学计算机学院

20/35

2、计算机系统组成

存储器M(Memory) ➢存储器的构成

存储体

存

00...00 地 00...01

存储单元

读

地 址 总 线

储 地 址 寄 存

址 00...10 译 码

...... ......

写 线

器

路

MAR

器 11...11

存储单元

读/写命令

2、计算机系统组成

控制器CU的组成: ➢指令控制部件:

• PC:程序计数器、指令地址寄存器; • IR:存放当前正在执行的指令; • ID:对指令操作码进行译码以识别指令。

➢地址形成部件:

• AR:存放需要访问数据的存储单元地址; • XR:变址寄存器,用于变址寻址; • 地址计算部件。注意:CPU中能够完成计算的部件

• 连接复杂; • 数据传输率高; • 对速度要求高的巨型机、并行机中大量使用。

2020/8/16

国防科技大学计算机学院

23/35

3、计算机的工作过程

一个简单例子:

a 乘以 x

➢已知a、b、c、d、x, 求解代数多项式: y=ax3+bx2+cx+d。

➢y=a*x3+b*x2+c*x+d

• 5次乘法,3次加法

存储时序控制线路

存

储 缓 冲 寄 存

数 据 总 线

器

MBR

2020/8/16

国防科技大学计算机学院

21/35

2、计算机系统组成

输入与输出设备(Input/Output Device) ➢又称外设、简称I/O; ➢主机:CPU、内存储器及相应接口; ➢种类:

• 输入设备 • 输出设备 • 输入输出设备

国防科技大学计算机学院

6/35

其他需要说明的问题

关于课堂纪律; 关于课程安排; 关于课后作业; 关于考试。

2020/8/16

国防科技大学计算机学院

7/35

第一章

绪论 Introduction

内容提要

计算机的发展史(简介) 计算机系统组成(掌握) 计算机工作过程(第一章/了解、全课程/掌握) 计算机的性能指标和分类(掌握) 计算机的应用与发展(简介)

2020/8/16

国防科技大学计算机学院

33/35

4、计算机的应用与发展

发展 ➢性能超级化

• 超高性能微处理器Cray on Chip • 并行处理技术的应用