第3章节--IO地址译码

第3章-IO端口地址译码技术

本章主要内容

➢ I/O 端口的基本概念 ➢ I/O 端口译码的基本原理 ➢ I/O 端口译码电路的设计

2020/5/11

计算机接口技术

1

一、接口信息与功能

1、接口信息 • 数据信号:

如:8位、16位、32位数据;

• 状态信号:

表示外设是否准备好信号。

CPU

地址 数据 控制

;将端口F4H和F5H的16位数据送AX ;将端口F4H、F5H、F6H和F7H的32位数据送 ;EAX ;从DX指出的端口输入32位数据到EAX

;EAX内容输出到DX指出的32位数据端口

2020/5/11

计算机接口技术

10

I/O指令表示,CPU从端口读数据或向端口写数据,

仅仅是指I/O端口与CPU的累加器之间的数据传输,

并未涉及数据是否传输到存储器的问题。若要将端口的数据 传输到存储器,还得用MOV指令进行传输。

例如:

MOV [DI],AL IN AL,DX

;将数据从AL→存储器 ;从端口读数据到AL

MOV [DI],AL ;将数据从AL→存储器

MOV DX,301H ;I/O端口

将端口的 数据传输 到存储器

MOV AL,[SI] ;从内存取数据到AL

信号转换功能:协调总线信号与I/O设备信号。转换包 括信号的逻辑关系、时序配合和电平转换。

可编程功能:增加接口的灵活性和智能性。

3.1 I/O 地址空间

如果忽略I/O地址空间的物理特征,仅从软件编程的角度来看,和 存储器地址空间一样,I/O地址空间也是一片连续的地址单元,可供 各种外设与CPU交换信息时,存放数据、状态和命令代码之用。

出程序段:接口电路硬件保护及操作系统中数据恢复。

第3章 端口地址译码技术

的接口卡发生冲突,最好采用DIP开关进行地址设置。

可通过“附件”→“系统信息”→“硬件资源”→“I/O” 选项来查看 I/O 端口的地址分配状况

12

2.3 I/O端口地址译码

(1) 基本概念与原理

基本概念

▲当执行I/O指令时,CPU首先在总线上发出要访问的端口地

址和必要的控制信号,然后通过一个译码电路将这些信号 转换为相应的I/O端口选通信号。

23

A2 A3 A4

A B C

Y0 Y1 Y2 Y3 2F0H~2F3H 8255A

A8

G2B G2A G1

Y4 Y5 Y6 Y7 74LS138 A0 A1 CS

M/IO# AEN

A5 A6 A7 A9

A0 A1

地址 2F0H 2F3H

A9 1 1 G

A8 0 0 G2B

A7 1 1

A6 1 1 G

能弱,程序设计灵活性差。增加了控制逻辑的复杂性。

6

(3) 独立编址下的I/O指令

指令类型

▲IN:从I/O端口读入数据到微处理器的累加器中。

▲OUT:将微处理器累加器中的数据写入到I/O端口。

注意:数据只在累加器(AX或AL)和端口间进行传递。

原则:传输字节数据时使用AL;传输字数据时使用AX。

基本内容

▲I/O端口与内存单元统一进行地址分配,使用统一的指令访问

I/O端口或者内存单元。又称存储器映射编址方式。

▲Motorola公司的68系列、Apple系列微机即是统一编址。

地址空间 0

内存地址 ( 共960K)

EFFFFH F0000 H I/O 地址 ( 共64K) FFFFFH

3

优点

I-O端口地址译码技术

I/O端口地址译码技术

统一编址的主要优点:一是对任何存储器操作指令都可用 于操作I/O接口,而不必使用专用的I/O指令,系统中存储器操 作指令是丰富多彩的,可以大大增强系统的I/O功能,使访问外 设端口的操作方便、灵活、不仅可对端口进行数据传送,还可 对端口内容进行移位和算术逻辑运算等;二是可以使外设数目 或I/O寄存器数目只受总存储容量的限制,从而大大增加系统的 吞吐率,这在某些大型控制或数据通信系统等特殊场合是很有 用的;三是使微机系统的读/

主要缺点:一是端口地址占用了存储器地址,使可用的内 存空间相对减少;二是由于地址位数长,访问内存的指令一般 较长,执行速度较慢;三是为了识别一个I/O端口,必须对全部 地址线译码,这样不仅增加了地址译码电路的复杂性,而且使

统一编址方式在单片机中得到广泛应用,而在通用型的计 算机系统中已经不再使用。

I/O端口地址译码技术

I/O端口地址译码技术

同时,由于使用专门的I/O指令访问端口,并且I/O端口地 址和存储器地址是分开的,故I/O端口地址和存储器地址可以 重叠,而不会相互混淆。并且由于存储器与I/O端口的控制结

这种方式的缺点是专用I/O指令类型少,远不如存储器访 问指令丰富,使程序设计的灵活性较差;且使用I/O指令一般 只能在累加器和I/O端口间交换信息,处理能力不如存储器映 像方式强;尤其是要求处理器能提供存储器读/写及I/O端口读/ 写两组控制信号,这不仅增加了控制逻辑的复杂性,而且对于 引脚线本来就紧张的CPU芯片来说不能不说是一个负担。

OUT PORT,AL

其中,PORT是一个8位的字节地址。

I/O端口地址译码技术

例如:

IN AL,60H;60H为系统板8255A的PA

OUT 61H,AL;61H为系统板8255A的PB

O地址译码一、实验目的掌握IO地...

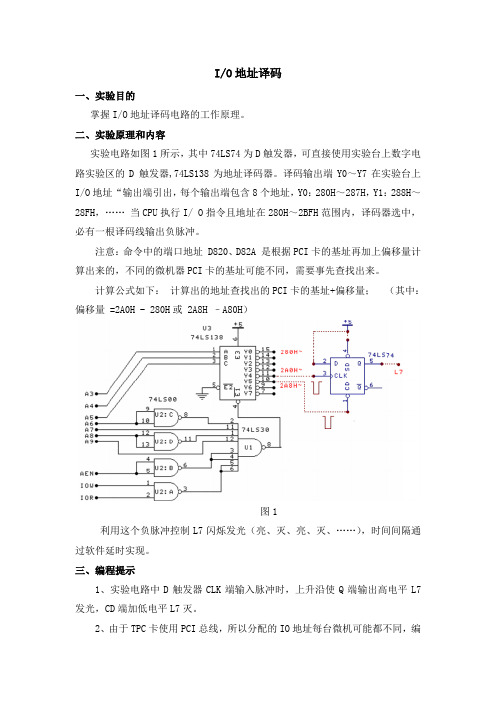

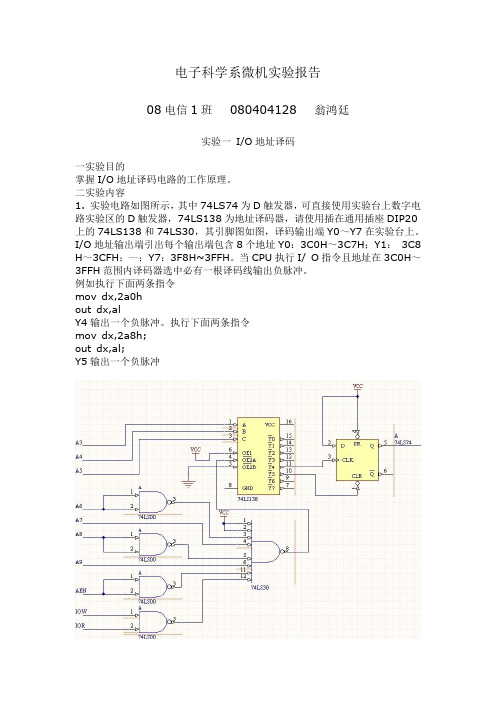

微机原理硬件实验报告实验一I/O地址译码一、实验目的掌握I/O地址译码电路的工作原理。

二、实验原理和内容1、实验电路如图1-1所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D触发器,74LS138为地址译码器。

译码输出端Y0~Y7在实验台上“I/O地址“输出端引出,每个输出端包含8个地址,Y0:280H~287H,Y1:288H~28FH,……当CPU执行I/O指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

利用这个负脉冲控制L7闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现。

2、接线: Y4/IO地址接 CLK/D触发器Y5/IO地址接 CD/D触发器D/D触发器接 SD/D角发器接 +5VQ/D触发器接L7(LED灯)或逻辑笔三.硬件连线图四.软件流程图五.源程序CODE SEGMENTASSUME CS:CODESTART: MOV DX,2A0HOUT DX,ALCALL DELAYMOV DX,2A8HOUT DX,ALCALL DELAYJMP STARTMOV AX,4C00HINT 21HDELAY PROC NEAR --延时子程序MOV BX,200LOOP1:MOV CX,0FFFFHLOOP2:LOOP LOOP2DEC BXCMP BX,0JNZ LOOP1RETDELAY ENDPCODE ENDSEND START六.实验结果小灯L7出现亮灭交替的现象,通过改变延时子程序BX的值可以改变亮灭的时间间隔。

七.实验总结与心得体会本次实验主要是对延时子程序的编写,由于书上有范例所以比较简单。

实验二简单并行接口一、实验目的掌握简单并行接口的工作原理及使用方法。

二、实验原理和内容1、按下面图简单并行输出接口电路图连接线路(74LS273插通用插座,74LS32用实验台上的“或门”)。

74LS273为八D触发器,8个D输入端分别接数据总线D0~D7,8个Q输出端接LED显示电路L0~L7。

第3章+地址译码技术与存储器接口

• I/O端口:是微处理器与输入输出设备直接通 信的寄存器或某些特定的器件。一个接口可 以有多个端口,如命令端口、状态端口和数 据端口等。

• I/O操作:CPU对I/O接口电路(与设备相关)的 操作.不是访问I/O设备.

• 计算机给接口电路中的每个寄存器分配一个端口, 因此,U在访问这些寄存器时,只需指明它们的端 口,不需指出是什么寄存器。

• 4)VC++程序

3.1.4. I/O端口地址分配

IBM PC/XT I/O 端口地址分配图

0000

001F 0020

003F 0040

005F 0060

007F 0080

009F 00A0

00BF 0080

32字节 32字节 32字节 32字节 32字节 32字节

0000~000F 0020~0021 0040~0043 0060~0063 0080~0083 00A0~00BF

3.1.3 I/O端口访问指令 外设

• 80x86 CPU构成的计算机,其CPU外围 0000

接口芯片及I/O接口部件皆采用独立编

址方式,采用IN和OUT指令实现数据的

65 KOU1

输入和输出操作。

F3 KOU2

内存

00000

11 32

02 KOU3

32

• 1)8086/8088采用I/O端口与累加器传

00

01

送数据。

• 若端口地址在 0~FFH 范围内,则用直 接寻址

• IN AL,端口地址

(输入)

• OUT 端口地址 ,AL

(输出)00FF

执行的操作为:

0100 11 KOU100

(AL)<—(PORT) (字节操作)

第3章-IO地址译码

主要优点: (1) I/O端口地址不占用存储器空间; (2) I/O指令短,执行速度快;

FFFFH

(3) I/O操作和存储器操作层次清晰,程序的可读性强。

缺点:

I/O指令种类有限, I/O空间不易扩展

2、统一编址(存储器映象方式)

地址 0000H ... 0100H 00FFH ...

I/O空间 (256个) 整 个 地 址 空 间

四、DMA传送方式

工作原理 由外设与计算机内存直接进行数据交换,而不是通 过CPU; 在DMA传送期间,DMA控制器接管了总线控制权,而 CPU处在停机方式,即处于等待状态; 在DMA传送完成后,CPU再恢复对总线的控制权,进 入工作状态。 CPU 特点 数据的传送不经过CPU。 RAM 外设 要求 DMA 需要DMA控制器及相关逻辑支持。 控制器 应用 适用于高速度大量数据传送时。

2、C语言I/O语句

C语言有强大的I/O操作功能,利用c语言可方便地设计操作 界面,同时也可以对外设进行直接控制. 端口输出 outportb(port,value) //从port端口输出字节型数据 value outportw (port,value) //从port端口输出字型数据value

了解I/O端口地址分配 对接口设计者非常重要。 一、64K I/O地址映像图 I/O地址线:16位 I/O端口地址空间:64K 分为两部分。 ① 留给微机系统和ISA总线 地址固定 ② 留给PCI总线,主板功能和用户应用 地址动态分配

① 0000H~03FFH

② 0400H~FFFFH

3.3

I/O端口地址分配

第3章基本的I/O接口 ---来自I/O地址译码内容提要

第三章 端口地址译码技术

A1 A0 0 0 8

•

22

逻辑表达式: Y= A9A8A7A6A5A4A3A2 A1A0 AEN IOR 摩根定律:或非=非与,非或=与非 Y=A9A8A7A6A5A4A3A2 + A1A0 AEN IOR

结论:输出Y低电平有效。即当端口地址 为2F8H,AEN=0,IOR=0低电平时,输出Y 有效。

第三章

3.1 3.3

I/O端口地址译码技术

I/O端口及其编址方式 I/O端口地址译码

返回目录

1

3.1

3.1.1

3.1.2 3.1.3

I/O端口及其编址方式

I/O端口和I/O操作

I/O端口地址编址方式 独立编址方式的端口访问

返回第三章

2

3.1.1

1.I/O端口

I/O端口和I/O操作

定义:端口(port)是接口电路中能被CPU直 接访问的寄存器(的地址)。 CPU 与外设之间交换信息具体是通过I/O 端口来进行的。

10

I/O端口访问

所谓对端口的访问就是CPU对端口的读/写。 指I/O端口与CPU的累加器之间的数据传送, 并未涉及数据是否传送到存储器的问题。

输入: 端口数据 输出: 内存中的数据

CPU中的累加器 CPU中的累加器

内存 I/O端口

11

3.1.3、独立编址方式的端口访问

1.I/O指令中端口地址的宽度

26

逻辑表达式:

Y1 =A9A8A7A6A5A4A3A2 + A1A0 AEN + IOR

Y1 = A9A8A7A6A5A4A3A2 · 1A0 AEN ·IOR A

I O地址译码(微机实验报告)

I/O地址译码一、实验目的掌握I/O地址译码电路的工作原理。

二、实验原理和内容实验电路如图1所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D 触发器,74LS138为地址译码器。

译码输出端Y0~Y7在实验台上I/O地址“输出端引出,每个输出端包含8个地址,Y0:280H~287H,Y1:288H~28FH,……当CPU执行I/ O指令且地址在280H~2BFH范围内,译码器选中,必有一根译码线输出负脉冲。

注意:命令中的端口地址 D820、D82A 是根据PCI卡的基址再加上偏移量计算出来的,不同的微机器PCI卡的基址可能不同,需要事先查找出来。

计算公式如下:计算出的地址查找出的PCI卡的基址+偏移量;(其中:偏移量 =2A0H - 280H或 2A8H –A80H)图1利用这个负脉冲控制L7闪烁发光(亮、灭、亮、灭、……),时间间隔通过软件延时实现。

三、编程提示1、实验电路中D触发器CLK端输入脉冲时,上升沿使Q端输出高电平L7发光,CD端加低电平L7灭。

2、由于TPC卡使用PCI总线,所以分配的IO地址每台微机可能都不同,编程时需要了解当前的微机使用那段IO地址并进行设置,获取方法请参看汇编程序使用方法的介绍。

(也可使用自动获取资源分配的程序取得中断号)。

四、实验代码CODE SEGMENTASSUME CS:CODESTART:LOOP1:MOV CX,0FFFFHLP1:MOV DX,2AOHIN AL,DXLOOP LP1MOV CX,0FFFFHLP2:NOPLOOP LP2MOV CX,0FFFFHLP3:MOV DX,2A8HIN AL,DXLOOP LP3MOV CX,0FFFFHLP4:NOPLOOP LP4MOV AH,0BHINT 21HCMP AL,0JZ LOOP1MOV AH,4CHINT 21HCODE ENDSEND START五、实验总结通过实验,了解和掌握I/O地址译码电路的工作原理,熟悉汇编代码的编写。

《微型计算机接口技术课件》第3章 IO端口地址译码技术

本章主要内容

Ø I/O 端口的基本概念 Ø I/O 端口译码的基本原理 Ø I/O 端口译码电路的设计

2020/7/9

计算机接口技术

1

3.2 .2 I/O 端口共用技术

一般情况下,一个端口只接收一种信息(命令、状态或数据) 的访问,但有些接口芯片,允许同一端口既作命令口用,又作状态口用, 或允许向同一个命令口写入多个命令字,这就产生端口共用的问题。

协处理器

0F8H~0FFH

表3.2系统的外设接口卡端口地址

I/O接口卡名称 端口地址

并行口控制卡1 378H~37FH

并行口控制卡2 278H~27FH

串行口控制卡1 3F8H~3FFH

串行口控制卡2 2F8H~2FFH

原型插件板

300H~31FH

同步通信卡1 3A0H~3AFH

同步通信卡2 380H~38FH

3.I/O地址映射对用户来讲是透明的。

2020/7/9

计算机接口技术

12

3.3.3 I/O端口地址选用的原则

1.凡是被系统配置占用了的地址一律不能使用; 2.未被占用的地址,原则上用户可以使用。但申明 保留的地址,不要使用; 3.留给用户可使用的端口地址:300H--31FH。

根据上述原则,本教材扩展的接口芯片,使用表 3.3中分配的I/O端口地址。

端口共用问题的处理方法是: 对命令口和状态口共用的处理方法是,根据读/写操作来区分。向该口 写,就是写命令,作命令口用;从该端口读,就是读状态,作状态口用 例如,串行接口芯片8251A采用这种办法。 对多个命令字写到同一个命令口时,可采用两种办法解决:其一,在 命令字中设置特征位,根据特征位的不同,就可以识别不同的命令,例如 82C55A接口芯片采用这种办法;其二,在编写初始化程序段时,按先后顺 序向同一个端口写入不同的命令字,命令寄存器就根据先后顺序的约定来 识别不同的命令,8251A接口芯片采用这种方法。

接口_第3章 IO端口地址译码技术

或

MOV DX, XXXXH OUT DX, AL OUT DX,AX

;8位传送(输出) ;16位传送(输出)

这里,XXXXH为16位的两字节地址。

2、I/O端口的寻址方式

I/O端口寻址有直接I/O端口寻址和间接I/O端口 寻址,其差别在I/O端口寻址是否经过DX传输。 例如:输入时 IN AL,0E0H ;直接寻址 MOV DX,300H ;间接寻址 IN AL,DX 例如:输出时 OUT 0E0H,AL ;直接寻址 MOV DX,300H ;间接寻址 OUT DX,AL

16位微处理器的I/O地址线是16位,实际上 只使用A0-A9地址线,地址线的选择应遵循下 列规则: 高位地址作为片间寻址,低位地址作为片 内寻址。 片内地址线数由接口中寄存器的数目决定。

2、I/O端口地址译码电路的输入与输出信号线

I/O地址译码电路的输入信号

I/O地址译码电路不仅仅与地址信号有关,而 且与控制信号有关。例如:

地址线 0 0 A 9 A8 A7 A6 A5 A4 A3 A 2 A1 A0

二进制

0

0 0

控制信号

0

C

B

A

? ? ? ? ?

片内地址

片选地址

地址范围在00H-0FFH区间的译码电路

开关式I/O地址译码电路设计

例:某微机系统的I/O空间为000H-3FFH,分成连 续的16段可选地址,每个段包括8个接口芯片, 每个接口芯片拥有8个端口。 分析:采用部分译码方法,允许16个段可以选择, 所以采用4位开关。

3.4

I/O端口地址分配及选用原则

IO端口地址译码PPT课件

同步通信卡1

3A0H~3AFH

同步通信卡2

380H~38FH

单显MDA

3B0H~3BFH

彩显CGA

3D0H~3DFH

彩显EGA/VGA

3C0H~3CFH

硬驱控制卡

1F0H~1FFH

软驱控制卡

3F0H~3F7H

PC网卡

360H~36FH

.

本章7首页

5.2.3 I/O端口地址译码

1. I/O地址译码电路工作原理及作用

.

本章12首页

本章要点

端口的概念 端口的地址编址方式及其特点 I/O端口地址选用的原则 掌握I/O端口地址译码电路的工作原理 I/O端口地址译码电路的设计与分析

.

本章13首页

片间选择:高位地址+控制信号

译码电路

片选信号

高位地址、 低位地址的划分

片内端口选择:低位地址直接与接口芯片地址线相连

.

本章8首页

5.2.3 I/O端口地址译码(续)

3. I/O端口地址译码电路设计

A9

地址范围:n根地址线未参与译码,译出地址含2n个 1)固定式端口地址译码 门电路译码法——单个地址或地址范围

微机原理与接口

(第5章)

信息工程学院 电子信息工程教研室

.

1

5.2 I/O端口地址译码技术

主要内容

5.2.1 I/O端口及其编址方式 5.2.2 I/O端口地址分配 5.2.3 I/O端口地址译码

.

2

5.2.1 I/O端口及其编址方式

1. I/O端口和I/O操作

1)I/O端口

端口(port):是接口电路中能被CPU直接访问的寄存器。

C

Y0

微机接口技术-第3章IO端口地址译码技术

内存 内存接口

系统总线:地址总线XA19-0,数据总线XD7-0,控制总线/XIOR ……

智能仪器接口 通信接口 过程控制接口 输入接口

输出接口

外存接口

数字化存储示 波器,数字化

万用表

终端 调制解调器 TTY 电传机

A/D转换器 开关量输入 D/A转换器 开关量输出

键盘 数字化仪 点阵打印 CRT 显示

么?

思考:在PC机上设计接口,你设计的接口IO地址必须不能与其他设备 接口IO地址冲突,你能想到用什么办法解决这个问题?

方案一:先查PC机硬件说明书,看那些IO 地址已经被占用。

缺点是麻烦,且非PC机器厂家生产的设备 (如扩展接口卡)地址,必须通过查该卡

说明书才能了解它占用的IO地址。

不可能!!你怎么知道你的卡被客户装在 哪台机器上?客户计算机上装了哪些其它 厂家的卡,你怎么能预先知道呢?客户买

Y X 9X A 8 X A 7 X A 6 X A 5 X A 4 X A 3X A 2 A X 1 X A 0 X AX I O A XA9 XA8 XA7 XA6 XA5 XA4 XA3 XA2

/+Y

例2。 使用74LS138设计一个系统板上IO端口地址译码电路,并且让每个接口芯片内部 可以有32个端口,非DMA期间可以访问接口芯片。

分析:输入 XA9-5,XAEN。因为低5位地址用来选中芯片内部端口,不作为外部译码器 的输入。一片138只能译码3位地址,这里用138对XA7-XA5译码。

输出 8个芯片选中信号/Y0-/Y7。 逻辑关系:XAEN=0,XA9XA8=00时,使译码器工作。 XA7-XA5=000时,输出/Y0=0, 其余全无效为1。 XA7-XA5=001时,输出/Y1=0, 其余全无效为1 XA7-XA5=010时,输出/Y2=0, 其余全无效为1 ……

I╱O地址译码

2Q

14

13

12

11

10

9

8

Rd

Q

CP

D Sd Q

D Sd Q

CP

Rd Q

1

2

3

4

5

6

7

1Rd 1D

1CP1Sd1Q1 Nhomakorabea GND

② 逻辑功能 逻辑功能如表所示。

输

Sd Rd

LH HL

LL HH HH

HH

入

CP D

xx xx xx ↑H ↑L

Lx

输出

Q n1 Qn1

HL LH H* H* HL LH

实验一 I/O地址译码

outport1 equ 2a0h outport2 equ 2a8h code segment

assume cs:code start:

mov dx,outport1 out dx,al call delay mov dx,outport2 out dx,al call delay

mov ah,4ch int 21h

delay proc near mov bx,2000

lll: dec bx jne lll ret

delay endp code ends end start

74LS74为带预置和清除端的两组D触发器,其外引线排列如图所示。

Vcc

2 Rd

2D

2CP 2Sd

2Q

Qn Qn

实验二、简单并行接口

编程从键盘输入 一个字符和数字, 将其ASCII码通 过输出口输出, 根据8个发光二 极管发光情况验 证正确性。

用逻辑开关预 置某个字母的 ASCII码,编程 输入这个ASCII 码,并将其对 应字母在屏幕 上显示

1实验一、 IO地址译码

+5

4 5 1 2

12

U2:B

6

IOR

U2:A

3

图2.1

五、 实验电路图

电路图中,74LS74为D触发器(符合CLK^RD=0的 约束条件,具有记忆功能)。

74LS138为3-8地址译器,译码输出端Y0-Y7在实 验台上“I/O地址”输出端引出,每个输出端包含有 八个地址,Y0:280H-287H, Y1:288H-28FH, …… 当CPU执行I/O指令且地址在280H-2BFH范围内,译 码器选中,必有一根译码线输出负脉冲。 表1.1为实验系统板接口芯片端口地址分配表

六、实验内容

1、熟悉实验台结构; 2、系统的安装; 3、电路连线; 4、实验编程

总线插座及 总插孔

8255A 8253 DAC0832 74LS244

8251A

ADC0809

逻辑电平开 关与LED显示 电路

实验安装

地址线

数据线

A19-A0:20位地址线 D7-D0: 8位数据线 IRQ: 中断请求输入信号,是用户中断请求引入端, 在IRQ2、IRQ3、IRQ4、IRQ7中,IRQ7级 别最低,PC总线接口卡在出厂时已将IRQ7作为中断信号。 IOR:I/O读信号 IOW:I/O写信号 MEMW:存储器写信号 MEMR:存储器读信号 AEN:地址允许信号,控制地址总线,以便进行DMA传送。 DRQ1:DMAC通道1的DMA请求信号 DACK1:DMAC通道1的DMA响应信号 CLK:时钟输出信号,信号是频率为4。77MHZ的时钟输出信号,作为8088系统时钟(主频) ALE:地址/状态复用线上信号作为地址码加以锁存。 T/C:计数终止信号 返回 其它为电源信号。

12 13 9 10

IO端口地址译码技术

4.3 I/o端地址译码

CPU为了对端口进行读写操作,就需要确定与自己交 为了对端口进行读写操作, 为了对端口进行读写操作 换信息的端口, 换信息的端口,那么是通过什么媒介把来自地址总线 上的地址代码翻译成为所需要访问的端口的, 上的地址代码翻译成为所需要访问的端口的,这是地 址译码问题,这介“ 就是I/O地址译码电路。 地址译码电路。 址译码问题,这介“媒介 ”就是 地址译码电路 一、I/O地址译码电路工作原理及作用 地址译码电路工作原理及作用

4.1 I/o端口及其编址方式

三、独立编址方式的端口访问 I/O指令有: 指令有: 指令有 1. IN 输入 2. OUT 输出 IN 输入指令 长格式为: 字节操作) 长格式为: IN AL,PORT (字节操作) IN AX,PORT (字操作) 字操作) 执行的操作为: 字节操作) 执行的操作为:(AL)<—(PORT) (字节操作) (AX)<—(PORT+1,PORT) (字操作) 字操作) , 注意长格式适用于端口地址范围为( 注意长格式适用于端口地址范围为(00H~0FFH)时 )

I/O端口地址译码技术 端口地址译码技术

教学重点

I/o端口及其编址方式 I/o端口及其编址方式 I/o端口地址译码 端口地址译码

4.1 I/o端口及其编址方式

端口和I/o操作 一、I/o端口和 端口和 操作 1、 I/o端口 、 端口 端口( 是接口电路中能被cpu直接访问的寄存器的 端口(port)是接口电路中能被 是接口电路中能被 直接访问的寄存器的 地址。 地址 。 Cpu通过这些地址即端口向接口电路中的寄存 通过这些地址即端口向接口电路中的寄存 器发送命令,读取状态和传送数据, 器发送命令,读取状态和传送数据,一个接口中可以 有几个端口,如命令端口、状态端口、数据端口。 有几个端口,如命令端口、状态端口、数据端口。对 端口的操作有三种类型: 只能读不能写 只能写不 端口的操作有三种类型:a.只能读不能写 b.只能写不 能读 c.可读可写 可读可写

I O地址译码实验

电子科学系微机实验报告08电信1班080404128 翁鸿廷实验一I/O地址译码一实验目的掌握I/O地址译码电路的工作原理。

二实验内容1. 实验电路如图所示,其中74LS74为D触发器,可直接使用实验台上数字电路实验区的D触发器,74LS138为地址译码器,请使用插在通用插座DIP20上的74LS138和74LS30,其引脚图如图,译码输出端Y0~Y7在实验台上。

I/O地址输出端引出每个输出端包含8个地址Y0:3C0H~3C7H;Y1:3C8 H~3CFH;⋯⋯;Y7:3F8H~3FFH。

当CPU执行I/ O指令且地址在3C0H~3FFH范围内译码器选中必有一根译码线输出负脉冲。

例如执行下面两条指令mov dx,2a0hout dx,alY4输出一个负脉冲。

执行下面两条指令mov dx,2a8h;out dx,al;Y5输出一个负脉冲利用这个负脉冲控制L7闪烁发光(亮、灭、亮、灭⋯⋯),时间间隔通过软件延时实现。

编程实现灯的延时:OUTPORT 1 EQU 2A0HOUTPORT 2 EQU 2A8HCode SegmentAssume Cs:CodeSTART :MOV DX,OUTPORT 1OUT DX,ALCALL DELAYMOV DX,OUTPORT 2OUT DX,ALCALL DELAYMOV AH,4CHINT 21HDELAY PROC NEARMOVE BX,2000III:DEC BXJNE IIIRETDELAY ENDPCODE ENDSEND START74LS138的管脚图其工作原理如下:当一个选通端(E3)为高电平,另两个选通端(E1)和/(E2))为低电平时,可将地址端(A0、A1、A2)的二进制编码在一个对应的输出端以低电平译出。

74LS138的真值表该电路的地址输出是从280H~2BFH,所以74LS138的地址译码输出关系为:/RWS=A9*A8*(/A7)*A6*A5*A4*(/A3)*(/A2)*(/A1)*(/A0)*(/AEN)*(IOW+IOR)地址范围A9 A8 A7 A6 A5 A4 A3 A2 A1 A0首地址280H 1 0 1 0 0 0 0 0 0 0末地址2BFH 1 0 1 0 1 1 1 1 1 174ls74的真值表。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• 辅助程序段:提供人-机对话手段。

3、接口的功能

• 数据缓冲功能:通过寄存器或锁存器实现。存放数据的 寄存器或锁存器称之为数据口。

• 接受和执行CPU命令功能:存放CPU命令代码的寄存器 称之为命令口,存放执行状态信息的寄存器称之为状态 口。

这种方式是接口中的端口地址单独编址,而不与存储 空间合一起。

如:IBM-PC系列、Z-80系列机

• 主要优点: 1、I/O端口地址不占用存储器空间;

2、I/O指令短,执行速度快;

3、I/O操作和存储器操作层次清晰,程序的可读性强。

3、Intel系列微机I/O编址

Intel系列微处理器支持I/O独立编址方式和I/O统一编 址(存储器映象编址)方式。I/O统一编址时,I/O地址不能缓 存。 • Intel系列微机系统仅支持I/O独立编址方式。

1.统一编址 从存储器空间划出一部分地址空间给I/O设

备,把I/O接口中的端口当作存储器单元一样进行 访问。 • 优点: 不设置专门的I/O指令,指令类型多,功能齐全。 • 缺点: 1、占用了存储器的地址空间,使存储器容量减小。 2、另外指令长度比专门I/O指令要长,因而执行 速度较慢。

2.独立编址

• 设备选择功能:CPU通过地址译码选择不同外设。即 CPU通过地址译码选择不同I/O接口。

• 信号转换功能:协调总线信号与I/O设备信号。转换包 括信号的逻辑关系、时序配合和电平转换。

• 可编程功能:增加接口的灵活性和智能性。

3.1.1 CPU与I/O之间的接口信息

1、接口信息

CPU

• 数据信息:

三、独立编址方式的端口访问

1. I/O指令中端口地址的宽度

IBM-PC系列采用I/O(input/output)指令访问端口,实 现数据的I/O传送。在I/O指令中可采用单字节地址或双 字节地址寻址方式。

• 单字节地址指令

其指令格式为:

IN AL, PORT

;输入

OUT PORT, AL

;输出

这里,PORT是一个8位的字节地址,则最多可访问256个 端口。

接口: 硬件— 支撑作用; 软件— 驱动控制。

CPU 接口 I/O设备

什么叫接口技术?

采用硬件与软件相结合的方法,研究微处理器如何与外 界进行最佳连接,实现高效可靠的信息交换的一门技术。

举例:

串行接口

并行接口

总线接口

显示卡 接口

USB 接口

键盘接口

硬盘接口

说明:

I/O设备与I/O接口

1. I/O接口受CPU控制,I/O设备受I/O接口控制。

端口输入: Value=inportb(port) //从port端口输入字节型数据,

并存储在 value变量中; Value=inportw(port) //从port端口输入字型数据,

;I/O端口

IN AL,DX ;从端口读数据到AL

MOV [DI],AL ;将数据从AL→存储器

输出时 MOV DX,301H

;I/O端口

MOV AL,[SI] ;从内存取数到AL

OUT DX,AL ;数据从AL→端口

3. C语言I/O语句

C语言有强大的I/O操作功能,利用c语言可方便 地设计操作界面,同时也可以对外设进行直接控制. • I/O命令 端口输出 outportb(port,value) //从port端口输出字节型数据 value outportw (port,value) //从port端口输出字型数据value

2. CPU通过端口地址向接口电路中的寄存器发送 命令,读取状态和传送数据。

3.一个接口可以有几个端口。 如命令口、状态口和数据口,分别对应于命令 寄存器、状态寄存器和数据寄存器。

举例:

30h

发送

命令寄存器

CPU

31h 传送

数据寄存器

32h

读取

状态寄存器

CPU对I/O端口的访问

3.1.3 I/O端口的编址方式

例如:

IN AL, 60H ;60H为系统板8255A的PA端口地址

OUT 61H, AL ;61H为系统板8255A的PB端口地址

• 双字节地址作为端口地址

MOV DX, × × × ×H

IN AL, DX

;8位传送

MOV DX, × × × ×H

OUT DX,AL

;8位传送

这里, × × × ×H 为16位的两字节地址。则最多

地址

如:数字量、模拟量、开关量; 数据

• 状态信息:

控制

数据

I/O

控制

设备

状态

表示外设是否准备好信号。

如:READY、BUSY、ACK

接口电路

• 控制信息:

表示启动、停止外设之类的信号. (STROBE)

3.1.2 I/O端口及其访问方式

一、I/O端口

1.接口电路中的端口是能被CPU直接存取访问的 寄存器。

低CPU的效率。 4. I/O直接接CPU,会使外设硬件结构过于依赖CPU,对

外设本身发展不利。

2. 接口组成

(1)接口硬件

(2)接口软件(设备驱动程序)

• 初始化程序段:设置接口工作方式及初始条

件。传送方式处理程序段:CPU针对不同的I/O 设备有不同的处理方式。

• 主控程序段:完成接口任务的程序。程序终

2. 为增加通用性,I/O接口的接口电路一般均具有可编程功能。

3. 微机的应用离不开与外部设备接口的设计、选用和连接。

• 为什么要引入接口?

1. 微机和I/O设备的信息类型和格式可能不一样。 2. 微机和I/O设备信号传输处理的速度可能不匹配。 3. 不用接口,I/O直接接CPU,随着外设增加,会大大降

第3章 基本的I/O接口

本章内容提要:

• 什么叫接口技术?

• 接口具有哪些功能? • 接口与CPU如何交换数据? • I/O端口及其编址方式 • I/O地址译码电路原理

3.1 I/O接口概述

一、接口(Interface) 就是CPU与外界的连接电路,或者说是与外

界进行信息交换的界面。

I/O设备: 键盘、显示器、打印机、硬盘、 光驱、控制设备、测量设备、 通讯设备

可寻址216=64K个端口。

例如:

MOV DX,300H IN AL,DX MOV DX,301H OUT DX,AL

;300H为扩展板8255A的PA端口 ; 301H为扩展板8255A的PB端口

2. I/O端口访问

• 所谓对端口的访问就是CPU对端口的读/写,将 端口的数据传送存储器。

例如:

输入时 MOV DX,300H