MIPS-mini指令集手册

mips汇编指令集功能的介绍

知道了什幺是指令集,这个时候还有一个概念就是编译。

编译其实就是把高级语言编程机器语言。也就是二进制的东西。烧录

openwrt的时候,用hex编辑器打开看看,里面全是二进制代码,这些就是翻

译后的机器语言。(当然,固件中处理指令集后,还有数据,数据就是普通的

资源文件,不会去控制cpu)。

因为更多的寄存器需要更多的指令空间对寄存器编码,也会增加上下

文切换的负担。

于一条指令集;(这里不讨论什幺汉字是笔画组成的,形象的比喻而已)

但是无论汉语和英语,都能实现人类基本交流。

例如:英语虽然只有26个字母,但是汉字却有几千个。但是有时候

翻译表达同一个意思,往往比中文要复杂。比如中文的诗句,简单的几个汉

字,就可以描述此次此刻的心境。

指令集就是cpu能读懂的指令,命令,就是人们预先定义好的,控制

MIPS指令集就是MIPS架构的CPU能读懂的语言。

MIPS汇编

MIPS指令集

MIPS指令集属于精简指令集

MIPS的所有指令都是32位,指令格式简单,而X86的指令长度不

是固定的。

简单的指令和格式易于译码和流水线操作,但是代码密度不高,导致

二进制ቤተ መጻሕፍቲ ባይዱ件大

MIPS有32个通用寄存器REG,为什幺是32个而不是更多呢?

mips汇编指令集功能的介绍

简单来说,指令集就是CPU能看得懂的语音,可以称之为机器语

言。

CPU指令集主要包括CISC(复杂指令集)和RISC(精简指令集)。

形象点说,

CISC类似于汉语,每一句话都是由汉字组成,而每一个汉字就相当

于一条指令集;

RISC类似于英语,每一句话都是由字母组成,而每一个字母就相当

MIPS基准指令集手册

第一届全国大学生计算机系统能力培养大赛基础指令集规范(v1.00)第一届全国大学生计算机系统能力培养大赛(以下简称“大赛”)技术方案中要求各参赛队开发支持MIPS 基准指令集的MIPS微系统。

本文档对需要支持的MIPS基准指令集进行明确规定。

各参赛队提交的设计作品必须实现本文档中的所有内容,但不限于。

如果发现本文档中有定义不精确之处,请查阅参考文献[1-3]中的相关章节;如发现两者存在冲突,以参考文献[1-3]中的内容为准。

本文档定义的MIPS基准指令集是在MIPS32指令集基础之上进行一定程度地裁剪,在控制系统设计规模的前提下,保证最简单系统的可实现性。

概要来说,这套指令集包含了所有非浮点MIPS I指令和MIPS32中的ERET指令,少量的CP0寄存器以支持中断和系统调用,不实现TLB MMU和特权等级。

本文档包含如下章节:第1章,“编程模型”,对支持的数据类型、软件可见寄存器、大小尾端进行定义。

第2章,“操作模式”,对处理器需要支持的操作模式进行定义。

第2章,“指令定义”,对需实现指令逐条定义。

第3章,“存储管理”,定义一套线性虚实地址映射机制。

第4章,“中断与例外”,介绍需实现的中断和例外的相关定义。

第5章,“系统控制寄存器”,对需实现的系统控制寄存器(俗称CP0寄存器)逐个进行定义。

1编程模型1.1 数据格式处理器可处理的数据格式定义如下:◆比特(bit, b)◆字节(Byte, 8bits, B)◆半字(Halfword, 16bits, H)◆字(Word, 32bits, W)1.2 寄存器处理器包含的软件可见的寄存器种类如下:◆32个32位通用寄存器,r0~r31。

其中有两个被赋予了特殊含义:r0,0号通用寄存器,值永远为0;r31,31号通用寄存器,被JAL,BLTZAL和BGEZAL指令隐式的用作目标寄存器,存放返回地址。

◆HI/LO寄存器。

HI寄存器存放乘法指令结果的高半部分或是除法指令结果的余数,LO寄存器存放乘法指令结果的低半部分或是除法指令结果的商。

MIPS指令集汇总(2021年整理精品文档)

MIPS指令集汇总编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(MIPS指令集汇总)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为MIPS指令集汇总的全部内容。

令功能应用实例LB从存储器中读取一个字节的数据到寄存器中LB R1,0(R2)LH从存储器中读取半个字的数据到寄存器中LH R1, 0(R2)LW从存储器中读取一个字的数据到寄存器中LW R1, 0(R2)LD从存储器中读取双字的数据到寄存器中LD R1, 0(R2)L。

S从存储器中读取单精度浮点数到寄存器中L.S R1,0(R2)L.D从存储器中读取双精度浮点数到寄存器中L。

D R1,0(R2)LBU功能与LB指令相同,但读出的是不带符号的数据功能与LH指令相同,但读出的是不带符号的数据LHU R1, 0(R2)LWU功能与LW指令相同,但读出的是不带符号的数据LWU R1, 0(R2)SB把一个字节的数据从寄存器存储到存储器中SB R1,0(R2)SH把半个字节的数据从寄存器存储到存储器中SH R1,0(R2)SW把一个字的数据从寄存器存储到存储器中SW R1, 0(R2)SD把两个字节的数据从寄存器存储到存储器中SD R1,0(R2)S.S把单精度浮点数从寄存器存储到存储器中S.S R1,0(R2)S。

D把双精度数据从存储器存储到存储器中把两个定点寄存器的内容相加,也就是定点加DADD R1,R2,R3DADDI把一个寄存器的内容加上一个立即数DADDI R1,R2,#3DADDU不带符号的加DADDU R1,R2,R3DADDIU把一个寄存器的内容加上一个无符号的立即数DADDIU R1,R2,#3ADD.S把一个单精度浮点数加上一个双精度浮点数,结果是单精度浮点数ADD。

mips指令集(24条指令)的字段和功能描述

MIPS指令集(24条指令)的字段和功能描述指令集概述M I PS(M ic ro pr oc es s or wi th ou tI nt erl o ck ed Pi pe li ne dSt a ge s)指令集是一种精简指令集(R IS C)体系结构,广泛应用于计算机体系结构的教学和实践中。

本文将介绍M IP S指令集中的24条常用指令,并对它们的字段和功能进行详细描述。

加载和存储指令1.l w指令字段描述:-指令格式:lw$r t,o f fs et($rs)-r s(源寄存器):指定存储单元的基址寄存器-r t(目标寄存器):指定目标寄存器,用于存储从存储单元中加载的数据-o ff se t:用于指定存储单元的偏移量,计算出实际地址功能描述:l w指令用于从存储单元中加载数据到目标寄存器。

它通过基址寄存器和偏移量计算出实际地址,并将存储单元中的数据加载到目标寄存器中。

2.s w指令字段描述:-指令格式:sw$r t,o f fs et($rs)-r s(源寄存器):指定存储单元的基址寄存器-r t(目标寄存器):指定源寄存器,用于存储到存储单元中的数据-o ff se t:用于指定存储单元的偏移量,计算出实际地址功能描述:s w指令用于将源寄存器中的数据存储到指定的存储单元中。

它通过基址寄存器和偏移量计算出实际地址,并将源寄存器中的数据存储到该地址对应的存储单元中。

算术和逻辑指令3.a d d指令字段描述:-指令格式:ad d$rd,$rs,$rt-r s(源寄存器1):参与运算的第一个源寄存器-r t(源寄存器2):参与运算的第二个源寄存器-r d(目标寄存器):用于存储运算结果功能描述:a d d指令用于将两个源寄存器中的数据相加,并将结果存储到目标寄存器中。

4.s u b指令字段描述:-指令格式:su b$rd,$rs,$rt-r s(源寄存器1):参与运算的第一个源寄存器-r t(源寄存器2):参与运算的第二个源寄存器-r d(目标寄存器):用于存储运算结果功能描述:s u b指令用于将源寄存器2中的数据从源寄存器1中的数据减去,并将结果存储到目标寄存器中。

MIPS指令集(共31条)

注意:因为MIPS16只有16个16位的寄存器,所以JAL指令中$31改成$15, 所有立即数均无需扩展,LUI指令直接就是将立即数付给RT寄存器。

$1=0

if (rs < rt) rd=1 else rd=0 ;其中rs=$2,rt=$3, rd=$1

sltu

000000

rs

rt

rd

00000

101011

sltu $1,$2,$3

if($2<$3)

$1=1 else

$1=0

if (rs < rt) rd=1 else rd=0 ;其中rs=$2,rt=$3, rd=$1

goto PC+4+40

if (rs != rt) PC <- PC+4 + (sign-extend)immediate<<2

slti

001010

rs

rt

immediate

slti $1,$2,10

if($2<10)

$1=1 else

$1=0

if (rs <(sign-extend)immediate) rt=1 else rt=0 ;

PC <- rs

I-type

op

rs

rt

immediate

addi

001000

rs

rt

immediate

addi $1,$2,100

$1=$2+100

rt <- rs + (sign-extend)immediate ;其中rt=$1,rs=$2

addiu

001001

MIPS指令集

MIPS CPU的一次操作可加载或存储1到8个字节的数据。

由于乘法的结果返回的速度不足以使下一条指令能够自动得到这个结果,乘法结果寄存器是互锁的(interlocked)。

在乘法操作完成之前试图读取结果寄存器就是导致CPU停止运行,直到完成。

和其他一些更简单的RISC体系结构相比,MIPS体系结构的目标之一是:体系结构朝着64位发展,从而使得地址的段式结构变得没有任何必要。

(在64位版本的X86核PowerPC中还有这个负担)功能分组:空操作:nop、ssnop(不能和其他指令同时发射,至少需要一个时钟周期)寄存器间的数据传送指令:move、movf、movt、movn、movz(后四个为条件传递指令)常数加载指令:dla、la(获取某些标号地址或程序中变量地址的宏指令);dli、li(加载常数立即数指令);lui(加载高位立即数指令)算术/逻辑操作指令:addu、addiu、daddu,daddiu(加法指令);dsub、sub(会触发溢出陷入的减法操作);dsubu、subu(普通减法指令);abs、dabs(求绝对值操作);dneg、neg、dnegu、negu(一元非操作);and、andi、or、ori、xor、xori、nor、not(按位逻辑指令);drol、dror、rol、ror(循环左移和右移);dsll、dsll32、dsllv(64位左移,低位补零);dsra、dsra32、dsrav(64位算术右移指令);dsrl、dsrl32、dsrlv(64位逻辑右移指令);sll、sllv(32位左移指令);sra、srav(32位算术右移指令);srl、srlv(32位逻辑右移指令);slt、slti、sltiu、sltu(硬件指令,条件满足就写入1,否则写0);seq、sge、sgeu、sgt、sgtu、sle、slue、sne (根据更复杂的条件设置目的寄存器的宏指令)整数乘法、除法以及求余指令:ddiv、ddivu、div、divu(整数除法的3操作数宏指令分别处理64位或32位有符号或无符号数);divo、divou(明确该指令是带有溢出检查的除法指令);dmul、mul(3操作数64位或32位乘法指令,没有溢出检查);mulo、mulou、dmulo、dumlou(乘法宏指令,如果结果不能存入一个通用寄存器,发生溢出,触发异常);dmult、dmultu、mult、multu(执行有符号/无符号32/64位乘法的机器指令);drem、dremu、rem、remu(求余操作);mfhi、mflo、mthi、mtlo(用于访问整数乘除单元的结果寄存器hi和lo)存取指令(内存访问指令):lb、lbu(加载一个字节,高位可以补零,或进行符号扩展,以补充整个寄存器的长度);ld(加载一个双字);ldl、ldr、lwl、lwr、sdl、sdr、swl、swr(向左、向右加载、存储一个字、双字);lh、lhu(加载一个半字,高位可以补零,或进行符号扩展,以补充整个寄存器的长度);lw、lwu(加载一个字);pref、prefx(把数据预取到缓冲);sb、sd、sh、sw(存储字节、双字、半字、字);uld、ulh、ulhu、ulw、usd、usw、ush(地址非对齐的数据存取宏指令);l.d、l.s、s.d、s.s(存取双精度和单精度浮点数的指令,地址必须对齐);ldxcl、lwxcl、sdxcl、swxcl(采用基址寄存器+偏移寄存器的寻址方式存取指令);跳转、分支和子程序调用指令:j(无条件跳转到一个绝对地址,访问256M的代码空间);jal、jalr(直接或间接子程序调用,这种跳转不仅能跳转到指定地址,而且可以顺便把返回地址(当前指令地址+8)放到ra寄存器中);b(基于当前指令地址的无条件相对跳转);bal (基于当前地址的函数调用指令);bc0f、bc0f1、bc0t、bc0t1、bc2f、bc2f1、bc2t、bc2t1(根据协处理器0和2的条件标志进行跳转);bc1f、bc1f1、bc1t、bc1t1(根据浮点条件标志位进行跳转);beq、beq1、beqz、beqz1、bge、bge1、bgeu、bgeu1、bgez、bgez1、bgt、bgt1、bgtu、bgtu1、bgtz、bgtz1、ble、ble1、bleu、bleu1、blez、blez1、blt、blt1、bltu、bltu1、bltz、bltz1、bne、bnel、bnez、bnezl(双操作数和单操作数的比较跳转指令);bgeza1、bgeza11、bltza1、bltza11(如果需要,这些指令是用于有条件函数调用的原始机器指令);断点及陷阱指令:break(产生一个“断点”类型的异常);sdbbp(产生EJTAG异常的断点指令);syscall(产生一个约定用于系统调用的异常类型);teq、teqi、tge、tgei、tgeiu、tgeu、tlt、tlti、tltiu、tltu、tne、tnei(条件异常指令,对一个或两个操作数进行条件测试);协处理器0的功能:cfc0、ctc0(把数据拷进和拷出协处理器0的控制寄存器);mfc0、mtc0、dmfc0、dmtc0(在通用寄存器和协处理器0寄存器之间交换数据);cfc2、ctc2、dmfc2、dmtc2、mfc2、mtc2(协处理器2的指令)。

mips汇编指令手册

MIPS汇编指令手册是一本详细介绍MIPS架构下汇编语言的书籍。

它包含了所有MIPS处理器支持的指令,以及这些指令的具体用法和示例。

首先,我们需要了解什么是MIPS架构。

MIPS(Microprocessor without Interlocked Pipeline Stages)是一种精简指令集计算机(RISC)架构,由斯坦福大学开发。

它的设计理念是简单、清晰和易于实现,这使得它在嵌入式系统和教育领域得到了广泛的应用。

在MIPS汇编指令手册中,我们可以看到各种类型的指令,包括数据传输指令、算术逻辑指令、控制流指令等。

每种指令都有其特定的格式和操作数,例如,数据传输指令通常包括一个源操作数和一个目标操作数,而算术逻辑指令则可能有一个或多个操作数。

在编写MIPS汇编程序时,我们需要遵循一定的规则。

首先,我们需要使用正确的指令格式。

其次,我们需要确保我们的程序没有语法错误。

最后,我们需要确保我们的程序能够正确地执行我们想要的操作。

在实际操作中,我们可以使用MIPS汇编器来编译我们的程序。

MIPS汇编器会将我们的汇编代码转换为机器代码,然后我们可以将这个机器代码加载到MIPS处理器上运行。

总的来说,MIPS汇编指令手册是学习和使用MIPS汇编语言的重要工具。

通过阅读和理解这本书,我们可以掌握MIPS汇编语言的基本知识和技能,从而能够编写出高效、可靠的MIPS 汇编程序。

c语言 mips指令

c语言 mips指令MIPS指令集是一种32位精简指令集(RISC)体系结构,它在计算机体系结构领域具有非常广泛的应用。

在编写C语言程序时,通常需要将高级语言的代码转化为MIPS指令集的汇编代码。

以下是一些关于C语言和MIPS指令集的相关参考内容,其中不包含链接的详细解释:1. C语言的数据类型映射到MIPS指令集的寄存器:- int类型通常映射到整数寄存器($t0-$t9)- float类型通常映射到浮点寄存器($f0-$f31)- char类型通常也映射到整数寄存器,但需要使用指令来执行字节操作2. C语言的条件语句(if-else语句)在MIPS指令集中的实现: - 使用比较指令(比如"slt", "sltu")将两个操作数进行比较- 根据比较的结果,使用分支指令(比如"beq", "bne", "j")跳转到不同的代码块- 可以使用标签(label)来标记不同的代码块,以便跳转3. C语言的循环语句(for循环、while循环)在MIPS指令集中的实现:- 使用比较指令判断循环条件,如果条件满足,则执行循环体内的指令- 在循环体内执行相应的操作,包括更新循环变量的值- 使用分支指令(比如"beq", "bne", "j")跳转到循环开头或循环结束的位置4. C语言的函数调用和参数传递在MIPS指令集中的实现:- 使用特殊的寄存器(比如$ra、$fp、$sp)来保存函数的返回地址、帧指针和栈指针- 将函数参数保存在寄存器或者栈中,并在函数内部使用它们- 使用分支指令跳转到函数的入口,执行函数体内的指令- 使用jr指令返回到调用函数的位置5. C语言中的数组和指针在MIPS指令集中的实现:- 使用基址寄存器(比如$gp)和偏移量来访问数组的元素- 使用la指令加载数组的地址到寄存器,使用lw和sw指令进行读取和存储操作- 使用指针变量保存地址,进行间接寻址操作6. C语言中的结构体和联合体在MIPS指令集中的实现:- 结构体和联合体的成员通常按照顺序在内存中排列- 使用指令来访问结构体和联合体的成员,比如使用lb和sb指令加载和存储字节型成员这些参考内容可以帮助程序员理解在C语言程序中,各种语法和语义对应着MIPS指令集的实现方式。

MIPS指令集汇总

MIPS指令集汇总以下是一些常用的MIPS指令:1.算术和逻辑操作:- add:将两个寄存器中的值相加,并将结果存储到目标寄存器中。

- sub:将第一个寄存器的值减去第二个寄存器的值,并将结果存储到目标寄存器中。

- mult:将两个寄存器中的值相乘,并将结果存储在两个特殊寄存器(HI和LO)中。

- div:将第一个寄存器的值除以第二个寄存器的值,并将结果存储在两个特殊寄存器(HI和LO)中。

- and:对两个寄存器中的值进行按位与操作,并将结果存储到目标寄存器中。

- or:对两个寄存器中的值进行按位或操作,并将结果存储到目标寄存器中。

- xor:对两个寄存器中的值进行按位异或操作,并将结果存储到目标寄存器中。

2.数据传输指令:- lw:从内存中加载一个字(4个字节)的数据到指定的寄存器中。

- sw:将指定寄存器中的数据存储到内存的指定位置中。

- lb:从内存中加载一个字节的数据到指定的寄存器中。

- sb:将指定寄存器中的数据的低8位存储到内存的指定位置中。

3.分支和跳转指令:- beq:如果两个寄存器中的值相等,则跳转到目标地址。

- bne:如果两个寄存器中的值不相等,则跳转到目标地址。

-j:无条件跳转到目标地址。

- jr:无条件跳转到一个寄存器中存储的地址。

- jal:有条件跳转到目标地址,并将返回地址保存在链接寄存器($ra)中。

4.系统调用指令:- syscall:执行一个系统调用,通过系统调用号(存储在$v0寄存器中)来定义执行的操作。

5.位移指令:- srl:对寄存器中的值进行逻辑右移。

- sll:对寄存器中的值进行逻辑左移。

- sra:对寄存器中的值进行算术右移。

除了上述指令外,还有一些其他的MIPS指令,如条件分支和加载延迟等。

此外,MIPS还支持浮点运算指令集(MIPS-FP),用于处理浮点运算。

总结起来,MIPS指令集包含了各种算术和逻辑操作、数据传输、分支和跳转、系统调用以及位移指令。

MIPS指令详解

MIPS指令详解计算机组成原理第五章指令系统5.6 MIPS指令详解1R 型指令000000R s R t shamt R d 6bits funct5bits 5bits 5bits 5bits 6bits R 型指令操作数和保存结果均通过寄存器进行;◆op :操作码,所有R 型指令中都全为0;◆rs :寄存器编号,对应第1个源操作数;◆rt :寄存器编号,对应第2个源操作数;◆rd :寄存器编号,据此保存结果;◆shamt :常数,在移位指令中使用;◆funct :功能码,指定指令的具体功能;1R型指令3寄存器R 型指令■R 型指令存在3种不同类型指令功能:$rd ← $rs op $rt指令[31:26][25:21][20:16][15:11][10:6][5:0]指令功能add 000000rs rt rd 00000100000寄存器加sub 000000rs rt rd 00000100010寄存器减and 000000rs rt rd 00000100100寄存器与or 000000rs rt rd 00000100101寄存器或xor000000rsrtrd00000100110寄存器异或1R 型指令1R型指令2寄存器R型指令指令[31:26][25:21][20:16][15:11][10:6][5:0]指令功能sll00000000000rt rd sa000000逻辑左移srl00000000000rt rd sa000010逻辑右移sra00000000000rt rd sa000011算术右移指令功能:$rd ← $rt shift sajr rs;1寄存器R 型指令指令[31:26][25:21][20:16][15:11][10:6][5:0]指令功能jr000000rs000000000000000001000寄存器跳转1R 型指令PC ← rs◆op :标识指令的操作功能;◆rs :第1个源操作数,是寄存器操作数;◆rt :目的寄存器编号,用来保存运算结果;◆imm :第2个源操作数,立即数;操作数中涉及立即数,结果保存到寄存器;OPRs R t6bits 立即数5bits 5bits 16bitsI 型指令2I 型指令指令[31:26][25:21][20:16][15:0]指令功能addi001000rs rt imm 寄存器和立即数“加”andi 001100rs rt imm 寄存器和立即数“与”ori 001101rs rt imm 寄存器和立即数“或”xori 001110rs rt imm 寄存器和立即数“异或”lw 100011rs rt imm 从存储器中读取数据sw 101011rs rt imm 把数据保存到存储器beq 000100rs rt imm 寄存器相等则转移bne 000101rsrt imm 寄存器不等则转移lui00111100000rt imm设置寄存器的高16位2I 型指令■I 型指令存在4种不同类型面向运算的I 型指令指令[31:26][25:21][20:16][15:0]指令功能addi 001000rs rt imm 寄存器和立即数“加”andi 001100rs rt imm 寄存器和立即数“与”ori 001101rs rt imm 寄存器和立即数“或”xori001110rsrtimm寄存器和立即数“异或”addi/andi/ori/xorirt, rs, imm; # $rt ← $rs op E(imm)2I 型指令第一条指令是进行符号扩展,其余是0扩展面向访存的I 型指令指令[31:26][25:21][20:16][15:0]指令功能lw 100011rs rt imm 从存储器中读取数据sw 101011rs rt imm 把数据保存到存储器lw rt, imm(rs) # $rt ← mem[$rs+E(imm)]sw rt, imm(rs) # mem[$rs+E(imm)] ←$rtMIPS32中唯一两条访问存储器的指令(RISC)2I 型指令面向数位设置的I 型指令指令[31:26][25:21][20:16][15:0]指令功能lui 00111100000rt imm 设置寄存器的高16位lui rt, imm # $rt ← imm<<16(空位补0)2I 型指令面向条件转移(分支)的I 型指令指令[31:26][25:21][20:16][15:0]指令功能beq 000100rs rt imm 寄存器相等则转移bne000101rsrtimm寄存器不等则转移beq rs, rt, imm bne rs, rt, imm#if($rs==$rt) PC←PC+E(imm)<<2是标准的PC 相对寻址方式其中imm 要先“带符号扩展”成32位,再左移2位。

MIPS Instruction Set (MIPS指令集)

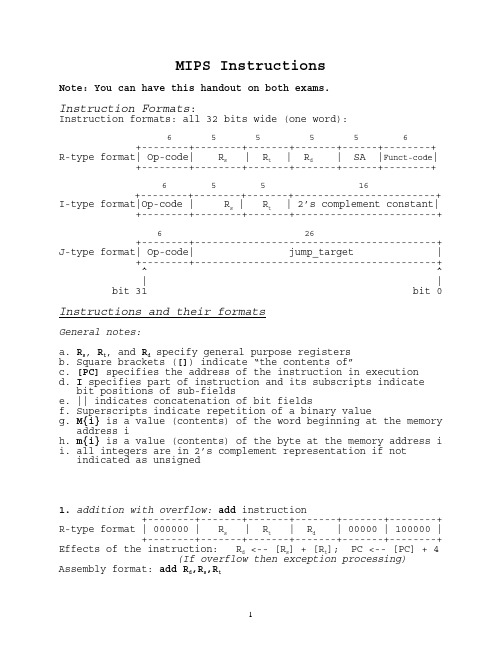

MIPS InstructionsNote: You can have this handout on both exams.Instruction Formats : Instruction formats: all 32 bits wide (one word):6 5 5 5 5 6+--------+--------+-------+-------+------+--------+ R-type format| Op-code| R s | R t | R d | SA |Funct-code | +--------+--------+-------+-------+------+--------+ 6 5 5 16 +--------+--------+-------+------------------------+ I-type format|Op-code | R s | R t | 2’s complement constant| +--------+--------+-------+------------------------+ 6 26 +--------+-----------------------------------------+ J-type format| Op-code| jump_target | +--------+-----------------------------------------+ ^ ^ | | bit 31 bit 0 Instructions and their formatsGeneral notes: a. R s , R t , and R d specify general purpose registers b. Square brackets ([]) indicate “the contents of” c. [PC] specifies the address of the instruction in execution d. I specifies part of instruction and its subscripts indicate bit positions of sub-fields e. || indicates concatenation of bit fields f. Superscripts indicate repetition of a binary value g. M{i} is a value (contents) of the word beginning at the memory address i h. m{i} is a value (contents) of the byte at the memory address i i. all integers are in 2’s complement representation if not indicated as unsigned 1. addition with overflow: add instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | R s | R t | R d | 00000 | 100000 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: R d <-- [R s ] + [R t ]; PC <-- [PC] + 4 (If overflow then exception processing) Assembly format: add R d ,R s ,R t2. add without overflow: addu instructionIdentical as add instruction, except: - funct=33dec - overflow ignored 3. subtract with overflow: sub instruction+--------+-------+------+-------+-------+--------+ R-type format | 000000 | R s | R t | R d | 00000 | 100010 | +--------+-------+------+-------+-------+--------+ Effects of the instruction: R d <-- [R s ] - [R t ]; PC <-- [PC] + 4 (If overflow then exception processing) Assembly format: sub R d ,R s ,R t 4. subtract without overflow: subu instructionIdentical as sub instruction, except: - funct=35dec - overflow ignored 5. multiply: mul instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | R s | R t | 00000 | 00000 | 011000 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction:Hi||Lo <-- [R s ] * [R t ]; PC <-- [PC] + 4 Assembly format: mult R s ,R t 6. unsigned multiply: mulu instructionIdentical as mut instruction, except: - funct = 25dec - contents of R s and R t are considered as unsigned integers 7. divide: div instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | R s | R t | 00000| 00000 | 011010 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: Lo <-- [R s ] / [R t ]; Hi <-- [R s ]mod[R t ] PC <-- [PC] + 4 Assembly format: div R s ,R t 8. unsigned divide: divu instructionIdentical as div instruction, except: - funct = 27dec - contents of R s and R t are considered as unsigned integers9. set less than: slt instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | R s | R t | R d | 00000 | 101010 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: if [R s ] < [R t ] then R d <-- 031 || 1 else R d <-- 032; PC <-- [PC] + 4 Assembly format: slt R d ,R s ,R t 10. set less than unsigned: sltu instructionIdentical as slt instruction, except: - funct = 43dec - contents of R s and R t are considered as unsigned integers. 11. logical and: and instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | R s | R t | R d | 00000 | 100100 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: R d <-- [R s ] AND [R t ]; PC <-- [PC] + 4 Assembly format: and R d ,R s ,R t 12 - 14. logical or, n or & exclusive or: or , nor , & xor instructions Identical as and instruction, except: - funct=37dec for or instruction - funct=39dec for nor instruction - funct=40dec for xor instruction - appropriate logical function performed instead of logical and 15. addition immediate with overflow: addi instruction+--------+-------+-------+-----------------------+ I-type format:| 001000 | R s | R t | immediate | +--------+-------+-------+-----------------------+ Effects of the instruction: R t <-- [R s ] + ([I 15]16 || [I 15..0]); PC <-- [PC] + 4 (If overflow then exception processing) Assembly format: addi R t ,R s ,immediate 16. addition immediate without overflow: addiu instruction Identical as addi instruction, except: - op-code=9dec - overflow ignored17. set less than immediate: slti instruction+--------+-------+-------+-----------------------+ I-type format: | 001010 | R s | R t | immediate | +--------+-------+-------+-----------------------+ Effects of the instruction: if [R s ] < ([I 15]16 || [I 15..0]) then R t <-- 031|| 1 else R t <-- 032 PC <-- [PC] + 4 Assembly format: slti R t ,R s ,immediate 18. set less than immediate unsigned: sltiu instructionIdentical as slti instruction, except: - op-code = 11dec - contents in the comparison are considered as unsigned integers. 19. logical and immediate: andi instruction+--------+-------+-------+-----------------------+ I-type format:| 001100 | R s | R t | immediate | +--------+-------+-------+-----------------------+ Effects of the instruction: R t <-- [R s ] AND (016 || [I 15..0]); PC <-- [PC] + 4 Assembly format: andi R t ,R s ,immediate 20-21. logical or immediate & xor immediate: ori , & xori instr. Identical as andi instruction, except: - op-code=13dec for ori instruction - op-code=14dec for xori instruction - appropriate logical function performed instead of logical and 22. load word : lw instruction+--------+-------+-------+-----------------------+ I-type format: | 100011 | R s | R t | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: R t <-- M{[R s ] + [I 15]16 || [I 15..0]} PC <-- [PC] + 4 (If an illegal memory address then exception processing) Assembly format: lw R t ,offset(R s ) 23. store word : sw instruction+--------+-------+-------+-----------------------+ I-type format: | 101011 | R s | R t | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: M{[R s ] + [I 15]16 || [I 15..0]} <-- [R t ] PC <-- [PC] + 4 (If an illegal memory address then exception processing) Assembly format: sw R t ,offset(R s )24. load unsigned byte : lbu instruction+--------+-------+-------+-----------------------+ I-type format: | 100100 | R s | R t | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: R t <-- 024 || m{[R s ] + [I 15]16 || [I 15..0]} PC <-- [PC] + 4 (If an illegal memory address then exception processing) Assembly format: lbu R t ,offset(R s ) 25. load byte : lb instructionIdentical as lbu instruction, except: - leftmost 24 bits of R t are loaded by a value of leftmost bit of the byte instead of zeros - op-code =32dec 26. store byte : sb instruction+--------+-------+-------+-----------------------+ I-type format: | 101000 | R s | R t | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: m{[R s ] + [I 15]16 || [I 15..0]} <-- [R t ]7..0 PC <-- [PC] + 4 (If an illegal memory address then exception processing) Assembly format: sb R t ,offset(R s ) 27. load upper immediate: lui instruction+--------+-------+-------+-----------------------+ I-type format: | 001111 | 00000 | R t | immediate | +--------+-------+-------+-----------------------+ Effects of the instruction: R t <-- [I 15-0] || 016; PC <-- [PC] + 4 Assembly format: lui R t ,immediate 28. branch on equal: beq instruction+--------+-------+-------+-----------------------+ I-type format: | 000100 | R s | R t | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: if [R s ] = [R t ] then PC <-- [PC] + 4 + ([I 15]14 || [I 15..0] || 02) (i.e. PC <-- [PC] + 4 + 4*offset) else PC <-- [PC] + 4 Assembly format: beq R s ,R t ,offset29. branch on not equal: bne instruction+--------+-------+-------+-----------------------+ I-type format: | 000101 | R s | R t | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: if [R s ] <> [R t ] then PC <-- [PC] + 4 + ([I 15]14 || [I 15..0] || 02) else PC <-- [PC] + 4 Assembly format: bne R s ,R t ,offset 30. branch on less than or equal zero: blez instruction+--------+-------+-------+-----------------------+ I-type format: | 000110 | R s | 00000 | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: if [R s ] < 0 then PC <-- [PC] + 4 + ([I 15]14 || [I 15..0] || 02) Assembly format: blez R s ,offset 31. branch on greater than zero: bgtz instruction+--------+-------+-------+-----------------------+ I-type format: |000111 | R s | 00000 | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: if [R s ] > 0 then PC <-- [PC] + 4 + ([I 15]14 || [I 15..0] || 02) else PC <-- [PC] + 4 Assembly format: bgtz R s ,offset 32. branch on less than zero: bltz instruction+--------+-------+-------+-----------------------+ I-type format: |000001 | R s | 00000 | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: if [R s ] < 0 then PC <-- [PC] + 4 + ([I 15]14 || [I 15..0] || 02) else PC <-- [PC] + 4 Assembly format: bltz R s ,offset 33. jump: j instruction+--------+-----------------------------------------+ J-type format|000010 | jump_target | +--------+-----------------------------------------+ Effects of the instruction: PC <-- [PC 31..28] || [I 25..0] || 02Assembly format: j jump_target34. jump and link: jal instruction+--------+-----------------------------------------+ J-type format|000011 | jump_target | +--------+-----------------------------------------+ Effects of the instruction: R 31 <-- [PC] + 4 PC <-- [PC 31..28] || [I 25..0] || 02Assembly format: jal jump_target 35. jump register: jr instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | R s | 00000 | 00000 | 00000 | 001000 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: PC <-- [R s ] Assembly format: jr R s 36. jump and link register: jalr instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | R s | 00000 | R d | 00000 | 001001 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: R d <-- [PC] + 4; PC <-- [R s ] Assembly format: jalr R d ,R s 37. no operation: nop instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | 00000 | 00000 | 00000 | 00000 | 000000 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: PC <-- [PC] + 4 Assembly format: nop (= sll R 0,0 shift logical left 0) 38. move from Hi: mfhi instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | 00000 | 00000 | R d | 00000 | 010000 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: R d <-- [Hi]; PC <-- [PC] + 4 Assembly format: mfhi R d39. move from Lo: mflo instruction+--------+-------+-------+-------+-------+--------+ R-type format | 000000 | 00000 | 00000 | R d | 00000 | 010010 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: R d <-- [Lo]; PC <-- [PC] + 4 Assembly format: mflo R dException HandlingWhen a condition for any exception (overflow, illegal op-code, division by zero, etc.) occurs the following hardware exception processing is performed: EPC <-- [PC] / | 028 || 1010 if illegal op-code (10) Cause_Reg <-- | 028 || 1100 if overflow (12) | 029 || 100 if illegal memory address (4) \ …………… etc. PC <-- 80000180hex 40. move from EPC: mfepc instruction+--------+-------+-------+-------+-------+--------+ R-type format | 010000 | 00000 | R t | 01110 | 00000 | 000000 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: R d <-- [EPC]; PC <-- [PC] + 4 Assembly format: mfepc R t (This is mfc0 Rt,CP0reg14) 41. move from Cause_Reg: mfco instruction+--------+-------+-------+-------+-------+--------+ R-type format | 010000 | 00000 | R d | 01101 | 00000 | 000000 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: R d <-- [Cause_Reg]; PC <-- [PC] + 4 Assembly format: mfco R t (This is mfc0 Rt,CP0reg13) Floating Point Instructions42. load word into co-processor 1: lwc1 instruction+--------+-------+-------+-----------------------+ I-type format: | 110001 | R s | f t | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: f t <-- M{[R s ] + [I 15]16 || [I 15..0]} PC <-- [PC] + 4 Assembly format: lwc1 f t ,offset(R s )43. store word from co-processor 1: swc1 instruction+--------+-------+-------+-----------------------+ I-type format: | 111001 | R s | f t | offset | +--------+-------+-------+-----------------------+ Effects of the instruction: M{[R s ] + [I 15]16 || [I 15..0]} <-- [f t ] PC <-- [PC] + 4 Assembly format: swc1 f t ,offset(R s )44. addition single precision: add.s instruction+--------+-------+-------+-------+-------+--------+ R-type format | 010001 | 00000 | f t | f s | f d |000000 | +--------+-------+-------+-------+-------+--------+ Effects of the instruction: f d <-- [f s ] + [f t ]; PC <-- [PC] + 4 (If overflow then exception processing) Assembly format: add.s R d ,R s ,R t 45. addition double precision: add.d instruction+--------+-------+-------+-------+-------+--------+ R-type format | 010001 | 00001 | f t | f s | f d |0000000| +--------+-------+-------+-------+-------+--------+ Effects of the instruction:f d ||f d+1<-- [f s ]||[f s+1] + [f t ]||[f t+1]; PC <-- [PC] + 4 (If overflow then exception processing) Assembly format: add.d f d ,f s ,f t45. subtract single precision: sub.s instructionSimilar as add.s but with funct=146. subtract double precision: sub.d instruction Similar as add.d but with funct=147. multiply single precision: mul.s instruction Similar as add.s but with funct=248. multiply double precision: mul.d instruction Similar as add.d but with funct=249. divide single precision: div.s instruction Similar as add.s but with funct=3 50. divide double precision: div.d instructionSimilar as add.d but with funct=3。

mips指令集

mips指令集加入日期条目指令2016年3月18日1sb2li(load immediate)3la(load address)4move5nop6bal7.set8.global9mtc010or11j2016年3月19日1.align2016年3月21日1bne(branch not equal)2subu3and4sw5addiu6srl7bnez(branch not equal zero) 2016年3月26日1LB 2LH3LW4LD5L.S6L.D7SB8SH9SW10SD11S.S12S.D2016年3月28日1beq(branch equal)2sll2016年3月31日1b2 .ent3beqz(Branch if Equal Zero )2016年4月1日1sltMIPS指令集(时序)解释把一个字节的数据从寄存器存储到存储器指令用于将一个立即数存入一个通用寄存器指令用于将一个地址(或者标签)存入一个通用寄存器将一个寄存器的值传给另外一个寄存器no-operationpc相对的子程序/函数调用设置状态设置全局可见将数据从特殊寄存器复制到通用寄存器或运算,两个寄存器中的内容相或直接跳转指令,跳转的地址在指令中bne s,t,label if (s != t) goto label三操作数减运算交运算存储一个字addiu是GPR和立即数做无符号加法操作32位逻辑右移条件转移指令,当寄存器中内容不为0时转移发生从存储器中读取一个字节的数据到寄存器从存储器中读取半个字的数据到寄存器从存储器中读取一个字的数据到寄存器从存储器中读取双字的数据到寄存器从存储器中读取单精度浮点数到寄存器从存储器中读取双精度浮点数到寄存器把一个字节的数据从寄存器存储到存储器把半个字节数据从寄存器存储到存储器把一个字的数据从寄存器存储到存储器把t2寄存器中值(1 Word),存储到t0的值再减去偏移量12, 所指向的RAM 中把两个字节的数据从寄存器存储到存储器把单精度浮点数从寄存器存储到存储器把双精度数据从存储器存储到存储器if (s == t) goto lable左移转移到标签告诉assembler将这一点标志为“name”函数的起始点,为调试提供信息。

MIPS 中文学习手册

对於熟悉汇编语言但不熟悉 MIPS 的读者,下面是一些例子。

/* this is a comment */ #so is this

entrypoint: #this's a label

其他方面,所有的寄存器都是一样的。可以被用在任何一个指令中(你也可以用$0 作 为一个指令的目标寄存器。当然不管你存入什么数据,数据都消失了。)

MIPS 体系结构下,程序计数器不是一个寄存器,其实你最好不要去那样想。在一个 具有流水线的 CPU 中,程序计数器的值在一个给定的时刻有多个可选值。这一点有点 迷惑人。jal 指令的返回地址跟随其后的第二条指令。 ... jal printf move $4, $6 xxx # return here after call

addu $1, $2, $3 # (registers) $1 = $2 + $3

与大多数汇编语言一样, MIPS 汇编语言也是以行为单位的。每一行的结束是一个指 令的结束,并且忽略任何“#”之后的内容,认为是注释。在一行里可以有多条指令。 指令之间要用分号“;”隔开。

一个符号(label)是一个后面跟着冒号“:”的字。符号可以是任何字符串的组合。 符号被用来定义一段代码的入口和定义数据段的一个存储位置。

在计算世界中, "体系结构"一词被用来描述一个抽象的机器,而不是一个具体的机器 实现. 这一点非常有用的, 用来区分在市场广告上已经被滥用的"体系结构"这个术 语. 读者有可能不熟悉"抽象描述",但其概念其实很简单.

当然,如果你是一个喜欢在 滑的路上开快车的司机,前轮还是后轮驱动就很有所谓 了。计算机也是如此。如果你需要高性能计算,一个计算机的具体参数与实现对你 就很重要了。

计算机设计与实践——MIPS基本指令

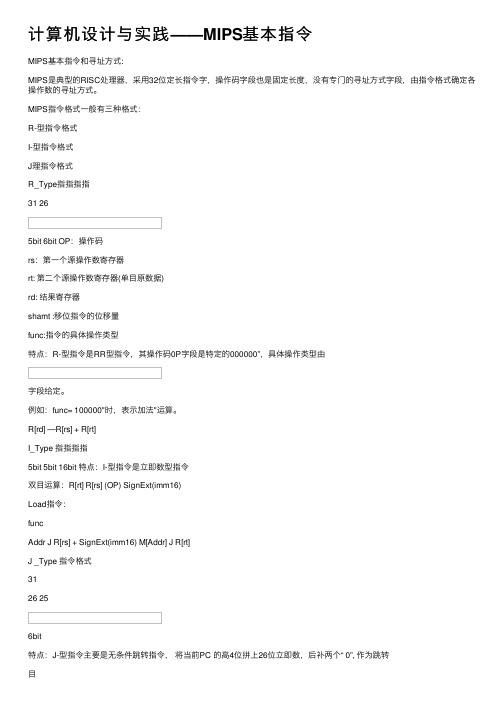

计算机设计与实践——MIPS基本指令MIPS基本指令和寻址⽅式:MIPS是典型的RISC处理器,采⽤32位定长指令字,操作码字段也是固定长度,没有专门的寻址⽅式字段,由指令格式确定各操作数的寻址⽅式。

MIPS指令格式⼀般有三种格式:R-型指令格式I-型指令格式J理指令格式R_Type指指指指31 265bit 6bit OP:操作码rs:第⼀个源操作数寄存器rt: 第⼆个源操作数寄存器(单⽬原数据)rd: 结果寄存器shamt :移位指令的位移量func:指令的具体操作类型特点:R-型指令是RR型指令,其操作码0P字段是特定的000000”,具体操作类型由字段给定。

例如:func= 100000"时,表⽰加法"运算。

R[rd] —R[rs] + R[rt]I_Type 指指指指5bit 5bit 16bit 特点:I-型指令是⽴即数型指令双⽬运算:R[rt] R[rs] (OP) SignExt(imm16)Load指令:funcAddr J R[rs] + SignExt(imm16) M[Addr] J R[rt]J _Type 指令格式3126 256bit特点:J-型指令主要是⽆条件跳转指令,将当前PC 的⾼4位拼上26位⽴即数,后补两个“ 0”, 作为跳转⽬标地址。

R 型指令:定点运算: add / addu , sub / subu , sra , mult/multu , div/divu逻辑运算:and / or / nor , sll / srl⽐较分⽀:beq / bne / slt / sltu跳转指令: jrI 型指令:定点运算: addi / addiu逻辑运算:andi / ori⽐较分⽀:slti / sltiu数据传送: lw / sw/ lhu / sh / lbu / sb / luiJ 型指令:j / jalAddr J R[rs] + SignExt(imm16) R[rt] J M[Addr]Store 指令:计算数据地址(⽴即数要进⾏符号扩展)从存储器中取出数据,装⼊到寄存器中设计模块划分,教学安排1、MIPS格式指令系统设计2、指令存储器设计3、寄存器堆设计4、ALU设计---- 基本算术、逻辑单元的设计32位超前进位加法器的设计32位桶式移位寄存器的设计5、取指令部件的设计6、⽴即数处理单元设计7、单周期处理器设计⼀⼀R型指令的数据通路设计I型指令的数据通路设计Load/Store指令的数据通路设计分⽀指令/转移指令的数据通路设计综合12条指令的完整数据通路设计8、ALU控制单元设计9、主控制单元的设计10、单周期处理器总体验证11、异常和中断处理及其电路实现12、带有异常和中断处理功能的处理器的设计设计⽰例1指令存储器设计1指令存储器模块定义:指令存储器⽤于存放 CPU 运算的程序指令和数据等,采⽤单端⼝存储器设计,设计最⼤为64个存储单元,每个存储单元数据宽度为32bit 。

(完整word版)MIPS 指令集

000100

sllv $1,$2,$3

$1=$2<<$3

rdrt << rs;其中rs=$3,rt=$2, rd=$1

srlv

000000

rs

rt

rd

00000

000110

srlv $1,$2,$3

$1=$2>>$3

rdrt >> rs;(logical)其中rs=$3,rt=$2, rd=$1

if($2<10)

$1=1 else

$1=0

if (rs<(zero-extend)immediate) rt=1 else rt=0;其中rs=$2,rt=$1

J-type

op

address

j

000010

address

j 10000

goto 10000

PC(PC+4)[31..28],address,0,0;address=10000/4

andi $1,$2,10

$1=$2 | 10

rtrs | (zero-extend)immediate;其中rt=$1,rs=$2

xori

001110

rs

rt

immediate

andi $1,$2,10

$1=$2 ^ 10

rtrs xor (zero-extend)immediate;其中rt=$1,rs=$2

or

000000

rs

rt

rd

00000

100101

or $1,$2,$3

$1=$2 | $3

rdrs | rt;其中rs=$2,rt=$3, rd=$1

MIPS指令集及汇编

和R12000(1997年)等型号。 z 随后,MIPS公司把重点放在嵌入式系统。

{ 1999年发布MIPS32和MIPS64架构标准,集成了所有原 来MIPS指令集,并且增加了许多更强大的功能。陆续开发 了高性能、低功耗的32位处理器内核(core)MIPS324Kc 与高性能64位处理器内核MIPS64 5Kc。

{ 应用广泛的32位MIPS CPU包括R2000,R3000 其ISA都是MIPS I,另一个广泛使用的、含有许多 重要改进的64位MIPS CPU R4000及其后续产 品,其ISA版本为MIPS III

一、 MIPS简介

{ 1984年,MIPS计算机公司成立。1992年,SGI收购了 MIPS计算机公司。1998年,MIPS脱离SGI,成为MIPS 技术公司。

龙芯2E笔记本电脑运行 OpenOffice打开Word文档

ቤተ መጻሕፍቲ ባይዱ

二、MIPS体系结构

{ 指令集体系结构类型:寄存器——寄存器型

(1)寄存器的特点 (2)整数乘法单元和寄存器 (3)寻址方式 (4)存储器和寄存器中的数据类型 (5)流水线冒险

二、 MIPS体系结构——(1)寄存器

{ MIPS 包含32个通用寄存器

{ 2000年,MIPS公司发布了针对MIPS32 4Kc的版本以及 64位MIPS 64 20Kc处理器内核。

一、 MIPS简介

{ 基于龙芯2E处理器的千元的PC、1999元的笔记本电脑、 意法半导体3000万元购买龙芯2E 5年的生产和销售权, 国产操作系统内核在龙芯2E上测试成功。

mips 指令格式及功能

mips 指令格式及功能

MIPS指令格式分为三种类型:R型、I型和J型,分别用于表示寄存器操作、立即数操作和跳转操作。

R型指令格式为:op rd, rs, rt,其中op为操作码,rd为目标寄存器,rs和rt为源寄存器。

R型指令主要用于寄存器的操作,如加减乘除、逻辑运算等。

I型指令格式为:op rt, rs, imm,其中op为操作码,rt为目标寄存器,rs为源寄存器,imm为立即数。

I型指令主要用于立即数的操作,如加载数据、存储数据、分支、比较等。

J型指令格式为:op addr,其中op为操作码,addr为跳转地址。

J型指令主要用于跳转操作,如无条件跳转、寄存器间接跳转等。

MIPS指令的功能多种多样,包括算术运算、逻辑运算、加载存储操作、分支跳转等。

其中,常用的指令包括:

1. 加减运算指令:add、addu、sub、subu等。

2. 逻辑运算指令:and、or、xor、nor等。

3. 移位指令:sll、srl、sra等。

4. 比较指令:slt、sltu、seq、sne等。

5. 加载存储指令:lw、sw、lb、sb等。

6. 分支指令:beq、bne、blez、bgtz等。

7. 跳转指令:j、jal、jr等。

8. 其他指令:syscall、nop等。

总之,MIPS指令集丰富多彩,可以满足各种计算需求,是计算

机体系结构中重要的一部分。

mips汇编指令手册

mips汇编指令手册摘要:一、概述MIPS汇编指令手册二、MIPS汇编指令的基本结构1.指令格式2.操作码和操作数3.寄存器文件三、数据传输指令1.加载和存储指令2.寄存器间的数据传输四、算术和逻辑指令1.加法和减法指令2.乘法和除法指令3.逻辑指令五、移位和位操作指令1.移位指令2.位操作指令六、条件跳转和分支指令1.无条件跳转指令2.条件跳转指令3.分支指令七、循环指令1.循环开始和结束指令2.循环计数指令八、调用和返回指令1.调用指令2.返回指令九、中断和异常处理指令1.中断指令2.异常处理指令十、系统调用指令1.系统调用指令概述2.常用系统调用举例正文:一、概述MIPS汇编指令手册MIPS(Microprocessor without Interlocking Protection Structures)是一种精简指令集计算机(RISC)架构,广泛应用于嵌入式系统和处理器设计。

MIPS汇编指令手册提供了详细的指令集和编程指南,帮助开发者更好地使用MIPS处理器。

本文将简要介绍MIPS汇编指令的基本结构和分类,以供参考。

二、MIPS汇编指令的基本结构1.指令格式MIPS汇编指令采用固定长度的指令格式,包括操作码和操作数。

操作码表示指令的类型,操作数表示指令处理的数据。

2.操作码和操作数MIPS汇编指令的操作码和操作数分为两类:立即数和寄存器。

立即数直接参与运算,而寄存器表示要从寄存器文件中操作的数据。

3.寄存器文件MIPS处理器具有31个通用寄存器,分为两组:一组是30个32位寄存器(X0-X29),另一组是1个32位通用寄存器(PC)。

三、数据传输指令数据传输指令主要用于在内存和寄存器之间传输数据。

1.加载和存储指令加载指令(LDR)将内存中的数据加载到寄存器中,存储指令(STR)将寄存器中的数据存储到内存中。

2.寄存器间的数据传输寄存器间的数据传输可以通过指令如:MOV、CMP等实现。

mips的指令集

mips的指令集MIPS指令集是一种常见的计算机指令集架构,广泛应用于大多数工作站、服务器和嵌入式系统中。

本文将介绍MIPS指令集的基本特点、主要指令和应用领域。

一、MIPS指令集的基本特点MIPS指令集采用精简指令集计算机(RISC)的设计理念,以简洁、高效的指令集为特点。

其基本特点包括:1. 定长指令格式:MIPS指令集采用定长指令格式,每条指令占据32位,简化了指令解码过程,提高了指令的执行速度。

2. 加载/存储架构:MIPS指令集采用了加载/存储架构,只有专门的加载和存储指令可以访问内存,其他指令只能对寄存器进行操作,这样可以减少存储器的访问时间,提高了指令的执行效率。

3. 三地址指令格式:MIPS指令集的大多数指令都采用三地址指令格式,即指令中包含三个操作数的寄存器地址,使得指令的操作更加灵活。

二、MIPS指令集的主要指令1. 数据传输指令MIPS指令集提供了一系列数据传输指令,包括加载指令(例如lw、lb等)和存储指令(例如sw、sb等),用于将数据从内存加载到寄存器或将数据从寄存器存储到内存中。

2. 算术逻辑指令MIPS指令集提供了一系列算术逻辑指令,包括加法指令(例如add、addi等)、减法指令(例如sub、subi等)、乘法指令(例如mul、muli等)和逻辑运算指令(例如and、or等),用于进行基本的算术和逻辑运算。

3. 控制指令MIPS指令集提供了一系列控制指令,包括无条件跳转指令(例如j、jr等)、条件跳转指令(例如beq、bne等)和函数调用指令(例如jal、jalr等),用于实现程序的控制流程。

4. 浮点运算指令MIPS指令集还提供了一系列浮点运算指令,包括浮点加法指令(例如add.s)、浮点乘法指令(例如mul.s)和浮点比较指令(例如c.eq.s),用于进行浮点数的运算和比较。

三、MIPS指令集的应用领域由于MIPS指令集具有精简、高效的特点,因此在许多领域得到了广泛的应用,包括:1. 嵌入式系统:MIPS指令集在嵌入式系统中应用广泛,例如智能手机、路由器、数字电视等,这些系统对指令的执行效率和功耗有较高的要求,MIPS指令集正好满足了这些需求。

mips汇编指令手册

mips汇编指令手册摘要:1.MIPS 汇编指令手册简介2.MIPS 汇编指令的分类3.MIPS 汇编指令的寻址方式4.MIPS 汇编指令的指令集5.MIPS 汇编指令的应用领域正文:1.MIPS 汇编指令手册简介MIPS 汇编指令手册是一本详细描述MIPS(Microprocessor without Interlocked Pipeline Stages,无锁流水线处理器)指令集的参考书。

MIPS 汇编指令手册包含了MIPS 处理器能够理解和执行的所有指令,以及这些指令的格式、功能和寻址方式等内容。

对于计算机体系结构和汇编语言程序设计等相关领域的研究者和开发者来说,MIPS 汇编指令手册是一本非常重要的参考资料。

2.MIPS 汇编指令的分类MIPS 汇编指令可以分为三类:(1)存储器指令:这类指令主要用于对存储器进行读写操作,包括加载(load)和存储(store)指令。

(2)算术逻辑指令:这类指令主要用于执行各种算术和逻辑运算,包括加法、减法、乘法、除法等运算指令,以及与、或、非等逻辑运算指令。

(3)转移指令:这类指令主要用于控制程序的执行流程,包括条件跳转、无条件跳转、循环等指令。

3.MIPS 汇编指令的寻址方式MIPS 汇编指令的寻址方式主要有以下几种:(1)直接寻址:指令中直接给出操作数的地址。

(2)间接寻址:指令中给出操作数的地址的地址,需要通过两次访问存储器才能获取到操作数。

(3)寄存器寻址:指令中给出操作数在寄存器中的名字。

(4)立即寻址:指令中直接给出操作数,操作数紧跟在指令后面。

4.MIPS 汇编指令的指令集MIPS 汇编指令集包含了大量的指令,这里列举一些常见的指令:(1)加载指令:load(2)存储指令:store(3)算术运算指令:add、sub、mul、div(4)逻辑运算指令:and、or、not(5)转移指令:jmp、jz、jnz、循环指令等5.MIPS 汇编指令的应用领域MIPS 汇编指令广泛应用于计算机体系结构、操作系统、编译原理等领域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

盖了功能访运分跳 每编码 格式 描述 操作

示例 约束

编码

格式 描述

操作

示例 其他

本文从MIP 了MIPS 指令分类 指令类型访存

I-TYPE I-TYPE 运算

R-TYP R-TYP R-TYP 分支 I-TYPE 跳转

J-TYPE 每条指令具体表2:lw

31 26 lw 100011

6 lw rt, offset(GPR[rt] ← m Addr ← GPR GPR[rt] ← m lw $v1, 8($s Addr 必须是否则产生地表4:31 26 25 2special 000000

rs

6 5 add rd, rs, rt GPR[rd] temp ← (GP (GPR[rt]31||G if temp 32 ≠ te Signa else GPR[r add $s1, $s2不考虑溢出PS 指令集中选令集中典型的型 助记符

E LW E

SW

PE ADD

PE SUB PE

OR E BEQ 等E

J

体的指令编码w 加载字 25 21 20 base

rt

5 5 (base)

memory[GPR[b R[base] + sign_memory[Addr] 0)

是4的倍数(即Ad 地址错误异常

add 加 21 20 16 15 1rt rd

5 5

GPR[rs]+GPR[PR[rs]31||GPR[rs GPR[rt])

emp 31 then

alException(Int rd] ← temp 31..0 , $s3 。

MIPS 选择了7条典R-TYPE 指令表1

功能 OPC 加载字 存储字 加 减 或 等于转移跳转

码、指令功能 16 15 offset

16

base]+offset] _ext(offset)

ddr 1..0必须为00 11 10 6 5 0 00000ad 100 5 6[rt] s]) + tegerOverflow)

S-mini 指典型的指令构令、I-TYPE 1 MIPS-mini CODE/FUNCT (16 进制) 23H 2BH 0/20H 0/22H 0/25H 4H 2H

能以及约束如 00), 0dd

0000

)

编码格式描述操作示例其他

编码格式描述操作示例约束指令集

构成了MIPS 指令、J-TY 指令集 T

(R[rt] = Me Mem[ GPR GPR[rd] =GPR[rd] =GPR[rd] = if (GPR[rs]PC = PC PC= JumpA 如表2至表8所 表3: 码

31 26 25special 000000

6 式or rd, rs, r 述GPR[rd] 作GPR[rd] 例or $s1, $s 他

码

31 26sw 101011

6 式sw rt, offse 述memory[GP 作

Addr ← GP memory[A 例sw $v1, 8($束Addr 必须是否则产生地S-mini 指令集PE 指令,如操作

(VerilogHDL 语em[ GPR[rs]+si R[rs]+sign_ext(GPR[rs] + GPR GPR[rs] - GPR GPR[rs] | GPR ] == GPR[rt]) C + 4 + BranchA Addr

所示。

sw 存储字

表5:or 或

5 21 20 1

6 15 1rs rt rd

5 5 5 rt

← GPR[rs] OR ← GPR[rs] OR 2, $s3 6 25 21 20 base

rt

5 5 t(base)

PR[base]+offse PR[base] + sign ddr] ← GPR[rt $s0)

是4的倍数(即A 地址错误异常 集。

MIPS-mi 如表1所示。

语法描述)

ign_ext(offset) (offset) ] = R[R[rt] R[rt] R[rt] Addr 11 10 6 5 0 00000 o

100 5 6

R GPR[rt] R GPR[rt] 16 15 offse 16 et] ← GPR[rt] n_ext(offset) t] Addr1..0必须为

ni 涵

] [rt] 0

or 0101

6 0

et

为00),

编码

格式描述

操作

示例其他31 26 25

special

000000

6

sub rd,

GPR[rd]

temp←{G

{

if temp32

SignalE

else

GPR[rd]

endif

sub $s1,

temp32≠ te

不考虑溢出

编码

格式

描述

操作

示例

其他

表6:sub减

5 21 20 1

6 15

rs rt rd

5 5 5

rs, rt

← GPR[rs] >

GPR[RS]31,GPR

{GPR[rt]31 ,GP

≠ temp31 then

xception ( Integ

] ← temp 31…

$s2, $s3

emp31 代表计算

出。

31 26 2

j

000010

6

j target

J指令是PC

可以在当前P

PC ←{ (P

j Loop_End

如果需要跳转

11 10 6 5

d

00000 1

5 5

>> GPR[rt]

R[rs]}–

R[rt] }

gerOverflow )

算结果溢出。

表

25

相关的转移指

PC所在的256

PC31 . . 28), i

d

转范围超出了当

sub

00010

6

编码

格式

描述

操作

示例

其他

8:J跳转

instr_in

26

指令。

当把4GB

6MB区域内任

instr_index, 2

当前PC所在的

表7:be

码

31 26 2

beq

000100

6

式beq rs,

述If ( GPR[r

作

If ( GPR[r

PC←PC

else

PC ← P

例beq $s1

他

转

ndex

6

B划分为16

意跳转。

2’b00 }

的256MB区域

eq相等转移

25 21 20 1

rs rt

5 5

rt, offset

rs] == GPR[rt]

rs] == GPR

C+4 + sign_ext

PC + 4

, $s2, -2

个256MB区域,

内时,可以使J

16 15 0

offset

16

) then 转移

R[rt] )

tend( offset||02 )

,j指令

JR指令。

移

)。