集成电路的ESD保护

基于CMOS工艺的射频集成电路ESD保护研究

保 护 核 心 电 路 之 间相 互 作 用 不 明 显 ,

的氧 化 层 更 薄 , 各 种 材 料 层 之 间 的 隔 金 属 材 料 分 布 不 均 匀 能 够 产 生 出 杂 散

当 端 口 的 静 电 高 电 压 和 大 电 流 进 入 芯 离 节 更 浅 , 作 电 流 和 工 作 电 压 越 小 。 分 布 的 寄 生 电 感 和 寄 生 电 容 ,与 衬 底 工 片 内 部 时 , 护 电 路 动 作 , 大 电 流 在 电路 外 围寄 生参 数 耦合 效 应 的微 小 扰 材 料 之 间 形 成 电磁 场 耦 合 ,增 加 了衬 保 将

基于 C MOS工艺 的射频 集成 电路 E D S 保护研究

北 方工 业 大 学信 息 工 程 学 院 鞠 家 欣 姜 岩峰 鲍嘉 明 杨 兵 张 晓 波

S S 二 随 着 工 艺特 征 尺 寸 的 缩 小 , 频 集 外 部 寄 生 参 数 的 影 响 , 而 E D 保 护 电 效 应 。E D 保 护 电路 通 常 利 用 电 阻 、 射 成 电 路 承 受 的 静 电放 电 ( S 问 题 日 E D)

价。

护 电 路 的 作 用 。 这 个 问 题 已经 成 为 困 线 两 部 分 , 由于 要 承 受 住 高 电 压 、 电 大

1 引言 .

中击 扰 射 频 集 成 电 路 设 计 者 的 一 个 带 有 共 流 的 ; , 防 护 器 件 的 面 积 不 能 随 工

研 因 器 随着 半 导 体 工 艺 技 术 的 发 展 , 统 性 的 棘 手 难 题 。 因 此 , 究 射 频 核 心 被 艺 按 比 例 缩 小 的 原 则 而 减 小 , 此 , 传 S 的C MOS工 艺 生产 射频集 成 电路 已经 保 护 电路 与 E D 保 护 电 路 之 间 相 互 作 件面 积本 身 所带 有 的寄 生 电阻 、寄 生 采 S 成 为 可 能。 射 频集 成 电路 的特 征尺 寸 用 的 机 理 , 取 合 适 的 E D 防 护 措 施 ,

双极性集成电路的ESD保护

低 阻 能量 损 耗 : E 1 × V =, 2C 2和 E l = / ×I 2L 3 如 果E D电 流 主 要 流 入 电 源 去 耦 电 容 , . S

应用 电路 。 了正确保 护I 需要 考虑以下 内 施加到 I 为 c, c的电压 由固定电荷量决定 :

容: ・ I 成 E D 的 传 递 模 式 对 C造 S ・C 内 部 的 E D保 护 电路 I S Q =C × V 和 Q i= Fa Ql n l i d

IS ED=2 V/ . k k 1 . 5Q

被 保 护 引脚 电 容上 的 能 量 如 图 4 示 , 所 对

E

卫

U

个 00 B 去 耦 电容 ,2 V H M 测 试 电 压 可 以 .1 F k B

如 果 对 I 进 行 达 到 2 V。 C 0

HB 测 试 , 试 电路 M 测

TmeI) i s

VI VEDX C0( 0 C1或 2 V= k = s /C + ) 0 2 V X

1 0 F (0 p t00I. 0 p /1 0 F- . J - l F)

图 3 钳位操 作( 测量数据)

l Vola c t ge d an Ener gyf kV ora 2 HBM Tes t

的初始 电压 是 2 V, k

E D电 流 约 为 l 3 S - A: 3

储 存 在 金 属 物 体 , 器 模 式 中 的 放 电 只 受 内 部 机

连接 电感的限制 。

双极性集成电路的 E D保护 S

E D P o e t n f r ioa t g a e i ut S r t c i o p lr n e r t d C r i o B I c s

ESD引起集成电路损坏原理模式及实例

ESD引起集成电路损坏原理模式及实例一.ESD引起集成电路损伤的三种途径(1)人体活动引起的摩擦起电是重要的静电来源,带静电的操作者与器件接触并通过器件放电。

(2)器件与用绝缘材料制作的包装袋、传递盒和传送带等摩擦,使器件本身带静电,它与人体或地接触时发生的静电放电。

(3)当器件处在很强的静电场中时,因静电感应在器件内部的芯片上将感应出很高的电位差,从而引起芯片内部薄氧化层的击穿。

或者某一管脚与地相碰也会发生静电放电。

根据上述三种ESD的损伤途径,建立了三种 ESD损伤模型:人体带电模型、器件带电模型和场感应模型。

其中人体模型是主要的。

二.ESD损伤的失效模式(1)双极型数字电路a.输入端漏电流增加b.参数退化c.失去功能,其中对带有肖特基管的STTL和LSTTL电路更为敏感。

(2)双极型线性电路a.输入失调电压增大b.输入失调电流增大c.MOS电容(补偿电容)漏电或短路d.失去功能(3)MOS集成电路a.输入端漏电流增大b.输出端漏电流增大c.静态功耗电流增大d.失去功能(4)双极型单稳电路和振荡器电路a.单稳电路的单稳时间发生变化b.振荡器的振荡频率发生变化c.R.C连接端对地出现反向漏电。

三.ESD对集成电路的损坏形式a.MOS电路输入端保护电路的二极管出现反向漏电流增大b.输入端MOS管发生栅穿c.MOS电路输入保护电路中的保护电阻或接触孔发生烧毁d.引起ROM电路或PAL电路中的熔断丝熔断e.集成电路内部的MOS电容器发生栅穿f.运算放大器输入端(对管)小电流放大系数减小g.集成电路内部的精密电阻的阻值发生漂移h.与外接端子相连的铝条被熔断i.引起多层布线间的介质击穿(例如:输入端铝条与n+、间的介质击穿)四.ESD损伤机理(1)电压型损伤a.栅氧化层击穿(MOS电路输入端、MOS电容)b.气体电弧放电引起的损坏(芯片上键合根部、金属化条的最窄间距处、声表面波器件的梳状电极条间)c.输入端多晶硅电阻与铝金属化条间的介质击穿d.输入/输出端n+扩区与铝金属化条间的介质击穿。

集成电路中esd失效机理分析

静电放电是一个复杂多变的随机过程,同时静电放电有许多不同的放电形式,产生静电放电的静电源多种多样,而且同一静电源对不同的物体放电时产生的结果也不一样,会受气候、环境等条件的影响,不利于得到具有重复性的放电结果,难以有效地对ESD的效应和危害进行止确的评估。但是根据不同场合静电放电的主要特点可以建立相应的静电放电模型,模拟静电放电的主要特征。

基于ESD产生的原因及其对集成电路放电的不同方式,通常将静电放电事件分为以下几类模型:人体模型(HBM)、机器模型(MM)、带电器件模型(CDM)、传输线脉冲模型(TLPM)等。

(1)人体模型(Human Body Mode--HBM)

当带有静电的人体或其他物体与IC管脚接触,储存于人体之中的电荷将转移到IC上,使其带电,或通过IC对地放电,这种ESD用人体放电模型来描述。该放电过程会在几百ns时间内产生数安培的瞬间放电电流,将IC内的器件烧毁。

静电是一种电能,它存在于物体表面,是正负电荷在局部失衡时产生的一种现象。静电现象是指电荷在产生与消失过程中所表现出的现象的总称,如摩擦起电就是一种静电现象。静电产生原因放电危害

由于物体间的接触分离(如摩擦、剥离、撕裂和搬运中的碰撞等)或电场感应,都会因物体之间或物体内部带电粒子的扩散、转移或迁移而形成物体表面电荷的积聚,即呈现带电现象。这种现象的存在,有可能导致物体表面电荷对空气中带异性电荷的微粒子尘埃的吸引造成电子敏感元器件绝缘性能的降低、结构腐蚀或破坏。当外界条件适宜时,这种积聚电荷还会产生静电放电,使元器件局部破损或击穿,严重时,还会引起火灾、爆炸等。曾报道某厂在修理程控交换机上的半导体集成电路时因静电引起爆炸事故的文章[1]。应当指出,静电引起电子元器件局部结构破损和性能降低,是对元器件使用寿命的一种潜在威胁,因为它难于检验,故造成事故的随机性更大,并且易于与其他失效原因混淆而被掩盖。

CMOS集成电路ESD保护技术研究

CMOS集成电路ESD保护技术研究董培培;张海涛【摘要】介绍了 ESD 保护原理、测试方法及典型的 ESD 保护电路,针对2000V 的 HBM模型ESD 保护指标要求,采用 CSMC 0.5μm 25V(VGS)/25V (VDS)DPTM工艺模型和 GGMOS 器件进行了全芯片的 ESD 保护电路设计,并对 ESD 保护管的输出驱动级做了探索,在保证输出级 ESD 保护能力的同时,提高了输出端口的带负载能力。

鉴于 ESD 保护结构工艺移植性较差,保护性能与工艺密切相关的特点,结合具体版图设计实践,总结了 ESD 保护结构版图设计的通用原则。

这些原则旨在提高 ESD 保护结构的抗静电能力或提高 ESD 保护器件的工作可靠性,与具体的实现工艺无关。

流片后的 ESD 实验表明,设计的 ESD 保护结构可以承受2000V HBMESD 攻击。

%The principles,measurement methods and typical circuits of ESD Protection are introduced in this ing CSMC 0.5μm 25V(VGS)/25V(VDS)DPTMProcess and GGMOS devices,the ESD protection circuits of the whole chip are designed to achieve 2000V HBMESD protection ability,and output driver designed with ESD protection FETs is explored to raise the driving ability of output pin while keeping the ESD protection ability.Because technology portability of ESD protection circuits is bad and ESD protection ability is highly related with technology,combined with layout design practice,the general principles of ESD layout design are presented.The principles,regardless of technology,aim at raising the protection ability or reliability of ESD protection structure.The ESD experiment of the fabricated chip shows that the designed ESD protection structure can endure 2000V HBMESD attack.【期刊名称】《微处理机》【年(卷),期】2016(037)005【总页数】4页(P9-12)【关键词】ESD保护;GGMOS 器件;电路设计;版图设计;通用原则;工作可靠性【作者】董培培;张海涛【作者单位】中国电子科技集团公司第四十七研究所,沈阳 110032;中国人民解放军 95979 部队,辽宁,沈阳 110045【正文语种】中文【中图分类】TN4随着电路设计和制造工艺水平的发展,CMOS集成电路工艺尺寸不断缩小,单芯片集成度不断变大,且电路结构越来越复杂,极大提高了集成电路的性价比。

集成电路的ESD防护技术分析

集成电路的ESD防护技术分析集成电路是现代电子技术的核心之一,它广泛应用于计算机、通讯、嵌入式系统等各个领域。

但是,在电路设计和使用过程中,静电放电(ESD)问题一直是个头痛的难题。

ESD会对集成电路造成不可恢复的损坏或缺陷,严重影响电路的可靠性和寿命。

因此,如何对集成电路进行ESD防护技术实现是一个很重要的问题。

ESD的来源很广泛,主要有三种:(1)人体静电;(2)设备间的静电;(3)环境中的静电。

因此,在集成电路设计中,需要考虑如何避免这些ESD的来源,同时加强防护策略。

现在,有很多的技术手段来解决这个问题,主要包括以下几种:1.背部引线设计:通过机械连接背部引线(SolderBall),将ESD引导至地面,以达到防护的目的。

这种设计简单、容易实现,但是会增加颗粒物,影响封装的可靠性。

2.内置防护电路设计:在集成电路内部,设计一定的电路来吸收和放电ESD,避免对引脚的损害。

这种设计简单、成本低,但是无法完全消除ESD影响。

3.局部工艺优化设计:通过局部的工艺优化措施,如在特定的地方采用金属层的补偿等方法,降低这些地方的ESD破坏风险。

这种设计可以较大程度上降低ESD损伤的风险,但需要根据具体情况进行工艺调整。

4.外置防护电路设计:在集成电路外部设计一定的防护电路,以吸收和放电ESD。

这种设计可以较好地保护集成电路,但是其成本较高,且需要考虑与已有设计的兼容性。

总之,ESD防护技术的应用非常广泛,需要根据具体情况来选择最合适的方案。

通过综合应用上述防护措施,可以有效消除或降低ESD的危害,从而提高集成电路的可靠性和稳定性。

esd保护概念

esd保护概念

ESD (Electrostatic Discharge) 保护是一种电子设备中使用的技术措施,旨在保护电子元件免受静电放电的损害。

静电放电是由于静电累积而引起的突然放电,可以对电子设备和元件造成损坏。

ESD保护的目标是通过减少静电放电对电子元件的影响,提高设备的可靠性和稳定性。

ESD保护有多种形式,包括:

1. 设备级ESD保护:通过在设备的输入和输出端口添加静电保护器件,限制静电放电进入设备。

2. PCB级ESD保护:通过在PCB上使用防静电涂层、添加静电保护器件和合理布局电路,限制静电放电对PCB和其中的元件的影响。

3. 元件级ESD保护:通过在电子元件上添加ESD保护器件,限制静电放电对元件本身的影响。

ESD保护器件通常是一种可以吸收和分散静电放电能量的电路元件。

常见的ESD保护器件包括二极管、MOSFET和保险丝等。

这些器件在正常工作时具有很高的电阻,以阻止静电放电通过,但在静电放电事件发生时能够迅速分散和吸收静电能量,从而保护后续电路和元件。

ESD保护在电子工业中非常重要,特别是对于静电敏感设备和元件,如集成电路、传感器和显示器等。

正确的ESD保护可以显著提高设备的可靠性和寿命,并确保其在恶劣的静电环境下正常工作。

集成电路ESD防护浅析

集成电路ESD防护浅析摘要:集成电路在我们日常生活中扮演着越来越重要的角色,而电子设备的工作环境是一个非常复杂的系统,在这个系统中,静电和电磁干扰是非常常见的问题。

当电子设备被这些问题困扰时,静电放电(ESD)会导致电子设备发生故障甚至损坏。

在许多情况下,静电放电对集成电路产生干扰,如信号完整性问题和逻辑电路错误。

为了防止这些问题对电路造成严重损害,有必要了解ESD的基本原理并掌握,同时做好防护措施。

本文将从静电放电的基本原理和基本防护措施两个方面入手,详细介绍集成电路ESD防护措施。

关键词:集成电路;ESD;防护对策静电是一种自然现象,产生静电的方式多种多样,例如:接触、摩擦、电气设备间的电感应等;例如人体因身体自身的移动、与其他物质的接触、脱离、摩擦力、感生等因素也会产生静电,静电量可达数千至数万伏特;例如在两个电极间,当电极与电极间存在着电势差异时,电极与电极间就会发生电荷输运,直到电极与电极间的电压达到平衡为止。

由于静电放电(ElectroStaticDischarge,ESD)对集成电路的影响越来越严重,为保证集成电路的可靠性和稳定性,必须对其进行ESD防护。

1.ESD的产生静电放电(ElectroStaticDischarge,ESD)是指由于物体表面静电的存在,而产生的电荷累积现象。

当物体表面存在电荷时,由于电场的作用,其附近的电子会受到强大电场的作用而发生位移。

这种位移就称为静电场位移。

当静电力超过了材料所能承受的最大临界值时,就会在材料内部或表面产生电荷积累而导致材料失效,或者产生对其他设备的干扰。

ESD是由静电放电引起的现象,静电放电时由于表面上出现了电荷累积而导致静电场位移。

ESD放电时有两种形式:一种是空间电荷,一种是表面电荷,其中空间电荷产生的原因是在两个物体之间存在着很小的空间距离(空气间隔),由于空气中存在着大量的自由电子和负离子,使得空气中的空间电荷数量很大,而这种静电电荷可以通过静电感应和静电放电两种方式来产生,静电感应主要是因为当两个物体之间存在着很小的距离时,由于空间电荷量较大,当有一个物体带负电时,其周围就会形成一个强大地电场,这种电场是一种不均匀介质中产生的电磁场,这种电磁场与空间电场相互作用,从而产生了电流,这种电流有很强的穿透力,可以穿透两个物体之间很小距离(空气间隔)而不受阻挡。

cmos 电路 esd泄放原理

CMOS电路是当今集成电路中最常见的一种电路类型,而ESD (Electrostatic Discharge,静电放电)则是一个不可忽视的问题。

在CMOS电路中,ESD对电路的损坏可能会导致严重影响甚至可能造成整个系统的失效。

了解CMOS电路中的ESD泄放原理对于电路设计和集成电路的稳定性至关重要。

一、CMOS电路简介1. CMOS电路特点CMOS电路是一种使用互补型金属氧化物半导体(Complementary Metal-Oxide-Semiconductor,简称CMOS)技术制作的集成电路。

CMOS电路具有低功耗、高噪声抑制、集成度高等优点,因此被广泛应用于数字集成电路、微处理器、存储器等领域。

2. CMOS电路结构CMOS电路由P型金属氧化物半导体(P-MOS)和N型金属氧化物半导体(N-MOS)两种类型的MOSFET器件组成。

它利用P-MOS和N-MOS的互补特性,实现高密度和低功耗。

二、ESD泄放原理1. ESD的危害ESD是指人体或物体在静电充电后,与另一对象或地面突然放电的现象。

在现代集成电路中,ESD是造成电路损坏和性能降低的主要原因之一。

当ESD发生时,电流冲击会对CMOS电路中的敏感元件产生破坏性影响。

2. ESD泄放原理ESD泄放是指在CMOS电路中设计专门的保护电路,以接受和限制ESD脉冲,从而保护电路不受损坏。

它通过引入ESD元件并将其连接到电源和地,以吸收来自ESD事件的能量,从而降低ESD对电路的损害。

三、CMOS电路中的ESD保护技术1. ESD保护器件在CMOS电路中,常用的ESD保护器件包括二极管、二极管堆、金属氧化物半导体场效应晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor,简称MOSFET)等。

这些保护器件能够有效限制ESD脉冲的能量,保护主要电路不受损坏。

2. ESD保护电路设计原则在设计CMOS电路的ESD保护电路时,需要考虑ESD脉冲的能量、速度以及保护电路的响应时间等因素。

谈谈集成电路ESD保护的器件和电路

谈谈集成电路ESD保护的器件和电路各位群友,大家晚上好,我是黄晓宗,一直从事模拟和混合信号IC设计工作,对ESD保护设计有一定的心得,今天和大家谈谈集成电路ESD保护的器件和电路,在交流的过程中会分享一些实际的案例,希望能够为大家做一些基础知识的铺垫,也感谢大家在这里进行交流。

我将分为以下部分介绍,在完成背景介绍后,将在第二、三和四章针对基本器件、二极管、SCR器件提高维持电压的技术进行讨论。

然后,通过工程案例和器件应用,分析和优化全芯片ESD保护设计;第五章将讨论SiP ESD中板级和片上协同保护的策略,提高系统的保护能力。

静电放电现象在日常生活中非常常见,干燥的冬天手指触碰到金属门把手,就会发生放电现象。

不同物体的接触和分离就是最常见的静电产生方式,例如摩擦可产生静电。

人体有感觉的静电放电电压在3000—5000V,这些静电对人体并不是致命的,但是对没有静电防护的电子产品来说可能会造成非常严重的后果。

电子产品离不开芯片,也就离不开ESD保护设计。

以我们的手机为例,移动电话转向智能电话技术,智能手机按键被触摸技术替代,取消了按键接口,人机交互通过触摸屏完成。

虽然目前的智能手机仍有耳机、电源充电、电源按键等端口外露,但是已经大大减少。

对于未来发展,当“非接触技术”(类似手势控制)替代目前的“接触技术”,那么直接的人机交互将减少静电损伤的风险。

芯片在生产、封装、测试、组装等过程中都受到ESD的威胁,所以保护设计也就贯穿整个芯片的始终。

这是典型的ESD失效照片。

一般来讲,一颗芯片上都会有相应的ESD保护电路,其目标就是泄放电流和钳位电压,保护脆弱的内部电路。

当然,RF电路为了性能的考虑,可能无ESD保护结构,其静电能力就可能200V-250V。

集成电路的ESD防护关键技术

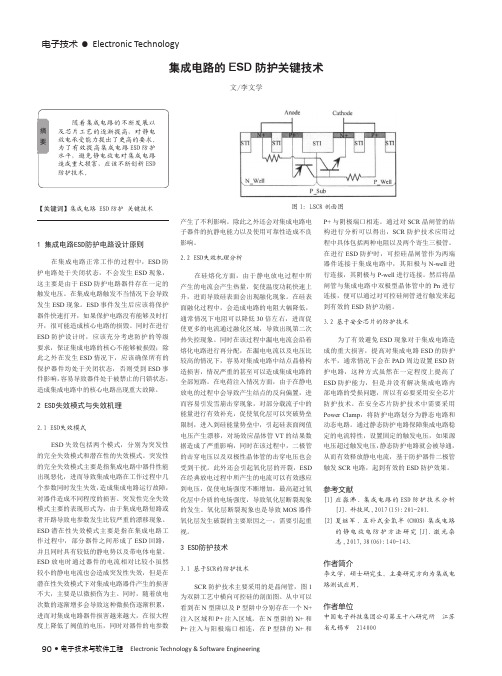

电子技术• Electronic Technology90 •电子技术与软件工程 Electronic Technology & Software Engineering【关键词】集成电路 ESD 防护 关键技术1 集成电路ESD防护电路设计原则在集成电路正常工作的过程中,ESD 防护电路处于关闭状态,不会发生ESD 现象,这主要是由于ESD 防护电路器件存在一定的触发电压。

在集成电路触发不当情况下会导致发生ESD 现象。

ESD 事件发生后应该将保护器件快速打开,如果保护电路没有能够及时打开,很可能造成核心电路的损毁。

同时在进行ESD 防护设计时,应该充分考虑防护的等级要求,保证集成电路的核心不能够被损毁;除此之外在发生ESD 情况下,应该确保所有的保护器件均处于关闭状态,否则受到ESD 事件影响,容易导致器件处于被禁止的闩锁状态,造成集成电路中的核心电路出现重大故障。

2 ESD失效模式与失效机理2.1 ESD失效模式ESD 失效包括两个模式,分别为突发性的完全失效模式和潜在性的失效模式。

突发性的完全失效模式主要是指集成电路中器件性能出现恶化,进而导致集成电路在工作过程中几个参数同时发生失效,造成集成电路运行故障,对器件造成不同程度的损害。

突发性完全失效模式主要的表现形式为,由于集成电路短路或者开路导致电参数发生比较严重的漂移现象。

ESD 潜在性失效模式主要是指在集成电路工作过程中,部分器件之间形成了ESD 回路,并且同时具有较低的静电势以及带电体电量。

ESD 放电时通过器件的电流相对比较小虽然较小的静电电流也会造成突发性失效,但是在潜在性失效模式下对集成电路器件产生的损害不大,主要是以微损伤为主。

同时,随着放电次数的逐渐增多会导致这种微损伤逐渐积累,进而对集成电路器件损害越来越大,在很大程度上降低了阀值的电压,同时对器件的电参数集成电路的ESD 防护关键技术文/李文学产生了不利影响。

除此之外还会对集成电路电子器件的抗静电能力以及使用可靠性造成不良影响。

电路中的ESD保护

❖电路中的ESD保护ESD的意思是“静电释放".集成电路器件工作在一定的电压、电流和功耗限定范围内,大量聚集的静电荷在条件适宜是就会产生高压放电,静电放电通过器件引线的高压瞬时传送,可能会使氧化层断开,造成器件的功能失常。

静电的产生主要包括:摩擦起电、感应起电和接触起电。

ESD保护器件的原理,ESD保护二极管是一种新型的集成化的静电保护器件,其内部相当于是一个齐纳稳压二极管,当输入电流超过它的额定电压时,就会被击穿,把过多的电能量导回大地,以起到保护电路的作用。

ESD保护器件一般接在外部接口处,防止外部产生的静电对电路内部造成影响。

ESD器件的主要性能参数1、最大工作电压,即是允许长时间连续施加在保护器件两端的电压,在此工作状态下,ESD保护器件不导通,保持高祖状态。

2、击穿电压,即是ESD器件开始工作时的导通电压。

3、钳位电压,即是ESD器件流过峰值电流时,其两端呈现的电压,超过此电压,可能造成ESD器件的永久性损伤.4、漏电流,在指定的直流电压下,通过ESD器件的电流,一般是nA级的,此电流越小,对被保护电路的影响越小。

5、电容,在给定电压、频率条件下测得的值,此值越小,对被保护的信号传输影响就越小。

6、响应时间,指ESD器件对输入电压钳制到预定电压的时间。

ESD保护器件TVS管即瞬态抑制二极管是一种二极管形式的高效保护器件,利用P-N结的反向击穿工作原理,将静电高压导入大地,从而保护了电器内部对静电敏感的器件.当TVS二极管的瞬时电压超过电路正常工作电压时,TVS二极管便发生雪崩,提供给瞬时电流一个超低电阻通路,其结果就是瞬时电流通过二极管被引开,避开可被保护器件,并且在电路恢复正常值之前使被保护回路一直处于截止状态,当瞬时脉冲结束以后,TVS二极管自动回复高阻状态,整个回路进入正常电压. TVS二极管的工作特性曲线如下图所示TVS管的选型(1)、TVS的最大反向钳位电压应小于被保护电路的损坏电压。

集成电路的ESD保护设计考核试卷

B.保护器件应具有快速响应特性

C.保护器件的响应时间应尽量慢

D.保护器件应具有足够的承受能力

5.以下哪种情况下,集成电路容易受到ESD的影响?()

A.高湿度环境

B.低湿度环境

C.低温环境

D.高温环境

6.在ESD保护电路设计中,常用的箝位电压是多少?()

A. 5V

B. 10V

11. ABC

12. AD

13. AC

14. ABCD

15. ABCD

16. ABCD

17. ABC

18. ABC

19. AD

20. ABCD

三、填空题

1.静电放电

2.电压

3. 1000

4.位置

5.电源

6.高压、快速响应

7.响应时间

8.插入损耗

9.箝位电压

10.地线

四、判断题

1. ×

2. √

3. ×

集成电路的ESD保护设计考核试卷

考生姓名:__________答题日期:__________得分:__________判卷人:__________

一、单项选择题(本题共20小题,每小题1分,共20分,在每小题给出的四个选项中,只有一项是符合题目要求的)

1.集成电路中ESD保护的作用是什么?()

A.提高电路的工作速度

4. ESD保护设计时,保护器件的__________应尽量靠近被保护电路。()

5.陶瓷电容通常不用于__________保护。()

6.碳化硅材料制成的ESD保护器件具有__________和__________的特点。()

7.在ESD保护电路中,__________是衡量保护器件响应速度的一个重要参数。()

谈谈集成电路ESD保护的器件和电路

谈谈集成电路ESD保护的器件和电路展开全文各位群友,大家晚上好,我是黄晓宗,一直从事模拟和混合信号IC设计工作,对ESD保护设计有一定的心得,今天和大家谈谈集成电路ESD保护的器件和电路,在交流的过程中会分享一些实际的案例,希望能够为大家做一些基础知识的铺垫,也感谢大家在这里进行交流。

我将分为以下部分介绍,在完成背景介绍后,将在第二、三和四章针对基本器件、二极管、SCR器件提高维持电压的技术进行讨论。

然后,通过工程案例和器件应用,分析和优化全芯片ESD保护设计;第五章将讨论SiP ESD中板级和片上协同保护的策略,提高系统的保护能力。

静电放电现象在日常生活中非常常见,干燥的冬天手指触碰到金属门把手,就会发生放电现象。

不同物体的接触和分离就是最常见的静电产生方式,例如摩擦可产生静电。

人体有感觉的静电放电电压在3000—5000V,这些静电对人体并不是致命的,但是对没有静电防护的电子产品来说可能会造成非常严重的后果。

电子产品离不开芯片,也就离不开ESD保护设计。

以我们的手机为例,移动电话转向智能电话技术,智能手机按键被触摸技术替代,取消了按键接口,人机交互通过触摸屏完成。

虽然目前的智能手机仍有耳机、电源充电、电源按键等端口外露,但是已经大大减少。

对于未来发展,当“非接触技术”(类似手势控制)替代目前的“接触技术”,那么直接的人机交互将减少静电损伤的风险。

芯片在生产、封装、测试、组装等过程中都受到ESD的威胁,所以保护设计也就贯穿整个芯片的始终。

这是典型的ESD失效照片。

一般来讲,一颗芯片上都会有相应的ESD保护电路,其目标就是泄放电流和钳位电压,保护脆弱的内部电路。

当然,RF电路为了性能的考虑,可能无ESD保护结构,其静电能力就可能200V-250V。

ESD对IC的损伤主要有两类,即大电流产生局部热量、高电场损伤绝缘层,都会导致电路或者器件功能性能的异常。

ESD保护的基本原理就是并联保护器件,以此泄放大电流和钳位高电压,避免对内部电路造成损伤。

ESD和集成电路的ESD保护

ESD和集成电路的ESD保护Part 1、ESD的事实存在什么是ESD?ESD的全名是Electrostatics Discharge(静电放电)从物理上来讲,产生静电释放的原因有摩擦、感应、剥离,产生静电放电的机制是因为物质失去了或者得到了电子从而使本身带上正电或者负电。

从表象来看,产生静电放电是因为两个电位不相同的物体间的电荷转移现象,而且不一定要伴随着有电弧或者火花的产生。

此外,大电流(安培级)和瞬间(纳秒级)的挤压也可以引起静电的释放,此类有如压电陶瓷。

自然界中的ESD现象:雷击、冬天脱毛衣时会有啪啪的声音、在地毯上走动或者从椅子上站起来后,碰触导体(例如金属门把)。

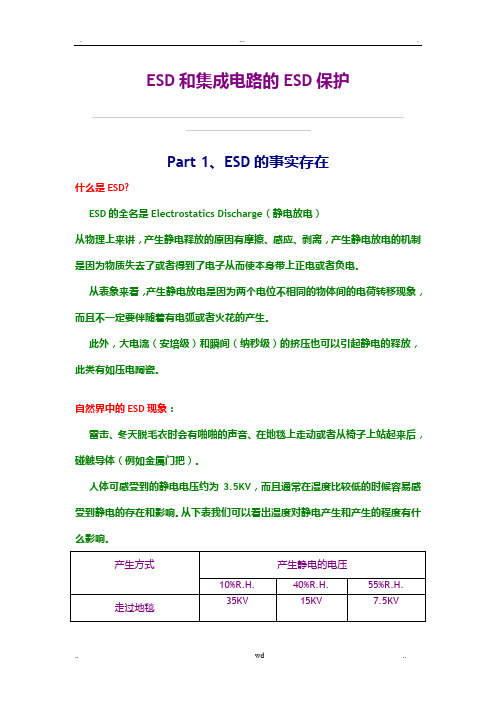

人体可感受到的静电电压约为3.5KV,而且通常在湿度比较低的时候容易感受到静电的存在和影响。

从下表我们可以看出湿度对静电产生和产生的程度有什么影响。

产生方式产生静电的电压10%R.H.40%R.H.55%R.H.走过地毯35KV15KV7.5KVPart 2、ESD对CMOS集成电路损害及测试1、引言集成电路工艺发展到深亚微米阶段,器件的物理尺寸日益减小,静电放电(Electrostatic Discharge,ESD)对集成电路的危害变得越来越显著。

因为随着关键尺寸的不断缩小,集成电路的功耗和发热也在不断地得到降低,但是也由于栅极能承受的最高电压在不断降低,所以集成电路被外界突发的ESD电压损坏的几率也在不断地提高。

据统计,将近40%的集成电路失效是由静电放电引起的。

因此,对集成电路进行ESD保护设计也变得尤为重要,因为ESD伤害来自生产、储存、运输各个方面,可谓时时有可能被伤害。

2、ESD模式及其测试方法ESD模型常见的有三种:人体模型(HBM ,Human Body Model)、充电器件模型(CDM,Charge Device Model)和机器模型(MM,Machine Mode),其中以人体模型最为通行。

一般的商用芯片,要求能够通过2KV静电电压的HBM检测。

esd保护器件原理

esd保护器件原理

esd保护器件是一种针对静电放电(ESD)现象设计的电子器件,主要用于保护集成电路和其他电子设备免遭静电破坏。

esd保护器件的原理基于静电放电的本质,它使用了一个或多个保护结构来限制静电放电过程中的电压和电流,从而确保被保护的器件不会受到损坏。

esd保护器件的保护结构通常包括二极管、MOSFET、TVS(穿孔瞬变压力抑制器)等组件,这些组件可以快速反应并吸收静电放电,从而保护被保护器件不受静电破坏。

除了保护结构,esd保护器件还需要考虑其它因素,如峰值电压、响应时间、ESD容忍度等等。

这些因素的综合考虑可以帮助设计出更加可靠的esd保护器件。

- 1 -。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路的ESD保护

概述

静电放电(ESD)会对集成电路(IC)造成破坏性的能量冲击,良好的IC设计能够在IC 装配到应用电路的过程中保护IC免遭ESD冲击的破坏。

安装后,IC还必须能够承受ESD穿过静电防护电路进入最终电路的冲击。

除此之外,机械防护、电源去耦电容都有助于提高ESD保护能力,但是,如果电容选择不当将会造成IC更容易损坏。

为了给IC提供合理的ESD保护,需要考虑以下内容。

•冲击IC的ESD传递模式

•内部ESD保护

•应用电路与IC内部ESD保护的相互配合

•修改应用电路提高IC的ESD保护能力

ESD传递模式

静电放电强度以电压形式表示,该电压由电容的储能电荷产生,最终传递到IC。

作用到IC的电压和电流强度与IC和ESD源之间的阻抗有关。

对电荷来源进行评估后建立了ESD测试模型。

ESD测试中一般使用两种充电模式(图1),人体模式(HBM)下将电荷储存在人体内(100pF等效电容),通过人体皮肤放电(1.5kΩ等效电阻)。

机器模式(MM)下将电荷储存在金属物体,机器模式中的放电只受内部连接电感的限制。

图1. ESD测试模型

以下概念对于评估ESD向IC的传递非常有用:

1. 电压高于标称电源电压时,IC阻抗较低。

对于图1中的HBM模式:Z

S = Z HBM = 1.5kΩ

2. 在MM模式下,电流受特征阻抗(约50Ω)的限制。

上述特征阻抗的计算可以从低阻L-C电路的能量(E)推导出来:

3. 如果ESD电流主要流入电源去耦电容,IC电压由储存的电荷量决定:

Q = C x V和Q Final = Q Initial

V1 x (C0 + C1) = V ESD x C0 (见图1)

4. 能够在瞬间导致IC损坏的能量相当于微焦级,有外部电源去耦电容时,考

虑这一点非常重要,图1中从电源电容(C1)传递到IC的能量是:

5. 耗散功率(P)会产生一定热量,假设能量经过一段较长的时间(t)释放掉,热量

将随之降低:

ESD能量传递到低阻电路时需要考虑其电流(上述第1、2条);对于高阻而言,能量以电压形式通过电荷转移传递到电源去耦电容和寄生电容(第3条)。

对IC造成损坏的典型能量是在不到一个毫秒的时间内将微焦级能量释放到IC (第4、5条)。

IC内部保护电路

标准保护方案是限制到达IC核心电路的电压和电流。

图1所示保护器件包括:•ESD二极管—在信号引脚与电源或地之间提供一个低阻通道,与极性有关。

•电源箝位—连接在电源之间,正常供电条件下不汲取电流,出现ESD冲击时呈低阻。

ESD二极管

如果对IC引脚进行HBM测试,测试电路的初始电压是2kV,通过ESD二极管的电流约为1.33A (图2):

图2. ESD二极管的电流和电压(测量数据)

理论上,进行HBM测试时引脚电压受限于二极管压降。

大电流会在ESD二极管和引线上产生I-R压降,在信号引脚产生额外的电压,如图2所示。

为了确定IC是否能够承受2kV的ESD冲击,需要参考厂商提供的资料。

IC的额定电压由最大电压决定,图1中的V

ESD,这是IC能够承受的一种特定的ESD源。

Maxim IC所能承受的ESD指标在可靠性报告中可以查找到。

电源箝位

双极型IC的箝位电路类似于在受保护核电路中提供一个受冲击时击穿的部件,图3给出了图1中箝位功能的详细电路。

箝位晶体管的过压导致集电极-基极之间的雪崩电流,发射结的正向偏置会进一步提高集电极电流,导致一个“突变”过程。

箝位时的V-I特性曲线如图4所示。

图3. 图1中的箝位电路

图4. V-I箝位特性

箝位二极管在IC其它电路遭到破坏之前导通,箝位管要有足够的承受力,保证ESD 电流不会导致二次击穿。

2kV HBM测试的箝位过程如图5所示,图5中的电压包括I-R压降和突变稳定后的箝位电压。

图5. 箝位工作过程(测量数据)

ESD保护与应用电路

箝位电压从第一次击穿变化到突变稳定后的导通电压,如图5所示。

为保证箝位时关闭正常的工作条件,设计的箝位电压一般要略高于IC的绝对最大电压。

电源去耦电容会影响箝位操作,传递到去耦电容的电荷会产生高于IC绝对最大值的电压,但还不足以使箝位电路导通。

这时的电容相当于一个能源,迅速向器件注入能量。

对于一个给定的去耦电容,ESD测试中初始电压的变化遵循电荷守恒原理。

例如,

使用一个0.01µF去耦电容,2kV HBM测试电压可以达到20V:

或

图6. 能量和电压与电源耦合电容的关系

被保护引脚电容上的能量如图6所示,对小的去耦电容,箝位二极管通过进入突变稳定模式限制电压(V1)。

突变稳定后的电压所产生的能量近似地随着电容的增大而成比例增大。

电源去耦电容增大到一定程度后,电荷传输不会产生导致箝位电路击穿的电压。

箝位电压高于IC所能承受的电压(典型值6V),低于二极管的击穿电压(约10V)时,对于存在去耦电容的情况,因为电容储能可能导致某些问题。

如果IC在没有外部电路的情况下进行测试,引脚上作用10V电压是可以接受的,对器件不会构成威胁。

改善ESD保护

合理选择去耦电容的大小有助于在电路中提高IC的保护,降低电容储能,使ESD 电荷不会产生击穿箝位电路的电压。

我们可以考虑图1中C1>>C0的情况:

最初:

将C1加倍,则会导致:

电容加倍,能量降低一倍。

对于小尺寸高速双极型IC,HBM测试中吸收的最大能量是1µJ;2kV人体模式下,如果电容小于0.02µF (图6),箝位二极管会产生动作。

为了使去耦电容的能量低于1µJ,去耦电容有两种选择:要么容值大于0.05µF,要么小于0.005µF。

当使用更高的测试电压时,要按比例增大0.05µF电容的尺寸。

实际应用中,通常不允许使用更大的去耦电容。

浪涌电流的要求会限制电容尺寸。

如果不控制电压摆率,唯一限制浪涌电流的途径就是限制去耦电容的尺寸:

去耦电容与电源间的引线总是存在一定量的电感,通常也会接入一个滤波电感。

这种配置下,最大浪涌电流取决于滤波电感与去耦电容的特征阻抗,这个阻抗(图7中的Zo)类似于MM测试中的电流限制。

图7. C1较大时的电源阻抗

通过限制浪涌电流,可以使用较大的滤波电容(C1);发生ESD冲击时,使得作用在IC上的电压低于器件允许的最大额定电压。

改善ESD保护的有效途径有:

•使用更大的滤波电容,使最大ESD电压低于IC引脚所能承受的绝对最大电压。

•使用小的滤波电容,使得箝位二极管在低能量时提供保护。

•增大串联电感限制大电容产生的浪涌电流。

•增加外部箝位二极管,如图8所示的齐纳二极管,使ESD电压低于器件所能承受的绝对最大电压(图9)。

图8. 齐纳ESD保护二极管

图9. 利用齐纳保护二极管改善箝位(测量数据)

结论

IC及其周边元件需要承受突破应用电路镜电防护层的ESD能量,电源的去耦电容可能是降低作用到IC上的ESD强度的一条低成本解决途径,诸多设计因素会影响ESD性能,具体可以归纳为:

1. 确定应用场合的测试电压(V ESD),典型值为2kV的HBM或100V MM模式。

2. 检查IC的可靠性报告,确认二极管、钳位二极管和传导路径适合的测试电

压。

Maxim的可靠性报告中提供了IC的相关信息。

3. 当使用外部电容,如电源滤波电容(C1)时,需检查其产生的电压,这个电压

最终作用到IC上。

4. 如果出现ESD冲击时,电压介于IC的最大额定电压(典型值为6V)与击穿电

压(典型值在8V至10V),可以考虑使用较大尺寸的电容来替代电源滤波的方案。