利用Snuer电路消除开关电源和ClassD功放电路中的振铃

电源噪声干扰情况原因分析及消噪方法解决

图 3 组合滤波器电路 根据要求插入损耗,可求出滤波电路的LCM、LDM、Cx、Cy 的值。如果 单环电路的插入损耗不能满足要求时,应该选择双环电路。 4.2.3 交流三相滤波电路 交流三相滤波电路又分为三相三线制和三相四线制两种。 典型的单环三相三线制滤波电路如图4所示;典型的双环三相三线制滤波电路 如图5所示。

图8直流滤波电路 显然,这是一个共模扼流圈的典型单环滤波电路。根据电路特点,它只适用于 直流输出端对地对称的电源电路。 如果直流输出是非对地对称电路,则只能采用图9所示的电路。该电路为采用 二级差模电感电路。如果插入损耗允许,当然也可采用一级差模电感电路。

图9二级 π 型滤波器 4.2 AC 电网常用 EMI 滤波器 4.2.1 差模滤波电路 由于开关电源的开关频率谐波噪声源阻抗为低阻抗,所以与之相对应的滤波器 输出端应是高阻抗串联大电感LDM。 AC电网火线和零线之间是低阻抗,所以与之对应的滤波器输入端也应是高阻 抗串联大电感LDM。如果想再进一步抑制差模噪声,可以在滤波器输入端并 接线间电容CX1,条件是它的阻抗要比AC电网火线、零线之间的阻抗还要 低得多。 开关电源工频谐波噪声源阻抗是高阻抗,所以与之相对应的滤波器输出端应是 低阻抗并联大电容CX2。

可以从持续期很短的尖峰干扰到完全失电之间进行变化。其中也包括电压变化、 频率变化、波形失真、持续噪声或杂波以及瞬变等,电源干扰的类型如下表所 示。[/B] 表 1-1 开关电源外部干扰类型表 序号 干扰类型 典型的起因 1 跌落 雷击;重载接通;电网电压低下 2 失电 恶劣的气候;变压器故障;其他原因的故障 3 频率偏移 发电机不稳定;区域性电网故障 4 电气噪声 雷达;无线电讯号;电力公司和工业设备的飞弧;转换器和逆变器 5 浪涌 突然减轻负载;变压器的抽头不恰当 6 谐波失真 整流;开关负载;开关型电源;调速驱动 7 瞬变 雷击;电源线负载设备切换;功率因素补偿电容切换;空载电动机的断开 在表 1-1 中的几种干扰中,能够通过电源进行传输并造成设备的破坏或影响其工 作的主要是电快速瞬变脉冲群和浪涌冲击波,而静电放电等干扰只要电源设备 本身不产生停振、输出电压跌落等现象,就不会造成因电源引起的对用电设备 的影响。[/B] 三.抑制干扰的一些措施抑制电磁干扰应该从骚扰源、传播途径和受扰设备人手。 首先应该抑制骚扰源,直接消除干扰原因;其次是消除骚扰源和受扰设备之间 的耦合和辐射,切断电磁干扰的传播途径;第三是提高受扰设备的抗扰能力, 减低其对噪声的敏感度。常用的方法是屏蔽、接地和滤波。 3.1 屏蔽采用屏蔽技术可以有效地抑制开关电源的电磁辐射干扰,即用电导率良 好的材料对电场进行屏蔽,用磁导率高的材料对磁场进行屏蔽。 3.2 接地所谓接地,就是在两点间建立传导通路,以便将电子设备或元器件连接 到某些叫作“地” 的参考点上。接地是开关电源设备抑制电磁干扰的重要方法, 电源某些部分与大地相连可以起到抑制干扰的作用。在电路系统设计中应遵循 “一点接地”的原则,如果形成多点接地,会出现闭合的接地环路,当磁力线穿过 该环路时将产生磁感应噪声。实际上很难实现“一点接地”,因此,为降低接地阻 抗,消除分布电容的影响而采取平面式或多点接地,利用一个导电平面作为参

如何排除电子电路中的噪音干扰

如何排除电子电路中的噪音干扰电子电路中的噪音干扰是一个常见的问题,它可能会导致信号失真、误读和设备故障等一系列严重后果。

因此,排除电子电路中的噪音干扰对于保证电路的正常运行和准确性具有重要意义。

本文将介绍一些常见的方法和技巧,帮助读者有效地解决这一问题。

I. 分辨噪音的类型首先,我们需要了解电子电路中噪音的类型。

根据噪音产生的原因,可以将其分为下面几类:1. 热噪音:由于电子元件内部的热运动引起的不可预测的电压或电流变化;2. 电源噪音:由电源本身引入电路的杂散信号,其频率通常在几十赫兹到几百千赫兹之间;3. 互耦噪音:由于不同电子元件之间的相互作用产生的噪音,通常是由于电磁场或电磁波的相互干扰引起;4. 传导噪音:来自外部电源或其他电子设备通过导线传输到电路中的噪音。

II. 减少热噪音的方法热噪音是由于电子元件内部的热运动引起的,因此减少热噪音的方法主要是降低电子元件的温度。

具体措施包括:1. 安装散热器:对于容易产生热噪音的元件,如功率放大器和稳压器等,安装散热器有助于散热,减少热噪音的产生;2. 优化电路布局:合理地安排电路中元件的位置,避免堆叠和过于密集的布线,以提高空气流通和热量散发效果;3. 降低电流:适度降低电子元件的工作电流可以减少热噪音的产生。

III. 消除电源噪音的方法电源噪音是由电源本身引入电路的杂散信号,其频率通常在几十赫兹到几百千赫兹之间。

排除电源噪音的方法包括:1. 使用滤波器:通过在电源输入端安装电源滤波器,可以滤除电源中的高频噪音,使电源输出更加稳定;2. 充分分离电源与信号地:信号地与电源地的共地会导致电源噪音传播到信号线上,因此应尽可能分离电源与信号地,以减少噪音的传递;3. 使用稳定的电源:选择稳定性好、噪音较低的电源供电,可有效降低电源噪音的干扰。

IV. 抑制互耦噪音的方法互耦噪音主要来自于电子元件之间的相互作用,通常是由于电磁场或电磁波的相互干扰引起。

为了减少互耦噪音的干扰,我们可以采取以下措施:1. 高频滤波器:在输入和输出信号线上安装高频滤波器,以阻止高频噪音的传播;2. 使用屏蔽设备:对于容易受到外界电磁场干扰的元件,如传感器和天线等,可以使用屏蔽设备来防止噪音的干扰;3. 电磁隔离:将不同的电子元件进行电磁隔离,避免互相干扰。

开关电源“有噪音”可以这样解决

开关电源“有噪音”可以这样解决凡是做过开发工作的人员都有这样的经历,测试开关电源或在实验中有听到类似产品打高压不良的漏电声响或高压拉弧的声音不请自来:其声响或大或小,或时有时无;其韵律或深沉或刺耳,或变化无常者皆有。

音频噪声一般指开关电源自身在工作的过程中产生的,能被人耳听到频率为20-20kHz的音频信号。

电子和磁性元件的振荡频率在人耳听觉范围内时,会产生能听见的信号。

这种现象在电力变换研究初期已为人知。

以50和60Hz工频工作的变压器常常产生讨厌的交流噪声。

如果负载以音频元件调制,以恒定超声频率工作的开关功率转换器也会产生音频噪声。

低功率电平时,音频信号通常与转换器无关.但是,设计人员可能希望降低其电路的声波发射.低功率AC-DC转换器中,将50或60Hz 变压器的铁心薄片焊接在一起,能使交流噪声降至容许的水平。

高频开关转换器中的铁氧体变压器也采用了类似的技木。

过去常用高级音频工程设备来研究开关电源的声波辐射。

这种装置可以非常精确地测量绝对声压级和声谱,但人类对声音的感觉是很主观的.很难说多大的声音是能听到的,更难以确定的是在特定应用中多大的声音会被认为是难以忍受的噪声。

声波辐射与电磁辐射相似,但没有用于衡量听觉容忍度的通用基准。

因此,设计者可以依据以下方针来处理与音频噪声相关的问题,减少产品的声音辐射。

电源音频噪声的产生与抑制方法:一、变压器产生的音频噪声在大多数反激式转换器应用中,变压器是主要的音频噪声源。

试验板上第一个变压器原型产生的噪声往往令人吃惊.采用众所周知的恰当的结构技巧将基本上消除噪声而不增加额外的费用.在装配原型变压器时要注意成品性能的可重复性。

有一些机制会产生变压器噪声,每种都会产生发出声音的机械位移。

这些机制包括:相对运动—磁芯两部分间的吸引力使其移动,压迫将其分隔的介质。

撞击—如果两块磁芯的表面能接触,它们响应磁通激励而移动会使二者碰撞或刮擦。

弯曲—仅在EE或EI结构的磁芯中间腿存在的裂隙,可使磁芯各部分沿其间吸引力的方向。

振铃吸收电路 -回复

振铃吸收电路-回复什么是振铃吸收电路振铃吸收电路是一种被广泛应用于通信系统中的电路,用于解决当信号通过长距离线路传输时产生的振铃现象。

振铃是指信号在传输过程中产生的回音或回波,可能会干扰到通信的正常进行。

振铃吸收电路的主要作用是减小或消除这种回音信号,提高通信质量。

振铃吸收电路的原理振铃吸收电路的原理基于信号的传输特性,利用特定电路的设计和配置来干扰并消除信号的回音。

该电路通常由吸收器、环形电感和负载电阻组成。

吸收器是振铃吸收电路中的核心部件,它可以吸收和转化回音信号。

吸收器通过将回音信号与特定频率的噪声信号相干,使其相消。

这样一来,回音信号就被消除或降低到可接受的程度,从而减小或消除振铃现象。

环形电感是振铃吸收电路中的另一个重要组成部分。

它起到滤波器的作用,削弱回音信号的幅度,并保持原始信号的强度。

环形电感通过调节其自感值和电容值来改变频率响应。

负载电阻在振铃吸收电路中起到阻尼器的作用。

它通过限制电路中的振荡和反射效应,帮助消除振铃问题。

负载电阻的选择需要根据具体应用的需求来确定。

振铃吸收电路的设计和实现步骤设计和实现振铃吸收电路需要以下步骤:1. 确定需求:首先要明确需要解决的振铃问题的性质和程度。

这有助于确定电路的设计指标和性能要求。

2. 选择振铃吸收电路类型:根据需求,选择合适的振铃吸收电路类型。

常见的类型包括电阻式、电容式和电感式等。

3. 电路设计:根据选择的电路类型,设计具体的电路结构和参数。

包括选择吸收器、环形电感和负载电阻的数值和配置。

4. 电路布局:将设计好的电路布局在电路板上或进行集成电路设计。

确保电路布线合理、稳定和可靠。

5. 电路测试和调试:完成电路的制作后,进行测试和调试。

通过信号源输入信号,观察输出信号,判断振铃吸收效果是否满足设计需求。

6. 电路优化:根据测试结果,对电路进行优化和调整。

可以通过调整参数、增加滤波器或添加其他组件来改善电路性能。

7. 电路应用:将优化后的振铃吸收电路应用到实际通信系统中。

功率放大器消除颤音的方法

功率放大器消除颤音的方法

功率放大器消除颤音的方法主要有以下几种:

1. 使用稳定的电源:颤音通常是由电源波动引起的,因此使用稳定的电源可以减少颤音产生的可能性。

可以考虑使用高质量的电源滤波器或稳压器。

2. 消除或减小共模干扰:共模干扰是指输入信号中的直流或低频噪声,可以通过使用耦合电容器或差分输入来抑制共模干扰,从而减少颤音的产生。

3. 提高输入电路的抗干扰能力:对于功率放大器的输入电路,可以采用差分输入电路、屏蔽输入线路或使用低噪声运算放大器等方法来提高抗干扰能力,减少颤音的产生。

4. 降低温度:高温环境容易导致功率放大器的颤音问题,因此适当的降低功率放大器的工作温度可以减少颤音的产生。

可以考虑使用散热器或风扇来降低温度。

5. 优化电路设计:通过优化功率放大器的电路设计,可以减少反馈电路的相位延迟,提高系统的稳定性,从而减少颤音的产生。

6. 地线布线和屏蔽设计:良好的地线布线和屏蔽设计可以减少干扰对功率放大器的影响,降低颤音的产生。

需要根据具体情况选择合适的方法进行处理,在设计和安装阶段就应该考虑到这些问题,并采取相应的措施。

运算放大电路振铃产生的原因及解决方法

写在前面想必大家都学过运算放大电路,然而电路参数稍微处理不好便会导致你设计的运算电路效果大大折扣。

振铃在运算放大电路中是经常出现的问题,因为参数的问题或者PCB板硬件本身的问题,往往导致你设计的放大电路不放大反而振荡,振荡电路不振荡反而放大,大学的时候实验室老师就是这么嘲笑我们的,哈哈。

刚下班,回家也没什么事儿,索性就加会儿班,写个博客,分享自己在这方面的理解,同时呢也做为自己的硬件学习笔记吧,我今天分享得就是运放电路振铃产生的原因,以及解决办法。

下面我们开始吧。

振铃产生的原因振铃是怎么产生的,知道了这点我们就知道采取什么措施来避免运放电路的振铃的产生。

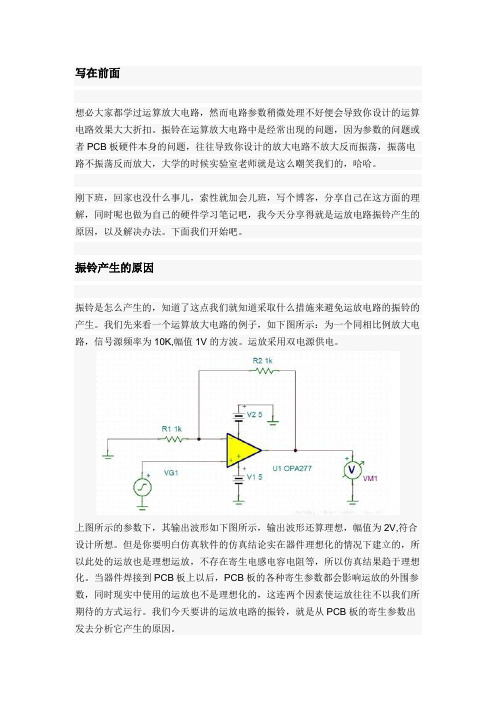

我们先来看一个运算放大电路的例子,如下图所示:为一个同相比例放大电路,信号源频率为10K,幅值1V的方波。

运放采用双电源供电。

上图所示的参数下,其输出波形如下图所示,输出波形还算理想,幅值为2V,符合设计所想。

但是你要明白仿真软件的仿真结论实在器件理想化的情况下建立的,所以此处的运放也是理想运放,不存在寄生电感电容电阻等,所以仿真结果趋于理想化。

当器件焊接到PCB板上以后,PCB板的各种寄生参数都会影响运放的外围参数,同时现实中使用的运放也不是理想化的,这连两个因素使运放往往不以我们所期待的方式运行。

我们今天要讲的运放电路的振铃,就是从PCB板的寄生参数出发去分析它产生的原因。

运放振铃产的原因就是由于反向输入端的寄生电容与反馈电阻构成了一个低通滤波器,大家知道低通滤波器会导致相位滞后。

而运算放大器呢,又是一个无脑的东西,它不知道人们把它接成了什么样子,它只知道吧同相端与反相端的电压差值放大无穷大倍,然而放大倍数又不可能无穷大,这就得益于输出端的反馈回路。

当输出电压过大时,反馈到反相端的电压也会变大,进而输出端电压减小,当输出端电压过小时,反馈到反相端的电压就变小,进而使输出端的电压增大,这样的一个过程如此往复形成一个动态平衡,保持输出端电压稳定。

稳定控制回路振铃现象的消除及其关键参数的选择

稳定控制回路振铃现象的消除及其关键参数的选择第一章:引言1.1 稳定控制回路的基本概念及其重要性1.2 振铃现象的出现及其影响1.3 研究目的和意义第二章:振铃现象的原因分析2.1 稳定控制回路的传递函数及特性2.2 振铃的定义和特点2.3 振铃产生的原因第三章:振铃现象的消除方法3.1 反馈控制方法3.2 前馈控制方法3.3 混合控制方法3.4 滤波器控制方法第四章:关键参数的选择与优化4.1 回路参数的选取方法4.2 参数的调整方法4.3 参数优化的算法与实现第五章:实验验证和结论5.1 实验方案设计5.2 实验结果分析5.3 结论与总结参考文献第一章:引言1.1 稳定控制回路的基本概念及其重要性稳定控制回路是一种广泛应用于工业、军事、航空、能源等领域的控制系统,其主要作用是对制动、加速、停车等动作进行控制,使得系统能够实现稳定的运行和高效的能耗。

稳定控制回路具有响应速度快、精度高、工作可靠、扰动抵抗能力强等特点,因此被广泛应用于现代工业生产和科学研究中,成为现代控制理论及应用的重要组成部分。

1.2 振铃现象的出现及其影响虽然稳定控制回路可以保证系统稳定运行,但是在某些场合下容易出现振铃现象,这种现象表现为系统输出随时间发生大幅度的振荡,其频率比较高,振幅又比较大,会严重影响系统的稳定性和控制精度。

振铃现象的发生通常是由于系统参数选择不当、环节误差放大等原因导致的。

1.3 研究目的和意义对于稳定控制回路来说,振铃现象是一个严重的技术难题,解决这个问题能够提高系统的性能和可靠性,从而更好地满足工程和实际需求。

本论文的研究目的是探讨稳定控制回路振铃的原因,分析影响因素,提出相应的消除方法,并通过关键参数的选择与优化进行实验验证,为稳定控制回路的优化设计提供参考和指导。

第二章:振铃现象的原因分析2.1 稳定控制回路的传递函数及特性稳定控制回路的动态响应特性主要由其传递函数决定,传递函数是指输入与输出之间的关系,它描述了系统的动态响应特性。

振铃吸收电路 -回复

振铃吸收电路-回复什么是振铃吸收电路?振铃吸收电路是一种电子电路,用于在电信系统中消除电信干扰信号或抑制共模噪声信号。

振铃吸收电路能够通过在信号线上加入特定的电感和电容元件来产生滤波效应,从而实现对噪声信号的消除。

振铃吸收电路的原理及工作机制振铃吸收电路利用谐振原理,通过合适的电感和电容参数来形成谐振状态。

当输入信号频率接近振铃电路的谐振频率时,振铃电路的阻抗将显著上升并达到峰值,从而具有很好的吸收效果。

这是因为振铃电路会形成一个与输入信号频率非常接近的高阻抗状态,从而将输入信号吸收掉。

振铃吸收电路的设计步骤1. 确定需要抑制的干扰频率范围:在设计振铃吸收电路之前,需要明确需要抑制的干扰信号的频率范围。

这可以通过测量和分析干扰信号得到。

2. 选择合适的电感元件:根据干扰信号的频率范围,选择合适的电感元件。

电感的参数包括电感值和电流饱和值等。

3. 选择合适的电容元件:根据振铃电路的谐振频率和所需的品质因数,选择合适的电容元件。

电容的参数包括电容值和工作电压等。

4. 组装电路并进行测试:将选定的电感和电容元件组装到电路中,并连接到需要抑制干扰信号的信号线上。

进行测试,检验振铃吸收电路的效果。

振铃吸收电路的应用领域振铃吸收电路广泛应用于电信系统、无线通信设备、音频系统、电源系统等领域。

它可以有效地消除电信传输中的噪声和干扰信号,提高通信质量和可靠性。

振铃吸收电路的优势和局限性振铃吸收电路具有以下优势:1. 高效吸收:振铃吸收电路能够有效地吸收干扰信号,提供清晰的输出信号。

2. 简单设计:振铃吸收电路的设计相对简单,只需要选择合适的电感和电容元件即可。

3. 低成本:由于振铃吸收电路的设计相对简单,所需的元件成本较低。

然而,振铃吸收电路也存在一些局限性:1. 受限谐振频率:振铃吸收电路的抑制效果受限于谐振频率的范围。

2. 对频率变化敏感:振铃吸收电路对输入信号的频率变化较为敏感,需要精确选择电感和电容元件。

开关电源振铃的修正

SLVA255 – September 2006

Jeff Falin PMPJeff Falin............................................................................................ PMP Portable Power Applications

L

PAR5

Figure 1. Boost Converter Schematic 图. 升压转换器示意图

ZHCA057–2006年9月 提交文档反馈 SLVA255 – September 2006 Submit Documentation Feedback

升压转换器开关节点的振铃最小化

Minimizing Ringing at the Switch Node of a Boost Converter

1

问题的描述 tion of the Problem

Figure 2. Ringing at Switch Node of Boost Converter 图. 升压转换器开关节点上的振铃曲线 Figure 2 shows a scope plot of the switch node of a boost converter on a 5-ns/div time scale. A scope and scope probe with at least a 500-MHz bandwidth, approximately twice the expected 200-MHz ringing 图 为5 2 展示了升压转换器开关节点上的实测曲线,时间刻度 (time scale) ns/div。测量所使用的示波器及 frequency, were used to take the plot. The scope probe’s ground loop was minimized to prevent inductive 示波器探针具有至少 500 MHz 的带宽,近似为所估算的 200 MHz 振铃频率的 2 倍。示波器探针的接地环 pick-up from distorting the measurement. With VIN = 3.3 V and VOUT = 5 V, the peak voltage at the switch 路做了最小化,以避免感应拾取 pick-up)造成测量结果的失真。由于 VIN = 3.3 V且 VOUT = V,因 node should be no more than V(inductive of the ringing at5the OUT + VDIODE≈ 5.7 V. However, the peak amplitude switch node is 9.8 V, which could damage the low-side switch. 此转换节点的峰值电压不应大于 VOUT + VDIODE≈5.7 V,但是开关节点上振铃的峰值幅度为 9.8 V,有可能损 坏低侧开关。 The power supply designer has several options during the design phase to minimize this ringing. If a controller is used, the designer should select FETs and diodes with minimal parasitic capacitances and then lay out the board to minimize the distance between both switches and the inductor, thereby 在设计方面,电源设计人员具有多种方法来实现振铃的最小化。如果采用控制器,设计人员应同时选用具 minimizing LPAR2 and LPAR3 . In addition, the designer can minimize LPAR1 by reducing the distance 有最小寄生电容的 FET 及二极管,并通过板载布线,最大程度的减小两个开关与电感之间的距离,从而使 between the source pin of the FET and the power ground point or plane. LPAR4 and LPAR5 can be L FET minimized by最小化。此外,设计人员还可以通过减小 placing the bulk output capacitor as close as电源引脚与电源接地点或接地层之间的距离来实 possible to the diode's cathode and power PAR2 和 LPAR3 ground. A high-frequency bypass capacitor [C ] between the output (0.01 µF – 2.2 µF) L and power 现 的最小化。通过将大输出电容尽可能地靠近二极管的阴极和接地电源放置,还将使得 OUT-BYP LPAR1 PAR4 及 LPAR5 ground is also recommended. 最小化。介于输出值(0.01 mF – 2.2 mF)和接地电源之间的高频旁路电容 (COUT-BYP) 来最小化振铃。在输出 Improving board layout may not mF be possible due to board size restrictions or due to an integrated FET 与电源地之间连接 的高频旁通电容 0.01 mF – 2.2 [C ]也是推荐的方法。 power IC with internal CPAR#, LPAR1, LPAR2, and LPAR3. OUT-BYP Therefore, a snubber circuit, consisting of RSNUB and CSNUB from the switch node to power ground may be required. A snubber is an energy-absorbing circuit 由于电路板的尺寸限制或是由于集成 电源 IC 所具有的内部 CPAR#、LPAR1、LPAR2 及 LPAR3,改进板载布线 FET by used to eliminate voltage spikes caused circuit parasitic inductance when a switch opens. By providing 的方法不一定可行,因此需要一个缓冲电路 ——由the 及 CSNUB 组成,从开关节点至电源地。该 RSNUB an alternate path to ground for the current (snubber) flowing through circuit's parasitic inductance, the snubber reduces the voltage transient and damps the subsequent ringing with the parasitic capacitance that occurs 缓冲电路是一个能量吸收电路,用于消除开关闭合时电路寄生电感所引起的电压毛刺。当开关闭合时,缓 when the switch opens. 冲电路为流经电路寄生电感的电流提供一条替代的接地通路,从而抑制了电压瞬变并降低了寄生电容上的 The rest of this application report provides steps on how to size the snubber components to damp the 后继起振铃。 ringing without significantly slowing down the switch turnoff rise time or reducing overall efficiency. 该应用报告的其余部分逐步讲述了在无明显减少开关关断的上升时间或降低整体效率的情况下,如何确定 After determining the frequency of the ringing, fINIT = 217 MHz, caused by the parasitic inductance [LΣPAR#] and parasitic capacitance [CΣPAR#] from the scope plot in Figure 2, add enough capacitance [CADD] from 缓冲电路元件的大小以抑制振铃。 the switch node to ground to reduce the ringing frequency by ½. Figure 3 shows the ringing at 113 MHz after 300 pF of capacitance has been added. 在确定了由寄生电感 [LΣPAR#] 及寄生电容 [CΣPAR#] 所引起的振铃频率(fINIT = 217 MHz)之后(如图 2 的实 测波形所示),在开关节点与接地之间连接适当的电容[CADD],可降低振铃频率至½。如图 3所示,在添加 了 300 pF 电容后,振铃频率为 113 MHz。

如何解决电路中的噪声问题

如何解决电路中的噪声问题电路中的噪声问题一直是工程师们在设计和实施电路时面临的挑战。

噪声会降低电路的性能和可靠性,影响信号的准确传输。

本文将介绍一些解决电路中噪声问题的方法和技术。

首先,了解噪声的来源是解决问题的第一步。

电路中的噪声可以来自多种来源,包括器件本身的噪声和外部干扰。

器件本身的噪声有热噪声和互模干扰噪声。

热噪声是由于器件内部的热激活运动引起的,它与电阻和温度有关。

互模干扰噪声是由于信号在不同电路之间进行传输时,相互之间的互相作用引起的。

外部干扰包括电源线的杂散噪声、电磁干扰和地线回流等。

以下是一些解决电路中噪声问题的常用方法和技术:1. 选择低噪声器件:选择具有低噪声特性的器件是减少电路噪声的有效方法。

在选择器件时,要查阅器件的噪声参数,比如热噪声和互模干扰噪声。

选择具有较低噪声参数的器件可以显著改善电路的性能。

2. 使用屏蔽材料和屏蔽技术:屏蔽材料的使用可以减少外部电磁干扰对电路的影响。

可以通过在电路周围加上金属屏蔽罩或者使用金属屏蔽网来阻挡干扰信号的进入。

此外,还可以使用屏蔽线缆或屏蔽外壳来降低电路的干扰噪声。

3. 进行地线隔离和回流:地线是电路中最常见的噪声来源之一。

通过合理设计地线回流路径和使用适当的隔离技术,可以减少地线回流带来的噪声。

同时,良好的地线布局可以降低地线回流的噪声影响。

4. 使用滤波器:滤波器是减少干扰噪声的重要工具。

可以使用低通、高通、带通或陷波滤波器来滤除特定频率范围内的噪声。

滤波器的选择要根据电路的特定需求来进行。

5. 优化供电系统:电源线的杂散噪声也是导致电路噪声的一个重要因素。

通过使用稳压器、电磁兼容滤波器和良好的电源布局,可以降低供电系统噪声并提高电路性能。

6. 使用差分信号传输:差分信号传输可以有效地减少共模噪声对信号的影响。

差分信号传输通过同时传输正向和反向信号,在接收端通过差分放大器来提取有用信号。

这样就可以将共模噪声有效地消除。

总结起来,解决电路中的噪声问题需要工程师综合考虑多种方法和技术。

继电器消除高压噪声

这个电路中,三个压电发动机PZ1、PZ2和PZ3,连接到RS 232 9T连接器的T1、T5和T9管脚。电路有三个继电器转换压电发动机的高压输入。通常继电器开环节点连接到高压放大器输出;继电器闭环节点连接到三个1 kΩ电阻,将高压引起的噪声旁路到地。

英文原文:

Relays eliminate high-voltage noise

设计多级滤波器来消除开关电源转换器的输出噪声

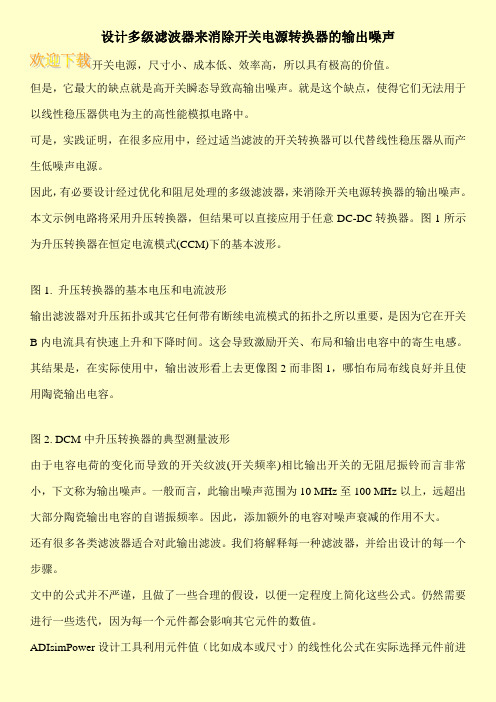

设计多级滤波器来消除开关电源转换器的输出噪声开关电源,尺寸小、成本低、效率高,所以具有极高的价值。

但是,它最大的缺点就是高开关瞬态导致高输出噪声。

就是这个缺点,使得它们无法用于以线性稳压器供电为主的高性能模拟电路中。

可是,实践证明,在很多应用中,经过适当滤波的开关转换器可以代替线性稳压器从而产生低噪声电源。

因此,有必要设计经过优化和阻尼处理的多级滤波器,来消除开关电源转换器的输出噪声。

本文示例电路将采用升压转换器,但结果可以直接应用于任意DC-DC转换器。

图1所示为升压转换器在恒定电流模式(CCM)下的基本波形。

图1. 升压转换器的基本电压和电流波形输出滤波器对升压拓扑或其它任何带有断续电流模式的拓扑之所以重要,是因为它在开关B内电流具有快速上升和下降时间。

这会导致激励开关、布局和输出电容中的寄生电感。

其结果是,在实际使用中,输出波形看上去更像图2而非图1,哪怕布局布线良好并且使用陶瓷输出电容。

图2. DCM中升压转换器的典型测量波形由于电容电荷的变化而导致的开关纹波(开关频率)相比输出开关的无阻尼振铃而言非常小,下文称为输出噪声。

一般而言,此输出噪声范围为10 MHz至100 MHz以上,远超出大部分陶瓷输出电容的自谐振频率。

因此,添加额外的电容对噪声衰减的作用不大。

还有很多各类滤波器适合对此输出滤波。

我们将解释每一种滤波器,并给出设计的每一个步骤。

文中的公式并不严谨,且做了一些合理的假设,以便一定程度上简化这些公式。

仍然需要进行一些迭代,因为每一个元件都会影响其它元件的数值。

ADIsimPower设计工具利用元件值(比如成本或尺寸)的线性化公式在实际选择元件前进。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

?>?设计支持?>?技术文档?>?应用笔记?>?供电电路?> APP 6287关键词:?开关电源, Class D功放,振铃应用笔记6287利用Snubber电路消除开关电源和Class D功放电路中的振铃Frank Pan, CPG部门高级应用工程师摘要:开关电源和Class D功放,因为电路工作在开关状态,大大降低了电路的功率损耗,在当今的电子产品中得到了广泛的应用。

由于寄生电感和寄生电容的存在,电路的PWM开关波形在跳变时,常常伴随着振铃现象。

这些振铃常常会带来令人烦恼的EMC问题。

本文对振铃进行探讨,并采用snubber电路对PWM 开关信号上的振铃进行抑制。

?振铃现象在开关电源和Class D功放电路中,振铃大多是由电路的寄生电感和寄生电容引起的。

寄生电感和寄生电容构成LC谐振电路。

LC谐振电路常常用两个参数来描述其谐振特性:振荡频率(),品质因数(Q值)。

谐振频率由电感量和电容量决定:。

品质因数可以定义为谐振电路在一个周期内储存能量与消耗能量之比。

并联谐振电路的Q值为:,其中R P是并联谐振电路的等效并联电阻。

串联谐振电路的Q值为:,其中R S为串联谐振电路的等效串联电阻。

在描述LC电路的阶跃跳变时,常用阻尼系数() 来描述电路特性。

阻尼系数跟品质因数的关系是:或。

在临界阻尼(=1)时,阶跃信号能在最短时间内跳变到终值,而不伴随振铃。

在欠阻尼(<1)时,阶跃信号在跳变时会伴随振铃。

在过阻尼(>1)时,阶跃信号跳变时不伴随振铃,但稳定到终值需要花费比较长的时间。

在图一中,蓝,红,绿三条曲线分别为欠阻尼(<1),临界阻尼(=1),过阻尼(>1)时,对应的阶跃波形。

图一不同阻尼系数对应的阶跃信号(从左至右分别为欠阻尼,临界阻尼,过阻尼时对应的阶跃信号)我们容易得到并联LC谐振电路的阻尼系数:。

在我们不改变电路的寄生电感和寄生电容值时,调整等效并联电阻可以改变谐振电路的阻尼系数,从而控制电路的振铃。

阶跃信号因振铃引起的过冲跟阻尼系数有对应的关系:。

OS(%)定义为过冲量的幅度跟信号幅度的比值,以百分比表示。

表一列出了不同阻尼系数对应的过冲OS(%)。

图二过冲图示表一:不同阻尼系数对应的过冲OS(%)阻尼系数0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 过冲量85.4% 72.9% 62.1% 52.7% 44.4% 37.25% 30.93% 25.4% 20.6% 阻尼系数0.5 0.55 0.6 0.65 0.7 0.75 0.8 0.85 0.9 过冲量16.3% 12.6% 9.5% 6.8% 4.6% 2.8% 1.5% 0.6% 0.15%振铃的危害对于振铃,我们直观感受到的是示波器屏幕上的电压的波动。

实际带来问题的通常是电路的电流的谐振。

在图三所示的电路里面,当PWM开关信号V1在0V 和12V切换时,流过电感L1和电容C1的谐振电流可以达到安培量级,如图四所示。

在高频(图三所示电路的谐振频率为232MHz,开关电源和Class D电路里常见的振铃频率在几十兆到几百兆Hz之间),安培量级的电流,通过很小的回路,都可能造成辐射超标,使产品无法通过EMC认证。

注:10米处电场强度计算公式为:,单位为伏特/米。

其中f为电流的频率(MHz),A为电流的环路面积(CM2?),I s为电流幅度(mA)。

图三LC谐振电路图四电容C1两端的电压和流过电容C1的谐振电流避免测量引入的振铃为了提高电路的效率,开关电源和Class D功放的PWM开关信号的上升/下降时间都比较短,常常在10ns量级。

测量这样的快速切换信号,需要考虑到示波器探头,特别是探头的接地线对测量结果的影响。

在图五的测量方法中,示波器探头的地线过长,跟探头尖端的探针构成很大的回路。

捕获到的信号出现了很大的振铃,如图六所示。

图五示波器探头上长的地线会影响PWM开关信号的测量结果图六图五测量方法对应的测试结果为了降低示波器探头对测量结果的影响,我们在电路板上焊接测量接地探针,并去除示波器探头上的地线,如图七所示。

通过这种方法,我们可以大大降低示波器探头地线对测量引入的振铃。

图八是使用这种方法捕获到的PWM开关信号的前后沿波形。

图七通过在PCB上焊接接地点改善测量结果图八图七测量试方法对应的测试结果开关电源和Class D功放电路中的谐振电路在开关电源和Class D功放电路中,芯片退耦电容到芯片电源引脚之间的PCB 走线,芯片电源引脚到内部硅片之间的邦定线可以等效成一个寄生电感。

在功率MOSFET截止时,功率MOSFET电极之间的电容(Cgs,Cgd,Cds) 可等效成一个寄生电容。

如图九所示。

这些寄生电感和寄生电容构成了LC谐振电路。

图九中的高端MOSFET导通,低端MOSFET截止时,可以等效成图十所示的LC谐振电路。

为了提高电路的效率,当今芯片内部集成的功率MOSFET的都做得比较小,常常在几十毫欧到几百毫欧之间。

这意味着谐振电路的阻尼系数可能很小。

造成的结果是在PWM开关切换时,伴随着比较大的振铃。

图九开关电源和D类功放电路里的寄生电感和电容图十图九中高端MOSFET导通,低端MOSFET截止时的等效电路利用Snubber抑制振铃上面对LC谐振电路的振铃做了介绍。

下面介绍利用snubber电路对振铃进行抑制。

如图十一中虚线框内的电路所示,Snubber电路由一个小阻值的电阻和一个电容串联构成。

其中电阻用来调节LC谐振电路的阻尼系数。

电容在振铃频率(即LC谐振频率)处呈现很低的容抗,近似于短路。

在PWM开关频率又呈现出较高的容抗。

如果没有电容的存在,PWM信号会一直加在电阻两端,电阻会消耗过多的能量。

下面给选取合适的电阻值,让PWM开关信号能快速稳定到终值,而又不产生振铃(临界阻尼)。

我们以图十一的电路为例。

其中L1是电路的寄生电感,C1是电路的寄生电容,是电路的等效并联电阻。

图十一snubber电路整理得到:用snubber改善振铃实例下面以一个实例介绍snubber电路元件值的选取。

图十二a 是一款降压DC-DC 在PWM开关引脚处测到的波形。

在PWM信号开关时,伴随着振铃现象。

通过示波器测量到的振铃频率为215.5MHz。

我们可以构建第一个方程:为了得到L1和C1的值,我们需要构建另外一个方程。

我们给电容C1并联一个小电容:在PWM引脚临时对地焊接一个56pF的电容。

这时,振铃频率变为146.2MHz,如图十二b。

据此,我们构建另一个方程:通过上面两个方程,可以很快计算出C1=47.7pF,L1=11.4nH。

然后,我们根据过冲量来计算等效并联电阻。

从图十三读出过冲OS(%)为28%,对应的阻尼系数()值为0.37。

,得到十三阶跃信号过冲我们得到了电路的L1,C1和的值,带入我们前面得到的公式,计算得到。

可以选取18欧姆的电阻。

电容的选择:元件值的选取原则是,在LC谐振频率(振铃频率)处,容抗要远小于的阻值。

对PWM开关信号,又要呈现出足够高的容抗。

图十四是采用560pF的电容,采用18欧姆电阻时,PWM开关信号的前沿波形。

对比图十二a中的波形,振铃得到了很大的改善。

图十四加入snubber电路后的PWM前沿波形Snubber电路的能量消耗Snubber电路中能量消耗在电阻上,而能量消耗的多少又取决于电容的容量,跟电阻的值无关。

这是因为:PWM信号给电容充电时,电路给snubber电路提供的能量为,而电容只得到了其中的一半(),另一半被消耗掉。

改变的电阻值,只是改变了电容充电的速度和消耗能量的速度,而不改变充电一次所消耗的总能量。

放电时,电容储存的能量被消耗。

在一个PWM开关周期的能量消耗为。

功率消耗为:,其中为PWM开关频率,V为snubber两端的电压幅度峰峰值。

有些应用场合对电路的效率有很高的要求,对snubber电路消耗的功率也需要进行限制。

遇到这种情况,可以适当调整snubber电路的元件值,在PWM信号的振铃和功率消耗之间取得平衡。

降低snubber功耗的另外一个有效办法是降低电路的寄生电感:把退耦电容尽量靠近芯片放置,加粗退耦电容到芯片之间PCB走线的宽度。

从前面提到的公式()可以看出,降低了寄生电感L1,在其他电路参数不改变的情况下,要保持同样的阻尼系数,需要更小的电阻值。

同时,寄生电感降低后,电路的振铃频率会提高。

这都允许我们选用更小容值的电容,从而可以降低snubber电路引入的功率损耗。

总结我们讨论了开关电源和Class D功放电路里PWM信号的振铃现象,振铃带来的危害,振铃引起的过冲和电路的阻尼系数的对应关系。

然后介绍了如何用snubber对振铃进行抑制。

最后通过一个实例介绍了snubber电路里元件值的选取。

在介绍过程中,引入了一些简单的数学公式。

这些数学公式有助于加深我们对概念的理解。

参考文献•“Radio-Frequency Electronics Circuits and Applications” by Jon B.Hagen•“EMC for Product Designers” Forth Edition by Tim Williams•“基于运算放大器和模拟集成电路的电路设计(第3版) ” Sergio Franco 着,刘树棠朱茂林荣玫译。