chp5触发器

(电子技术教学课件)ch5门电路及触发器

(2-18)

二、输入、输出负载特性 1、前后级之间电流的联系 &?&

(2-19)

前级输出为 高电平时

R2 T3

R5

前级

+5V

+5V

R4

R1

反偏

T4

T1

流出前级 电流IOH (拉电流)

后级

(2-20)

R2 C S2

CP

Q F主 Q

R1 C S1

K CP J

(2-60)

JK触发器 的功能

J=K=0时:

被封锁

Q Q 保持原态

Q F从 Q

R2 C S2

CP

F主

R1 C S1

=0 K CP J =0

(2-61)

JK触发器 的功能

J=K=1时:

相当于T触 发器T=1

Q F从 Q

R2 C S2

CP

F主

2、在控制端加入负脉冲,可以使触发器状 态变化。SD端加入负脉冲,使Q=1,SD 称为“置位”或“置一”端。RD端加入 负脉冲,使Q=0,RD称为“复位”或 “清0”端。

(2-52)

三、 触发器按逻辑功能的分类

1 RS触发器

Q

Q

&

&

c

d

直接置0 或置1

RD

& a

SD

& b

时钟信号

R

CP

S

(2-53)

含义

输入为低电平时流入 输 入 端 的 电 流 < 1 .6 m A 。 输入为高电平时流入 输 入 端 的 电 流 <40μ A。

DS-19A08-BNG DS-19A08-BN网络报警小主机用户手册 V1.1

2.1 主板接口描述 .......................................................................................................................... 10 2.2 设备接线 .................................................................................................................................. 11

网络报警小主机.用户手册

目录

第 1 章 网络报警小主机简介........................................................................................................9

1.1 功能简介 .................................................................................................................................... 9 1.2 功能特性 .................................................................................................................................... 9

ch.5 触发器

1 1.

触发器保持 “1”态不 ” Q Q变

.

0 1

0 0

& G1 SD1

& G2

RD1

总目录 章目录 返回 上一页 下一页 章目录 上一页 下一页

(4) SD=0,RD = 0

“1”态 ” 当信号S 当信号 D= RD = 0 Q 1 同时变为1时 同时变为 时,由 1. 于与非门的翻转 时间不可能完全 & G1 相同, 相同,触发器状 1 1 0 态可能是“ ” 态可能是“1”态, 1 1 也可能是“ ” 也可能是“0”态, SD 0 不能根据输入信 号确定。 号确定。 Q

.

1

1 0 若先翻转

& G2 1 1 RD 0

先翻转,则触发器为“ ” 若G1先翻转,则触发器为“0”态

总目录 章目录 返回 上一页 下一页 章目录 上一页 下一页

基本 RS 触发器功能表 SD 1 0 1 0 RD 0 1 1 0 Q 0 1 不变 功能 置0 置1 保持

逻辑符号 Q Q

同时变 1后不确定 后不确定

在箭头旁边用文字或 符号表示实现转换所 必备的条件

总目录 章目录 返回 上一页 下一页 章目录 上一页 下一页

例2:画出同步 RS 触发器的输出波形。设触发器的 触发器的输出波形。 初态为Q=0。 初态为Q=0。

S 0 0 1 1

R 0 1 0 1

Qn+1 Qn 0 1 不定

总目录 章目录 返回 上一页 下一页 章目录 上一页 下一页

SD RD RD(Reset Direct)-直接置“0”端(复位 低电平有效 Direct)-直接置“ 端) SD(Set Direct)-直接置“1”端(置位端) Direct)-直接置“ 置位端)

计算机组成原理chp5

指令寄存器IR(Instruction Register)

2、CPU的基本组成

指令译码器ID(Instruction Decoder)

暂存在指令寄存器中的指令只有在其操作码部分经译码后才 能识别出是一条什么样的指令。 译码器经过对指令进行分析和解释,产生相应的控制信号提 供给时序控制信号形成部件。 由脉冲源产生一定频率的脉冲信号作为整个机器的时钟脉冲 时序控制信号形成部件又称微操作信号发生器,真正控制各 部件工作的微操作信号是由指令部件提供的操作信号、时序 部件提供的时序信号、被控制功能部件所反馈的状态及条件 综合形成的。

计算机科学与技术学院系统教研室

5.2.3LAD指令的指令周期

取指周期 执行周期

计算机科学与技术学院系统教研室

5.2.3LAD指令的指令周期

计算机科学与技术学院系统教研室

5.2.5 ADD指令的指令周期

计算机科学与技术学院系统教研室

5.2.5ADD指令的指令周期

计算机科学与技术学院系统教研室

第五章 中央处理器

第五章 中央处理器

5.1CPU功能和组成 5.2指令周期 5.3时序产生器 5.4微程序控制器及其设计 5.5硬布线控制器及其设计 5.6传统CPU 5.7流水CPU 5.8RISC的CPU 5.9多媒体CPU

计算机科学与技术学院系统教研室

5.1 CPU的功能和组成

1、CPU的功能

计算机科学与技术学院系统教研室

5.2 指令周期

计算机科学与技术学院系统教研室

5.2.1 指令周期的基本概念

概念

指令周期:指取指令、分析指令到执行完该指令所需的全部 时间。 各种指令的指令周期相同吗?为什么? 机器周期通常又称CPU周期, 通常把一条指令周期划分为若干个机器周期,每个机器周期 完成一个基本操作。 主存的工作周期(存取周期)为基础来规定CPU周期,比如, 可以用CPU读取一个指令字的最短时间来规定CPU周期 不同的指令,可能包含不同数目的机器周期。 一个机器周期包含若干个时钟周期(节拍脉冲或T脉冲)。 CPU周期规定,不同的计算机中规定不同

chp2-5

F A Bi Cni i i

Cni 1 Ai Bi AiCni BiCni

为了实现多种算术逻辑运算,可将Ai和Bi输入一个函数发

生器(进位传递函数和进位产生函数)得到输出Xi和Yi, 作为一位全加器的输入(见下页图)。

4

2.5.2 多功能算术/逻辑运算单元ALU

2.5 定点运算器的组成

2.5.1 2.5.2 2.5.3 2.5.4 2.5.5 逻辑运算 多功能算术/逻辑运算单元ALU 先行进位ALU 内部总线 定点运算器的基本结构

1

2.5 定点运算器的组成

基本组成包括:

算术逻辑运算单元ALU:核心部件 暂存器:用来存放参与计算的数据及运算结果,它

11

2.5.2 多功能算术/逻辑运算单元ALU

上述片内进位采用串行,具有延时长的缺点如何改进? 思考:Cn+i与X、Y有关,而每一位中X、Y的产生是不是 同时的?

答:由于每一位中X、Y的产生是同时的,则可以由下面方法算出并行进 位的Cn+4 第0位向第1位的进位公式为 Cn+1=Y0+X0Cn (1) 其中Cn是向第0位(末位)的进位。 第1位向第2位的进位公式为

22

成组先行进位部件CLA的逻辑图74182

23

2.5.3 先行进位ALU

例:设计16位先行进位ALU(图2.13)

内先行进位,片间先行进位.

24

32位ALU逻辑方框图

2个74L182 8个4位ALU74L181

25

64位组间先行进位ALU

G* P*

7 4 L 1 8 2 G3 P3 Cn+z G2 P2 Cn+y G1P1 Cn+xG0 P0

16

74181ALU逻辑图(2)

chp5-3

指令格式:ATH

IN, OUT, LEN;

HTA

IN, OUT, LEN

LD I0.0 //使能输入端 ATH VB100, VB200, 4 //使能输入有 //效时,把VB100开始的4个ASCII码转 //换成从VB200开始的十六进制数

ASCII码到十六进制数转换指令举例

5.3.4 转换指令

转换指令是指对操作数的类型进行转换, 包括数据的类型转换、码的类型转换以及 数据和码之间的类型转换。

数据类型主要包括字节、整数、双整数、 实数,不同性质的指令对操作数的类型要 求不同,类型转换指令可将固定的一个数 值用到不同类型要求的指令,而不必对数 据进行针对类型的重新装载。

返回

5.3.4 转换指令

5.3.5 表功能指令

3. 表查找指令

表查找指令执行之前,应先对INDX的内容清0,当使能

输入有效时,从INDX开始搜索表TBL,寻找符合由PTN 和CMD所决定的条件的数据,如果没有发现符合条件的 数据,则INDX的值等于EC。如果找到一个符合条件的 数据,则将该数据的表中地址装入INDX中。 表查找指令执行完成,找到一个符合条件的数据,如果 想继续向下查找,必须先对INDX加1,以重新激活表查 找指令。

数据最大填表数为 TL=5(<=100) 实际填表数EC=0003(<=100)

数据0 数据1 数据2 无效数据 无效数据

5.3.5 表功能指令

1. 填表指令

ATT指令 该指令在梯形图中有2个数据输入端:DATA为数值输 入,指出将被存储的字型数据或其地址;TBL表格的 首地址,用以指明被访问的表格。当使能输入有效时, 将输入字型数据添加到指定的表格中。

锁存器 寄存器 触发器

锁存器、触发器和寄存器分析触发器:flipflop,锁存器:latch,寄存器:register锁存器在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器.由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。

由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能构成一个存储n位二进制码的寄存器。

锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,尽当锁存器处于使能状态时,输出才会随着数据输入发生变化。

触发器触发器是边沿敏感的存储单元,数据存储的动作有某一信号的上升或者下降沿进行同步的。

在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器.由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。

由于一个触发器能够存储一位二进制码,所以把n个触发器的时钟端口连接起来就能构成一个存储n位二进制码的寄存器。

寄存器用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。

其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。

寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。

触发器是在时钟的沿进行数据的锁存的,而锁存器是用电平使能来锁存数据的。

所以触发器的Q输出端在每一个时钟沿都会被更新,而锁存器只能在使能电平有效器件才会被更新。

有一些教科书里的触发器实际是锁存器。

在FPGA设计中建议如果不是必须那么应该尽量使用触发器而不是锁存器。

钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器,钟控D触发器在使能情况下输出随输入变化,边沿触发器只有在边沿跳变的情况下输出才变化。

两个D锁存器可以构成一个D触发器,归根到底还是dff是边沿触发的,而latch是电平触发的。

锁存器的输出对输入透明的,输入是什么,输出就是什么,这就是锁存器不稳定的原因,而触发器是由两个锁存器构成的一个主从触发器,输出对输入是不透明的,必须在时钟的上升/下降沿才会将输入体现到输出,所以能够消除输入的毛刺信号。

数字电子技术5章

波形图

反映锁存器输入信号取值和状态之间对应关系 的图形称为波形图。

R'D S'D

Q

Q'

置1 保持 置1 置0 置1 不允许 置1

例:在 SR 锁存器电路中,已知 SD 和 RD 的电压波形 如图所示,试画出 Q和 Q' 端对应的电压波形。

解:实质上这是一个用已知的 SD 和 RD 的状态确定 Q 和 Q ' 状态的问题。 只要根据每个时间区里 SD 和 RD 的 状态去查触发器的特性表,即可找出 Q 和 Q' 的相应状态,并画出它们的 波形图。

CLK

波R

形S

图

Q

Q'

不 置 不 置不置 不置 不不 不 变 1 变 0 变 1 变 0 变变变

例:已知电平触发SR触发器的输入信号波形如下图, 试画出Q、Q'端的电压波形。设触发器的初态为Q=0。

解:由给定的输入波形可见在第 一个CLK高电平期间先是S=1、 R=0,输出被置成Q=1,Q'=0。随 后输入变成了S=R=0,因而输出 状态保持不变。最后输入又变为 S=0、R=1,将输出置成Q=0, Q'=1,故CLK回到低电平以后触 发器停留在Q=0,Q'=1的状态。

因为锁存器新的状态Q*(Qn+1,也叫做次 态)不仅与输入状态有关,而且与锁存器原 来的状态Q(Qn,也叫做初态)有关,所以 把Q也作为一个变量列入了真值表,并将Q称 作状态变量,把这种含有状态变量的真值表 叫做锁存器的特性表(或功能表)。

特性表(功能表)

态初 ,态 也: 就锁 是存 锁器 存接 器收 原输 来入 的信 稳号 定之 状前 态的 。状

由于控制方式的不同(即信号的输入方式以及触发器状 态随输入信号变化规律的不同),触发器的逻辑功能在细 节上又有所不同。因此根据触发器逻辑功能的不同分为 SR触发器、JK触发器、T触发器、D触发器等几种类型。

数字电子技术基础第五章-触发器

CLS KRQQ*

0X X 0 0 0X X 1 1 10 0 0 0 10 0 1 1 10 1 0 0 10 1 1 0 11 0 0 1 11 0 1 1 1 1 1 0 1* 1 1 1 1 1*

《数字电子技术基础》第五版

5.3 电平触发的触发器

一、基本SR触发器的电路结构与工作原理

CLS KRQQ*

主从JK电路结构与工作原理

在CLK高电平期间,主触发器只翻转一次

工作原理

《数字电子技术基础》第五版

CLJKKQQ* X X X X Q*

0 00 0 0 01 1 0 10 0 0 11 0 1 00 1 1 01 1 1 10 1 1 11 0

工作原理

《数字电子技术基础》第五版

CLJKKQQ* X X XX Q

《数字电子技术基础》第五版

第五章 触发器

5.1 概述

Flip-flop

一、触发器

能够存储一位二值信息的基本电路单元。

二、触发器特点: 1.保持 2.更新

《数字电子技术基础》第五版

三、触发器分类:

按逻辑功能分:SR触发器、D触发器、 JK触发器、T触发器。

按触发方式分:电平触发方式、脉冲触发方式 及边沿触发方式。

0 00 0 0 01 1 0 10 0 0 11 0 1 00 1 1 01 1 1 10 1 1 11 0

工作原理

《数字电子技术基础》第五版

CLJKKQQ* X X XX Q

0 00 0 0 01 1 0 10 0 0 11 0 1 00 1 1 01 1 1 10 1 1 11 0

工作原理

工作原理

《数字电子术基础》第五版

CLS KRQQ*

触发器

互补输出端, 互补输出端, (一)由与非门组成的基本 正常工作时, 正常工作时, 它们的输出 1. 电路结构及逻辑符号 状态相反。 状态相反。 Q Q

RS 锁存器

Q Q

低电平有效 S R G1 G2 SD RD

SD

信号输入端

RD

置1端,也 置0端,也 称置位端。 称复位端。 称置位端 。 称复位端 。 S 即 Set R 即 Reset

主从RS RS触发器 三、 主从RS触发器

1.电路结构 .

由两级同步RS触 由两级同步 触 发器串联组成。 发器串联组成。 G1~G4组成从触 ~ 组成从触 发器,G5~G8组 发器, ~ 组 成主触发器。 成主触发器。 CP 与CP’互补, 互补, 互补 使两个触发器工 作在两个不同的 时区内。 时区内。

Q = 1,Q = 0 时,称为锁存器的 1 状态,记为 Q = 1; 状态, , ; Q = 0,Q = 1 时,称为锁存器的 0 状态,记为 Q = 0。 状态, , 。

二、可控 RS 锁存器

1. 电路结构与工作原理 Q 基本 RS 锁存器 Q 工作原理

★ CP = 0 时,G3、G4

G1 1 S Q3 G3 Q4 R 1

JK触发器的功能小结: 触发器的功能小结: 触发器的功能小结 1. 当J=0、K=0时,具有保持功能; 、 时 具有保持功能; 2. 当J=1、K=1时,具有翻转功能; 、 时 具有翻转功能; 3. 当J=0、K=1时,具有复位功能; 、 时 具有复位功能; 4. 当J=1、K=0时,具有置位功能。 、 时 具有置位功能。

触发器转换成D触发器 一、JK触发器转换成 触发器 触发器转换成

Q

Q

KC J

CHP5

VB中的控制结构

• 顺序结构 • 选择结构

– 在程序执行的过程中,根据是否满足条件来 判断控制是否转移。 – 根据不同的情况执行不同的操作

• 循环结构

– 重复执行程序的某一部分

选择结构

1. If…Then语句(单分支结构)

表达式

F

If <表达式> Then T 语句块 语句块 End If 或 If <表达式> Then <语句> 例:已知两个数x和y,比较它们的大小, 图1-3-7 单分支结构 使得x大于y. x y If x<y Then t=x x=y t y=t End If 或 If x<y Then t=x: x=y: y=t 图 1-3-8 两个数交换

图 1-3-10 多分支结构

不管有几个分支,依次判断,当某条件满足,执行相应的语句块, 其余分支不再执行;若条件都不满足,且有Else子句,则执行该 语句块,否则什么也不执行。. ElseIf不能写成 Else If。

例 已知百分制成绩mark,显示对应的五级制成绩 哪些正确,哪些错误?

方法一 If mark >= 90 Then Print "优" ElseIf mark >= 80 Then Print "良" ElseIf mark >= 70 Then Print "中" ElseIf mark >= 60 Then Print "及格" Else Print "不及格" End If 方法二 If mark < 60 Then Print "不及格" ElseIf mark < 70 Then Print "及格" ElseIf mark < 80 Then Print "中" ElseIf mark < 90 Then Print "良" Else Print "优" End If 方法三 If mark >= 60 Then Print "及格" ElseIf mark >= 70 Then Print "中" ElseIf mark >= 80 Then Print "良" ElseIf mark >= 90 Then Print "优" Else Print "不及格" End If

555构成的电路

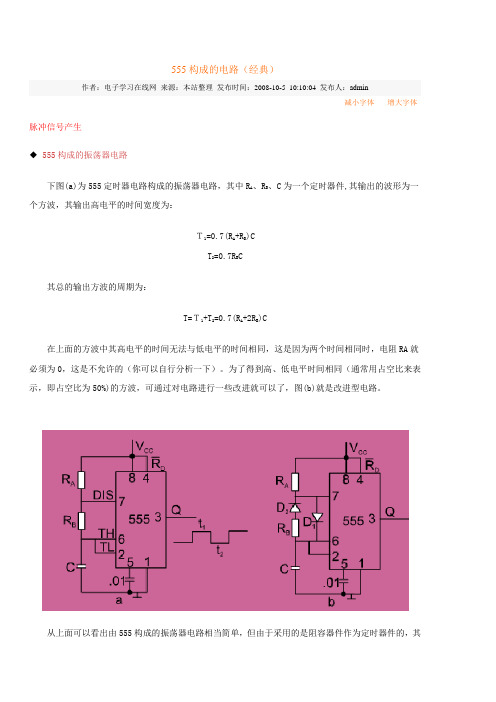

555构成的电路(经典)作者:电子学习在线网来源:本站整理发布时间:2008-10-5 10:10:04 发布人:admin减小字体增大字体脉冲信号产生◆555构成的振荡器电路下图(a)为555定时器电路构成的振荡器电路,其中R A、R B、C为一个定时器件,其输出的波形为一个方波,其输出高电平的时间宽度为:T1=0.7(R A+R B)CT2=0.7R B C其总的输出方波的周期为:T=T1+T2=0.7(R A+2R B)C在上面的方波中其高电平的时间无法与低电平的时间相同,这是因为两个时间相同时,电阻RA就必须为0,这是不允许的(你可以自行分析一下)。

为了得到高、低电平时间相同(通常用占空比来表示,即占空比为50%)的方波,可通过对电路进行一些改进就可以了,图(b)就是改进型电路。

从上面可以看出由555构成的振荡器电路相当简单,但由于采用的是阻容器件作为定时器件的,其频率的稳定性不高,一般仅能用于报警器电路或频率稳定性要求不高的场合。

为了得到更高的频率稳定的性一般采用石英晶体振荡器电路。

◆CMOS石英晶体振荡器电路石英晶体一种具有较高频率稳定性的选频器件,广泛用于通信、定时等频率要求高的场合,下图(a)为石英晶体的符号用频率特性曲线,从特性曲线可以看出其具有较高的品质因素。

图(b)为CMOS石英晶体振荡器的典型电路,第一个非门与晶体、电阻、电容构成振荡电路,其输出接近为一个正弦波,第二个CMOS非门起到一个整形作用,将非方波整形为一个理想的方波。

在这里须强调的是,通常人们将晶体与晶振两个名词混淆,其实这是两个完全不同的两个东西,晶体是一个器件,通常为扁平封装或圆柱形金属封装的两脚踏实地器件,而晶振是一个电路,如上面的电路就是晶振,在电子器件商店也有一种四脚封装的晶振电路,其四个脚分别为:电源、地线、输出、空脚。

在使用和采购时一定要注意这两个的区别,否则会闹出笑话。

单稳态电路单稳态电路的特点在前面的触发器电路中,当输入时钟有效边沿时输出发生变化,这时输入无论如何变化,其输出保持稳定,其输出状态既可以是0,也可以是1,这种电路有两个稳定的状态,故将触发器电路又可称为双稳态触发器电路。

d触发器5分频电路代代码

d触发器5分频电路代代码d触发器5分频电路代代码d触发器5分频电路是一种常用的电子电路,可以将输入信号进行分频,常用于计数器等电路中。

下面是d触发器5分频电路的代代码:```C++void setup() {pinMode(2, INPUT);pinMode(4, OUTPUT);}void loop() {boolean state = digitalRead(2);if(state == HIGH) {digitalWrite(4, HIGH);delayMicroseconds(10);digitalWrite(4, LOW);delayMicroseconds(10);}else {digitalWrite(4, LOW);}}```此代码实现了d触发器5分频电路的功能,将输入信号分成5部分,输出到4号引脚上。

接下来,我们将针对代码进行详细解释。

代码分析首先,在setup函数中,将2号引脚设置为输入,4号引脚设置为输出:```C++pinMode(2, INPUT);pinMode(4, OUTPUT);```在loop函数中,首先读取2号引脚的输入信号:```C++boolean state = digitalRead(2);```然后,判断输入信号是否为HIGH:```C++if(state == HIGH) {// do something}else {// do something}```如果输入信号为HIGH,即代表输入信号发生了变化,需要进行分频操作。

接下来,通过digitalWrite函数控制4号引脚输出HIGH信号10微秒,然后再控制4号引脚输出LOW信号10微秒:```C++digitalWrite(4, HIGH);delayMicroseconds(10);digitalWrite(4, LOW);delayMicroseconds(10);```这个过程将重复5次,即实现了d触发器5分频的功能。

数字电子技术基础(第五版)第五章触发器PPT课件

增加一个下降沿检测电路。

边沿触发器的特点

边沿触发器只在时钟信号的边沿 时刻改变状态,具有较高的抗干 扰能力和稳定性。同时,边沿触 发器可以实现多个触发器的级联

和同步操作。

06

集成触发器及其应用

集成触发器类型与特点

波形分析

在波形图中,可以观察到输入信号J、K以及输出信号Q、Q' 的波形变化。通过对比输入信号和输出信号的波形,可以验 证触发器的逻辑功能是否正确实现。

T触发器实现方法

T触发器定义

T触发器是一种特殊类型的触发器,其输入信号为T,输出信号为Q和Q'。当T=1时,触 发器翻转;当T=0时,触发器保持原状态不变。

和时钟信号CP接入芯片对应的引脚即可。

03

可编程逻辑器件实现

利用可编程逻辑器件(如FPGA、CPLD等)实现D触发器的功能。通过

编程配置逻辑器件的内部逻辑单元,实现D触发器的逻辑功能。

04

JK触发器和T触发器

JK触发器电路结构

基本结构

由两个可控RS触发器构成,输入信号为J和K,输出信号为 Q和Q'。

功能表

列出输入信号S、R与输出信号Q、Q'之间关系的表格,用于描述触发器的逻辑功能。功能表中应包含所有可能的 输入组合及对应的输出状态。

03

同步RS触发器及D触发器

同步RS触发器电路结构

1 2 3

基本RS触发器

由两个与非门交叉耦合构成,具有置0、置1和保 持功能。

同步RS触发器

在基本RS触发器的基础上,引入时钟信号CP, 使得触发器的状态只在CP的上升沿或下降沿发生 改变。

chp5-4_流水线1详解

促使计算机性能提高的因素除了器件性能得提 高外还有哪些呢??

6

5.7 流水CPU

5.7.1并行处理技术 5.7.2流水CPU的结构 5.7.3流水线中的主要问题 5.7.4 Pentium CPU

7

5.7.1并行处理技术

并行性(Parrelism)概念

问题中具有可以同时进行运算或操作的特性 例:在相同时延的条件下,用n位运算器进行n位 并行运算速度几乎是一位运算器进行n位串行运算 的n倍(狭义)

13

5.7.2流水CPU的结构

•具有两条以上的指令流水线 •上图中流水线满载时,每一个时钟周期可以执行2条指令 •采用时间和空间并行技术

14

5.7.2流水CPU的结构

流水线(Pipelining)的分类

按级别分为

指令流水线

算术流水线

处理机流水线(宏流水线)

15

5.7.3流水线中的主要问题

写回后清0该指令的所有目的寄存器源寄存器在向量位中对应的位都为0否则等待这些位清除3358risccpufifo队列称为历史缓冲器每当一条指令发射后副本传入fifo队列队尾执行完毕后离开队列3458risccpu如果采用延迟转移选项则转移指令后的转移延迟时间内指令被发射是一个32位的全相联cache用来保存转移路径的前两条指令3558risccpu超标量流水线结构如下3658risccpui1ldar1i2addr2r1i3addr3r4i4mulr4r5i5ldar6i6mulr6r7画出按序完成流水线时空图rawwarwaw3758risccpui63858risccpu3959cpu指利用计算机来综合集成地处理文字图形图象声音视频动画等媒体从而形成的一种全新的信息传播和处理的计算机技术

chp8-触发器

Software and Engineering Collage of HDU

6

Email: tuliming@

Copyright@ Atu

Course Name:Principles and Design of Database

Inserted 和 Deleted介绍

触发器语句中使用了两个特殊的表:Inserted和 Deleted,它们由系统自动创建和管理.可以使用这 两个临时的驻留内存的表测试某些数据修改的效果 及设置触发器操作的条件;但不能直接对表中的数 据进行更改.

Copyright@ Atu

Course Name:Principles and Design of Database

第8章 触发器

Atu

Software and Engineering Collage of HDU

1

Email: tuliming@

Copyright@ Atu

CREATE TRIGGER Category_Delete 3 3 0 ON Categories 执行触发器动作 FOR DELETE 4 0 AS UPDATE P SET Discontinued = 1 FROM Products AS P INNER JOIN deleted AS d ON 日志记录 P.CategoryID = 语句 d.CategoryID 日志记录DELETE语句

Course Name:Principles and Design of Database

主要内容

触发器概述 创建触发器 Inserted表和deleted表 使用触发器 修改,删除触发器

Software and Engineering Collage of HDU