[计算机硬件技术基础][机械工业出版社]第8章_中断技术习题答案(2021整理)

《计算机硬件技术基础》课程期末考试试卷和答案

《计算机硬件技术基础》课程期末考试试卷 A一、填空题(每空1分,共40分)1、中央处理单元包括运算器和控制器,是计算机的核心部分。

2、微型计算机中的总线包括数据总线、地址总线和控制总线三类。

3、Intel 80386微处理器是32位CPU,寻址空间达232(或者4G)。

4、设置高速缓存的目的是解决CPU的运算速度和内存的读写速度不平衡问题。

5、CPU的工作频率称为主频,系统总线的工作频率称之为外频。

6、EGA、VGA、SVGA标志着显示卡(或显卡)的不同规格和性能。

7、微型计算机的主存储器一般采用半导体存储器。

8、微机系统中的输入输出控制方式包括程序控制方式、中断控制方式、直接存储器存取方式(DMA)和输入输出处理机控制方式。

9、接口板通常由数据(缓冲)寄存器、设备状态寄存器、控制字寄存器、设备地址选择器和中断控制电路组成。

10、“当两个部件或设备同时请求向总线发送信息时,总线应按照预定的优先级将使用权交给其中一个,以免发生冲突”是指总线的控制功能。

11、用于静止图像压缩的国际标准为JPEG 标准。

12、数据压缩主要应用于传输和存储两个方面。

13、在Internet上的各种网络和各种不同类型的计算机相互通讯的基础协议是TCP/IP ,计算机之间文件传输使用的协议是FTP 。

14、万维网的网页是用HTML语言编写的,并在通信协议HTTP的支持下工作。

15、无线网络的传输技术可分为光波传输和无线电波传输两类。

16、“迅驰”移动计算技术不是单纯代表CPU,它是三种组件实现共同协作,包括了Intel Pentium-M处理器、Intel 855芯片组系列和Intel Pro/无线2100网络连接。

17、以太网是采用总线结构的一种局域网。

在以太网中,所有的结点(计算机或其他设备)通过以太网卡和电缆连接到一条总线上,并采用CSMA/CD 方式进行相互间的数据通信。

18、微型计算机每个指令周期可分为取址周期和执行周期。

计算机硬件基础课后习题答案

第1章计算机概述1:计算机的类型有哪些?简述它们的特点目前国际上比较流行的计算机分类是:巨型计算机、主机(大、中型机)、小型计算机、和个人计算机。

巨型计算机指运算速度快、存储容量大的高性能计算机,它采用了大规模并行处理的体系结构,CPU由数以百计、千计的处理器组成,有极强的运算处理能力。

计算机的运算速度平均每秒1000万次以上;存贮容量在1000万位以上。

巨型机的研制水平是一个国家计算机技术水平的重要标志。

主机(大、中型机)大型机的运算速度一般在100万次/秒至几千万次/秒,通常用每秒运行多少万次来作为运算速度单位,字长32~64位,主存容量在几百兆字节以上,。

它有比较完善的指令系统,丰富的外部设备和功能齐全的软件系统。

其特点是通用,有极强的综合处理能力。

中型机的规模介于大型机和小型机之间。

小型机的机器规模小、结构简单、设计试制周期短,便于及时采用先进工艺技术,软件开发成本低,易于操作维护。

微型计算机是以微处理器(CPU)为核心,通过系统总线(BUS)将存储器、外围控制电路、输入输出接口连接起来的系统称为微型计算机。

若配有相应的外围设备(如显示器、键盘、打印机等)和系统软件,就组成了微型计算机系统(Micro Computer System)。

微型计算机具有以下特点:◆集成度高,体积小,重量轻,价格低廉;◆部件标准化,易于组装及维修;◆高可靠性及适应性。

2:微型计算机简单分哪几类?各有什么特点?微型计算机简单可分为常见的台式微型计算机即个人计算机PC,笔记本,及掌上电脑台式机具有:集成度高、体积较小价格低廉、部件标准化、,易于组装维修、高可靠性及适应性,计算能力强等特点;笔记本具有体积小重量轻,便于携带移动性强,耗电少功能强的特点;掌上电脑具有更小的体积、更轻的重量、更少的耗电和更强的可移动性的特点,其方便的上网功能正将加速“处处计算,移动计算”的时代到来。

;Flash存储器与RAM相比具有非易失性的优势,但是寿命短,可擦写次数少,读写速度慢,且不能完成完全随机读写。

(完整版)计算机硬件技术基础习题答案(太原理工)

(完整版)计算机硬件技术基础习题答案(太原理⼯)计算机硬件技术基础习题答案习题⼀:1-8: 28 Bytes = 256 Bytes;216 Bytes = 210×26Bytes = 64KB;220 Bytes = 210×210Bytes = 1MB;232 Bytes = 210×210×210×22 Bytes = 4GB 。

1-12:指令通常包括操作码和操作数两部分。

操作码表⽰计算机执⾏什么具体操作;操作数表⽰参加操作的数的本⾝或操作数所在的地址(操作数的地址码)。

1-22:[+89]补= 0 101 1001B;[-89]补= 1 010 0111B;[+67]补= 0 100 0011B;[-67]补= 1 011 1101B。

(1)[-89]补+ [+67]补= 10100111B + 01000011B= 1 110 1010B = eaHV = D7C D6C=00=0 ⽆溢出D7C = 0; D6C = 0(2)[+89]补+ [-(-67)]补= [+89]补+ [+67]补=01011001B + 01000011B= 1 001 1100B = 9cHV = D7C D6C=01=1溢出D7C = 0; D6C = 1(3)[-89]补+ [-67]补= 10100111B + 10111101B= 1, 0 110 0100B = 64HV = D7C D6C=10=1溢出D7C = 1; D6C = 0(4)[-89]补+ [-(-67)]补= [-89]补+ [+67]补=10100111B + 01000011B= 1 110 1010B = eaHV = D7C D6C=00=0 ⽆溢出D7C = 0; D6C = 01-30:(1) 01111001 + 01110000补码竖式:01111001+ 01110000———————11101001V = D7C D6C=01=1 溢出;两正数相加,其结果应为正数;但结果为负数,故产⽣了溢出,正溢出。

计算机硬件基础课后答案

2-18(1)1278H+3469H=0001 0010 0111 1000+0011 0100 0110 1001=0100 0110 1110 0001SF=0 ZF=0 AF=1 PF=1 CF=0 OF=0(2)54E3H-27A0H=0101 0100 1110 0011+1101 1000 0110 0000=1 0010 1101 0100 0011SF=0 ZF=0 AF=0PF=0 CF=0 OF=0当进行16位或8位加或减运算时,若最高位产生进位或借位时,将CF置1,否则为0,当进行带符号数补码运算时,运算结果超出了机器所能表示的数值范围,就产生溢出,将OF置1,否则OF置0,即OF用来表示有符号数运算的溢出,而CF则用来表示无符号数运算的溢出。

2-24答:存储慢速设备(存储器或I/O设备)的数据时,必须插入等待周期T W来延长总线周期,插入T W多少取决于CPU完成独立操作所需时间。

2-26读存储器写存储器4-5DATASEG SEGMENTMY1B DB ‘PERSONAL COMPUTER’MY2B DB 20MY3B DB 14HMY4B DB 00010100BMY5W DW 20 DUP(?)MY6W EQU 100DATASEG ENDS4-6(1) BX = (2);(2) AL = (2);(3) CX = (10);(4) DL = (10).4-7(1) V AR1、V AR2、V AR3的偏移地址是30H,3AH,40H;(2) DATA1的值是50H,CNT的值是16;(3) V AR2+2的内容为2。

4-8(2)X为字变量,Y则可以字节方式访问X;(4)X为字变量,初值放在内存中的顺序为88H和62H,Y为字节变量,初值依次为62H和88H;(5)X和Y均为字变量,初值不同,因为X为16进制数,Y为10进制数。

4-9(1)源操作数1000超过字节范围(3)CMP的两个操作数不能同时为存储器操作数(5)JNZ的转移位置不能用字变量给出4-11(1) DATA1 DB 86H, 27H, 23H, 00H, 24H, 1AH(2) DATA2 DW 0B430H, 1062H或者(1)DATA1 LABEL BYTEARRAY DW 2786H,23H,1A24H(2) DATA2 LABEL WORDARRAY DB 30H,0B4H,62H,10H4-12DATA SEGMENT WORDTABLE DB 100 DUP(0)DATA ENDSSTACK SEGMENT WORD STACK ‘STACK’DB 1024 DUP(0)STACK ENDSCODE SEGMENT ‘CODE’ASSUME DS:DATA,SS:STACK, CS:CODEMAIN PROC FARSTART: PUSH DSMOV AX, 0PUSH AXMOV AX, DATAMOV DS, AXMOV ES, AXLEA BX, TABLEMOV CX, 100LOP: MOV BYTE PTR [BX], 64HINC BXLOOP LOPRETMAIN ENDPCODE ENDSEND START4-15TRAN MACRO X, Y, Z ;X, Y, Z为源、目标数据块的首地址,Z为数据块的长度MOV CX, ZMOV SI, OFFSET XMOV DI, OFFSET YCLDREP MOVSBENDM4-16MOV AX, WORD PTR XADD AX, WORD PTR YMOV WORD PTR Z, AXMOV AX, WORD PTR X+2ADC AX, WORD PTR Y+2MOV WORD PTR Z+2, AX4-17DATA SEGMENTSTRG DB 1000 DUP(?)STR1 EQU STRG+7STG2 EQU STRG+27STRSE EQU 50DATA ENDSSTACK SEGMENT PARA STACK ‘STACK’DB 100 DUP(?)STACK ENDSCODE SEGMENTASSUME CS:CODE, DS:DATA, ES:DATA MAIN: MOV AX, DATAMOV DS, AXMOV ES, AXMOV CX, STRSEMOV SI, OFFSET STG1MOV DI, OFFSET STG2CLDPUSH SIADD SI, STRSE-1CMP SI, DIPOP SIJL OKSTDADD SI, STRSE-1ADD DI, STRSE-1OK: REP MOVSBMOV AX, 4C00HINT 21HCODE ENDSEND MAIN4-18(1)DATA SEGMENTDATA ENDSCODE SEGMENT…MOV AH, 01H ; 从键盘输入一个字符,其ASC码值在AL中INT 21HCMP AL, 41HJZ P0CMP AL, 42HJZ P1…CMP AL, 4AHJZ P9JMP EXITP1: …RETP2: …RET……P9: …RETEXIT: MOV AH, 4CHINT 21H….(2)DATA SEGMENTBASE DW P0, P1, ……,P9DATA ENDSCODE SEGMENT…MOV AH, 01H ; 从键盘输入一个字符,其ASC码值在AL中INT 21HCMP AL, 'A' ; 判别字符是否位于‘A’到‘J’之间JB EXITCMP AL, 'J'JA EXITSUB AL, 'A' ;在正确范围之内,根据表内地址分支MOV BL, ALMOV BH, 0SHL BX, 1JMP BASE[BX]P1: …RETP2: …RET……P9: …RETEXIT: MOV AH, 4CHINT 21H….4-19LEA BX, xLEA SI, yLEA DI, sumADD BX, 7ADD SI, 7ADD DI, 8 ;和可能要9个字节MOV CX, 8CLCLOP: MOV AL, [BX]ADC AL, [SI]DAAMOV [DI], ALDEC BXDEC SIDEC DIDEC CXJNZ LOPMOV AL, 0ADC AL, 0MOV [DI], AL4-20MOV SI, OFFSET FIRSTMOV CX, 0 ;CX中存放A的个数LOOP: MOV AL, [SI]CMP AL, ‘$’JZ NEXTCMP AL, ‘A’JNE LPINC CXLP: INC SIJMP LOOPNEXT: ……4-21DATA SEGMENTDATA_W DW …………;若干个数COUT EQU ($-DATA_W)/2COUT1 DB 0COUT2 DB 0COUT3 DB 0DATA ENDSSTACK SEGMENT PARA STACK ‘STACK’DB 100 DUP(0)STACK ENDSCODE SEGMENTASSAUM CS:CODE,DS:DATASTART PROC FARPUSH DSMOV AX, 0PUSH AXMOV AX, DATAMOV DS, AXMOV DX, 0 ;正数、负数、0暂时分别存在BL、BH、DL 中MOV BX, 0LEA SI, DATA_WMOV CX, COUTNEXT: MOV AX, [SI]CMP AX, 0JG LP1JL LP2INC DLJMP OKLP1: INC BLJMP OKLP2: INC BHOK: ADD SI, 2LOOP NEXTMOV COUNT1,BLMOV COUNT2,BHMOV COUNT3,DLRETSTART ENDPCODE ENDSEND START4-22DATA SEGMENTARRAY D B …………;若干个数COUT EQU $-ARRAYMAX DB ?MIN DB ?DATA ENDSSTACK SEGMENT PARA STACK ‘STACK’DB 100 DUP(0)STACK ENDSCODE SEGMENTASSAUM CS:CODE,DS:DATASTART PROC FARPUSH DSMOV AX, 0PUSH AXMOV AX, DATAMOV DS, AXLEA BX, ARRAYMOV CX, COUTGOT: MOV AL, [BX]TEST AL, 01HJZ NEXTINC BXJMP GOTNEXT: MOV DH, ALMOV DL, AL ;DH暂存最大偶数,DL暂存最小偶数,初始置首个偶数LEA BX, ARRAYLOP: MOV AL, [BX]TEST AL, 01HJNZ NEXT2CMP AL, DLJA NEXT1MOV DL, ALJMP NEXT2NEXT1: C MP AL, DHJB NEXT2MOV DH, ALNEXT2: I NC BXLOOP LOPMOV MAX, DHMOV MIN, DLRETSTART ENDPCODE ENDSEND START4-24LEA BX, STRINGMOV CX, 80 NEXT: MOV AL, [BX]CMP AL, 20HJZ OKINC BXLOOP NEXTMOV CL, -1JMP FINOK: NEG CXADD CX, 80FIN: …………4-25LEA BX, STRINGMOV CH, 0LOP: MOV AL, [BX]CMP AL, ODHJZ EXITINC CHINC BXJMP LOPEXIT: …4-26(1)LEA SI,STRING1LEA DI,STRING2MOV C X,20CLDREP MOVSB(2)LEA SI,STRING1LEA DI,STRING2ADD SI,19ADD DI,19MOV C X,20STDREP MOVSB(3)MOV A L,20HLEA DI, STRING1MOV C X,20CLDREPNZ SCASBJZ FOUNDMOV D L,0 ;未找到FOUND:DEC DIMOV BX,DIMOV DL,01H ;找到(4)LEA SI,STRING1LEA DI,STRING2MOV C X,20CLDREP CMPSBJNZ NEQMOV B L,0 ;相同NEQ: M OV BL,01H ;不相同4-28(1) DISPLAY PROCMOV CH, 4MOV CL, 4MOV BX, AX ;(*)NEXT: ROL BX, CLMOV DL, BLAND DL, 0FHADD DL, 30HCMP DL, 39HJBE PRINTADD DL, 07HPRINT: MOV AH, 2INT 21HDEC CHJNZ NEXTRETDISPLAY ENDP(2) 与(1)基本相同,仅将(*)语句修改为MOV BX, WORDTEMP(3) 将(*)句替换为下列语句(假设子程序中并未保护现场寄存器,主程序入栈的参数就是预显示的数据)MOV BP, SPMOV BX, [BP+2]4-29;模块1,文件名MAIN.ASMEXTRN DISPLAY: FAR ;引用外部符号PUBLIC MESG ;定义外部符号DATA1 SEGMENTMESG DB 'ASSEMBLER$'DATA1 ENDSCODE1 SEGMENTASSUME CS: CODE1, D S: DATA1MAIN: MOV AX, DATA1MOV DS, AX ;装入段基址PUSH DSCALL DISPLAYMV AH, 4CHINT 21HCODE1 ENDSEND MAIN;模块2,文件名DISPLAY.ASMEXTRN MESGPUBLIC DISPLAY ;定义外部符号DATA2 SEGMENTDB 100UP(?)DATA2 ENDSCODE2 SEGMENTASSUME CS: CODE2, DS: DATA2DISPLAY PROC FARMOV AX, DATA2MOV DS, AX ;装入段基址MOV DX, OFFSET MESGMOV AH, 9 ;屏幕显示INT 21HRETDISPLAY ENDPCODE2 ENDS4-30SUM1 PROC NEARCMP CX,0JZ EXIT1MOV AX,0 ;数组和在AX中AGAIN:ADD AL,[SI]ADC AH,0 ;和或许为字INC SILOOP AGAINEXIT1:RETSUM1 ENDP4-31STACK SEGMENT PARA STACK ‘STACK’DB 100 DUP (0)STACK ENDSCODE SEGMENTASSAUM CS: CODESTART PROC FARPUSH DSMOV AX, 0PUSH AXMOV AX, DATAMOV DS, AXMOV CX, 4MOV DX, 0.LOP1: MOV AH, 1INT 21HCMP AL, 46HJA EXIT ;字符ASCII码不在0~9,A~F之间CMP AL, 40HJA LOP2CMP AL, 39HJA EXIT ;字符ASCII码不在0~9,A~F之间CMP AL, 30HJB EXIT ;字符ASCII码不在0~9,A~F之间SUB AL, 30HJMP NEXTLOP2: SUB AL, 37HNEXT: MOV AH, 0PUSH CXMOV CL, 4ROL DX, CLPOP CXADD DX, AXLOOP LOP1EXIT: RETSTART ENDPCODE ENDSEND START5-41K X 8 : 末地址=1000H+3FFH=13FFH 2K X 8 : 末地址=1000H+7FFH=17FFH 4K X 8 : 末地址=1000H+FFFH=1FFFH 8K X 8 : 末地址=1000H+1FFFH=2FFFH 5-5所占地址空间为:20000H~27FFFH5-61# 8000H~87FFH2# 8800H~8FFFH3# 9000H~97FFH4# A000H~A3FFH5# A400H~A7FFH6# A800H~ABFFH7# AC00H~AFFFH5-76-1IN AL, PORT_TCMP AL, 0FEH ;k0单独被按下,即最低位为0,其余位为高JZ NEXT1CMP AL, 0FDH ;JZ NEXT2MOV AL, 00H ;其他的情况,将灯全部不点亮OUT PORT_T, ALJMP EXITNEXT1: M OV AL, 01H ;K0被按下,LED0~LED7顺次点亮,送1则对应的灯亮MOV CX, 8LOOP1: OUT PORT_T, ALCALL DELAYROL AL, 1LOOP LOOP1JMP EXITNEXT2: M OV AL, 80H ;K1被按下,LED0~LED7反序点亮,送1则对应的灯亮MOV CX, 8LOOP2: OUT PORT_T, ALCALL DELAYROR AL, 1LOOP LOOP2EXIT: ….6-2 解:MOV CX,100MOV BX,OFFSET DATASIN-TEST:IN AL,STATUSTEST AL,80HJZ IN-TESTIN AL,DATAS_PORTMOV [BX],ALINC BXLOOP IN-TEST6-3 解:MOV BX,OFFSET STRINGWAIT:IN AL,STATUSAND A L,80HJNZ WAITMOV AL, [BX]OUT DATAS,ALCMP AL,0DHJZ ENDINC BXJMP WAITEND:……6-6执行INT 8后CPU将PSW, IP, CS压入堆栈,堆栈的情况如下图:SP 00FAH00FBH00FCH00FDH00FEH00FFHSP=00FAH, SS=0300H, IP=0040H, CS=0100H因为IF,.TF进入中断后自动为零,所以PSW=0040H.6-9IRQ3申请中断,IRQ3正在被服务,20H, 05H6-12MOV DX, 0FFDCHMOV AL, 00010011B ;ICW1OUT DX, ALMOV DX, 0FFDDHMOV AL, 90H ;ICW2OUT DX, ALMOV AL, 00000001B ;ICW4OUT DX, AL6-17RRREG DB ?SRREG DB ?IMREG DB ?…MOV AL, 00001010B ;读IRROUT 20H, ALIN AL, 20HMOV RRREG, ALMOV AL, 00001011B ;读ISROUT 20H, ALIN AL, 20HMOV SRREG, ALIN AL, 21H ;读IMRMOV IMREG, AL7-9①8255初始化:C口工作在工作方式0,其中C口上半部输入,C口下半部输出,于是8255控制字应为00001000B,即08H;设控制口地址为CTRL,C口地址为PORTC,则8255初始化程序如下:MOV AL, 08HMOV DX, CTRLOUT DX, AL②中断服务程序:设有一延时子程序名为DELAY,则中断服务子程序为:ALARM PROC FARPUSH AX ;现场保护PUSH DXMOV DX, PORTC ;查询PC7确认微导线状态IN AL, DXTEST AL, 80H ;JZ EXIT ;如PC7为0表示微导线未断,退出服务程序MOV DX, CTRL ;通过写控制口,达到单独设置PC0的输出值的目的MOV AL, 10000000BLP: OUT DX, ALCALL DELAY ;调用延时程序,使PC0按指定频率输出脉冲XOR AL, 00000001B ;采用异或指令实现最后一位取反,而其他位不变的目的JMP LPPOP DX ;现场恢复POP AXIRETENDP7-11MOV AL, 00000010B ;8255初始化,A口输出,B口输入,均工作在工作方式0MOV DX, 3C3HMOV DX, 3C0H ;使A口的初始输出为全1,即使继电器线圈无电流OUT DX, ALMOV AL, 0FFHLP: MOV DX, 3C1HIN AL, DXNOT ALMOV DX, 3C0HOUT DX, ALCALL DELAY ;调用延时程序JMP LP。

《计算机硬件技术基础》题集

《计算机硬件技术基础》题集一、选择题(每题2分,共20分)1.下列哪一项不是计算机硬件系统的基本组成部分?A. 运算器B. 控制器C. 存储器D. 操作系统2.下列关于CPU的描述中,哪一项是错误的?A. CPU是计算机的核心部件,负责执行程序指令。

B. CPU的性能直接决定了计算机的运行速度。

C. CPU主要由运算器和控制器组成。

D. CPU的位数是指它能够同时处理的二进制数的位数,目前常见的有32位和64位。

3.下列哪种存储器属于外部存储器?A. RAMB. ROMC. 硬盘D. 缓存4.下列哪种接口是目前主流计算机上常用的串行通信接口?A. PS/2B. USBC. VGA5.下列哪一项不是计算机总线的主要类型?A. 数据总线B. 地址总线C. 控制总线D. 电源总线6.下列关于BIOS的描述中,哪一项是正确的?A. BIOS是计算机启动时加载的第一个软件。

B. BIOS存储在计算机的内存中。

C. BIOS的主要功能是进行系统资源管理。

D. BIOS可以通过软件升级。

7.下列哪种类型的显示器是目前市场上主流的显示器?A. CRT显示器B. LCD显示器C. LED显示器D. PDP显示器8.下列关于计算机电源的描述中,哪一项是错误的?A. ATX电源是目前主流的计算机电源标准。

B. 计算机电源的主要功能是将交流电转换为直流电。

C. 电源的功率越大,计算机的性能就越好。

D. 电源的+12V输出主要用于为硬盘和光驱等设备供电。

9.下列哪一项不是衡量硬盘性能的主要指标?B. 转速C. 缓存大小D. 接口类型10.下列关于计算机主板的描述中,哪一项是错误的?A. 主板是计算机各种硬件设备的连接载体。

B. 主板上的芯片组决定了主板的主要性能。

C. 主板上的BIOS芯片用于存储计算机的基本输入输出程序。

D. 主板上的CMOS芯片用于存储计算机的系统时间、日期等信息,断电后信息会丢失。

二、填空题(每题2分,共20分)1.计算机硬件系统主要由______、、、输入设备和输出设备五大部分组成。

微机原理与接口技术课后第八章习题答案

第8章中断系统与可编程中断控制器8259A1.什么叫中断?8086微机系统中有哪几种不同类型的中断?答:在CPU执行程序的过程中,由于某个事件的发生,CPU暂停当前正在执行的程序,转去执行处理该事件的一个中断服务程序,待中断服务程序执行完成后,CPU再返回到原被中断的程序继续执行。

这个过程称为中断。

8086微机系统中有3种中断:1)外部可屏蔽中断。

2)外部不可屏蔽中断。

3)内部中断2.什么是中断类型?它有什么用处?答:通常用若干位二进制编码来给中断源编号,该编号称为中断类型号。

8086微处理器用8位二进制码表示一个中断类型,有256个不同的中断。

这些中断可以划分为内部中断、外部不可屏蔽中断、外部可屏蔽中断三类。

用处:使CPU识别中断源,从而能正确地转向该中断源对应的中断服务程序入口。

3.什么是中断嵌套?使用中断嵌套有什么好处?对于可屏蔽中断,实现中断嵌套的条件是什么?答:微处理器在处理低级别中断的过程中,如果出现了级别高的中断请求,微处理器停止执行低级中断的处理程序而去优先处理高级中断,等高级中断处理完毕后,再接着执行低级的未处理完的程序,这种中断处理方式成为中断嵌套。

使用中断嵌套的好处是能够提高中断响应的实时性。

对于某些对实时性要求较高的操作,必须赋予较高的优先级和采取中断嵌套的方式,才能保证系统能够及时响应该中断请求。

对于可屏蔽中断,实现中断嵌套的条件有:(1)微处理器处于中断允许状态(IF=1)(2)中断请求的优先级高于正在执行的中断处理程序的优先级。

(3)中断请求未被8259屏蔽。

(4)没有不可屏蔽中断请求和总线请求。

4.什么是中断向量?中断类型号为1FH的中断向量为2345H:1234H,画图说明它在中断向量表中的存放位置。

答:中断向量为每个中断服务子程序的入口地址,为32位(16位的偏移地址和16位的段地址),在中断向量表中占用4个地址单元。

在8086CPU组成的计算机系统中,采用最低的1024个地址单元(称为0页)来存储中断向量。

专科《计算机硬件技术基础》_试卷_答案

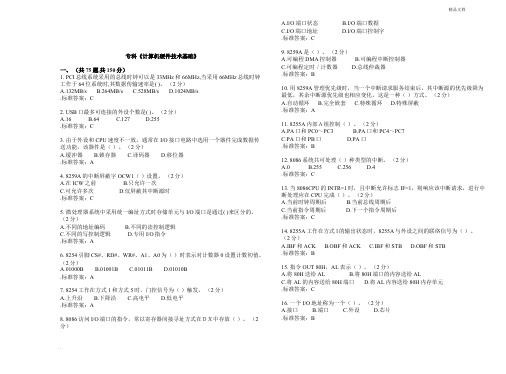

精品文档专科《计算机硬件技术基础》一、(共75题,共150分)1. PCI总线系统采用的总线时钟可以是33MHz和66MHz,当采用66MHz总线时钟工作于64位系统时,其数据传输速率是( )。

(2分)A.132MB/sB.264MB/sC.528MB/sD.1024MB/s.标准答案:C2. USB口最多可连接的外设个数是( )。

(2分)A.16B.64C.127D.255.标准答案:C3. 由于外设和CPU速度不一致,通常在I/O接口电路中选用一个器件完成数据传送功能,该器件是()。

(2分)A.缓冲器B.锁存器C.译码器D.移位器.标准答案:A4. 8259A的中断屏蔽字OCW1()设置。

(2分)A.在ICW之前B.只允许一次C.可允许多次D.仅屏蔽其中断源时.标准答案:C5. 微处理器系统中采用统一编址方式时存储单元与I/O端口是通过( )来区分的。

(2分)A.不同的地址编码B.不同的读控制逻辑C.不同的写控制逻辑D.专用I/O指令.标准答案:A6. 8254引脚CS#、RD#、WR#、A1、A0为()时表示对计数器0设置计数初值。

(2分)A.01000BB.01001BC.01011BD.01010B.标准答案:A7. 8254工作在方式1和方式5时,门控信号为()触发。

(2分)A.上升沿B.下降沿C.高电平D.低电平.标准答案:A8. 8086访问I/O端口的指令,常以寄存器间接寻址方式在DX中存放()。

(2分)A.I/O端口状态 B.I/O端口数据C.I/O端口地址D.I/O端口控制字.标准答案:C9. 8259A是()。

(2分)A.可编程DMA控制器B.可编程中断控制器C.可编程定时/计数器D.总线仲裁器.标准答案:B10. 用8259A管理优先级时,当一个中断请求服务结束后,其中断源的优先级降为最低,其余中断源优先级也相应变化,这是一种()方式。

(2分)A.自动循环B.完全嵌套C.特殊循环D.特殊屏蔽.标准答案:A11. 8255A内部A组控制()。

《计算机硬件技术基础》试题(A)答案

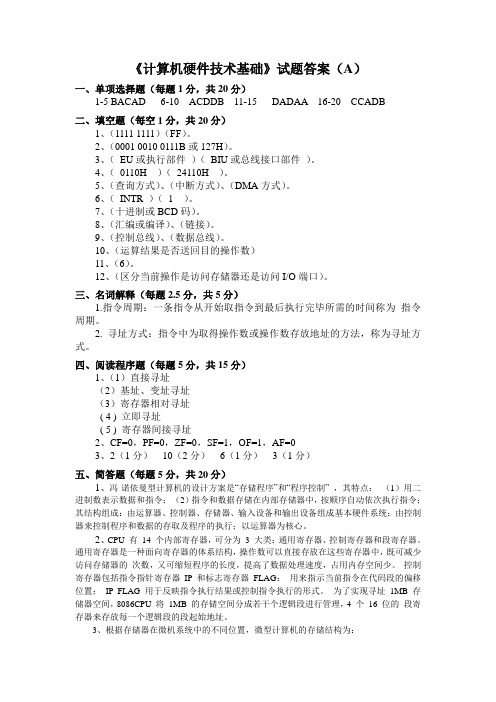

《计算机硬件技术基础》试题答案(A)一、单项选择题(每题1分,共20分)1-5 BACAD 6-10 ACDDB 11-15 DADAA 16-20 CCADB二、填空题(每空1分,共20分)1、(1111 1111)(FF)。

2、(0001 0010 0111B或127H)。

3、(EU或执行部件)(BIU或总线接口部件)。

4、(0110H )(24110H )。

5、(查询方式)、(中断方式)、(DMA方式)。

6、(INTR )(1 )。

7、(十进制或BCD码)。

8、(汇编或编译)、(链接)。

9、(控制总线)、(数据总线)。

10、(运算结果是否送回目的操作数)11、(6)。

12、(区分当前操作是访问存储器还是访问I/O端口)。

三、名词解释(每题2.5分,共5分)1.指令周期:一条指令从开始取指令到最后执行完毕所需的时间称为指令周期。

2. 寻址方式:指令中为取得操作数或操作数存放地址的方法,称为寻址方式。

四、阅读程序题(每题5分,共15分)1、(1)直接寻址(2)基址、变址寻址(3)寄存器相对寻址( 4 )立即寻址( 5 ) 寄存器间接寻址2、CF=0,PF=0,ZF=0,SF=1,OF=1,AF=03、2(1分)10(2分)6(1分)3(1分)五、简答题(每题5分,共20分)1、冯·诺依曼型计算机的设计方案是“存储程序”和“程序控制” ,其特点:(1)用二进制数表示数据和指令;(2)指令和数据存储在内部存储器中,按顺序自动依次执行指令;其结构组成:由运算器、控制器、存储器、输入设备和输出设备组成基本硬件系统;由控制器来控制程序和数据的存取及程序的执行;以运算器为核心。

2、CPU 有14 个内部寄存器,可分为3 大类:通用寄存器、控制寄存器和段寄存器。

通用寄存器是一种面向寄存器的体系结构,操作数可以直接存放在这些寄存器中,既可减少访问存储器的次数,又可缩短程序的长度,提高了数据处理速度,占用内存空间少。

《计算机硬件技术基础》试题及答案

《计算机硬件技术基础》试题及答案《计算机硬件技术基础》试题(A)一、选择题(每题1分,共15分)1.计算机硬件的核心部件是(A)。

(A)处理器 (B)运算器 (C)嵌入式微处理器 (D)控制器2.( D )的说法正确。

(A)字是计算机处理器处理数据的基本单位(B)字长是处理器一次能同时处理二进制数的位数,如16位、32位(C)以字长定义计算机的位数,如16位机、32位机、64位机(D)A、B、C3.( D )的说法正确。

(A)主频是处理器的工作频率(B)外频是向处理器提供的基准时钟的频率(C)外频是处理器与其他部件之间传送数据的T作频率(D)A、B、C4.( C )的说法错误。

(A)处理器是计算机的核心部件(B)处理器的发展促进计算机的发展(C)AMD64是32位处理器(D)处理器一次能处理的数据位数不断提高5.(A)是计算机各部件传输信息的通路(A)总线 (B)主板 (C)I/O设备 (D)存储器6.同一时刻(B)控制总线。

(A)只能有一个从部件 (B)只能有一个主部件(C)有多个主部件(D)只能有一个主部件和一个从部件7.(C)是串行外部总线。

(A)PCI (B)ISA (C)USB (D)AGP8.IEEEl394是一种(A)接口,称为数码影像设备的接口标准。

(A)串行 (B)并行 (C)A/D (D)D/A9.(D)是图形显示卡专用总线。

(A)ISA (B)EISA (C)PCI (1)AGP10.存储容量最大的是(D)。

(A)寄存器(B)高速缓存 (C)内存 (D)外存11.(B)的速度与处理器的速度匹配。

(A)寄存器 (B)高速缓存 (C)内存 (D)外存12.处理器与外设不能直接连接,通过(B)连接。

(A)桥粱 (B)接口 (C)端口 (D)缓冲器13.下列数据传送方式中效率最高的是(C)方式。

(A)IN/OUT (B)查询 (C)中断(D)串行14. A/D转换器用于(C)。

(A)十进制数转换成二进制数 (B)二进制数转换成十进制数(C)模拟信号转换成数字信号 (D)数字信号转换成模拟信号15.D/A转换器用于(D)。

计算机硬件习题答案

原14-18题目有问题,换了一个题目第7章7-1 8086/8088 CPU有哪几种中断?1)外设中断源。

一般有键盘、打印机、磁盘、磁带等,工作中要求CPU为它服务时,会向CPU 发送中断请求。

2)故障中断源。

当系统出现某些故障时(如存储器出错、运算溢出等),相关部件会向CPU发出中断请求,以便使CPU转去执行故障处理程序来解决故障。

3)软件中断源。

在程序中向CPU发出中断指令(8086为INT指令),可迫使CPU转去执行某个特定的中断服务程序,而中断服务程序执行完后,CPU又回到原程序中继续执行INT 指令后面的指令。

4)为调试而设置的中断源。

系统提供的单步中断和断点中断,可以使被调试程序在执行一条指令或执行到某个特定位置处时自动产生中断,从而便于程序员检查中间结果,寻找错误所在。

7-2 软件中断和硬件中断有何特点,如何区别?外部中断源即硬件中断源,来自CPU外部。

8086 CPU提供了两个引脚来接收外部中断源的中断请求信号:可屏蔽中断请求引脚和不可屏蔽中断请求引脚。

通过可屏蔽中断请求引脚输入的中断请求信号称作可屏蔽中断请求,对这种中断请求CPU可响应,也可不响应,具体取决于标志寄存器中IF标志位的状态。

通过不可屏蔽中断请求引脚输入的中断请求信号称作不可屏蔽中断请求,这种中断请求CPU必须响应。

软件中断执行软件中断指令时,会产生软件中断。

8086系统中,设置了三条中断指令,分别是:<1>中断指令INT n:用户可以用INT n指令来产生一个类型为n的中断,以便让CPU执行n号中断的中断服务程序。

<2>断点中断INT 3:执行断点指令INT 3,将引起类型为3的断点中断,这是调试程序专用的中断。

<3>溢出中断INTO:如果标志寄存器中溢出标志位OF为1,在执行了INTO指令后,产生类型为4的溢出中断。

7-3 中断排队方法有哪些方法?1.软件查询确定中断优先级。

计算机硬件基础——第八章(中断系统)

AJMP MAIN

AJMP IT0P MAIN: MOV SP,#60H MOV TMOD, #01H MOV TH0 ,#M

DJNZ R7,DD2

DJNZ R5,DD1 RET

MOV TL0,#N

SETB TR0 SETB EA SETB ET0 SJMP $

从上例可看出中断大大提高了CPU的工作效率。

中建立堆栈。 ②在中断服务程序的开始应有保护现场的指令。 即将中断服务程序中用到的各寄存器的内容压入堆栈保存,在中 断结束之前弹回恢复,然后返回。这样就能保证返回原断点时各

寄存器内容与中断服务前相同,使原程序能正确运行。

③中断与调用子程序的异同: 中断过程中由主程序转向中断服务程序的请求是由外部设备提出 的,发生中断的时刻不确定,而在何处调用子程序则是由程序确 定的。

3

一.8031的中断请求源

有5个中断源,它们是:串行口 T1 INT1 T0 INT0

TCON (88H)中相应的位锁存它们的中断标志:

TF1 其中:

TR1

TF0

TR0

IE1

IT1

IE0

IT0

IT0 :INT0触发方式选择,0:低电平触发,1:负跳变触发

IE0 :INT0选择负跳变触发时的中断标志,0:INT0未申请中断, 1:INT0申请中断 INT0选择低电平触发时此标志无用。 IT1、IE1同上定义对INT1控制。

10

例

8000H

MOV A, #06H

①

8002H

8005H

MOV B, #05H

MUL AB MOV IE , #05H MOV R0 , #30H …………….

②

8006H 8009H 800BH

计算机原理学习指导第八章-综合练习题参考答案

计算机原理学习指导第八章-综合练习题参考答案《计算机原理学习指导》第八章综合练习题参考答案一.填空题1.主机CPU和IOP之间的通信,原则上是通过共享__主存储器__来实现的.2.可以根据中断源在系统中的位置将中断源分为内部中断和外部中断,一般运算器除法错是__内部中断__,键盘输入要求中断是_外部中断___.3. 响应中断的必须满足3个条件:(1)中断源有中断请求(2)CPU处于开中断状态,而且没有更高优先级的中断请求存在(3)一条指令执行完毕.4.. 字节多路通道是一种简单的共享通道,它是建立在_时间分割___的基础上,轮流为多台低速和中速外设服务.选择通道数据的传送是以_成组(数据块)____方式进行,因此传送速率高.5. 多个中断源在软件查询方式中_优先级最高的___最先被访问.6. 根据数据传送方式,可以将通道分为__选择__通道,__字节多路__通道和数组多路通道.7. 一个中断向量对应一个__中断服务程序的入口地址__8. 中断处理过程可以嵌套,_优先级高___的设备可以中断__优先级低__的设备的中断服务程序.9. 中断请求的优先排队可以归纳为2大类,它们是__硬件判优__和__软件判优__.10.. DMA方式中,DMA控制器从CPU完全接管对_总线___的控制,数据交换不经过CPU,而之间在内存和_I/O设备___之间进行.11. 通道是一个特殊功能的处理器____,它有自己的_指令和程序___,专门负责数据输入输出的传送控制,CPU只负责_数据处理___功能.12. DMA的含义是_直接存储器访问___,用于解决__数据块高速传送__问题.二.单项选择题1..选择通道上可连接若干外围设备,其数据传送的单位是(D ).A.字节B.字C.位D.数据块2.中断向量地址是(B ).A.子程序入口地址B.中断服务程序入口地址C.中断服务程序入口地址的地址D.例行程序入口地址3.对于低速度输入输出设备,应当选用的通道是(B ).A.数组多路通道B.字节多路通道C.选择通道D.DMA专用通道4.微型机系统中,主机和高速硬盘进行数据交换一般采用(B ).A.程序中断控制B.直接存储器访问C.程序直接控制D.通道控制5.常用于大型计算机的控制方式是(D ).A.程序查询方式B.DMA方式C.中断方式D.通道方式6.下述I/O控制方式中,主要由程序实现的是(D ).A.外围处理机方式B.中断方式C.DMA方式D.通道方式7.有关中断状态,不可响应的中断是(C ).A.硬件中断B.软件中断C.可屏蔽中断D.不可屏蔽中断8.以下论述正确的是(D ).A.CPU响应中断期间仍执行原程序B.在中断响应中,保护断点和现场由用户编程完成C.在中断过程中,若又有中断源提出中断,CPU立即响应D.在中断响应中,保护断点是由中断响应自动完成的9.中断系统是(C ).A.仅用硬件B.仅用软件C.软,硬件结合D.以上都不对10.DMA方式是在(B )之间建立直接的数据通路.A.CPU与外围设备B.主存与外围设备C.外设与外设D.CPU与主存11.通道是特殊的处理器,它有自己的(C ),因此具有较强的的并行工作能力.A.运算器B.存储器C.指令和程序D.以上都有12.字节多路通道上数据传送是以(A )为单位进行的.A.字节B.数据块C.字D.位13.通道程序是由(B )组成的.A.I/O指令B.通道指令(通道控制字)C.通道状态字D.以上都不对14.DMA数据的传送是以(B )为单位进行的.A.字节B.字C.数据块D.位三.判断题1.所有的数据传送方式都必须由CPU控制实现.(× )2.外部设备一旦申请中断,便能立刻得到CPU的响应.( ×)3.一个更高优先级的中断请求可以中断另一个处理程序的执行.(√ )4.为了保证中断服务程序执行完毕以后能正确返回到被中断的断点继续执行程序,必须进行现场保护操作.(√)5.中断级别最高的是不可屏蔽中断.(√ )6.程序中断方式一般适用于随机出现的服务.( √ )7.一旦有中断请求出现,CPU立即停止当前指令的执行,转去受理中断请求.(×)8.CPU响应中断时暂停运行当前程序,自动转换到中断服务程序.(√ )。

计算机硬件技术基础(第2版) 习题答案 耿增民 孙思云 第8章 习题答案

矢量图像,也称为向量图,在数学上定义为一系列由线连接的点,适用于图形设计、文字设计和一些标志设计、版式设计等。矢量图用一组绘图指令来描述图像的内容,这些指令根据图形的几何特性(点点关系)定义图形的轮廓,并用颜色进行描边和填充。

有损压缩

利用人的视觉对于边缘急剧变化不敏感和对图像的亮度信息敏感、对颜色分辨率弱的特点,舍弃一些非主要的细节,在允许一定限度失真的前提下,对图像数据进行压缩。

量化

把声波波形幅度的数字化表示称为量化。

语音识别技术

语音识别技术(Automatic Speech Recognition,ASR),又称为自动语音识别,其目标是将人类的语音中的词汇内容转换为计算机可读的输入。

音频卡

声卡(Sound Card)也叫音频卡,是多媒体技术中最基本的组成部分,它是实现声波/数字信号相互转换的一种硬件。

(8)请计算存储5分钟的44.1k采样频率下16位立体声音频数据至少需要多少K字节?

答:

(9)简述MIDI的含义。

答:MIDI是Musical Instrument Digitial Interface的缩写,是音乐与计算机结合的产物,是一项工业产品的产物,泛指数字音乐的国际标准。

(10)视频采集卡的工作原理是什么?一般有哪些分类?

第八章习题答案

1.名词解释

多媒体计算机

多媒体计算机的英文全称为Multimedia Personal Computer,简称MPC。相对于一般的PC(个人计算机),多媒体计算机增加了一些多媒体部件(包括硬件和软件),使得计算机具有多媒体处理能力。

位图

位图图像(bitmap),也称为点阵图像或绘制图像,是由称作像素的单个点组成的。这些点可以进行不同的排列和染色以构成图样。

计算机硬件技术中断技术知识考试题

计算机硬件技术中断技术知识考试题第八章习题参考答案8.1 什么是中断?使用中断技术有什么好处?答:中断是指由CPU内/外部事件引起或者由程序的预先安排,使CPU中断正在运行的正常程序(主程序),而转到为该内部/外部事件或者预先安排的事件服务程序,待服务完毕,再返回被暂时中断的正常程序处继续执行正常程序的过程。

使用中断技术,能够使计算机方便地实现如下一些操作:(1)分时操作。

有了中断系统,CPU能够命令多个外部设备同时工作,CPU分时操纵这些外设,大大提高了CPU的吞吐率。

(2)实现实时处理。

当计算机用于实时操纵,系统要求计算机为它服务的时间是随机的,而中断系统中这种请求--响应模式正好迎合了实时系统的需求。

(3)故障处理。

计算机在运行过程中,往往会出现一些故障,如电源掉电、存储出错、运算溢出等。

有了中断系统,当出现上述情况时,CPU能够随时转去执行故障处理程序,自行处理故障而不必停机。

随着微型计算机的进展,中断系统不断增加新的功能,中断系统甚至能够实现计算机系统中软硬件资源的自动管理。

8.2 什么叫中断系统?它具备什么功能?答:把能够实现中断全部功能的软件、硬件的总称称之中断系统。

不一致计算机的中断系统,其具体实现可能不尽一样,但中断系统的基本功能是相同的。

中断系统的基本功能如下:1.能实现中断响应、中断处理(服务)、中断返回与中断屏蔽。

这是中断系统最基本的功能。

2.能实现中断优先级排队(管理)。

即当有多个中断源同时申请中断时,CPU如何能够优先响应最紧急的中断申请。

3.能实现中断嵌套。

即当CPU正在为优先级较低的中断源服务时,具有较高优先级的中断源提出中断申请,如今中断系统应当同意较高优先级的中断源中断较低优先级的中断源,待较高优先级的中断处理完成后,再接着处理较低优先级的中断,这种中断服务程序再被中断的过程称之中断嵌套。

8.3 何谓非屏蔽中断与可屏蔽中断?答:非屏蔽中断是指用户不能用软件屏蔽的中断。

计算机硬件技术中断技术知识考试题

计算机硬件技术中断技术知识考试题第八章习题参考答案8.1 什么是中缀?采用中缀技术有哪些益处?答:中缀是指由CPU内/外部事情惹起或由顺序的预先布置,使CPU中缀正在运转的正常顺序〔主顺序〕,而转到为该外部/外部事情或预先布置的事情效劳顺序,待效劳终了,再前往被暂时中缀的正常顺序处继续执行正常顺序的进程。

采用中缀技术,可以使计算机方便地完成如下一些操作:〔1〕分时操作。

有了中缀系统,CPU可以命令多个外部设备同时任务,CPU分时控制这些外设,大大提高了CPU的吞吐率。

〔2〕实理想时处置。

当计算机用于实时控制,系统要求计算机为它效劳的时间是随机的,而中缀系统中这种央求--照应形式正好迎合了实时系统的需求。

〔3〕缺点处置。

计算机在运转进程中,往往会出现一些缺点,如电源掉电、存储出错、运算溢出等。

有了中缀系统,当出现上述状况时,CPU可以随时转去执行缺点处置顺序,自行处置缺点而不用停机。

随着微型计算机的开展,中缀系统不时添加新的功用,中缀系统甚至可以完成计算机系统中软硬件资源的自动管理。

8.2 什么叫中缀系统?它具有哪些功用?答:把可以完成中缀全部功用的软件、硬件的总称称为中缀系统。

不同计算机的中缀系统,其详细完成能够不尽一样,但中缀系统的基本功用是相反的。

中缀系统的基本功用如下:1.能完成中缀照应、中缀处置〔效劳〕、中缀前往和中缀屏蔽。

这是中缀系统最基本的功用。

2.能完成中缀优先级排队〔管理〕。

即当有多个中缀源同时央求中缀时,CPU如何可以优先照应最紧急的中缀央求。

3.能完成中缀嵌套。

即当CPU正在为优先级较低的中缀源效劳时,具有较高优先级的中缀源提出中缀央求,此时中缀系统应当允许较高优先级的中缀源中缀较低优先级的中缀源,待较高优先级的中缀处置完成后,再接着处置较低优先级的中缀,这种中缀效劳顺序再被中缀的进程称为中缀嵌套。

8.3 何谓非屏蔽中缀和可屏蔽中缀?答:非屏蔽中缀是指用户不能用软件屏蔽的中缀。

第八至十章习题答案

第八至十章习题答案P2658.5中断向量表的功能是什么?叙述CPU利用中断向量表转入中断服务程序的过程。

答:中断向量表具有根据中断类型号存储相应中断服务程序入口地址的功能。

CPU利用中断向量表转入中断服务程序的过程如下:由中断类型号n乘以4获得中断向量在中断向量表中的起始地址,然后把存储在低地址4n、4n+1两单元16位的中断服务程序入口偏移地址置入IP,把存储在高地址4n+2、4n+3两单元16位的中断服务程序入口段地址置入CS,最后跳转到中断服务程序。

8.6叙述可屏蔽中断的响应过程。

答:在开中断(IF=1)和INTR引脚有中断请求信号的情况下,可屏蔽中断响应过程如下:1)等待当前指令结束,然后进入中断响应周期;2)从微处理器外部的中断控制逻辑获得中断类型号;3)当前的PSW、CS、IP的内容依次压入堆栈;4)清除PSW中的IF位和TF位为0;5)把中断服务程序的入口地址置入IP和CS。

8.18某8086系统用3片8259A级联构成中断系统,主片中断类型号从10H开始。

从片的中断申请连主片的IR4和IR6引脚,它们的中断类型号分别从20H、30H开始。

主、从片均采用上升沿触发,非自动中断结束方式。

且主片采用特殊全嵌套方式,从片采用完全嵌套方式。

请编写他们的初始化程序。

解:设8258A主片的端口地址为20H(A0=0)和21H(A1=1),第一个8259A从片的端口地址为50H(A0=0)和51H(A1=1),第二个8259A从片的端口地址为0A0H(A0=0)和0A1H(A1=1),初始化程序如下:主片:MOVAL,00010001B;ICW1:边沿触发,级联OUT20H,ALMOVAL,00010000B;ICW2:中断类型号10H~17HOUT21H,ALMOVAL,01010000B;ICW3:IR4和IR6连有从片OUT21H,ALMOVAL,00010001B;ICW4:特殊全嵌套,非缓冲,非自动中断结束OUT21H,AL从片1:MOVAL,00010001B;ICW1:边沿触发,级联OUT50H,ALMOVAL,00100000B;ICW2:中断类型号20H~27HOUT51H,AL MOVAL,00000100B;ICW3:INT引脚连主片IR4OUT51H,ALMOVAL,00000001B;ICW4:完全嵌套,非缓冲,非自动中断结束OUT51H,AL从片2:MOVAL,00010001B;ICW1:边沿触发,级联OUT0A0H,ALMOVAL,00110000B;ICW2:中断类型号30H~37HOUT0A1H,AL MOVAL,00000110B;ICW3:INT引脚连主片IR6OUT0A1H,ALMOVAL,00000001B;ICW4:完全嵌套,非缓冲,非自动中断结束OUT0A1H,AL8.19设8259A的端口地址为50H(A0=0)和51H(A1=1),请给下面的8259A初始化程序加上注释,说明各命令字的含义。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

本文为网上收集整理,如需要该文档得朋友,欢迎下载使用第八章习题参考答案8.1 什么是中断?采用中断技术有哪些好处?答:中断是指由CPU内/外部事件引起或由程序的预先安排,使CPU中断正在运行的正常程序〔主程序〕,而转到为该内部/外部事件或预先安排的事件效劳程序,待效劳完毕,再返回被暂时中断的正常程序处继续执行正常程序的过程。

采用中断技术,可以使计算机方便地实现如下一些操作:〔1〕分时操作。

有了中断系统,CPU可以命令多个外部设备同时工作,CPU分时控制这些外设,大大提高了CPU的吞吐率。

〔2〕实现实时处理。

当计算机用于实时控制,系统要求计算机为它效劳的时间是随机的,而中断系统中这种请求--响应模式正好迎合了实时系统的需求。

〔3〕故障处理。

计算机在运行过程中,往往会出现一些故障,如电源掉电、存储出错、运算溢出等。

有了中断系统,当出现上述情况时,CPU可以随时转去执行故障处理程序,自行处理故障而不必停机。

随着微型计算机的开展,中断系统不断增加新的功能,中断系统甚至可以实现计算机系统中软硬件资源的自动管理。

8.2 什么叫中断系统?它具备哪些功能?答:把能够实现中断全部功能的软件、硬件的总称称为中断系统。

不同计算机的中断系统,其具体实现可能不尽一样,但中断系统的根本功能是相同的。

中断系统的根本功能如下:1.能实现中断响应、中断处理〔效劳〕、中断返回和中断屏蔽。

这是中断系统最根本的功能。

2.能实现中断优先级排队〔管理〕。

即当有多个中断源同时申请中断时,CPU如何能够优先响应最紧急的中断申请。

3.能实现中断嵌套。

即当CPU正在为优先级较低的中断源效劳时,具有较高优先级的中断源提出中断申请,此时中断系统应当允许较高优先级的中断源中断较低优先级的中断源,待较高优先级的中断处理完成后,再接着处理较低优先级的中断,这种中断效劳程序再被中断的过程称为中断嵌套。

8.3 何谓非屏蔽中断和可屏蔽中断?答:非屏蔽中断是指用户不能用软件屏蔽的中断。

它是通过8086的NMI引脚进入。

非屏蔽中断不受中断允许标志IF的影响,当NMI线上一旦有请求时,CPU便在执行完当前指令后,立即予以响应。

所以,这种中断通常用来处理系统的紧急事件和重大故障,如系统的掉电处理、内存或I/O总线的奇偶错误等。

可屏蔽中断是指用户可以用指令禁止和允许的中断。

它是来自CPU的INTR端的中断。

当CPU收到可屏蔽中断请求信号时,是否予以响应取决于中断允许标志IF的状态。

假设IF=1,那么CPU在执行完当前指令后,响应中断请求;假设IF=0,那么禁止可屏蔽中断。

精品文档,word文档可屏蔽中断通常用于各种外部设备的中断。

微型计算机配置的外部设备一般有硬盘、软盘、键盘、显示器和打印机等。

这些外部设备通过8259A可编程中断控制器与CPU相连,8259A 接收来自外设的中断请求,由8259A向CPU发出中断请求。

8.4 CPU在什么情况下才响应中断〔可屏蔽〕?答:一个可屏蔽中断假设想得到CPU的响应,必须同时满足以下所有条件:首先,CPU应收到一个可靠的中断请求信号,且该中断请求信号应一直保持到它被响应为止。

其次,在中断请求的同时,没有更高级的请求信号发生。

即这个中断请求应该是当前申请中断的、且没有被屏蔽的、优先级最高的中断源。

第三,CPU内部应处在开中断〔允许中断〕状态。

对8086CPU,应设置IF=1。

第四,CPU至少要在当前指令执行完成时才可能响应中断。

事实上,CPU只在特定的时刻〔当前指令周期最后一个总线周期的最后一个时钟周期〕才采样有无中断申请。

第五,如果遇到CPU正在执行中断返回指令〔IRET〕,或CPU正在对中断资源进行操作〔如执行STI指令〕,那么要在现行指令执行完后接着再执行一条其他指令,此后才能响应新的中断。

这么做的目的是为了隔离两个中断。

8.5 什么叫中断优先权〔级〕?有哪些解决中断优先权〔级〕的方法?答:大多数的处理机系统都是多中断源—单申请线的系统,即多个中断源共用同一条中断申请线向CPU申请中断。

因此首先要解决系统中有两个或两个以上中断源同时申请中断时CPU优先响应哪个中断源的中断申请问题,即让哪个中断源的中断申请优先通过唯一的中断申请线向CPU申请中断。

为此,提出了中断优先级的概念。

CPU总是首先响应当前申请中断的、最高优先权的请求。

软件查询中断源及优先级排队方法。

该方法的主要思想是:多个中断源的中断申请通过一个“或〞逻辑后由同一引脚向CPU申请中断,同时在中断接口电路中设置一个中断请求锁存器,以保存各个中断源的中断申请。

CPU中断响应,在关闭中断、保护断点和标志存放器内容后,转入系统唯一的、为所有中断源所共用的中断效劳程序入口执行中断效劳程序,在中断效劳程序中用软件查询的方法查找中断源,从而将程序转向相应的中断效劳程序。

显然,按照先查到的先效劳的思想,软件查询的顺序就是中断优先级的顺序。

实现这种软件查询中断源及优先级排队方法所需的硬件接口逻辑非常简单,改变各中断源的优先级次序也非常方便,但缺点是软件查询所需的时间较长。

因此这种方法主要用于系统规模较小、对响应时间要求不太高的场合。

链式优先权排队逻辑。

多个中断源的中断申请通过一个“或〞逻辑后由同一引脚向CPU 申请中断,同时设置中断请求触发器以保存各个中断源的中断申请。

各中断源还需准备一个唯一标识该中断源的的标识码—中断矢量,已备CPU在响应中断时根据此标识码来判断中断的来源以及将要转入的中断效劳程序入口。

来自CPU的中断响应信号INTA通过多个与门逐次向后传送,形成一个传送INTA信号的链条,称为菊花链。

每个中断源的中断优先级由它们在链条中的位置来决定。

处于链首的中断源具有最高的优先级,链尾中断源的优先级最低。

在当前申请中断的中断源中,只有收到有效INTA信号的中断源,才有资格翻开三态缓冲器向本文为网上收集整理,如需要该文档得朋友,欢迎下载使用精品文档,word 文档数据总线释放其中断矢量。

处在链条前端的中断源,可以中断处于链条后端正在进行效劳的中断源。

链式优先权排队逻辑电路比拟简单,中断响应速度快〔只取决于门电路的延迟时间〕,但随着中断源个数的增加链条的长度也随之增加,中断源个数过多时也影响中断响应速度并且电路也显庞大,此外,调整中断源的优先级次序也比拟麻烦。

编码器和比拟器优先级排队逻辑。

具有中断请求存放、中断屏蔽、中断嵌套、自动对中断源进行编码并输出中断矢量等功能。

编码器和比拟器优先级排队逻辑功能齐全、中断响应速度较快,但硬件比拟复杂。

8.6 中断处理过程一般包括哪些步骤?中断处理过程主要包括中断申请、中断响应、中断源识别、中断效劳和中断返回等几个阶段。

图8-3示出了中断处理的一般过程。

主程序中断服务程序8.7 什么是中断类型号?简述其作用。

答:中断类型号〔码〕是系统为每个中断源分配的、唯一标识该中断源的编码。

当一个中断被CPU 所响应时,中断逻辑应将该中断的中断类型码〔中断向量〕自动送给CPU ,CPU 根据该中断类型号根据一定方法找到相应的该中断源的中断效劳程序的入口地址,并将程序转向中断效劳程序。

8.8 什么是中断响应周期?简述在中断响应周期中CPU 和8259A 一般需要完成的工作。

答:CPU 只有在响应外部可屏蔽中断时,才执行2个连续的中断响应周期,其目的是:第1个中断响应周期,外部中断逻辑准备中断类型码,此时CPU 使数据总线AD 0-AD 7浮空,第2个响应周期,CPU 通过数据总线AD 0-AD 7接收中断类型号,得到中断向量表地址。

8.9 8259A的主要功能是什么?内部主要的有哪些存放器?分别完成什么功能?答:Intel8259A是一片可编程中断控制器集成电路芯片。

可编程是指用户可以用软件编程的方法来设定芯片的工作环境和工作方式,使之芯片适应于各种应用需求。

一片8259A可以管理8级中断,多片8259A级联可使中断最大扩展至64级,每一级中断都可以屏蔽或允许,8259A在中断响应周期,可提供相应的中断类型号,从而迅速转至中断效劳程序,8259A设计有多种工作方式,可以通过编程来选择,以适应不同的应用场合。

内部存放器:中断清求存放器IRRIRR〔Interrupt Request Register〕是与外部接口的中断请求线相连的存放器,请求中断处理的外部中断源通过IR0-IR7向8259A申请中断,并把中断请求信号锁存在中断请求存放器中。

中断屏蔽存放器IMRIMR〔Interrupt Mask Register〕是一个8位存放器,用来设置中断请求的屏蔽信息。

当IMR 中第i位被屏蔽时〔即IMR i=1〕,禁止IR i发出的中断请求信号。

中断效劳存放器ISR〔Interrupt Service Register〕用于存放当前正在进行处理的中断源。

ISR的置位是在中断响应周期,由优先权电路〔PR〕根据IRR中各申请中断位的优先级别和IMR中屏蔽字的状态,选取允许中断的最高优先级请求位,选通到ISR中。

当中断处理完毕,ISR的复位由中断结束方式决定。

初始化命令字〔ICW1-ICW4〕存放器和操作命令字OCW1-OCW3存放器。

8.10 简述8086CPU的中断结构及中断处理过程。

答:8086具有强有力的中断系统,可以处理256种不同的中断。

如果将这些中断进行分类,那么可以分为两大类:外部中断和内部中断。

外部中断是由外部硬件的请求产生的中断,所以又称为硬件中断。

内部中断是由指令的执行或者软件对标志存放器中某个标志的设置产生的中断,所以又称为软件中断。

8086CPU响应中断的处理过程如图8-25所示。

从图中可以看出,对于类别不同的中断,CPU的响应次序是不同的。

CPU首先响应内部中断,其次是非屏蔽中断和可屏蔽中断,最后才响应单步中断。

CPU只有在响应外部可屏蔽中断时,才执行2个连续的中断响应周期,其目的是:第1个中断响应周期,外部中断逻辑准备中断类型码,此时使数据总线AD0-AD7浮空,第2个响应周期,CPU通过数据总线AD0-AD7接收中断类型号,得到中断向量表地址。

对于其他类别的中断,由于其类型号是固定的或由指令的操作数指定,故不经过这一步骤。

以下步骤和操作是各类中断共有的:1.执行—个总线写周期,将标志存放器的内容压入堆栈。

2.保存单步标志。

将标志存放器中IF标志和TF标志置0,从而禁止在中断响应过程中其他可屏蔽中断进入,禁止单步中断。

3.执行2个总线写周期。

在这2个写周期内,分别将CS和IP的内容压入堆栈。

4.执行一个总线读周期。

在这个周期中,从向量地址的前两个字节中读取中断处理程序入口地址的偏移量送IP存放器。

5.执行一个总线读周期。

在这个周期中,从向量地址的后两个字节中读中断处理程序段基址送CS存放器。