字符叠加芯片MB90092手册中文版

欧姆网9102B Handheld Spectrum Analyzer商品说明书

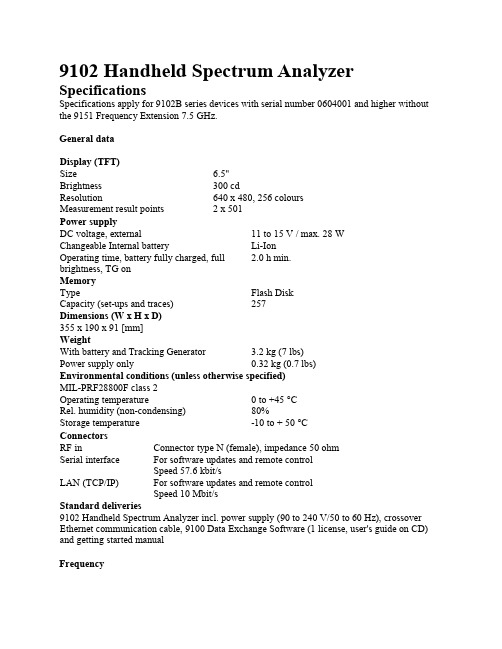

9102 Handheld Spectrum Analyzer SpecificationsSpecifications apply for 9102B series devices with serial number 0604001 and higher without the 9151 Frequency Extension 7.5 GHz.General dataDisplay (TFT)Size 6.5''Brightness 300 cdResolution 640 x 480, 256 coloursMeasurement result points 2 x 501Power supplyDC voltage, external 11 to 15 V / max. 28 WChangeable Internal battery Li-Ion2.0 h min.Operating time, battery fully charged, fullbrightness, TG onMemoryType Flash DiskCapacity (set-ups and traces) 257Dimensions (W x H x D)355 x 190 x 91 [mm]WeightWith battery and Tracking Generator 3.2 kg (7 lbs)Power supply only 0.32 kg (0.7 lbs)Environmental conditions (unless otherwise specified)MIL-PRF28800F class 2Operating temperature 0 to +45 °CRel. humidity (non-condensing) 80%Storage temperature -10 to + 50 °CConnectorsRF in Connector type N (female), impedance 50 ohmSerial interface For software updates and remote controlSpeed 57.6 kbit/sLAN (TCP/IP) For software updates and remote controlSpeed 10 Mbit/sStandard deliveries9102 Handheld Spectrum Analyzer incl. power supply (90 to 240 V/50 to 60 Hz), crossover Ethernet communication cable, 9100 Data Exchange Software (1 license, user's guide on CD) and getting started manualFrequencyFrequency rangeMeasurement range 100 kHz to 4 GHzResolution 1 kHzSweep timeSpan > 10 kHz 1 ms to 250 sSpan = 0 Hz 1 ms to 250 sResolution bandwidth (RBW)RBW (-3 dB) range 100 Hz to 1 MHz (RBW selection manual or automatic) Video bandwidth (VBW)VBW range (-3 dB) 10 Hz to 1 MHz (VBW selection manual or automatic)SSB noise< -80 dBc/Hz (f = 2 GHz, Δf = 100 kHz, RBW = 10 kHz, VBW = 1 kHz)AmplitudeMeasurement rangeAveraged noise floor to 20 dBmDisplay unitsdBm, dBµV, dBmV, dBV, dBDisplayed average noise level (DANL) (RBW = 100 Hz, attenuation = 0 dB)10 to 1000 MHz < -127 dBm,typ.-130 dBm 1000 to 4000 MHz < -130 dBm,typ.-135 dBm Input attenuationSetting range 0(10) to 50 dB Attenuation steps 10 dB Dynamic rangeRange > 70 dB Max. measurable input level (attenuation = 40 dB) 20 dBm Min. measurable input level -130 dBm Level accuracy10 to 3600 MHz ±1 dBRF input match (1 to 4000 MHz, input attenuation = 10 dB)VSWR < 1.6, typ. < 1.5 Return loss < -12 dB Spurious responseImage rejection (f = 1 GHz) > 80 dBLO breakthrough (attenuation = 10 dB) < -77 dBm Spurious level (attenuation = 0 dB) < -90 dBm Intermodulation-free range> 63 dB (input level -30 dBm, f1 = 990 MHz, f2 = 992 MHz)FunctionsDetector & sweepDetector types pos./neg. peak, pos. peak, neg. peak, sampleSweep processing actual, average, max. hold, min. holdTraceMax. displayed traces 2Trace points 2 x 501(Two independent traces are available, min. hold, max.hold at the same time)Trace functions A+B ? A, A-B ? A,trace offset, copy a>b, copy b>aMarkerMax. markers 6Delta markers 5Marker functions max. peak, next peakTransfer functions M ? centre frequency, M ? ref. level, M ? f stepLimit checkLimit functions upper, lower, upper and lowerPower measurementMeasurement functions Channel Power, ACPR, OBWDefault systems GSM, WCDMA, DECT, WLANDemodulationAM/FM on marker/permanent/on multi marker9102 Handheld Spectrum Analyzer with 9151 Frequency Extension 7.5 GHz SpecificationsFrequency rangeMeasurement range 100 kHz to 7.5 GHzSSB noise< –80 dBc/Hz (f = 5.7 GHz, ?f = 100 kHz, RBW = 10 kHz, VBW = 1 kHz)Displayed average noise level (DANL) (RBW = 100 Hz, attenuation = 0 dB)10 MHz to 4 GHz < –119 dBm, typ. –121 dBm 4 GHz to 7 GHz < –120 dBm, typ. –123 dBm 7 to 7.5 GHz < –113 dBmDynamic rangeRange (5.000 GHz / 5.001 GHz) > 70 dBMax. measurable input level20 dBm(attenuation = 40 dB)Min. measurable input level (<4 GHz) –119 dBmMin. measurable input level (4 GHz to 7 GHz) –120 dBmMin. measurable input level (7 GHz to 7.5 GHz)–112dBm(attenuation = 0 dB)RF input match (input attenuation = 10 dB)VSWR (100 MHz to 4 GHz) < 1.6VSWR (4 GHz to 6 GHz) < 2.0 VSWR (6 GHz to 7.5 GHz) < 2.3 Return loss (100 MHz to 4 GHz) < –15 dB Return loss (4 GHz to 6 GHz) < –9 dB Return loss (6 GHz to 7.5 GHz) < –7 dB Spurious responseImage rejection (f = 6.7 GHz) ) > 60 dB Spurious level (100 kHz to 4 GHz) < –90 dBm< –83 dBm Spurious level (4 GHz to 7.5 GHz)(attenuation = 0 dB)< –57 dBm LO leakage (7.7 GHz)(attenuation = 10 dB)。

基于MB90092的视频字符叠加器的设计

S — 主输控 { 全 C 横 人制_ . L X 抽 r _ 型鱼

一

视 信 频号

输^ 同步 信 号

C L 8一

— — —

_ _ J

]

』

.

输入

M 902 B 0 9 有两种 同步方式 : 当外 部有视频信号输入时 , 它采用提取 的外部 同步信号 , 工作 在外部 同步模 式 ; 当外 部没有视频信 号输 入时 , 此时也相应 的没有 同步信号可 以提取 , 9 0 2内部可通 过E 与 X MB 0 9 XS S 之间所 接的 晶体 ( 此处 接入 1.3 M晶体 , 频信号 为P L制 ) 77 4 视 A 自行产 生同步信号 , 直接输 出只含叠加 字符 的视频信号, 在监视器上显示不 同 背景颜色 、 不同字符颜色的视频信号 , 此为 内同步模式。 MB 0 9 与AR 902 M只有 3 条通信线 :I 串行数据输入 ) C K( SN( , L 串行 S 时钟 ) s 片选信 号) , ( c 。 23 制单元及字库电路 _ 控 本 设计 中控 制单元除 了要对 M 90 2 B 0 9 进行控制 外 , 还需要 提供 更 新 字库的功能 。由于字库容量 比较大 , 而普通 单片机的寻址空间不够 , 无 法完成整 个字库 的烧 写 , 能满足要求 , 不 因此这 里采用一块 A M微 R

引 言

、

随着视频监 控系统应用 的普及, 安全 防护的要求也在 不断提高 , 单 纯的视频画面监控 已经不能满足现代监控 的需要。现在很多用户要求 监视 的画 面中能带有 与之相关 的各种信息 , 比如监控 的地点 、 时间 、 监 控 的状 态信息及一些实时更新 的数据等 。 本 文设 计了一种能在视频 画面中任意位置叠加任 意字符和图形的 视频字 符叠加系统 。它 可以方便 的接收外部数据并 把相关 的信息叠加 到视频 画面中 , 监视信息和 画面一 目了然 , 能应用在对 监控性能要求较 高的场合 , 比如储 物仓 库 、 超市 、 银行和高速公路收费站等 。 1系统设计 . 11 . 原理及设计思路 为 了向视频信 号中叠加所 需字符 信息 , 先要处理 的就是视频 信 首 号和叠 加字符 的同步问题 , 也就是保证 经视频 信号提取 电路分离 出的 行与场信 号对于所 需叠加 的字符信号 的同步 , 然后再使这 两种不 同的 信号叠加起来后在 同一幅画面 中显示 出来 。传统的方法是通过 自己用 分立 器件搭 建各部 分核心 电路 , 此种方 法实现起 来 比较复 杂而且系 统 的整 体性能会 因为 引人了过多的分立元件 而降低。还有一种方法是使 用专 用 的集 成芯 片来实现 , 优点是实现 电路简单 , 其 使用 的元 器件少 , 系统稳 定性 强 , 本系统采用后者实现 。 1 9 0 2 要 功 能 特 点 .MB 09 主 2 MB 0 9 是 日本 富士公 司推 出的一 款 O D专用集 成芯片 , 用该 90 2 S 使 芯片 可以向视频画 面中叠加 各种文字及 图像信息 。该 芯片叠加 目标信 息时需使用 外部字库芯片 , 因此 其相应的提供有外挂字库 的接 口, 它能 支持多 达 1 Mbt的外 部存储空 间的访 问 , 6 i s 用户可 以 自己向字库芯片 中 烧入 自己所需 叠加 的任意点阵字符或图像等 。 MB 0 9 9 0 2内部结 构模块 如图 1 所示。

基于MB90092的字符叠加系统设计

保 障视 频 信 号 的 清 晰输 出。 图 1 所示 是 该 视 频叠

加系统 的硬 件结 构框 图。 阻 输 f步 号 颁 同 信 分离

l

这 种 方案 的优点 是元 件数量 少 。电路简 单 容易 实

现 。系统 稳定性 好 。

I — L l1 l I Mg 8

EHY 0 7 XSND0】 A[8 [ 1

统 的通 用性 和 实用 性 ,本 文选 择 MB o 9 来 实 现 902

间 、 日期 、提 示语 或 图形 标 志等 。为 此 ,本 文给

出 了一般 的低 成本 、高 可靠视 频叠 加 系统 的设 计 方案

字符 叠加 系统 。

2 硬 件 设 计

1 视 频 叠 加 系统 原 理

21 总体 结构 . OS O — cen D sly D f n S re — i a)是 视 频 叠 加 的 英 p

维普资讯

第9 卷

期 2 7第9 0 年月 o 9

婚墓缔 痢

V1 N. o o . 9 9

Sp 0 7 e .2 0

基于MB 0 9 的字符叠加系统设计 902

王 天 玉

( 同济 大 学中德 学院 ,上 海

摘

20 9) 0 0 2

要 :介 绍 了基 于 专 用视 频 叠 加 芯 片 MB 0 9 实现 字 符 叠 加 的 系统 结 构 及 外 围 电路 实现 原 90 2

— VI N

D0】 [7

A[ 1 】 0 8 字库 芯片 W 2 COO 9 4

CE

视 频 叠 加 芯 片

毋9 0 2 0 9

P1 1 CS

通过 比较 两种 方案 的优 劣 。本设 计 采用 第二 种 方案来 实 现视频 叠加 。而第二 种 方案 在芯 片选 型 上又有 两种 不 同的 芯片可 供选 择 。一种 是 芯 片

ANALOG DEVICES AD9520-0 中文数据手册

特性 低相位噪声锁相环(PLL) 片内VCO调谐范围:2.53 GHz至2.95 GHz 支持最高2.4 GHz的外部3.3 V/5 V VCO/VCXO 1路差分或2路单端参考输入 支持最高250 MHz的CMOS、LVDS或LVPECL参考 参考输入接受16.67 MHz至33.3 MHz晶振 可选参考时钟倍频器 参考监控功能 自动和手动参考切换/保持模式,支持可选的恢复式/非恢 复式切换 参考间无毛刺切换 从保持模式自动恢复 可选数字或模拟锁定检测 可选零延迟工作 12路1.6 GHz LVPECL输出分为4组 每组3路输出,具有一个带相位延迟的1至32分频器 加性输出抖动低至225 fs rms 分组输出的通道间偏斜:<16 ps 可以将每路LVPECL输出配置为2路CMOS输出(fOUT ≤ 250 MHz) 上电时所有输出自动同步 可以根据需要手动同步多路输出 SPI和I²C兼容型串行控制端口 64引脚LFCSP封装 非易失性EEPROM存储配置设置

DIV/Φ

DIV/Φ

DIV/Φ

图1

AD9520串行接口支持SPI和I2C®端口。封装内EEPROM可 以通过串行接口进行编程,存储用于上电和芯片复位的用 户定义寄存器设置。 AD9520具有12路LVPECL输出,分为四组。任何一路1.6 GHz LVPECL输出都可以重新配置为两路250 MHz CMOS输 出。 每组输出具有一个分频器,其分频比(从1至32)和相位(粗 调延迟)均可以设置。 AD9520提供64引脚LFCSP封装,可以采用3.3 V单电源供电。 外部VCO的工作电压最高可达5.5 V。独立的输出驱动器电 源可以为2.375 V至3.465 V。 AD9520的额定工作温度范围为−40°C至+85°C标准工业温 度范围。

高频耦合防弹芯片数据手册说明书

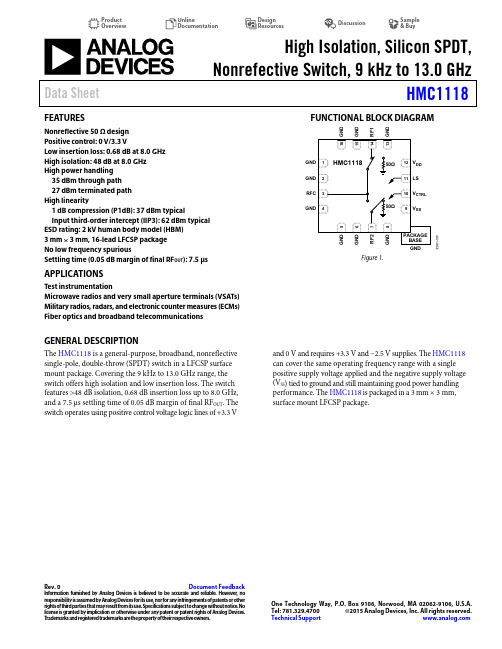

High Isolation, Silicon SPDT,Nonrefective Switch, 9 kHz to 13.0 GHz Data Sheet HMC1118Rev. 0Document FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, N orwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2015 Analog Devices, Inc. All rights reserved. Technical Support FEATURESNonreflective 50 Ω designPositive control: 0 V/3.3 VLow insertion loss: 0.68 dB at 8.0 GHzHigh isolation: 48 dB at 8.0 GHzHigh power handling35 dBm through path27 dBm terminated pathHigh linearity1 dB compression (P1dB): 37 dBm typicalInput third-order intercept (IIP3): 62 dBm typicalESD rating: 2 kV human body model (HBM)3 mm × 3 mm, 16-lead LFCSP packageNo low frequency spuriousSettling time (0.05 dB margin of final RF OUT): 7.5 μs APPLICATIONSTest instrumentationMicrowave radios and very small aperture terminals (VSATs) Military radios, radars, and electronic counter measures (ECMs) Fiber optics and broadband telecommunicationsFUNCTIONAL BLOCK DIAGRAMGNDGNDRFCGNDNDNDF1ND12961-1Figure 1.GENERAL DESCRIPTIONThe HMC1118 is a general-purpose, broadband, nonreflective single-pole, double-throw (SPDT) switch in a LFCSP surface mount package. Covering the 9 kHz to 13.0 GHz range, the switch offers high isolation and low insertion loss. The switch features >48 dB isolation, 0.68 dB insertion loss up to 8.0 GHz, and a 7.5 μs settling time of 0.05 dB margin of final RF OUT. The switch operates using positive control voltage logic lines of +3.3 V and 0 V and requires +3.3 V and −2.5 V supplies. The HMC1118 can cover the same operating frequency range with a single positive supply voltage applied and the negative supply voltage (V SS) tied to ground and still maintaining good power handling performance. The HMC1118 is packaged in a 3 mm × 3 mm, surface mount LFCSP package.HMC1118Data SheetRev. 0 | Page 2 of 11TABLE OF CONTENTSFeatures .............................................................................................. 1 Applications ....................................................................................... 1 Functional Block Diagram .............................................................. 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications ..................................................................................... 3 Electrical Specifications ............................................................... 3 Digital Control Voltages .............................................................. 4 Bias and Supply Current .............................................................. 4 Absolute Maximum Ratings ............................................................ 5 ESD Caution .................................................................................. 5 Pin Configuration and Function Descriptions ..............................6 Interface Schematics .....................................................................6 Typical Performance Characteristics ..............................................7 Insertion Loss, Return Loss, and Isolation ................................7 Input Compression Point and Input Third-Order Intercept ...8 Theory of Operation .........................................................................9 Applications Information .............................................................. 10 Evaluation PCB ........................................................................... 10 Outline Dimensions ....................................................................... 11 Ordering Guide .. (11)REVISION HISTORY10/15—Revision 0: Initial VersionData Sheet HMC1118 SPECIFICATIONSELECTRICAL SPECIFICATIONSV CTRL = 0 V/3.3 V dc, V DD = LS = 3.3 V dc, V SS = −2.5 V dc, T A = 25°C, 50 Ω system, unless otherwise specified.Table 1.Parameter Test Conditions/Comments Min Typ Max Unit INSERTION LOSS9 kHz to 3.0 GHz 0.5 1.0 dB9 kHz to 8.0 GHz 0.68 1.1 dB9 kHz to 10.0 GHz 0.7 1.3 dB9 kHz to 13.0 GHz 1.3 2.0 dB ISOLATION RFC TO RF1/RF2 (WORST CASE)9 kHz to 3.0 GHz 40 50 dB9 kHz to 8.0 GHz 42 48 dB9 kHz to 10.0 GHz 28 35 dB9 kHz to 13.0 GHz 18 25 dB RETURN LOSSOn State 9 kHz to 3.0 GHz 26 dB9 kHz to 8.0 GHz 22 dB9 kHz to 13.0 GHz 9 dB Off State 9 kHz to 3.0 GHz 26 dB9 kHz to 8.0 GHz 14 dB9 kHz to 13.0 GHz 5 dB RADIO FREQUENCY (RF) SETTLING TIME50% V CTRL to 0.05 dB margin of final RF OUT7.5 µs50% V CTRL to 0.1 dB margin of final RF OUT 6 µs SWITCHING SPEEDt RISE/t FALL10%/90% RF 0.85 µst ON/t OFF50% V CTRL to 10%/90% RF 2.7 µs INPUT POWER 1 MHz to 13.0 GHz1 dB Compression (P1dB) 35 37 dBm 0.1 dB Compression (P0.1dB) 35 dBm INPUT THIRD-ORDER INTERCEPT (IIP3) Two-tone input power = 14 dBm at each tone, 1 MHz to 13.0 GHz 62 dBm RECOMMENDED OPERATING CONDITIONS1Positive Supply Voltage (V DD) 3.0 3.6 V Negative Supply Voltage (V SS) −2.75 −2.25 V Control Voltage (V CTRL) Range 0 V DD V Logic Select (LS) Voltage Range 0 V DD V RF Input Power V DD/V CTRL = 3.3 V, V SS = −2.5 V, T A = 85°C, frequency = 2 GHzThrough Path 35 dBm Termination Path 27 dBm Hot Switch Power Level V DD = 3.3 V, T A = 85°C, frequency = 2 GHz 27 dBm Case Temperature Range (T CASE) −40 +85 °C1 These are the recommended values for these parameters.Rev. 0 | Page 3 of 11HMC1118 Data SheetDIGITAL CONTROL VOLTAGESV DD = 3.3 V ± 10%, V SS = −2.5 V ± 10%, T CASE = −40°C to +85°C, unless otherwise specified.Table 2.Parameter Symbol Min Typ Max Unit Test Condition/CommentsINPUT CONTROL VOLTAGE <1 µA typicalLow V IL−0.3 +0.8 VHigh V IH 2.0 V DD + 0.3 VBIAS AND SUPPLY CURRENTTable 3.Parameter Symbol Min Typ Max UnitSUPPLY CURRENTV DD = 3.3 V I DD20 200 µAV SS = −2.5 V I SS0.5 10 µARev. 0 | Page 4 of 11Data SheetHMC1118Rev. 0 | Page 5 of 11ABSOLUTE MAXIMUM RATINGSTable 4.ParameterRatingPositive Supply Voltage (V DD ) Range −0.3 V to +3.7 V dc Negative Supply Voltage (V SS ) Range −2.8 V to +0.3 V Control Voltage (V CTRL ) Range −0.3 V to V DD + 0.3 V Logic Select (LS) Voltage Range−0.3 V to V DD + 0.3 V RF Input Power 1 (V DD /V CTRL = 3.3 V, V SS = −2.5 V, T A = 85°C, Frequency = 2 GHz) See Figure 2 to Figure 4 Through Path 37 dBm Termination Path28 dBm Hot Switch Power Level (V DD = 3.3 V,T A = 85°C, Frequency = 2 GHz) 30 dBm Storage Temperature Range−65°C to +150°C Maximum Reflow Temperature (MSL3 Rating) 260°C Channel Temperature135°C Thermal Resistance (Channel to Package Bottom)Through Path 116°C/W Terminated Path100°C/W ESD Sensitivity (HBM), Class 22 kV1For recommended operating conditions, see Table 1.Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.4–24–20–16–12–8–40010987654321P O W E R (d B )FREQUENCY (GHz)12961-002Figure 2. Power Derating Through Path4–24–20–16–12–8–400.010.11101001000P O W E R (d B )FREQUENCY (MHz)12961-004Figure 3. Power Derating Through Path (Low Frequency Detail)4–24–20–16–12–8–400.010.1110100100010000P O W E R (d B )FREQUENCY (MHz)12961-003Figure 4. Power Derating for Hot Switching PowerESD CAUTIONHMC1118Data SheetRev. 0 | Page 6 of 11PIN CONFIGURATION AND FUNCTION DESCRIPTIONSDD CTRL SSG N DG N DR F 2G N D G N DG N DR F 1G N D12961-005NOTES1. THE EXPOSED PAD MUST BE CONNECTED TO THE RF/DC GROUND OF THE PRINTED CIRCUIT BOARD (PCB).Figure 5. Pin ConfigurationTable 5. Pin Function DescriptionsPin No.MnemonicDescription1, 2, 4 to 6, 8, 13, 15, 16GNDGround. The package bottom has an exposed metal pad that must connect to the printed circuit board (PCB) RF/dc ground. See Figure 6 for the GND interface schematic.3 RFC RF Common Port. This pin is dc-coupled and matched to 50 Ω. A dc blocking capacitor is required ifthe RF line potential is not equal to 0 V dc.7 RF2 RF2 Port. This pin is dc-coupled and matched to 50 Ω. A dc blocking capacitor is required if the RFline potential is not equal to 0 V dc.14 RF1 RF1 Port. This pin is dc-coupled and matched to 50 Ω. A dc blocking capacitor is required if the RFline potential is not equal to 0 V dc.9 V SS Negative Supply Voltage Pin. 10 V CTRL Control Input Pin. See Table 1, Table 2, and Table 6. 11 LS Logic Select Input Pin. See Table 1, Table 2, and Table 6. 12 V DD Positive Supply Voltage Pin. EPADExposed Pad. The exposed pad must be connected to the RF/dc ground of the printed circuit board (PCB).Table 6. Truth TableControl InputSignal Path StateLS V CTRL RFC to RF1RFC to RF2High L ow On Off High High Off On ow L owOff On ow HighOnOffINTERFACE SCHEMATICSGND12961-006Figure 6. GND Interface SchematicV12961-007V CTRLFigure 7. V CTRL Interface SchematicV 12961-008LSFigure 8. LS Interface SchematicData SheetHMC1118Rev. 0 | Page 7 of 11TYPICAL PERFORMANCE CHARACTERISTICSINSERTION LOSS, RETURN LOSS, AND ISOLATION–4–3–2–12468101214I N S E R T I O N L O S S (d B )FREQUENCY (GHz)12961-009Figure 9. Insertion Loss vs. Frequency–50–40–30–20–10024********R E T U R N L O S S (d B )FREQUENCY (GHz)12961-011Figure 10. Return Loss vs. Frequency0–90–80–70–60–50–40–30–20–102468101214I S O L A T I O N (d B )FREQUENCY (GHz)12961-010Figure 11. Isolation Between RFC and the RF1 and RF2 Ports vs. Frequency0–100–90–80–70–60–50–40–30–20–1002468101214I S O L A T I O N (d B )FREQUENCY (GHz)12961-012Figure 12. Isolation Between RF1 and RF2 Ports vs. FrequencyHMC1118Data SheetRev. 0 | Page 8 of 11INPUT COMPRESSION POINT AND INPUT THIRD-ORDER INTERCEPT4028303234363813121110987654321I N P U T C O M P R E S S I O N (d B m )FREQUENCY (GHz)12961-013Figure 13. 0.1 dB and 1 dB Compression Point vs. Frequency40283032343638013121110987654321I N P U T C O M P R E S S I O N (d B m )FREQUENCY (GHz)12961-014Figure 14. 1 dB Input Compression Point vs. Frequency over Temperature6545505560012108642I N P U T I P 3 (d B m )FREQUENCY (GHz)12961-015Figure 15. Input Third-Order Intercept (IIP3) Point vs. Frequency overTemperature 401015202530350.010.11101001000I N P U T C O M P R E S S I O N (d B m )FREQUENCY (MHz)12961-016Figure 16. 0.1 dB and 1 dB Input Compression Point vs. Frequency(Low Frequency Detail)401015202530350.010.11101001000I N P U T C O M P R E S S I O N (d B m )FREQUENCY (MHz)12961-017Figure 17. 1 dB Input Compression Point vs. Frequency over Temperature(Low Frequency Detail)65605550450.11101001000I N P U T I P 3 (d B m )FREQUENCY (MHz)12961-018Figure 18. Input Third-Order Intercept (IIP3) Point vs. Frequency overTemperature (Low Frequency Detail)Data SheetHMC1118Rev. 0 | Page 9 of 11THEORY OF OPERATIONThe HMC1118 requires a positive supply voltage applied to the V DD pin and a negative supply voltage applied to the V SS pin. Bypassing capacitors are recommended on the supply lines to minimize RF coupling. The HMC1118 can operate with a single positive supply voltage applied to the V DD pin and the negative voltage input pin (V SS ) connected to ground; however, some performance degradations in the input power compression and third-order intercept can occur.The HMC1118 is controlled via two digital control voltages applied to the V CTRL pin and the LS pin. A small value bypassing capacitor is recommended on these digital signal lines to improve the RF signal isolation.The HMC1118 is internally matched to 50 Ω at the RF input port (RFC) and the RF output ports (RF1 and RF2); therefore, no external matching components are required. The RF1 and RF2 pins are dc-coupled, and dc blocking capacitors are required on the RF paths if the RF potential is not equal to a common-mode voltage of 0 V . The design is bidirectional; the input and outputs are interchangeable.The ideal power-up sequence is as follows:1. Power up GND.2. Power up V DD and V SS . The relative order is not important.3. Power up the digital control inputs. The relative order ofthe logic control inputs is not important. Powering the digital control inputs before the V DD supply can inadvertently forward bias and damage the internal ESD protection structures.4. Power up the RF input. The logic select (LS) allows the user to define the control input logic sequence for the RF path selections. With the LS pin set to logic high, the RFC to RF1 path turns on when V CTRL is logic low, and the RFC to RF2 path turns on when V CTRL is logic high. With LS set to logic low, the RFC to RF1 path turns on when V CTRL is logic high, and the RFC to RF2 path turns on when V CTRL is logic low.Depending on the logic level applied to the LS and V CTRL pins, one RF output port (for example, RF1) is set to on mode, by which an insertion loss path provides the input to the output. The other RF output port (for example, RF2) is then set to off mode, by which the output is isolated from the input. When the RF output port (RF1 or RF2) is in isolation mode, internally terminate it to 50 Ω, and the port absorbs the applied RF signal (see Table 7).Table 7. Switch Mode OperationDigital Control Inputs Signal ModeLS V CTRL RFC to RF1 RFC to RF2 High LowOn mode. A low insertion loss path from the RFC port to the RF1 port.Off mode. The RF2 port is isolation from the RFC port andinternally terminated to a 50 Ω load to absorb the applied RF signals.High HighOff mode. The RF1 port is isolation from the RFC port and internally terminated to a 50 Ω load to absorb the applied RF signals.On mode. A low insertion loss path from the RFC port to the RF2 port. Low LowOff mode. The RF1 port is isolation from the RFC port and internally terminated to a 50 Ω load to absorb the applied RF signals.On mode. A low insertion loss path from the RFC port to the RF2 port. Low HighOn mode. A low insertion loss path from the RFC port to the RF1 port.Off mode. The RF2 port is isolation from the RFC port andinternally terminated to a 50 Ω load to absorb the applied RF signals.HMC1118Data SheetRev. 0 | Page 10 of 11APPLICATIONS INFORMATIONEVALUATION PCBGenerate the evaluation PCB used in this application with proper RF circuit design techniques. Signal lines at the RF port must have 50 Ω impedance, and the package ground leads and backside ground slug must be connected directly to the ground plane similarly to what is shown in Figure 19. The evaluation board shown in Figure 19 is available from Analog Devices, Inc. upon request.12961-019Figure 19. EV1HMC1118LP3D Evaluation PCBTable 8. Bill of Materials for the EV1HMC1118LP3D Evaluation Board 1Item Description Manufacturer 2J1 to J3 PC mount SMA RF connectors TP1 to TP5 Through-hole hold mount test points C1, C5 100 pF capacitors, 0402 packageU1 HMC1118 SPDT switch Analog Devices, Inc.PCB 600-01012-00-1 evaluation PCB, Rogers 4350 circuit board materialEV1HMC1118LP3D , Analog Devices, Inc.11 Reference this number to order the full evaluation PCB.2The blank cells in the manufacturer column are left blank intentionally for they are user-selectable.Product OverviewOnlineDocumentation Design ResourcesDiscussionSample & BuyData SheetHMC1118Rev. 0 | Page 11 of 11OUTLINE DIMENSIONS0.080.95FOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONSSECTION OF THIS DATA SHEET.01-08-2015-A000000*COMPLIANT WITH JEDEC STANDARDS MO-220-VEED-4WITH THE EXCEPTION OF PACKAGE EDGE TO LEAD EDGE.Figure 20. 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ]3 mm × 3 mm Body, Very Very Thin Quad(CP-16-38)Dimensions shown in millimeters1 HMC1118LP3DE and HMC1118LP3DETR are RoHS-Compliant Parts.2See the Absolute Maximum Ratings section. 3XXXX is the 4-digit lot number.©2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D12961-0-10/15(0)。

基于MB90092型专用字符叠加电路的视频监控系统的设计与实现

再显示 ,从而检测出被监控方高科技人员随意拆动 监控头系统的行为,有效防止了因信号传输线路被

随意改 动而导 致伪 图像 的 引入 。本系 统能 在一些 要 求 较 高 且 监 视 背

态 伪 随机符 号 的方法 防止系 统在 运行 时监控 头被 拆

卸。 一旦 线路 被拆 动 , 主监控 端给 出 的确认标 识将 不

便使用人员知道该图像信息以何种方式来 自何处及

与之相 关 的信息, 时间, 区徽标 , 时数 据显 示 如 地 实 在 屏幕上 。但是 对 于监 控人 员 而 言 。 控 端遭 到 攻 监 击 是一个 值得担 心 的问题 。因此, 技术方 案 和增 改善 强安 全性 是对 目前状 况提 出 的一 种迫 切要 求 。监 控

t e e a t e so g p e e n r mo e c n r ll O wi e g a a t e . h x cn s fi e a p a d o e t o t O m l b u r n e d ma r o l

Ke wo d : B 0 9 ; vd oc aa trs p rmp st n; mo i rsse ; d sg y rs M 90 2 ie h r ce u ei o i o i nt y tm o ein

a yfo o u p s t c fhg —e h p ro so h emia r nr d c d。 Usn hsmeh d, wa m n p ro eat k o ih tc e sn n te tr n laei t u e r a o ig ti t o

1 引 言

随着监 控现 场 的扩展 和探 头数 量增 多 。 在监 控 端 的图像 显示 系统 中, 常需要 接 收外 部 数据 并 把 经 相 关 的信 息实 时地 连 同 图像 显 示在 监 控屏 幕上 , 以

MB90092 寄存器BIT的含义

Command 3 (VRAM Write Control)FIL : VRAM fill controlFIL = 0:Do not fill VRAM.FIL = 1: Fill VRAM.Command 5 (Screen Control 2)KID : Halftone controlKID = 0 : Perform normal display, disabling halftone display.APC : APC controlAPC = 1 : Turn the APC function ONGYZ : Main screen line enlargement controlBH2 to BH0 : Color phase control Color phase offset 45 degreesW3 to W0 : Main screen line spacing controlCommand 7 (Main Screen Vertical Display Position Control)EC : Sync signal output controlLP : Simple NTSC/PAL controlLP = 0 : Normal operationLP = 1 : Simple NTSC/PAL operationFO : Color phase signal(FSCO pin)output controlY5 to Y0 : Main screen vertical display position control (in dot units)Command 8 (Main Screen Horizontal Display Position Control)SC : Sync signal input control bitSC = 1 : Set the EXHSYN pin as a horizontal sync signal input and the EXVSYN pin as a vertical sync signal input.FC : Sync signal input 3 s filter controlX5 to X0 : Main screen horizontal display position controlCommand 9 (Kanji Font Display Control)GRM : Main screen display mode controlGRM = 0 : Display the main screen in normal mode.The main screen can display only normal characters.The character background color can be set for each character Command 10 (Color Control)RB : Main screen solid-fill background display controlBK : Main screen blink display controlCC : Main screen character color/monochrome controlBC : Main screen character background color/monochrome control(Main screen graphic color/monochrome control)UC : Screen background color/monochrome controlUG, UR, UB : Screen background colorCommand 4 (Screen Control 1)IE : Internal/external synchronization controlIN : Interlaced/noninterlaced display controlEB : Screen background display controlEO : Field controlCM : Color/monochrome display controlZM : Zoom-in controlNP : NTSC/PAL controlNP = 0: Output display signals using the NTSC system.NP = 1: Output display signals using the PAL system.P2, P0 : Pattern background controlDC : Display controlDC = 1: Enable display output operation.Command 0 (VRAM Address Setting)VSL : VRAM write controlRA8 to RA5 : VRAM row address setting (00 to B H)CA4 to CA0 : VRAM column address setting (00 to 17H)Main Screen Sharacter Control Data Write (If VSL = 0 in Command 0)Command 1-1 (Main screen character control data setting 1)Command 2-1 (Main screen character control data setting 2)(MD), MC to M0 : Character codeAT : Specify character attribute display.CG, CR, CB : Character colorsBG, BR, BB : Character background colors(GR) : Specify normal character/graphic character display(BS) : Specify shaded background display.Writing Sub-screen Line Control Data (When Command 0:VSL = 1, CA0 = 0)Set sub-screen line control data.Command 1-2 (Sub-screen line control data setting 1)Command 2-2 (Sub-screen line control data setting 2)SMD to SM0 : Sub-screen line first character codeSDC : Sub-screen line output controlSGR : Sub-screen line character display controlSCG to SCB : Sub-screen line character colors (when SGR = 0)SCG : Sub-screen line graphic color transparency control (when SGR = 1)SCR, SCB : Sub-screen line graphic color phase control (when SGR = 1)Main Screen Line Control Data Write (If VSL = 1 and CA0 = 1in Command 0)This command sets the line control data of the main screen.Command 1-3 (Main screen line control data setting 1)Command 2-3 (Main screen line control data setting 2)OF1, OF0 : Character color phase controlPC : Shaded pattern background color/monochrome controlPG, PR, PB : Shaded pattern background colorG2, G1, G0 : Character size controlSOC : Output priority controlVD : Video signal output controlDG : Digital signal output controlKC : Line background color/monochrome controlKG, KR, KB : Line background colorCommand 11 (Sub-Screen Control)SG2 to SG0 : Sub-screen configuration controlSCC : Sub-screen character color/monochrome controlSBC : Sub-screen character background color/monochrome controlSGC : Sub-screen graphic color/monochrome controlSBG, SBR, SBB : Sub-screen pattern background colorCommand 12 (Sub-Screen Vertical Position Control) SGA : Sub-screen full-screen mode controlSY7 to SY0 : Sub-screen vertical display positionCommand 13 (Sub-Screen Horizontal Position Control) SX8 to SX0 : Sub-screen horizontal display position。

基于MB90092的电梯楼层显示器设计

实现 了将 电梯 当前 所处 楼层相 关信 息动 态实时 叠加 至视频 信号 的功 能 , 时还 能检 测 视频 信 号 的有 无 , 而便 于 保安 监 控人 员 及 时 同 从

处理有 关情 况。应 用结果 表 明 , 系统 运行 稳定 可靠 、 该 编程 简单 、 可维 护性 和可扩 充性 都较 强 。 关键词 :智 能 电磁干扰

状态 ;

⑨ 可 以设置 1 1 ~ 2个字符 的电梯名称 ; ⑩ 自带 国标一 、 二级汉字库。

1 电梯楼 层显 示器 的总体 方案

电梯楼层显 示 器采 用 双 A 8 S2单 片机 作 为 主 T95

要 控 制 芯 片, 与 MB 0 9 、 M18 、 M2 F 8 B 9 0 2 L 8 1 A 9 00 、

和 粤铭 徐 支 影 高 嵩 索 勋 胡 j } l

( 长春理 工 大学 电子信 息工 程学 院 , 吉林 长春 10 2 ) 3 0 2

摘

要 :介绍 了基 于 M 9 0 2型专 用视 频字符 叠加 芯片 的电梯 楼层 显示 器 的硬件 与 软件 设 计 , 合 双 A 8 S 2核 心 的单 片机 系统 , B 09 结 T 95

中图分 类号 :T 2 7 P7

可 靠性

A 8 S 2 频信 号 T9 5 视

动态 实时

安保 监控

文献 标志码 :B

Ab ta t: Had r n ot r e in o i try mo io n ipa ae n MB9 0 2,te d dc td I tx n r p i v rad I sr c r wa ea d s f waed sg fa l soe n tr g d s ly b s d o t f i 09 h e iae C e ta d g a hc o ell C

290 Series Waveform Generators说明书

290 Series Waveform GeneratorsArbitrary WaveformsWaveforms The maximum arbitrary waveform size is 1 M points. Up to 500 user-definedwaveforms may be stored on the removable memory card. Arbitrarywaveforms can be defined by front panel editing controls, by downloading ofwaveform data via RS-232,USB or GPIB, or by writing directly to theremovable memory card using the USB card reader/writer connected to aPC.Waveform memory 1 M points. Minimum waveform size is 8 points.Vertical resolution 12 bitsSample clock range 100 mHz to 100 MHzResolution 4 digitsAccuracy ± 1 digit of settingOutput filter Selectable between 40 MHz Elliptic, 20 MHz Bessel or noneSequence Up to 1024 waveforms may be linked. Each waveform can have a loopcount of up to 32,768. A sequence of waveforms can be looped up to1,048,575 times or run continuously.Noise function Digital noise generated by a 35-bit linear feedback register clocked at 100MHz. User’s external filter defines bandwidth and responseStandard WaveformsWaveforms Sine, square, triangle, DC, positive ramp, negative ramp, sin(x)/x, pulse,pulse train, cosine, haversine and havercosineSine, Cosine, Haversine, HavercosineRange 0.1 mHz to 40 MHzResolution 0.1 mHz or 10 digitsAccuracy Better than 10 ppm for 1 yearTemperature stability Typically < 1 ppm/°COutput level 5 mV to 20 V p-p from 50 ΩHarmonic distortion < 0.15 % THD to 100 kHz; < –60 dBc to 20 kHz, < –50 dBc to 1 MHz, < –40dBc to 10 MHz, < –30 dBc to 40 MHzNon-harmonic spurii < –60 dBc to 1 MHz, < –60 dBc + 6 dB/octave 1 MHz to 40 MHzSquareRange 1 mHz to 50 MHzResolution 1 mHz (4 digits)Accuracy ± 1 digit of settingOutput level 5 mV to 20 V p-p from 50 ΩRise and fall times < 8 nsTriangleRange 0.1 mHz to 500 kHzResolution 0.1 mHz or 10 digitsAccuracy Better than 10 ppm for 1 yearOutput level 5 mV to 20 V p-p from 50 Ω, linearity error: < 0.1 % to 30 kHzRamps and Sin(x)/xRange 0.1 mHz to 500 kHzResolution 0.1 mHz or 10 digitsAccuracy Better than 10 ppm for 1 yearOutput level 5 mV to 20 V p-p from 50 ΩLinearity error < 0.1 % to 30 kHzPulse and Pulse TrainOutput level 5 mV to 20 V p-p from 50 ΩRise and fall times < 8 nsPeriod Range: 40 ns to 100 s; Resolution: 4-digits; Accuracy: ± 1 digit of setting Delay Range: –99.9 s to + 99.99 s; Resolution: 0.001 % of period or 10 nsWidth Range: 10 ns to 99.99 s; Resolution: 0.001 % of period or 10 nsTrains of up to 10 pulses may be specified, each having independently defined width, delay and level. The baseline voltage is separately defined and the sequence repetition rate is set by the pulse train period.Operating ModesContinuous Waveform runs continuouslyTriggered Burst Each active edge of the trigger signal will produce one burst of thewaveformCarrier waveforms All standard and arbitraryMax. carrier frequency The smaller of 2.5 MHz or the maximum for the selected waveform. 100Msamples/s for ARB or Sequence.Number of Cycles 1 to 1048575Trigger rep. rate 0.005 Hz to 100 kHz internal, dc to 1 MHz externalTrigger source Internal from keyboard or trigger generator. External from TRIG IN orremote interface.Start/stop phase ± 360 ° settable with 0.1 ° resolution, subject to waveform frequency andtypeGated Waveform will run while the Gate signal is true and stop while false Carrier waveforms All standard and arbitraryMax. carrier frequency The smaller of 2.5 MHz or the maximum for the selected waveform. 80Msamples/s for ARB or Sequence.Trigger rate 0.005 Hz to 100 kHz internal, dc to 1 MHz externalGate signal source Internal from keyboard or trigger generator. External from TRIG IN orremote interface.Start/stop phase ± 360 ° settable with 0.1 ° resolution, subject to waveform frequency andtypeSweep Capability provided for both standard and arbitrary waveforms.Arbitrary waveforms are expanded or condensed to exactly 4096points and DDS techniques are used to perform the sweep.Carrier waveforms All standard and arbitrary except pulse, pulse train and sequence. Sweepmode: Linear or logarithmic, continuous or triggered.Sweep direction Up, down, up/down or down/upSweep range 1 mHz to 40 MHz in one range. Phase continuous. Independent setting ofstart/stop frequency.Sweep time 1 ms to 999 s (3 digit resolution)Marker Variable during sweep.Sweep trig. Source The sweep may be free run or triggered from the following sources:Manually from keyboard. Externally from TRIG IN input or remote interface. Sweep hold Sweep can be held and restarted by HOLD keyTone Switching Capability provided for both standard and arbitrary waveforms.Arbitrary waveforms are expanded or condensed to exactly 4096points and DDS techniques used to allow instantaneous frequencyswitching.Carrier waveforms All waveforms bar pulse, pulse train, sequenceFrequency list Up to 16 frequencies from 1 mHz to 40 MHzTrigger rep. rate 0.005 Hz to 100 kHz internal, dc to 1 MHz external. Usable repetition rateand waveform frequency depend on the tone switching mode.Source Internal from keyboard or trigger generator. External from TRIG IN orremote interface.Tone switching modesGated The tone is output while the trigger signal is true and stopped, at the end ofthe current waveform cycle, while the trigger signal is false. The next tone isoutput when the trigger signal is true again.Triggered The tone is output when the trigger signal goes true and the next tone isoutput, at the end of the current waveform cycle, when the trigger signalgoes true again.FSK The tone is output when the trigger signal goes true and the next tone isoutput, immediately, when the trigger signal goes true again.External Amplitude ModulationCarrier frequency Entire range for selected waveformCarrier waveforms All standard and arbitrary waveformsModulation source Modulation socketFrequency range DC to 500 kHzSignal range Approx. 1 V pk-pk for 100 % level change at maximum outputExternal Signal SummingCarrier frequency Entire range for selected waveformCarrier waveforms All standard and arbitrary waveformsSum source Sum socketFrequency range DC to 16 MHzSignal range Approximately 2 Vpk-pk input for 20 Vpk-pk output.Trigger GeneratorSource Internal source 0.005 Hz to 100 kHz squarewave adjustable in 10 us steps.3 digit resolution. Available for external use from the SYNC OUT socket. Main Outputs – One for each channelOutput impedance 50 ΩAmplitude 5 mV to 20 V pk-pk open circuit (2.5 mV to 10 V pk-pk into 50 Ω. Amplitudecan be specified open circuit (Hi Z) or into an assumed load of 50 Ωor 60 Ω,in Vpk-pk, Vrms or dBm.Ampl. accuracy Better than 2 % ± 1 mV at 1 kHz into 50 Ω.Ampl. flatness ± 0.2 dB to 1 MHz; ± 0.4 dB to 40 MHzDC offset range ± 10 V. DC offset plus signal peak limited to ± 10 V from 50 Ω. Offset accuracy Typically within ± 3 % ± 10 mV, unattenuatedResolution 3 digits or 1 mV for both Amplitude and DC OffsetSync Out – One for each channel Multifunction output user definable or automatically selected to be any of the following:Waveform sync (All waveforms) A square wave with 50 % duty cycle at the main waveform frequency, or a pulse coincident with the first few points of an arbitrary waveform.Position markers (Arbitrary only) Any point(s) on the waveform may have associated marker bit(s) set high or lowBurst done Produces a pulse coincident with the last cycle of a burstSequence sync Produces a pulse coincident with the end of a waveform sequenceTrigger Selects the current trigger signal. Useful for synchronising burst or gatedsignals.Sweep sync Outputs a pulse at the start of sweep to synchronise an oscilloscope orrecorder. Can additionally output a sweep marker.Phase lock out Used to phase lock two generators. Produces a positive edge at the 0ophase point.Output signal level Logic level of < 0.8 V to > 3 V for all outputs except Sweep Sync. SweepSync is a 3-level waveform.Trig InFrequency range DC to 1 MHzSignal range Threshold nominally TTL level; max. input ± 10 VMin. rulse width 50 ns for Trigger and Gate modes; 50 µs for Sweep modeInput impedance 10 kΩModulation InFrequency range DC to 500 kHzSignal range VCA: Approximately 1 Vpk-pk for 100 % level change at maximum outputSCM: Approximately ± 1 Vpk for maximum outputInput impedance Typically 1 kΩSum InFrequency range DC to 30 MHz (291) DC to 16 MHz (292/294)Signal range Approximately 2 Vpk-pk input for 20 Vpk-pk outputInput impedance Typically 1 kΩHold Holds an arbitrary waveform at its current position. A TTL low level or switchclosure causes the waveform to stop at the current position and wait until aTTL high level or switch opening which allows the waveform to continue.The front panel MAN/HOLD key or remote command may also be used tocontrol the Hold function.Input impedance 10 kΩRef Clock In/OutSet to input Input for an external 10 MHz reference clock. TTL/CMOS threshold level. Set to output Buffered version of the internal 10 MHz clock. Output levels nominally 1 Vand 4 V from 50 Ω.Set to phase lock Used together with SYNC OUT on a master and the TRIG IN on a slave tosynchronize (phase lock) two generators ARB Clock InFrequency Range DC to 50 MHzMax. input voltage + 5 V, -1 VInter-Channel OperationInter-Channel Modulation The waveform from any channel may be used to Amplitude Modulate (AM) or Suppressed Carrier Modulate (SCM) the next channel. Alternatively any number of channels may be Modulated (AM or SCM) with the signal at the MODULATION input socket.Carrier frequency Entire range for selected waveformCarrier waveforms All standard and arbitrary waveformsModulation types AM: Double sideband with carrierSCM: Double sideband suppressed carrierModulation source Internal from the previous channel. External from Modulation input socket.The external modulation signal may be applied to any number of channelssimultaneouslyFrequency range DC to > 100 kHzInternal AM depth 0 % to 105 %Internal AM resolution 1 %Carrier Suppression(SCM)> 40 dBExternal modulation signal range VCA: Approximately 1 V pk-pk for 100 % level change at maximum output SCM: Approximately ± 1 Vpk for max. outputInter-Channel Analogue Summing Waveform Summing sums the waveform from any channel into the next channel. Alternatively any number of channels may be summed with the signal at the SUM input socket.Carrier frequency Entire range for selected waveformCarrier waveforms All standard and arbitrary waveformsSum source Internal from the previous channel. External from SUM IN socket. Frequency range DC to > 16 MHzExt. signal range Approx. 5 Vpk-pk input for 20 Vpk-pk outputInter-Channel Phase Locking Two or more channels may be phase locked together. Each locked channel may be assigned a phase angle relative to the other locked channels. Arbitrary waveforms and waveform sequences may be phase locked but certain constraints apply to waveform lengths and clock frequency ratios.With one channel assigned as the Master and other channels as Slaves a frequency change on the master will be repeated on each slave thus allowing multiphase waveforms at the same frequency to be easily generated. DDS waveforms are those with 7 digits of frequency setting resolution, while Non-DDS waveforms have 4 digits.Phase resolution DDS waveforms: 0.1 degreeNon-DDS waveforms 0.1 degree or 360 degrees/number of points whichever is the greater Phase error < ± 10 ns all waveforms.Inter-Channel Triggering Any channel can be triggered by the previous or next channel. The previous/next connections can be used to ‘daisy chain’ a trigger signal from a ‘start’ channel, through a number of channels in the ‘chain’ to an ‘end’ channel.Each channel receives the trigger out signal from the previous (or next) channel, and drives its selected trigger out to the next (orprevious) channel. The ‘end’ channel trigger out can be set up to drivethe ‘start’ channel, closing the loop.In this way, complex and versatile interchannel trigger schemes maybe set up. Each channel can have its trigger out and its outputwaveform set up independently. Trigger out may be selected fromWaveform End, Position Markers, Sequence Sync or Burst Done.Using the scheme above it is possible to create a sequence of up to 64waveform segments, each channel producing up to 16 segments andall channels being summed to produce the complete waveform at theoutput of channel 4.The signals from the REF IN/OUT socket and the SYNC OUT socketcan be used to phase lock two instruments where more than 4channels are required.InterfacesRS-232 Variable Baud rate, 9600 Baud maximumIEEE488 Conforms with IEEE488.2USB Conforms with USB 1.1General SpecificationsDisplay 20 character x 4 row alphanumeric LCDData entry Keyboard selection of mode, waveform etc.; value entry by numeric keys orby rotary control.Memory card Removable memory card conforming to the Compact Flash memory cardstandard. Sizes from 32 MB to 1 GB can be used.Stored settings Up to 500 complete instrument set-ups may be stored and recalled from thememory card. Up to 500 arbitrary waveforms can also be storedindependent of the instrument settings.Size 130 mm (3U) high; 335 mm long; 350 mm wide (292/294), 212 mm wide(291)Weight 292/294: 7.2 kg (16 lb); 291: 4.1 kg (9 lb)Power 110 to 120 V or 100 V nominal 50/60/400 Hz; 220 to 240 V nominal, 50/60Hz. Voltage adjustable internally; operating range ± 10 % of nominal; 60 VAmax. Installation Category II.ComplianceOperating range +5 °C to 40 °C, 20 to 80 % RHStorage range –20 °C to +60 °CEnvironmental Indoor use at altitudes to 200 m, Pollution Degree 2Safety Complies with EN61010-1EMC Complies with EN61326Instrument drivers Labview and LabWindows CVI drivers are either supplied with theinstrument or are available via your local Fluke OfficeSupplied Items IEC Mains Lead. Printed manual (partly multi-language), multi-languagemanual on CD, Waveform Manager Plus software, compact Flash memorycard, compact Flash card reader/writer (USB connection to PC)Options 19-inch rack mounting kit。

基于OSD控制器MB90092的一种视频安全通信系统设计

20 0 9年 1 2月

苏

州

大

学

学

报( 工

科

版)

V 12 No 6 o. 9 . De . O 9 c2O

J RNAL OF S HOU UNI OU UZ VERST ENGI IY( NEERI NG CI S ENCE EDII T ON)

2 1 电源时钟模 块 .

电路 工作 电压为 5 C, V D 由稳 压芯 片 L85提供 。时钟 模 块 由频 率 为 1MH 和 1.3 MH 的 两无 源 70 2 z 7 744 z 晶振 组成 , 分别 为微控 制模 块 主芯 片 A 8C 1以及 字符 叠加模 块 主芯 片 MB 0 9 T95 90 2提供 工作 时钟频 率 。

2 2 视频 信号 同步分 离模 块 .

视频 信号来 自监 控现 场 的监控摄 像 头 , 占用 带 宽 为 6 5 z 除 图像 信 号外 , 其 . MH , 还包 括 行 场 同步 信 号 、 消 隐信 号 、 脉 冲信号及 前后 均衡 脉 冲等 , 槽 以消 隐 电平 为零 电平 基准 点 。行 、 同步 脉 冲是 字 符显 示 的基 准 , 场 所 以输 入 的视 频 信号 先经 同步分 离 电路 分 离 出行 场 同步脉 冲。视 频 同步 分离 器 采用 N t n l e cn u t 公 ai a S mi d co o o r

全性 能要 求较 高的场合 , 物馆 、 行 、 如博 银 海关 以及公 司仓库等 。

1 系统 工作 原理

视频字 符叠加技 术是 指在 视频上 附着图形或 字符信号 , 从而在屏 幕 的特定位置上 与 图像 信号进行 同时显

示, 这项技术是 应用 电视 技术 中的一个重要 领域 , 应用 电视 系统 中发挥着重 要 的作 用 , 在 现将其 用于视频监 控 系统 , 得视频监 控 、 使 通信更 为安全 可靠 。如 图 1 所示 , 系统在 监控 摄像 头处 附 加 电路 , 用伪 随机 序列 编 本 采 码显示各 种类型 的图形或字 符 , 而远 程监控 中心也采用 与之相对 应 的伪 随机序列 编码来 检测各种类 型 的图形

MB90092芯片在成像测井字符叠加中的应用

M 902 以很方便的把这些相关信息通过应用 B 09 可

文字 叠加 到视频 图像 中.

MB 09 902由串行输入 控制 电路 、T A P L信 N S /A

号 发生器 电路 、 显示 存储 器 V A R M控 制 电路 、 显示

1 MB 0 9 9 0 2简 介

MB 09 902是 一 款 专 用 的视 频 字 符 叠 加 芯 片 ,

硬件 各部 分 的功能 描述如 下 :

1 )视频 同步分离 : 用 L 8 14同步 分离器 利 M1 8 ] E

计时 , 把相 应 的时 间通 过 字 符 叠 加 到视 频 信 号 中 输 出 , 录测 井 时间 , 记 以便对 测井 资料存 档 . 3 )字 符 叠 加 : 90 2是 该 系 统 的核 心 , MB 0 9 接

[ ] F JS 公 司. N—C R E IP A O T O L R 1 U IU O S E N D S L Y C N R L E

始化 控制 也 是 该 系 统 软 件 控 制 的主 要 工 作 , 面 下

介绍根据 M 902的时序图对其发送数据和命令 B 09

以及 对其 寄存器 的设 置 .

[ ] 刘艳 滢 , 2 李桂 菊 , 田睿 , 等.基 于 MB 09 9 02的实时图 像显示 系统 的设计 [ ] 长春理工大学学报 ,0 4 2 J. 20 ,7

( ) 49 . 1 :9 —6

中利用 8 C 1的通用 IO口模 拟串行 通信 , 95 / 利用

软件 来 实 现模 拟 S I 式 进 行 通 信 , 括 串 行 时 P方 包 钟、 串行数 据输 入/ 出及 片选 信号 . 输 2 )寄存 器 的设 置 : 寄存 器 的设 置 主要包 括 : 对 同步方式 、 频制式 、 符大小 、 视 字 字符 的颜 色和 背

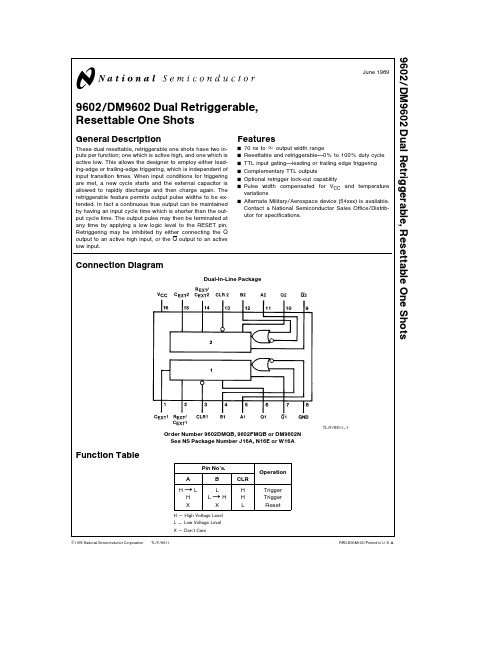

9602FMQB资料

Connection Diagram

Dual-In-Line Package

TL F 6611 – 1

Order Number 9602DMQB 9602FMQB or DM9602N See NS Package Number J16A N16E or W16A

Function Table

Pin No’s A HxL H X B L LxH X CLR H H L Trigger Trigger Reset Operation

b 65 C to a 150 C

Note The ‘‘Absolute Maximum Ratings’’ are those values beyond which the safety of the device cannot be guaranteed The device should not be operated at these limits The parametric values defined in the ‘‘Electrical Characteristics’’ table are not guaranteed at the absolute maximum ratings The ‘‘Recommended Operating Conditions’’ table will define the conditions for actual device operation

24 04 0 45 60

b1 6 b1 6 b 1 24 b 1 41 b 25 b 35

VOL

V mA

IIH IIL

mA

IOS ICC

Short Circuit Output Current Supply Current

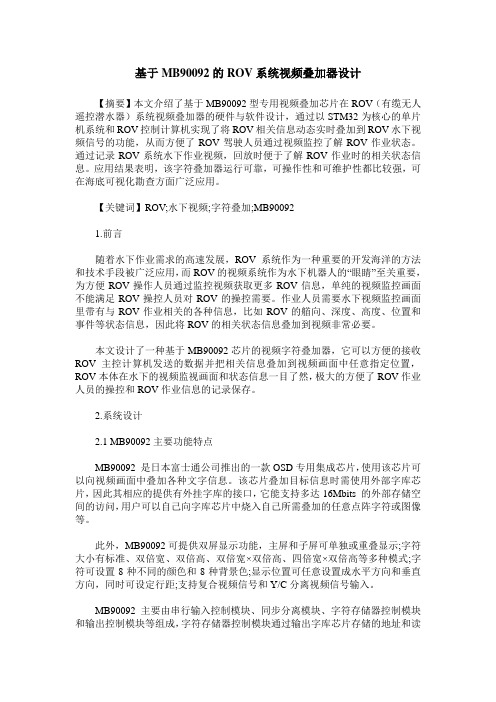

基于MB90092的ROV系统视频叠加器设计

基于MB90092的ROV系统视频叠加器设计【摘要】本文介绍了基于MB90092型专用视频叠加芯片在ROV(有缆无人遥控潜水器)系统视频叠加器的硬件与软件设计,通过以STM32为核心的单片机系统和ROV控制计算机实现了将ROV相关信息动态实时叠加到ROV水下视频信号的功能,从而方便了ROV驾驶人员通过视频监控了解ROV作业状态。

通过记录ROV系统水下作业视频,回放时便于了解ROV作业时的相关状态信息。

应用结果表明,该字符叠加器运行可靠,可操作性和可维护性都比较强,可在海底可视化勘查方面广泛应用。

【关键词】ROV;水下视频;字符叠加;MB900921.前言随着水下作业需求的高速发展,ROV系统作为一种重要的开发海洋的方法和技术手段被广泛应用,而ROV的视频系统作为水下机器人的“眼睛”至关重要,为方便ROV操作人员通过监控视频获取更多ROV信息,单纯的视频监控画面不能满足ROV操控人员对ROV的操控需要。

作业人员需要水下视频监控画面里带有与ROV作业相关的各种信息,比如ROV的艏向、深度、高度、位置和事件等状态信息,因此将ROV的相关状态信息叠加到视频非常必要。

本文设计了一种基于MB90092芯片的视频字符叠加器,它可以方便的接收ROV主控计算机发送的数据并把相关信息叠加到视频画面中任意指定位置,ROV本体在水下的视频监视画面和状态信息一目了然,极大的方便了ROV作业人员的操控和ROV作业信息的记录保存。

2.系统设计2.1 MB90092主要功能特点MB90092 是日本富士通公司推出的一款OSD专用集成芯片,使用该芯片可以向视频画面中叠加各种文字信息。

该芯片叠加目标信息时需使用外部字库芯片,因此其相应的提供有外挂字库的接口,它能支持多达16Mbits 的外部存储空间的访问,用户可以自己向字库芯片中烧入自己所需叠加的任意点阵字符或图像等。

此外,MB90092可提供双屏显示功能,主屏和子屏可单独或重叠显示;字符大小有标准、双倍宽、双倍高、双倍宽×双倍高、四倍宽×双倍高等多种模式;字符可设置8种不同的颜色和8种背景色;显示位置可任意设置成水平方向和垂直方向,同时可设定行距;支持复合视频信号和Y/C分离视频信号输入。

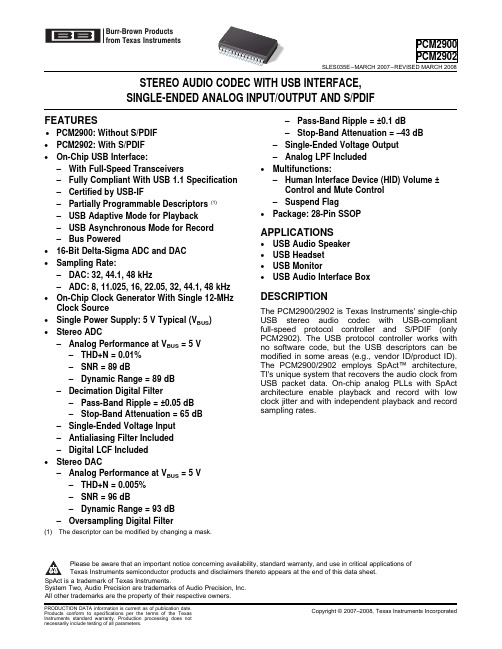

pcm2900数据手册

BurrĆBrown Productsfrom TexasInstrumentsFEATURESAPPLICATIONSDESCRIPTIONPCM2900PCM2902SLES035E–MARCH2007–REVISED MARCH2008 STEREO AUDIO CODEC WITH USB INTERFACE,SINGLE-ENDED ANALOG INPUT/OUTPUT AND S/PDIF–Pass-Band Ripple=±0.1dB•PCM2900:Without S/PDIF–Stop-Band Attenuation=–43dB•PCM2902:With S/PDIF–Single-Ended Voltage Output•On-Chip USB Interface:–Analog LPF Included –With Full-Speed Transceivers•Multifunctions:–Fully Compliant With USB1.1Specification–Human Interface Device(HID)Volume±Control and Mute Control –Certified by USB-IF–Suspend Flag–Partially Programmable Descriptors(1)•Package:28-Pin SSOP–USB Adaptive Mode for Playback–USB Asynchronous Mode for Record–Bus Powered•USB Audio Speaker•16-Bit Delta-Sigma ADC and DAC•USB Headset•Sampling Rate:•USB Monitor–DAC:32,44.1,48kHz•USB Audio Interface Box–ADC:8,11.025,16,22.05,32,44.1,48kHz•On-Chip Clock Generator With Single12-MHzClock Source The PCM2900/2902is Texas Instruments'single-chip •Single Power Supply:5V Typical(V BUS)USB stereo audio codec with USB-compliantfull-speed protocol controller and S/PDIF(only •Stereo ADCPCM2902).The USB protocol controller works with –Analog Performance at V BUS=5V no software code,but the USB descriptors can be–THD+N=0.01%modified in some areas(e.g.,vendor ID/product ID).The PCM2900/2902employs SpAct™architecture,–SNR=89dBTI's unique system that recovers the audio clock from –Dynamic Range=89dB USB packet data.On-chip analog PLLs with SpAct–Decimation Digital Filter architecture enable playback and record with lowclock jitter and with independent playback and record –Pass-Band Ripple=±0.05dBsampling rates.–Stop-Band Attenuation=65dB–Single-Ended Voltage Input–Antialiasing Filter Included–Digital LCF Included•Stereo DAC–Analog Performance at V BUS=5V–THD+N=0.005%–SNR=96dB–Dynamic Range=93dB–Oversampling Digital Filter(1)The descriptor can be modified by changing a mask.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications ofTexas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.SpAct is a trademark of Texas Instruments.System Two,Audio Precision are trademarks of Audio Precision,Inc.All other trademarks are the property of their respective owners.PRODUCTION DATA information is current as of publication date.Copyright©2007–2008,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasABSOLUTE MAXIMUM RATINGSPCM2900PCM2902SLES035E–MARCH 2007–REVISED MARCH 2008This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.PACKAGING ORDERING INFORMATIONPCM2900SPECIFIED PACKAGE PACKAGE ORDERING TRANSPORT PRODUCTPACKAGE-LEADTEMPERATUREDESIGNATORMARKING NUMBER (1)MEDIARANGE PCM2900E Rails PCM2900E SSOP-2828DB–25°C to 85°CPCM2900EPCM2900E/2KTape and reel(1)Models with a slash (/)are available only in tape and reel in the quantities indicated (e.g.,/2K indicates 2000devices per reel).Ordering 2000pieces of PCM2900E/2K gets a single 2000-piece tape and reel.PCM2902SPECIFIED PACKAGE PACKAGE ORDERING TRANSPORT PRODUCTPACKAGE-LEADTEMPERATUREDESIGNATORMARKING NUMBER (1)MEDIARANGE PCM2902E Rails PCM2902E SSOP-2828DB–25°C to 85°CPCM2902EPCM2902E/2KTape and reel(1)Models with a slash (/)are available only in tape and reel in the quantities indicated (e.g.,/2K indicates 2000devices per reel).Ordering 2000pieces of PCM2902E/2K gets a single 2000-piece tape and reel.over operating free-air temperature range (unless otherwise noted)(1)PCM2900/PCM2902UNIT V BUSSupply voltage–0.3to 6.5V Ground voltage differences,AGNDC,AGNDP,AGNDX,DGND,DGNDU ±0.1V SEL0,SEL1,TEST0(DIN)(2)–0.3to 6.5V Digital input voltage D+,D–,HID0,HID1,HID2,XTI,XTO,TEST1(DOUT)(2),SSPND –0.3to (V DDI +0.3)<4V V IN L,V IN R,V COM ,V OUT R,V OUT L –0.3to (V CCCI +0.3)<4V Analog input voltageV CCCI ,V CCP1I ,V CCP2I ,V CCXI ,V DDI–0.3to 4V Input current (any pins except supplies)±10mA Ambient temperature under bias–40to 125°C T stg Storage temperature –55to 150°C T JJunction temperature 150°C Lead temperature (soldering)260°C,5s Package temperature (IR reflow,peak)250°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)():PCM29022Submit Documentation Feedback Copyright ©2007–2008,Texas Instruments IncorporatedELECTRICAL CHARACTERISTICSPCM2900PCM2902 SLES035E–MARCH2007–REVISED MARCH2008all specifications at T A=25°C,V BUS=5V,f S=44.1kHz,f IN=1kHz,16-bit data,unless otherwise notedPCM2900E,PCM2902EPARAMETER TEST CONDITIONS UNITMIN TYP MAXDIGITAL INPUT/OUTPUTHost interface Apply USB Revision1.1,full speedAudio data format USB isochronous data formatINPUT LOGICD+,D–2 3.3XTI,HID0,HID1,and2.523.3High-level input HID2V IH VDC voltageSEL0,SEL12 5.25DIN,PCM2902 2.52 5.25D+,D–0.8XTI,HID0,HID1,and0.9Low-level input HID2V IL VDC voltageSEL0,SEL10.8DIN,PCM29020.9D+,D–,XTI,SEL0,±10SEL1High-level inputI IH V IN=3.3VµAvoltage HID0,HID1,and HID25080DIN,PCM290265100D+,D–,XTI,SEL0,±10SEL1Low-level inputI IL V IN=0VµAvoltage HID0,HID1,and HID2±10DIN,PCM2902±10 OUTPUT LOGICD+,D– 2.8High-level outputV OH DOUT,PCM2902I OH=–4mA 2.8VDC voltageSSPND I OH=–2mA 2.8D+,D–0.3 Low-level outputV OL DOUT,PCM2902I OL=4mA0.5VDC voltageSSPND I OL=2mA0.5CLOCK FREQUENCYInput clock frequency,XTI11.9941212.008MHz ADC CHARACTERISTICSResolution8,16bits Audio data channel1,2channelCopyright©2007–2008,Texas Instruments Incorporated Submit Documentation Feedback3ELECTRICAL CHARACTERISTICSPCM2900PCM2902SLES035E–MARCH 2007–REVISED MARCH 2008all specifications at T A =25°C,V BUS =5V,f S =44.1kHz,f IN =1kHz,16-bit data,unless otherwise notedPCM2900E,PCM2902E PARAMETERTEST CONDITIONSUNITMINTYPMAXCLOCK FREQUENCY 8,11.025,16,22.05,32,44.1,f SSampling frequencykHz48DC ACCURACY%of Gain mismatch,channel-to-channel ±1±5FSR %of Gain error ±2±10FSR %of Bipolar zero error±0FSRDYNAMIC PERFORMANCE (1)V CCCI =3.67V,V IN =–0.5dB (2)0.01%0.02%THD+NTotal harmonic distortion plus noise V IN =–0.5dB (3)0.1%V IN =–60dB 5%Dynamic rangeA-weighted 8189dB SNRSignal-to-noise ratio A-weighted8189dB Channel separation8085dBANALOG INPUTInput voltage 0.6V CCCI V p-p Center voltage 0.5V CCCIV Input impedance30k Ω–3dB 150kHz Antialiasing filter frequency responsef IN =20kHz–0.08dBDIGITAL FILTER PERFORMANCEPass band 0.454f SHz Stop band 0.583f SHz Pass-band ripple ±0.05dB Stop-band attenuation65dB t dDelay time17.4/f S s LCF frequency response–3dB0.078f SMHzDAC CHARACTERISTICSResolution 8,16bits Audio data channel1,2channelCLOCK FREQUENCY f S Sampling frequency32,44.1,48kHz(1)f IN =1kHz,using a System Two™audio measurement system by Audio Precision™in the RMS mode with 20-kHz LPF,400-Hz HPF in calculation.(2)Using external voltage regulator for V CCCI (as shown in Figure 36and Figure 37,using with REG103xA-A)(3)Using internal voltage regulator for V CCCI (as shown in Figure 38Figure 39)4Submit Documentation Feedback Copyright ©2007–2008,Texas Instruments IncorporatedELECTRICAL CHARACTERISTICSPCM2900PCM2902 SLES035E–MARCH2007–REVISED MARCH2008all specifications at T A=25°C,V BUS=5V,f S=44.1kHz,f IN=1kHz,16-bit data,unless otherwise notedPCM2900E,PCM2902EPARAMETER TEST CONDITIONS UNITMIN TYP MAXDC ACCURACY%of Gain mismatch channel-to-channel±1±5FSR%of Gain error±2±10FSR%of Bipolar zero error±2FSR DYNAMIC PERFORMANCE(1)V OUT=0dB0.005%0.016%THD+N Total harmonic distortion plus noiseV OUT=–60dB3% Dynamic range EIAJ,A-weighted8793dB SNR Signal-to-noise ratio EIAJ,A-weighted9096dB Channel separation8692dB ANALOG OUTPUTV O Output voltage0.6V CCCI V p-p Center voltage0.5V CCCI VLoad impedance AC coupling10kΩ–3dB250kHz LPF frequency responsef=20kHz–0.03dB Digital filter performancePass band0.445f S HzStop band0.555f S HzPass-band ripple±0.1dBStop-band attenuation–43dBt d Delay time14.3f S s POWER SUPPLY REQUIREMENTSV BUS Voltage range 4.355 5.25VDCADC,DAC operation5667mA Supply currentSuspend mode(2)210µAADC,DAC operation280352P D Power dissipation mWSuspend mode(2) 1.05Internal power supply V CCCI,V CCP1I,V CCP2I,3.25 3.35 3.5VDCvoltage V CCXI,and V DDITEMPERATURE RANGEOperation temperature–2585°CθJA Thermal resistance100°C/W(1)f OUT=1kHz,using a System Two audio measurement system by Audio Precision in the RMS mode with20-kHz LPF,400-Hz HPF.(2)Under USB suspend stateCopyright©2007–2008,Texas Instruments Incorporated Submit Documentation Feedback5 PIN ASSIGNMENTS1 2 3 4 5 6 7 8 9 10 11 12 13 1428 27 26 25 24 23 22 21 20 19 18 17 16 15D+D–VBUS DGNDUHID0HID1HID2SEL0SEL1VCCCI AGNDCV LINV RINVCOMSSPNDTEST0VCCXIAGNDXXTOVCCP2IDGNDVCCP1IV LOUTXTITEST1VDDIAGNDPV ROUTPCM2900(Top View)12345678910111213142827262524232221201918171615D+D–VBUSDGNDUHID0HID1HID2SEL0SEL1VCCCIAGNDCV LINV RINVCOMSSPNDDINVCCXIAGNDXXTOVCCP2IDGNDVCCP1IV LOUTXTIDOUTVDDIAGNDPV ROUTP0007-06PCM2902(Top View)PCM2900PCM2902SLES035E–MARCH2007–REVISED MARCH20086Submit Documentation Feedback Copyright©2007–2008,Texas Instruments IncorporatedPCM2900PCM2902SLES035E–MARCH2007–REVISED MARCH2008 PCM2900TERMINAL FUNCTIONSTERMINALI/O DESCRIPTIONNAME NO.AGNDC11–Analog ground for codecAGNDP18–Analog ground for PLLAGNDX22–Analog ground for oscillatorD–2I/O USB differential input/output minus(1)D+1I/O USB differential input/output plus(1)DGND26–Digital groundDGNDU4–Digital ground for USB transceiverHID05I HID key state input(mute),active-high(2)HID16I HID key state input(volume up),active-high(2)HID27I HID key state input(volume down),active-high(2)SEL08I Must be set to high(3)SEL19I Must be set to high(3)SSPND28O Suspend flag,active-low(Low:suspend,High:operational)TEST024I Test pin,must be connected to GNDTEST125O Test pin,must be left openV BUS3–Connect to USB power(V BUS)V CCCI10–Internal analog power supply for codec(4)V CCP1I17–Internal analog power supply for PLL(4)V CCP2I19–Internal analog power supply for PLL(4)V CCXI23–Internal analog power supply for oscillator(4)V COM14–Common for ADC/DAC(V CCCI/2)(4)V DDI27–Internal digital power supply(4)V IN L12I ADC analog input for L-channelV IN R13I ADC analog input for R-channelV OUT L16O DAC analog output for L-channelV OUT R15O DAC analog output for R-channelXTI21I Crystal oscillator input(5)XTO20O Crystal oscillator output(1)LV-TTL level(2) 3.3-V CMOS-level input with internal pulldown.This pin informs the PC of serviceable control signals such as mute,volume up,orvolume down,which have no connection with the internal DAC or ADC directly.See the Interface#3and End-Points sections.(3)TTL Schmitt trigger,5-V tolerant(4)Connect a decoupling capacitor to GND.(5) 3.3-V CMOS-level inputCopyright©2007–2008,Texas Instruments Incorporated Submit Documentation Feedback7PCM2900PCM2902SLES035E–MARCH 2007–REVISED MARCH 2008PCM2902TERMINAL FUNCTIONSTERMINAL I/O DESCRIPTIONNAME NO.AGNDC 11–Analog ground for codec AGNDP 18–Analog ground for PLL AGNDX 22–Analog ground for oscillatorD–2I/O USB differential input/output minus (1)D+1I/O USB differential input/output plus (1)DGND 26–Digital groundDGNDU 4–Digital ground for USB transceiver DIN 24I S/PDIF input (2)DOUT 25O S/PDIF outputHID05I HID key state input (mute),active high (3)HID16I HID key state input (volume up),active high (3)HID27I HID key state input (volume down),active high (3)SEL08I Must be set to high (4)SEL19I Must be set to high (4)SSPND 28O Suspend flag,active-low (Low:suspend,High:operational)V BUS 3–Connect to USB power (V BUS )V CCCI 10–Internal analog power supply for codec (5)V CCP1I 17–Internal analog power supply for PLL (5)V CCP2I 19–Internal analog power supply for PLL (5)V CCXI 23–Internal analog power supply for oscillator (5)V COM 14–Common for ADC/DAC (V CCCI /2)(5)V DDI 27–Internal digital power supply V IN L 12I ADC analog input for L-channel V IN R 13I ADC analog input for R-channel V OUT L 16O DAC analog output for L-channel V OUT R 15O DAC analog output for R-channel XTI 21I Crystal oscillator input (6)XTO 20OCrystal oscillator output(1)LV-TTL level(2) 3.3-V CMOS-level input with internal pulldown,5-V tolerant(3) 3.3-V CMOS-level input with internal pulldown.This pin informs the PC of serviceable control signals such as mute,volume up,or volume down,which have no connection with the internal DAC or ADC directly.See the Interface #3and End-Points sections.(4)TTL Schmitt trigger,5-V tolerant(5)Connect a decoupling capacitor to GND.(6)3.3-V CMOS-level input8Submit Documentation Feedback Copyright ©2007–2008,Texas Instruments IncorporatedPCM2900FUNCTIONAL BLOCK DIAGRAMSSPNDTEST1V LIN V RIN V COMV LOUT V ROUT XTIXTOD+D–SEL0SEL1HID0HID1HID2V BUSV CCCIV CCP1IV CCP2IV CCXIV DDIDGNDUDGNDAGNDXAGNDPAGNDCB0238-01TEST0PCM2900PCM2902SLES035E–MARCH 2007–REVISED MARCH 2008Copyright ©2007–2008,Texas Instruments Incorporated Submit Documentation Feedback 9PCM2902FUNCTIONAL BLOCK DIAGRAMSSPNDDIN V LIN V RIN V COMV LOUT V ROUT DOUT XTIXTOD+D–SEL0SEL1HID0HID1HID2V BUSV CCCIV CCP1IV CCP2IV CCXIV DDIDGNDUDGNDAGNDXAGNDPAGNDCB0239-01PCM2900PCM2902SLES035E–MARCH 2007–REVISED MARCH 200810Submit Documentation Feedback Copyright ©2007–2008,Texas Instruments IncorporatedPCM2900/2902DIAGRAM OF ANALOG FRONT-END(RIGHT CHANNEL)S0011-06TYPICAL CHARACTERISTICSADC7580859095−50−250255075100T A − Free-Air Temperature − °CD y n a m i c R a n g e a n d S N R − d BG0020.0030.0040.0050.0060.0070.0080.0090.010−50−250255075100T A − Free-Air Temperature − °CT H D +N − T o t a l H a r m o n i c D i st o r t i o n + N o i s e − %G0010.0030.0040.0050.0060.0070.0080.0090.0104.04.55.0 5.5V BUS − Supply Voltage − VT H D +N −T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %G00375808590954.04.55.0 5.5V BUS − Supply Voltage − VD y n a m i c R a n g e a n dS N R − d BG004SLES035E–MARCH 2007–REVISED MARCH 2008All specifications at T A =25°C,V BUS =5V,f S =44.1kHz,f in =1kHz,16-bit data,using REG 103xA-A,unless otherwise notedTOTAL HARMONIC DISTORTION +NOISE at –0.5dBDYNAMIC RANGE and SNRvsvsFREE-AIR TEMPERATUREFREE-AIR TEMPERATUREFigure 1.Figure 2.TOTAL HARMONIC DISTORTION +NOISE at –0.5dBDYNAMIC RANGE and SNRvsvsSUPPLY VOLTAGESUPPLY VOLTAGEFigure 3.Figure 4.75808590953035404550f S − Sampling Frequency − kHzD y n a m i c R a n g e a n d S N R − d BG006f S − Sampling Frequency − kHzG005DAC909192939495969798−50−250255075100T A − Free-Air Temperature − °CD y n a m i c R a n g e a n d S N R − d BG0080.0030.0040.0050.0060.0070.008−50−250255075100T A − Free-Air Temperature − °CT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %G007TYPICAL CHARACTERISTICS (continued)All specifications at T A =25°C,V BUS =5V,f S =44.1kHz,f in =1kHz,16-bit data,using REG 103xA-A,unless otherwise notedTOTAL HARMONIC DISTORTION +NOISE at –0.5dBDYNAMIC RANGE AND SNRvsvsSAMPLING FREQUENCYFigure 5.Figure 6.TOTAL HARMONIC DISTORTION +NOISE at 0dBDYNAMIC RANGE AND SNRvsvsFREE-AIR TEMPERATUREFREE-AIR TEMPERATUREFigure 7.Figure 8.9091929394959697984.04.55.0 5.5V BUS − Supply Voltage − VD y n a m i c R a n g e a n d S N R − d BG0100.0030.0040.0050.0060.0070.0084.04.55.0 5.5V BUS − Supply Voltage − VT H D +N − T o t a lH a r m o n i c D i s t o r t i o n + N o i s e − %G0099091929394959697983035404550f S − Sampling Frequency − kHzD y n a m i c R a n g e a n d S N R − d BG0120.0030.0040.0050.0060.0070.0083035404550f S − Sampling Frequency − kHzT H D +N − T o t a l H a r m o n i c D i s t o r t i o n + N o i s e − %G011SLES035E–MARCH 2007–REVISED MARCH 2008TYPICAL CHARACTERISTICS (continued)All specifications at T A =25°C,V BUS =5V,f S =44.1kHz,f in =1kHz,16-bit data,using REG 103xA-A,unless otherwise notedTOTAL HARMONIC DISTORTION +NOISE at 0dBDYNAMIC RANGE AND SNRvsvsSUPPLY VOLTAGESUPPLY VOLTAGEFigure 9.Figure 10.TOTAL HARMONIC DISTORTION +NOISE at 0dBDYNAMIC RANGE AND SNRvsvsSAMPLING FREQUENCYSAMPLING FREQUENCYFigure 11.Figure 12.SUPPLY CURRENT0.200.220.240.260.280.304.004.25 4.50 4.755.00 5.255.50V BUS − Supply Voltage − V203040506070G013I C C − O p e r a t i o n a l S u p p l y C u r r e n t − m AI C C − S u s p e n d S u p p l y C u r r e n t − m A2030405060703035404550f S − Sampling Frequency − kHz I C C − O p e r a t i o n a l Su p p l y C u r r e n t − m AG0140.100.150.200.250.300.350.40−40−20020406080100T A − Free-Air Temperature − °CI C C − S u s p e n d S u p p l y C u r r e n t − mAG015TYPICAL CHARACTERISTICS (continued)All specifications at T A =25°C,V BUS =5V,f S =44.1kHz,f in =1kHz,16-bit data,using REG 103xA-A,unless otherwise notedOPERATIONAL AND SUSPEND SUPPLY CURRENTvsSUPPLY VOLTAGEFigure 13.OPERATIONAL SUPPLY CURRENTSUSPEND SUPPLY CURRENTvsvsSAMPLING FREQUENCYFREE-AIR TEMPERATUREFigure 14.Figure 15.ADC DIGITAL DECIMATION FILTER FREQUENCY RESPONSEFrequency [y f S ]A m p l i t u d e − d BG016Frequency [y f S ]0.00.20.40.60.8 1.0A m p l i t u d e − dBG017Frequency [y f S ]−20−16−12−8−40.460.480.500.520.54A m p l i t u d e − d BG019Frequency [y f S ]0.00.10.20.30.40.5A m p l i t u d e − d BG018SLES035E–MARCH 2007–REVISED MARCH 2008TYPICAL CHARACTERISTICS (continued)All specifications at T A =25°C,V BUS =5V,f S =44.1kHz,f in =1kHz,16-bit data,unless otherwise notedOVERALL CHARACTERISTICSSTOP-BAND ATTENUATIONFigure 16.Figure 17.PASS-BAND RIPPLETRANSITION-BAND RESPONSEFigure 18.Figure 19.ADC DIGITAL HIGH-PASS FILTER FREQUENCY RESPONSEFrequency [y f S /1000]0.00.10.20.30.4A m p l i t u d e − dBG020Frequency [y f S /1000]−1.0−0.8−0.6−0.4−0.201234A m p l i t u d e − d BG021ADC ANALOG ANTIALIASING FILTER FREQUENCY RESPONSEf − Frequency − kHzA m p l i t u d e − d B0.011101000.1G023f − Frequency − kHzA m p l i t u d e − d B11001k 10k10G022TYPICAL CHARACTERISTICS (continued)All specifications at T A =25°C,V BUS =5V,f S =44.1kHz,f in =1kHz,16-bit data,unless otherwise notedSTOP-BAND CHARACTERISTICSPASS-BAND CHARACTERISTICSFigure 20.Figure 21.STOP-BAND CHARACTERISTICSPASS-BAND CHARACTERISTICSFigure 22.Figure 23.DAC DIGITAL INTERPOLATION FILTER FREQUENCY RESPONSEFrequency [y f S ]A m p l i t u d e − dBG024Frequency [y f S ]−0.8−0.6−0.4−0.20.20.00.10.20.30.40.5A m p l i t u d e − d BG025Frequency [y f S ]−20−18−16−14−12−10−8−6−4−200.460.470.480.490.500.510.520.530.54A m p l i t u d e − d BG026SLES035E–MARCH 2007–REVISED MARCH 2008TYPICAL CHARACTERISTICS (continued)All specifications at T A =25°C,V BUS =5V,f S =44.1kHz,f in =1kHz,16-bit data,unless otherwise notedSTOP-BAND ATTENUATIONPASS-BAND RIPPLEFigure 24.Figure 25.TRANSITION-BAND RESPONSEFigure 26.DAC ANALOG FIR FILTER FREQUENCY RESPONSE−50−40−30−20−100Frequency [y f S ]A m p l i t u d e − dBG027−0.8−0.6−0.4−0.20.20.00.10.20.30.40.5Frequency [y f S ]A m p l i t u d e − d BG028DAC ANALOG LOW-PASS FILTER FREQUENCY RESPONSEf − Frequency − kHzA m p l i t u d e − d B0.011101000.1G030f − Frequency − kHzA m p l i t u d e − d B11001k 10k10G029TYPICAL CHARACTERISTICS (continued)All specifications at T A =25°C,V BUS =5V,f S =44.1kHz,f in =1kHz,16-bit data,unless otherwise notedSTOP-BAND CHARACTERISTICSPASS-BAND CHARACTERISTICSFigure 27.Figure 28.STOP-BAND CHARACTERISTICSPASS-BAND CHARACTERISTICSFigure 29.Figure 30.SLES035E–MARCH2007–REVISED MARCH2008USB INTERFACEControl data and audio data are transferred to the PCM2900/2902via D+(pin1)and D–(pin2).All data to/from the PCM2900/2902is transferred at full speed.The device descriptor contains the information described in Table1.The device descriptor can be modified on request;contact a Texas Instruments representative for details.Table1.Device DescriptionUSB revision 1.1compliantDevice class0x00(device-defined interface level)Device subclass0x00(not specified)Device protocol0x00(not specified)Max packet size for end-point08bytesVendor ID0x08BB(default value,can be modified)Product ID0x2900/0x2902(default value,can be modified)Device release number 1.0(0x0100)Number of configurations1Vendor strings String#1(see Table3)Product strings String#2(see Table3)Serial number Not supportedThe configuration descriptor contains the information described in Table2.The configuration descriptor can be modified on request;contact a Texas Instruments representative for details.Table2.Configuration DescriptorInterface Four interfaces0x80(Bus powered,no remotePower attributewakeup)0x32(100mA.Default value,can beMax powermodified)The string descriptor contains the information described in Table3.The string descriptor can be modified on request;contact a Texas Instruments representative for details.Table3.String Descriptor#00x0409#1Burr-Brown from TI(default value,can be modified)#2USB audio codec(default value,can be modified)DEVICE CONFIGURATIONFigure31illustrates the USB audio function topology.The PCM2900/2902has four interfaces.Each interface is constructed by alternative settings.M0024-03Interface #0Figure B Audio Function TopologyInterface #0is defined as the control interface.Alternative setting #0is the only possible setting for interface #0.Alternative setting #0describes the standard audio control interface.A terminal constructs the audio control interface.The PCM2900/2902has five terminals as follows:•Input terminal (IT #1)for isochronous-out stream •Output terminal (OT #2)for audio analog output •Feature unit (FU #3)for DAC digital attenuator •Input terminal (IT #4)for audio analog input•Output terminal (OT #5)for isochronous-in streamInput terminal #1is defined as USB stream (terminal type 0x0101).Input terminal #1can accept 2-channel audio streams constructed by left and right channels.Output terminal #2is defined as a speaker (terminal type 0x0301).Input terminal #4is defined as a microphone (terminal type 0x0201).Output terminal #5is defined as a USB stream (terminal type 0x0101).Output terminal #5can generate 2-channel audio streams constructed by left and right channels.Feature unit #3supports the following sound control features.•Volume control •Mute controlThe built-in digital volume controller can be manipulated by an audio class specific request from 0dB to -64dBInterface #1Interface #2Interface #3SLES035E–MARCH 2007–REVISED MARCH 2008in 1-dB steps.Changes are made by incrementing or decrementing by one step (1dB)for every 1/f S time interval until the volume level has reached the requested value.Each channel can be set for different values.The master volume control is not supported.A request to the master volume is stalled and ignored.The built-in digital mute controller can be manipulated by audio class specific request.A master mute control request is acceptable.A request to an individual channel is stalled and ignored.Interface #1is the audio streaming data-out interface.Interface #1has the following seven alternative settings.Alternative setting #0is the zero bandwidth setting.All other alternative settings are operational settings.ALTERNATIVE TRANSFER SAMPLING RATEDATA FORMATSETTINGMODE(kHz)00Zero Bandwidth0116bit Stereo 2s complement (PCM)Adaptive 32,44.1,480216bit Mono 2s complement (PCM)Adaptive 32,44.1,48038bit Stereo 2s complement (PCM)Adaptive 32,44.1,48048bit Mono 2s complement (PCM)Adaptive 32,44.1,48058bit Stereo Offset binary (PCM8)Adaptive 32,44.1,48068bitMonoOffset binary (PCM8)Adaptive32,44.1,48Interface #2is the audio streaming data-in the interface.Interface #2has the following 19alternative settings.Alternative setting #0is the zero bandwidth setting.All other alternative settings are operational settings.ALTERNATIVE TRANSFER SAMPLING RATEDATA FORMATSETTINGMODE(kHz)00Zero Bandwidth0116bit Stereo 2s complement (PCM)Asynchronous 480216bit Mono 2s complement (PCM)Asynchronous 480316bit Stereo 2s complement (PCM)Asynchronous 44.10416bit Mono 2s complement (PCM)Asynchronous 44.10516bit Stereo 2s complement (PCM)Asynchronous 320616bit Mono 2s complement (PCM)Asynchronous 320716bit Stereo 2s complement (PCM)Asynchronous 22.050816bit Mono 2s complement (PCM)Asynchronous 22.050916bit Stereo 2s complement (PCM)Asynchronous 160A 16bit Mono 2s complement (PCM)Asynchronous 160B 8bit Stereo 2s complement (PCM)Asynchronous 160C 8bit Mono 2s complement (PCM)Asynchronous 160D 8bit Stereo 2s complement (PCM)Asynchronous 80E 8bit Mono 2s complement (PCM)Asynchronous 80F 16bit Stereo 2s complement (PCM)Synchronous 11.0251016bit Mono 2s complement (PCM)Synchronous 11.025118bit Stereo 2s complement (PCM)Synchronous 11.025128bitMono2s complement (PCM)Synchronous11.025Interface #3is the interrupt data-in interface.Alternative setting #0is the only possible setting for interface #3.Interface #3constructs the HID consumer control device and reports the following three key statuses.•Mute (0xE209)•Volume up (0xE909)•Volume down (0xEA09)。

在屏显示芯片MB90092的原理及应用

2 内部 结构 及 工作 原 理

MB 0 9 含 有 l 个 内部模 块 ,其 内部 结构 模 90 2 2 块 框 图如 图1 示 。其 中串行 输 入 控制 模 块用 于 所

3 电 手 元 器 件 焘 用 2 0 . W 'ed c O 08 W .  ̄ n 3 Wc

人 MB 0 9 。 9 0 2

◇ 芯 片 内建 上 电复位 电路 ,因此 ,使用 时须

先清 除 上 电复 位 ,芯 片才 能工作 ,这 样可 避免 出

MB 0 9 的主要性 能特 点如下 : 9 02

现 意想不 到的结果 。 ◇ 芯 片封装采 用8 引脚 的Q P 0 F 封装形 式 。体 积很 小 。

维普资讯

第 28第 3 1卷 年 月 0 期 o 3 o

姆霹缔 厕

V1 o o1N. . 3 0

Ma .2 o r o8

3 控 制 命 令 功 能

MB 0 9 共 有 1 条 控 制 命 令 ,其 中命 令 1 9o 2 4 和 命 令2 又分为 三种 。下面是命 令功 能介绍 : 命令0 R M地址 控制 。MB 0 9 的字符 显 :V A 9 02 示 存 储 器 ( R M)包 括 主 屏 字 符控 制 R M、子 V A A

屏 行 控 制 R M和 主 屏 行 控 制 R M。 用 于 控 制 A A

R M三种 不 同的功 能并使命 令 1 A 和命 令2 有三 种 各 不 同 的格 式 ,命 令0 于选择V A 用 R M的地址 ; 命令11 — :主屏 字符控 制 1 : 命 令2 1 — :主屏 字符控 制2 。命 令 1 1 — 用 — 和2 1 于对 主屏 字符控 制R M进行 写入 ,它 们可 为主屏 A

基于MB90092的视频字符叠加系统的设计

M Y g Ch g a On en Gu ng a wei Fe Xi ga ng ao ng

( 西安工业大学 电子信息工程学院, 陕西 西安

703 ) 102

(c o l o l cr n c If ra in E gn e ig i n T c n l g c l U ie s t ,S a x i n 7 03 ) S ho f E e to i n o m t o n ie rn ,X ’a e ho o ia n vr iy h n iX ’a 10 2

图 一是 该 视 频 叠 加 系统 的硬 件结 构 框 图。

式来 自 何处,以及对应图像的其他相关信息, 如当前的站址

号 、u I 、实时 数据 及 状 态 信 息显 示 到屏 幕 上 。针 对 目前 大 -' ,H j- ]

部分显示系统均采用分立元器件 ,结构复杂,不易于维护等

22 字符叠加模块 M902 . B09 [ M902 B09 是通用的字符叠加集成电路,具有视频信号发

生器、显示存储器 (RM 和字形存储器接 口,只需少量外部 VA)

缺点 ,本文提出采用富士通公司的字符叠加芯片 M902 , B09

不仅软件编程 简单,全 中文显示 , 而且还可 以设置子菜单 ( 用副屏显示) 把更多的信息实时叠加显示在屏幕上。

Carlin Combustion 90524A Triple Limit Control说明书