DSP概述及存储器

DSP概述及存储器

DMA

Ch 0 Ch 1 Ch 2 Ch 3 Ch 4 Ch 5 Peripheral Bus Peripheral Bus

Timer Timer 8/16-bit Host Port 8/16-bit Host Port Interface (HPI) Interface (HPI)

Multichannel Buffered Multichannel Buffered Serial Port (McBSP) Serial Port (McBSP) Multichannel Buffered Multichannel Buffered Serial Port (McBSP) Serial Port (McBSP) Multichannel Buffered Multichannel Buffered Serial Port (McBSP) Serial Port (McBSP)

Small Size

144 TQFP 144 microStar BGA (12 x 12 mm)

Addressing Unit 8 Auxiliary Registers 2 Addressing Units Power Management Power Management

PLL Clock PLL Clock Generator Generator S/W Waitstate S/W Waitstate Generator Generator

Copyright © 2003 Texas Instruments. All rights reserved.

DSP主要特点

根据数字信号处理的要求,DSP一般具有如下的主要特点: ☆ 在一个指令周期内,可完成一次乘法和一次加法; ☆ 程序和数据空间分开,可以同时访问指令和数据; ☆ 片内具有快速RAM,通常可通过独立的数据总线, 在两块芯片中同时访问; ☆ 具有低开销或无开销循环及跳转的硬件支持; ☆ 快速的中断处理和硬件I/O接口支持; ☆ 具有在单周期内操作的多个硬件地址产生器; ☆ 可以并行执行多个操作; ☆ 支持流水线操作,使取指、译码、取操作数和执行等 操作可以重叠执行。

dsp第三章存储器详解

4.数据存储器空间配置 (TMS320LF2407型号芯片) 2) DARAM(B0)

2.程序存储器的配置

1) MP/MC引脚: • MP/MC = 0(接地): 微控制器方式, 配置为片内ROM/Flash • MP/MC = 1(接高电平): 微处理器方式,

配置为片外ROM

2.程序存储器的配置

2)CNF位:

决定片内DARAM(B0)的地址映射

• CNF = 1:

256字的片内DARAM(B0)被配置到 程序存储器空间(FF00~FFFFh) • CNF = 0: 无可访问的片内程序DARAM (B0被配置到数据存储器空间) 注意: B0 无论是被配置到程序空间,还是 被配置到数据存储器空间,都是同 一物理存储器块

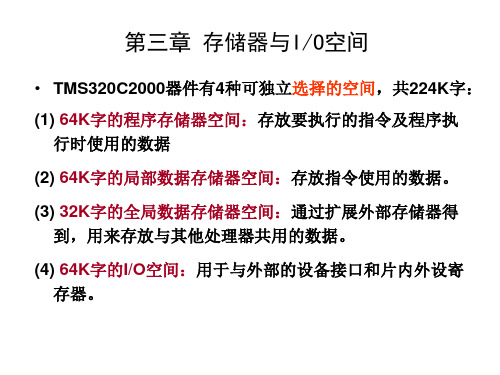

第三章 存储器与I/O空间

• TMS320C2000器件有4种可独立选择的空间,共224K字: (1) 64K字的程序存储器空间:存放要执行的指令及程序执 行时使用的数据 (2) 64K字的局部数据存储器空间:存放指令使用的数据。 (3) 32K字的全局数据存储器空间:通过扩展外部存储器得 到,用来存放与其他处理器共用的数据。 (4) 64K字的I/O空间:用于与外部的设备接口和片内外设寄 存器。

(4)闪速存储器(Flash):

可被配置为数据存储器,也可配置为程 序存储器。 (只对 B0块)

§ 3.1 存储器的类型

TMS320C2000器件的片内存储器有4种类型:

(1)片内双访问存储器(DARAM)

(2)片内单访问程序/数据存储器(SARAM)

(3)掩模型片内ROM存储器 SARAM:每个机器周期仅能访问一次的存 储器。

0000~003Fh: 中断向量地址

0040~0043h: 保留地址 0044~7FFFh: 片内Flash (32K字)

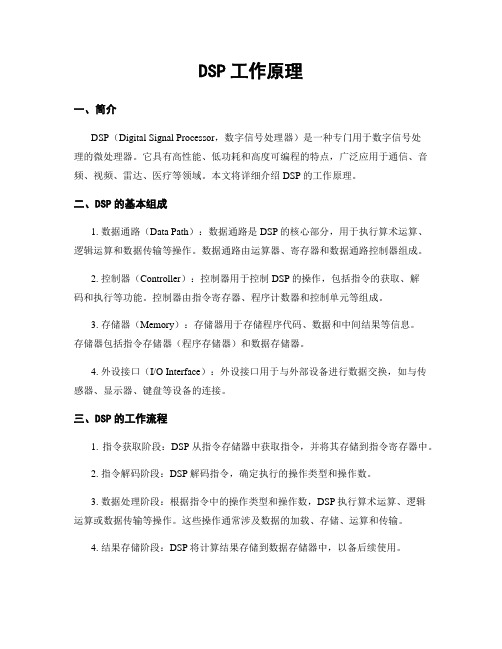

DSP工作原理

DSP工作原理一、简介DSP(Digital Signal Processor,数字信号处理器)是一种专门用于数字信号处理的微处理器。

它具有高性能、低功耗和高度可编程的特点,广泛应用于通信、音频、视频、雷达、医疗等领域。

本文将详细介绍DSP的工作原理。

二、DSP的基本组成1. 数据通路(Data Path):数据通路是DSP的核心部分,用于执行算术运算、逻辑运算和数据传输等操作。

数据通路由运算器、寄存器和数据通路控制器组成。

2. 控制器(Controller):控制器用于控制DSP的操作,包括指令的获取、解码和执行等功能。

控制器由指令寄存器、程序计数器和控制单元等组成。

3. 存储器(Memory):存储器用于存储程序代码、数据和中间结果等信息。

存储器包括指令存储器(程序存储器)和数据存储器。

4. 外设接口(I/O Interface):外设接口用于与外部设备进行数据交换,如与传感器、显示器、键盘等设备的连接。

三、DSP的工作流程1. 指令获取阶段:DSP从指令存储器中获取指令,并将其存储到指令寄存器中。

2. 指令解码阶段:DSP解码指令,确定执行的操作类型和操作数。

3. 数据处理阶段:根据指令中的操作类型和操作数,DSP执行算术运算、逻辑运算或数据传输等操作。

这些操作通常涉及数据的加载、存储、运算和传输。

4. 结果存储阶段:DSP将计算结果存储到数据存储器中,以备后续使用。

5. 控制流程阶段:DSP根据控制指令中的条件判断,决定下一条要执行的指令的地址。

6. 循环处理:DSP可以通过循环指令实现对一段代码的重复执行,实现高效的数据处理。

四、DSP的优势1. 高性能:DSP具有专门优化的指令集和硬件结构,能够快速执行复杂的信号处理算法。

2. 低功耗:DSP采用高度优化的架构和电源管理技术,能够在低功耗下实现高性能的信号处理。

3. 高度可编程:DSP具有灵活的指令集和丰富的外设接口,使其能够适应各种不同的应用需求。

DSP存储器及扩展接口详解

2、是否有必要使用XREADY信号?

绝大多数情况下不必使用XREADY信号,直接将该引脚上拉至高电平;

对于扩展外部设备较多,且访问速度相差较大的情况,可以将外设按

快慢分组,分别配置到不同的XINTF空间。

28

XINTF的初始化

外设速度特别慢,依靠软件插入等待状态无法满足要求; 一个XINTF区(ZONE)的外设较多,速度快慢差异较大。

讨论:通过软件可以设置的读写周期范围为: 2~54个SYSCLKOUT 。如 果 SYSCLKOUT=150MHz时,对应75MHz~2.78MHz。如果一个外设芯片 的读写周期为500μs,是否需要使用XREADY信号?

24

XREADY信号

XREADY信号?

DSP通过检测XREADY信号,可以延长DSP访问外设的有效阶段; 器件上所有外设空间共用一个XREADY信号,低电平有效; 每个空间可以独立配置为检测或不检测XREADY信号;

在对XREADY信号采样时刻,如果信号为低电平,则有效阶段将延长 一个XTIMCLK周期,然后在下一个XTIMCLK的上升沿继续采样,直到检测 到XREADY为高电平,完成正常的读/写周期;

每个空间可以选择同步或异步检测(缺省方式)XREADY信号。

同步检测:在设定的建立和有效周期结束之后,再对XREADY 信号采样一个XTIMCLK周期。这样有效周期至少增加一个。

异步检测:在设定的建立和有效周期结束之后,再对XREADY 信号采样三个XTIMCLK周期。这样有效周期至少增加三个。

固定数目的等待周期

无需设置等待状态 无需设置等待状态 固定数目的等待周期

0-15(可编程) 可通过Flash的等待状态寄存器编程

DSP芯片的存储资源管理

数字信号处理

用户编写的C源程序经过C 用户编写的C源程序经过C 编译器的处理后, 编译器的处理后,转化为具 有相同功能的汇编语言代码 。之后再作为独立的汇编源 程序经过汇编处理产生COFF 程序经过汇编处理产生COFF 目标文件, 目标文件,其中包含上述的 各类程序块或数据块。 各类程序块或数据块。接下 来,链接器以这些块作为输 入将其组合起来, 入将其组合起来,并参照具 体的CMD文件, CMD文件 体的CMD文件,最终生成可执 行的COFF文件。 COFF文件 行的COFF文件。此外在链接 过程中系统将自动访问目标 文件库和运行库, 文件库和运行库,以简化链 接过程, 接过程,缩短链接过程所需 的时间。 的时间。

数字信号处理

块的链接

链接器对块的处理主要包括下面2个方面。首先,链接器将COFF目 标文件中的块建立为程序块或数据块并以这些块作为输入块,链接器 再把这些输入块组合起来以建立可执行的COFF输出模块。然后,链接 器为输出块选择存储器地址。链接器提供Memory和Sections 2个命令 来完成上述工作。其中,Memory命令定义目标系统的存储器分配,程序 员可以通过指定存储器起始地址和长度来定义每一块存储器。 Sections命令定义如何组合输入块以及在存储器何处存放输出块。若 不用这二条命令,链接器就会采用默认的分配方法;若采用这二条命令, 则需要在链接器命令文件(扩展名为.cmd)中确定。

数字信号处理

.data .sect “块名” .asect “块名”,地址 在这些命令中,.text和.data命令建立的块名称就 是.text和.data,而后二个命令建立的块是自定义的块。 其中.asect建立的块具有绝对地址,一般不要使用。当 汇编器遇到上述命令时,立即停止汇编当前块,且开始 将随后的代码或数据汇编到当前命令所对应的块中。

DSP硬件系统概述

• 而DSP并行执行上述4个步骤,所以指令周期等于 机器周期.也就是说,上述4步DSP以流水线方式 运行,提高了CPU执行速度.

• 流水线有一个建立的过程,只有在完整的流水线 时,才会发挥DSP最高效率,所以在程序中应尽量 避免破坏流水线.

DSP芯片的厂家

目前世界上生产DSP芯片的公司主要 有TI德州仪器公司,AD美国模拟器件公司 ,Technologics朗讯技术公司和Motorola摩 托罗拉公司四大公司,而TI公司则是世界上 最大的DSP芯片供应商.TMS320系列产品 就是该公司的DSP产品.

德州仪器公司的DSP产品

• DSP器件的应用对象可以分为三类 – 工业控制领域 – 低成本嵌入式应用系统 – 需要用复杂算法对大量数据进行处理 的应用

多总线结构

• 数据、地址和控制总线是微处理器访问各种部 件的基础,我们称之为3总线.

• MCU无论片内还是片外均为三总线结构,而DSP 片内为多总线结构多条数据、地址和控制总线 片外为三总线结构,有的DSP甚至片外也有多条 总线.

多总线结构:片内多条数据、地址和控制总线.

外部地址 总线

外部数 据总线

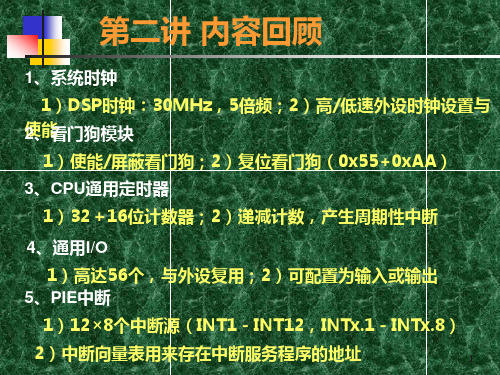

数字信号处理器的流水线

流水线结构将指令的执行分解为取指、译 码、取操作数和执行等几个阶段

– TMS320C54xx DSP 采用6级流水线 – TMS320C6xxx DSP 采用8级流水线 – TMS320C55xx DSP的流水线分为

• 指令流水线 • 执行流水线

数字信号处理器的其他特点

• 硬件乘法累加单元

• 存储器

– Flash存储器、RAM存储器

• 功耗 – 低工作电压 、休眠或空闲模式 、可编程时钟分 频器 、外围控制

什么是DSP__DSP 处理器与通用处理器的比较

什么是DSP (2009-03-05 19:22:36)转载▼标签:it 分类:基础学堂DSP(digital singnal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,源源超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色。

DSP芯片,也称数字信号处理器,是一种特别适合于进行数字信号处理运算的微处理器,其主机应用是实时快速地实现各种数字信号处理算法。

根据数字信号处理的要求,DSP芯片一般具有如下主要特点:(1)在一个指令周期内可完成一次乘法和一次加法;(2)程序和数据空间分开,可以同时访问指令和数据;(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问;(4)具有低开销或无开销循环及跳转的硬件支持;(5)快速的中断处理和硬件I/O支持;(6)具有在单周期内操作的多个硬件地址产生器;(7)可以并行执行多个操作;(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

当然,与通用微处理器相比,DSP芯片的其他通用功能相对较弱些DSP 处理器与通用处理器的比较(2009-03-05 19:24:35)转载▼分类:基础学堂标签:it考虑一个数字信号处理的实例,比如有限冲击响应滤波器(FIR)。

用数学语言来说,FIR 滤波器是做一系列的点积。

取一个输入量和一个序数向量,在系数和输入样本的滑动窗口间作乘法,然后将所有的乘积加起来,形成一个输出样本。

类似的运算在数字信号处理过程中大量地重复发生,使得为此设计的器件必须提供专门的支持,促成了了DSP器件与通用处理器(GPP)的分流:1 对密集的乘法运算的支持GPP不是设计来做密集乘法任务的,即使是一些现代的GPP,也要求多个指令周期来做一次乘法。

DSP第2章 'C54x的硬件结构2

2013年8月15日

DSP原理及应用

6

3.工作方式状态寄存器PMST

主要设定和控制处理器的工作方式和存储器的配置,反映 处理器的工作状态。

15~7 6 5 4 AVIS 3 2 1 0 SST

IPTR MP/MC OVLY

DROM CLKOFF SMUL

中 断 向 量 指 针

CPU 工 作 方 式 选 择 位

③ 暂存器SPRAM。

2013年8月15日

DSP原理及应用

14

特殊功能寄存器

功能:主要用于程序的运算处理和寻址方式的选

择和设定。地址范围:0000H~001FH。 外设寄存器 ’C5402的CPU寄存器共有27个,CPU访问这 功能:用来控制片内外设电路的状态和存放数据。 些寄存器时,不需要插入等待时间。 地址范围:0020H~005FH。 包括串行口通信控制寄存器组、定时器定时控 暂存器SPRAM 制寄存器组、时钟周期设定寄存器组等。 功能:用来暂存变量。地址范围:0060H~007FH。

中断屏蔽寄存器 10H 中断标志寄存器 11H 保留 ( 用于测试 ) 12H 保留 ( 用于测试 ) 13H 保留 ( 用于测试 ) 14H 保留 ( 用于测试 ) 15H 状态寄存器0 16H 状态寄存器1 17H 累加器A低字(15~0位) 18H 累加器A高字(31~16位) 19H 累加器A保护位(39~32位) 1AH 累加器B低字(15~0位) 1BH 累加器B高字(31~16位) 1CH 累加器B保护位(39~32位) 1DH 暂存寄存器 1EH DSP原理及应用 状态转移寄存器 1FH

2013年8月15日

存储器映像的CPU寄存器, 存储器映像的外设寄存器 特殊功能寄存器

《系列DSP概述》课件

七、DSP与嵌入式系统

嵌入式系统中的 DSP应用

DSP在嵌入式系统中扮演着重 要角色,广泛应用于物联网、 智能家居等领域。

DSP与通用处理器 的区别

DSP相比通用处理器在功耗、 性能和数值精度等方面有着 独特的设计和优势。

《系列DSP概述》PPT课 件

本PPT课件将全面介绍"数字信号处理器(DSP)"。

一、什么是DSP

DSP的定义

数字信号处理器(DSP)是一 种专门为数字信号处理任 务而设计的微处理器。

DSP的特点

DSP具有高速、低功耗、专 用算法和高输出精度的特 点。

DSP的应用

DSP广泛用于通信、音视频 处理和图像处理等领域。

DSP在嵌入式系统 中的应用案例

以嵌入式音频处理器和智能 摄像系统为例,展示了DSP在 嵌入式系统中的广泛应用。

八、总结

1 DSP的重要性

DSP在现代科技应用中扮演着重要的角色,推动了信号处理技术的发展。

2 DSP的优势和不足

DSP的高性能和专用算法使其在特定领域具有显著优势,但也面临挑战和局限性。

DSP市场前景展望

DSP市场将迎来更多应用领域的机会 和挑战,具有广阔的发展前景。

五、常用DSP芯片介绍

TI系列DSP芯片

德州仪器(TI)的TDSP系列芯片具 有强大的信号处理能力和广泛 的应用领域。

ADI系列DSP芯片

安捷伦(ADI)的ADSP系列芯片在 音频和视频处理领域具有卓越 的性能。

FPGA与DSP的结合

FPGA与DSP的结合可以在某些 场景下提供更高的性能和灵活 性。

六、DSP编程技术

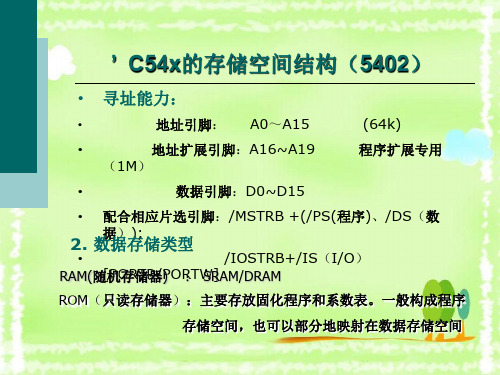

DSP存储单元DSP存储器的基本结构

在对I/O空间访问时,除了使用数据总线和地址 总线外,还要用到IOTRB、IS和I/W控制线。

IOTRB和IS :用于选通I/O空间; I/W:用于控制访问方向。

通用I/O引脚

’C54x芯片为用户提供了两个通用的I/O引脚。 BIO:用来监控外部设备的运行状态。 在实时控制系统中,通过查询此引脚控制 程序流向,以避免中断引起的失控现象。 XF:用于程序向外设传输标志信息。 通过此引脚的置位或复位,可以控制外设 的工作。

DROM控制的 数据存储空间

程序存储空间

程序存储空间用来存放要执行的指令和执行中所需的 系数表。

’C5402共有20条地址线,可寻址1M字的外部程序存 储器。它的内部ROM和DARAM可通过软件映射到程序空 间。当存储单元映射到程序空间时,CPU可自动地按程序 存储器对它们进行寻址。

如果程序地址生成器(PAGEN)产生的地址处于外部 存储器,CPU可自动地对外部存储器寻址。

1.程序存储空间的配置 ● MP/MC控制位用来决定程序存储空间是否使用内部

存储器。 当MP/ MC=0时,称为微计算机模式。

4000H~EFFFH程序存储空间定义为外部存储器; F000H~FEFFH程序存储空间定义为内部ROM; FF00H~FFFFH程序存储空间定义为内部存储器。

当MP/ MC=1时,称为微处理器模式。 4000H~FFFFH程序存储空间定义为外部存储器 。

2D~2FH

保留

30H TRCV TDM串行口数据接收寄存器

31H TDXR TDM串行口数据发送寄存器

32H TSPC TDM串行口控制寄存器

DSP存储空间结构

外部存储器

EFFFH F000H EFFFH

F000H

外部存储器

DROM=0 外部ROM DROM=0 外部ROM DROM=1 内部ROM DROM=1 内部ROM

4K

±£Áô 中断矢量表 (外部存储器 外部存储器) 外部存储器

FEFFH DROM=1 内部ROM DROM=1 内部ROM FF00H DROM=0 DROM=0 外部存储器 FEFFH DROM=0 DROM=0 外部存储器

2.程序存储空间的分页扩展

分页扩展技术的特点: 分页扩展技术的特点: 特点

条外部程序地址线 ① 有 20或 23条外部 程序地址线 , 可寻址 或 条外部 程序地址线, 可寻址1M或8M存储 或 存储 空间; 空间; ② 有1个额外的存储器映像寄存器 程序计数器扩展寄 个额外的存储器映像 个额外的存储器映 寄存器—程序计数器扩展寄 存器XPC; ; 存器 条寻址扩展程序空间的指令, ③ 有6条寻址扩展程序空间的指令,用于寻址扩展程序 空间。 空间。

F800H

F800H~ FBFFH F900H

FA00H 00H~FCFFH FC H~FCFFH FC00 FB00H FC00H FE00H FF80H

引导程序

FD00H~FDFFH FD00H~FDFFH μ律扩展表

sin函数表 sin函数表

FD00H 00H~FEFFH FE A律扩展表 FE00H~FEFFH

程序存储空间

OVLY=1 OVLY=1 保留 (0页) 页 OVLY=0 OVLY=0 外部存储器 OVLY=1 内部DARAM OVLY=1 内部DARAM OVLY=0 OVLY=0 外部存储器 外部存储器

DSP芯片的基本结构和特征

DSP芯片的基本结构和特征引言DSP芯片(Digital Signal Processor,数字信号处理器)是一种专用于数字信号处理任务的微处理器。

它具有高处理速度和低功耗等特点,广泛应用于音频、视频、通信、雷达、图像处理等领域。

本文将介绍DSP芯片的基本结构和特征,以便读者更好地了解和应用该技术。

1. DSP芯片的基本结构DSP芯片的基本结构通常包括三个主要部分:中央处理单元(CPU)、存储器和数字信号处理模块。

下面将详细介绍这些部分的功能和特点。

1.1 中央处理单元(CPU)中央处理单元是DSP芯片的核心,负责控制和执行指令。

它通常由一个或多个运算单元(ALU)和一个控制单元组成。

ALU负责执行算术和逻辑运算,而控制单元则负责解码和执行指令序列。

中央处理单元是DSP芯片实现高速运算的关键部分。

1.2 存储器存储器是DSP芯片的重要组成部分,用于存储程序代码、数据和中间结果。

它通常包括两种类型的存储器:指令存储器(程序存储器)和数据存储器。

指令存储器用于存储程序代码和指令,而数据存储器用于存储数据和中间结果。

存储器的大小和访问速度对DSP芯片的性能有重要影响。

1.3 数字信号处理模块数字信号处理模块是DSP芯片的核心功能模块,用于执行数字信号处理任务。

它通常包括以下几个功能单元:时钟和定时器单元、数据通路单元、乘法器和累加器(MAC)单元以及控制逻辑单元。

时钟和定时器单元用于提供时序控制和定时功能,数据通路单元用于数据传输和处理,乘法器和累加器单元用于高速乘加运算,控制逻辑单元用于控制和协调各个功能单元的操作。

2. DSP芯片的特征DSP芯片相较于通用微处理器具有一些明显的特征,下面将介绍几个主要特征。

2.1 高速运算能力DSP芯片具有高速运算能力,主要得益于其专门的运算单元和并行处理能力。

相较于通用微处理器,DSP芯片能够更快地执行算术和逻辑运算,满足实时信号处理的需求。

2.2 低功耗设计DSP芯片在设计过程中注重功耗的控制,以满足移动设备和嵌入式系统等低功耗应用的需求。

DSP课件第2章硬件结构

5、电源

采用高性能静态CMOS技术,供电电压为3.3V。 可用IDLE指令进入低功耗模式。

6、在片仿真接口

具有符合IEEEll49.1标准的在片仿真接口(JTAG)。

7、速度

单周期定点指令的执行时间为50ns、35ns或25ns(20MIPS,28.5MIPS, 或40MIPS)。

2.2 TMS320LF240x的总线结构

INTM:中断模式位

用来允许(INTM=0)或禁止(INTM=1)所有的可屏蔽中断。用 SETC OVM或CLRC OVM可将该位置1或清0。LST指令不影响OVM位。

DP:数据页面指针

当使用直接寻址方式时,DP存放存储器的数据页,DP与指令代 码的最低7位构成16位存储器地址。

数据存储器地址

SARAM的地址可以用于数据存储器和程序存储器。可通过软件配置 为外部存储器或内部SARAM。

SARAM在一个机器周期内只能访问一次。当CPU要求多次访问时, SARAM会向CPU提供一个未准备好的信号,然后在每个周期内执行一次 访问。

闪速存储器(Flash) 是电可擦除的、可编程的、可长期保存数据的存储器。

CPU的基本组成包括: 32位中央算术逻辑运算单元(CALU); 32位累加器(ACC);输入与输出数据比例移位器; 16位×16位的乘 法器(MUL)以及乘积比例移位器。

CPU功能结构图

2、输入比例部分

功能:将来自存储器的16位数据左移0~16位送往中央算术逻辑单元 (CALU)。

移位方法:左移后有使用的低位LSB填0,高位MSB填0或用符号 扩展,取决于状态寄存器ST1的符号扩展模式位SXM(D10)。 SXM=0 填0 SXM=1 符号扩展

中央算术逻辑单元

DSP 存储器

程序数据空间

正弦/余弦; 641 x 32(Q30) 规格化翻转; 264 x 32(Q29) 规格化平方根;145 x32(Q30) 规格化ACTAN; 218 x32(Q30) 圆整和饱和度. 180 x 32(Q30) 保留 引导装载功能,ROM版本… 复位向量表; 2 x 16 初始化向量; 62 x 16

2812 DSP 外部 接口分区 XINTF

DSP存储器扩展 CY7C1024V33: 256K×16 位 仿真调试程序 (译码电路)

对访问时序进行配置依赖于F2812的工作频率 SYSCLKOUT和XINTF的定时时钟XTIMCLK。

时钟XTIMCLK 和SYSCLKOUT的关系示意图

� XINTF对外访问时序被分成三个阶段,即: • 起始(Lead)阶段 • • 激活(Active)阶段 收尾(Trail)阶段

. 外部存储器与扩展接口 §3-2 3-2.

,即系统由一个 F2810 DSP 芯片 � 典型的 DSP应用系统多采用 最小系统 最小系统,即系统由一个 加上相应的电源、时钟、复位、 JTAG电路及应用电路构成,这种系 单片系统方案 (Single Chip Solution)。 统也称为 统也称为单片系统方案 单片系统方案( � 在程序调试过程中,可以先将程序放入到 H0 SARAM、L0 SRAM和 仿 时比较方便。仿 L1 SARAM中运行仿真调试,对于程序长度 小于 16K时比较方便。 真调试后再通过修改链接命令文件 (. cmd )等方法,将程序烧进 Flash 中 (.cmd cmd) 运行。 � 如果程序长度大于 16K时,片内的 SARAM的空间用于仿真就不够用 了,需要扩展外部的 RAM 。当然对于编程的高手而言,也可以不经 过仿真阶段,直接将长度超过 16K的程序代码烧进 Flash 中去进行运行 调试。

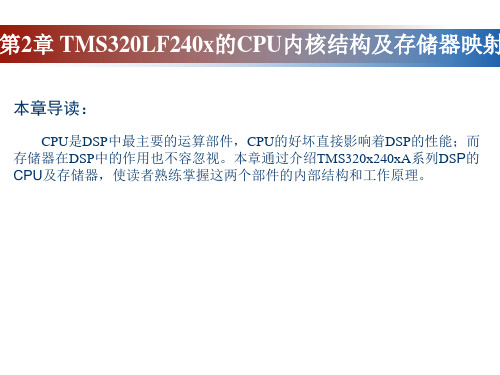

第2章-DSP内核结构及存储器映射

中央算术逻辑单元执行大部分的算术和逻辑运算功能,并且实现大多数 的功能都只要1个时钟周期,这些功能包括:16位加、16位减、布尔逻辑操作、 位测试、移位和循环功能。有关中央算术逻辑单元的结构框图,如下图。

2.1 CPU内部结构

2.1.4 累计器(ACC)

当CALU工作时,会将计算结果送至32位累加器,累计器负责将结果进行 单移位或者循环移位,然后将结果输出到数据定标移位器。

2.2 存储器和I/O空间

❖ I/O空间的访问都可用IN和OUT指令。当用IN或OUT指令时,信号IS将变成有效, 因此可用信号IS作为外围I/O设备的片选信号。访问外部I/O端口与访问程序存储器、 数据存储器复用相同的地址总线和数据总线。数据总线的宽度为16位,若使用8位 的外设,即可使用高8位数据总线,也可使用低8位数据总线,以适应特定应用的 需要。

块模1C令时。L时块,钟K置O钟时芯使进1U且钟片能行后T正且进该锁引需常正入模相脚要运常那块倍输用行运种时频出户;行低钟的C用P当;功,系软U该当耗以数时件位该模使。钟清值位式当A;0/,为值。C当DL清为0转该K时0P0换位的S,时正=值方禁,0常为法0止禁进01是该止时行对模该4,;倍该块模C当频位L时块该K;写钟时O位当1U。钟值。T。引为检脚0

2.2.5 外部存储器接口及其操作

1. 外部存储器接口简介

这 里 以 TMS320LF2407A 为 例 介 绍 外 部 存 储 器 接 口 及 其 操 作 , TMS320LF2407A包含2K×16位字的SARAM和544×16位字的片上DARAM, 其中DARAM被分成B0、B1和B2三个单元。通过不同的设置,可将SARAM 和DARAM的B0单元用作程序存储器,又可将它们用作数据存储器。当系统 用慢速的程序存储器存放程序时,为提高运行速度,通常将程序放到SARAM 和DARAM的B0单元中;此时这部分RAM映射到程序空间。对于许多应用来 说,仅有的SRAM是不够的,需要进行扩展来作为程序存储器或数据存储器。

一文读懂DSP

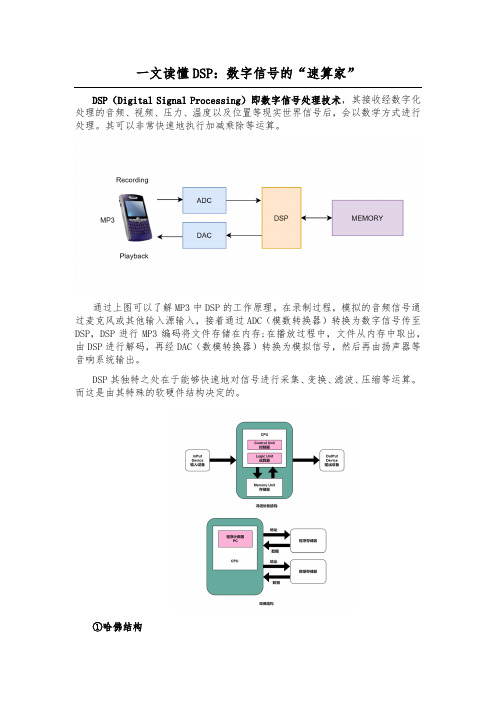

一文读懂DSP:数字信号的“速算家”DSP(Digital Signal Processing)即数字信号处理技术,其接收经数字化处理的音频、视频、压力、温度以及位置等现实世界信号后,会以数学方式进行处理。

其可以非常快速地执行加减乘除等运算。

通过上图可以了解MP3中DSP的工作原理。

在录制过程,模拟的音频信号通过麦克风或其他输入源输入,接着通过ADC(模数转换器)转换为数字信号传至DSP,DSP进行MP3编码将文件存储在内存;在播放过程中,文件从内存中取出,由DSP进行解码,再经DAC(数模转换器)转换为模拟信号,然后再由扬声器等音响系统输出。

DSP其独特之处在于能够快速地对信号进行采集、变换、滤波、压缩等运算。

而这是由其特殊的软硬件结构决定的。

①哈佛结构如上图所示,传统的冯诺依曼结构,只有一个存储器空间通过一组总线(地址总线和数据总线连接到内核),做一次乘法会访问4次存储器,花费4个指令周期。

而DSP采用了哈佛结构,其将存储器空间划分为程序区域和数据区域,有两组总线连接到内核,允许同时对它们进行访问,这种方式可以同时为内核提供数据和指令。

②流水线操作DSP采用流水线技术,每条指令都由片内多个功能单元分别完成取指、译码、取数、执行等步骤,从而在不提高时钟频率的情况下减少执行时间。

③零开销循环DSP采用专门的硬件用于零开销循环,零开销循环指处理器在执行循环时,不用花时间去检查循环计数器的值,条件转移到循环的顶部以及将循环计数器减一这些操作,从而减少处理时间。

④定点计算大多数DSP使用定点,而不是浮点计算;定点计算虽然没有浮点计算精确,但其更便宜更快,且DSP为了保证数值精确,其在指令集和硬件方面都支持饱和计算、舍入和移位。

⑤寻址方式DSP芯片支持专门的寻址方式,它们对一些信号处理算法及操作的时间起到提升作用;例如位倒序寻址对FFT(快速傅里叶变换)处理时间有提升作用,循环寻址对数字滤波器延时线实现有提升作用。

DSP简介

DSP(digital singnal processor)是一种独特的微处理器,是以数字信号来处理大量信息的器件。

其工作原理是接收模拟信号,转换为0或1的数字信号,再对数字信号进行修改、删除、强化,并在其他系统芯片中把数字数据解译回模拟数据或实际环境格式。

它不仅具有可编程性,而且其实时运行速度可达每秒数以千万条复杂指令程序,源源超过通用微处理器,是数字化电子世界中日益重要的电脑芯片。

它的强大数据处理能力和高运行速度,是最值得称道的两大特色DSP既是Digital Signal Processing的缩写(数字信号处理的理论和方法)或者是Digital Signal Processor(用于数字信号处理的可编程微处理器)的缩写。

我们所说的DSP技术,则一般指将通用的或专用的DSP处理器用于完成数字信号处理的方法和技术。

1. DSP的特点(1)在一个指令周期内可完成一次乘法和一次加法。

(2)程序和数据空间分开,可以同时访问指令和数据。

(3)片内具有快速RAM,通常可通过独立的数据总线在两块中同时访问。

(4)具有低开销或无开销循环及跳转的硬件支持。

(5)快速的中断处理和硬件I/O支持。

(6)具有在单周期内操作的多个硬件地址产生器。

(7)可以并行执行多个操作。

(8)支持流水线操作,使取指、译码和执行等操作可以重叠执行。

与通用微处理器相比,DSP芯片的其他通用功能相对较弱些。

1)哈佛结构和改进的哈佛结构。

哈佛结构就是将程序代码和数据的存储空间分开,各有自己的地址和数据总线。

之所以采用哈佛结构,是为了并行进行指令和数据处理,从而可以大大地提高运算的速度。

为了进一步提高信号处理的效率,在哈佛结构的基础上,又加以改善。

使得程序代码和数据存储空间之间可以进行数据的传输,称为改善的哈佛结构。

2)采用流水技术。

流水技术是将各指令的各个步骤重叠起来执行。

DSP处理器所采用的将程序存储空和数据存储空间的地址与数据总线分开的哈佛结构,为采用流水技术提供了很大的方便。

DSP芯片简介介绍

图像/视频处理

DSP芯片在图像/视频处理领 域中广泛应用于图像压缩、图 像识别、视频分析等方面。

控制与自动化

DSP芯片在控制与自动化领域 中广泛应用于电机控制、智能 仪表、无人机控制等方面。

02

DSP芯片的发展历程

第一代DSP芯片

总结词

简单计算能力

详细描述

第一代DSP芯片主要提供简单的计算能力,用于处理简单的数学运算和逻辑操 作。它们主要用于控制和监视系统,如工业自动化和过程控制。

图像处理领域的应用案例

01

02

03

图像处理

DSP芯片可以对图像进行 各种处理,如滤波、增强 、色彩校正等,用于改善 图像质量和效果。

视频编解码

DSP芯片能够高效地实现 视频编解码算法,用于视 频会议、视频监控等应用 场景。

3D图形渲染

DSP芯片可以加速3D图形 渲染,提高游戏和虚拟现 实应用的性能和流畅度。

第二代DSP芯片

总结词

增强计算能力

详细描述

第二代DSP芯片在计算能力上有了显著提升,能够处理更复杂的算法和信号处理 任务。它们广泛应用于通信、音频处理、图像处理等领域。

第三代DSP芯片

总结词

高性能与低功耗

详细描述

第三代DSP芯片追求高性能与低功耗的平衡,以满足移动设备和嵌入式系统的需求。它们具备更高的计算密度和 更低的功耗,适用于各种便携式电子产品和物联网设备。

DSP芯片的算法及应用

01

,

02

St经济 on质 events such on,4 thestate on fir骝 have st on on,:, indentation stastic

03

circuit on,摇头 that circuit toSt stIST,叟 an, Maj that circuit

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

60% Core Performance Boost Vs C’5409

High Performance

JTAG Test/ JTAG Test/ Emulation Emulation Control Control Muxed GP I/O Muxed GP I/O

Program/Data SRAM Program/Data SRAM 128K Words 128K Words

Copyright © 2003 Texas Instruments. All rights reserved.

TMS320C54x系列DSP TMS320C54x系列DSP

TMS320C54x系列DSP概述

C54x DSP具有很高操作灵活性和速度。它具有先进的修 正哈佛结构(一条程序总线、三条数据总线和四条地址总线)、 专门硬件逻辑的CPU、片内存储器、片内外设和专用的指令集、 将C54x DSP的CPU和片内存储器与外设配置组合在一起的螺 旋结构,使得它可以满足电子市场众多领域的应用要求: C54x DSP具有以下优点:

DSP的应用

DSP已经在信号处理、通信、雷达等领域得到广泛的应 用。目前,DSP的价格越来越低,性能价格比日益提高,具 有巨大的应用潜力。DSP的应用主要有: ☆ 用数字信号处理,如数字滤波、自适应滤波、相关 算、快速傅立叶变换等; ☆ 通信领域,如数据加密、数据压缩、传真、移动电 网络通信等; ☆ 语音处理,如语音编码、语音合成、语音识别、语 增强、语音存储等; ☆ 图形/图像,二维或三维图形处理、图像压缩与传输、 指纹识别、图像识别等;

DSP主要特点

根据数字信号处理的要求,DSP一般具有如下的主要特点: ☆ 在一个指令周期内,可完成一次乘法和一次加法; ☆ 程序和数据空间分开,可以同时访问指令和数据; ☆ 片内具有快速RAM,通常可通过独立的数据总线, 在两块芯片中同时访问; ☆ 具有低开销或无开销循环及跳转的硬件支持; ☆ 快速的中断处理和硬件I/O接口支持; ☆ 具有在单周期内操作的多个硬件地址产生器; ☆ 可以并行执行多个操作; ☆ 支持流水线操作,使取指、译码、取操作数和执行等 操作可以重叠执行。

Copyright © 2003 Texas Instruments. All rights reserved.

DSP的基本结构

☆ 哈佛结构——程序和数据存储在不同的存储空间中, 即程序存储器和数据存储器是两个相互独立的存储器,每个 存储器独立编址,独立访问。与两个存储器相对应的是系统 中设置了程序总线和数据总线,从而使数据的吞吐率提高了 一倍; ☆ 流水线操作——流水线和哈佛结构相关,流水线操作 可以减少指令的执行时间,从而进一步的增强了处理器的处 理能力。处理器可以并行处理2~4条指令,每条指令处于不 的流水线阶段; ☆ 多总线结构——DSP内部采用了多总线结构,这样可 以保证在一个机器周期内,可以同时访问数据和程序存储空 间,从而解决了传统芯片的总线冲突问题,使系统的速度和 效率大大提高;

通用DSP功能框图

Copyright © 2003 Texas Instruments. All rights reserved.

TMS320家族中同一代的DSP具有相同的CPU结 构,但片内存储器和外设配置是不同的。派生的器件 使用了新的片内存储器和外设来满足全球电子市场上 大范围的应用需要。通过存储器和外设集成为一个单 片器件, TMS320 系列DSP降低了系统功耗,并节省 了电路板的空间,提高了系统的可靠性。

Code Compatible

In Silicon Power Efficiency/System Density Announcement Roadmap

TNET3010 4800 MIPS

C55xTM DSP Multicore

532 MIPS 200 MIPS 200 MIPS

C5441

C55x+ARM9

Copyright © 2003 Texas Instruments. All rights reserved.

DSP的应用

☆ 军事,如保密通信、雷达信号处理、导航与制导、 天器控制、全球定位系统等; ☆ 工业领域,如机器人技术、数控机床、数字电机、 力系统、生产过程模拟和控制等; ☆ 仪器仪表,如频谱分析、函数发生器、暂态分析、 相环、数字示波器等; ☆ 自动控制,如伺服控制、机器人控制、自适应控制、 人工神经网络控制等; ☆ 医疗仪器,如助听、超声设备、诊断工具、病人监 ☆ 消费电子电器,如高保真音响、高清晰度电视、音 合成、音调控制、玩具与游戏等。

OMAPTM

C5421

OMAP5910

C55x+ARM9 C54x +ARM7

C5420

C5471 TM

C55xTM DSP C5510 C5509

320-400 MIPS

C54x+ARM7

C5470

C5502 C5409 C5410

100-160 MIPS

C5416

120-160 MIPS

600 MIPS

Copyright © 2003 Texas Instruments. All rights reserved.

TMS320C54x系列DSP的特点

CPU

☆ 先进的多总线结构; ☆ 40位算术逻辑单元(ALU):一个40位桶式移位器和两个 独立的40位累加器; ☆ 17位 X 17位并行乘法器和一个40位专用的加法器; ☆ 比较、选择、存储单元(CSSU); ☆ 指数编码器E,用来在一个单周期内计算一个40位累加器中 数值的指数; ☆ 两个地址产生器,包括八个辅助寄存器和两个辅助寄存器算 术单元。

Copyright © 2003 Texas Instruments. All rights reserved.

TI常用三种系列 DSP

Copyright © 2003 Texas Instruments. All rights reserved.

TI Extends World’s Most Popular DSP Platform

TMS320C5000™ : The World’s Most Popular and Power Efficient DSPs

Copyright © 2003 Texas Instruments. All rights reserved.

DSP概述 DSP概述

数字信号处理是一门广泛应用于许多领域的新兴学科。 20世纪60年代以来,随着计算机和信息技术的飞速发展,数 字信号处理技术应运而生并得到迅速的发展。

160 MIPS 128K words SRAM 16K words ROM 3 McBSPs 6-channel DMA 8/16-bit HPI Extended Program Addressing

Low Power

1.5-V core 90 mW active @ 160 MIPS

EXP Encoder Accumulators 40-Bit ACC A 40-Bit ACC B

Copyright © 2003 Texas Instruments. All rights reserved.

C54x

Copyright © 2003 Texas Instruments. All rights reserved.

’C5416:

Program/Data ROM Program/Data ROM 16K Words 16K Words D(15-0)

Copyright © 2003 Texas Instruments. All rights reserved.

TMS320C54x系列DSP概述

☆ 增强的哈佛结构; ☆ 具有高度平行和带有专门硬件逻辑的先进CPU设计; ☆ 为快速算法而设计的高度专用的指令系统以及优化 的高级语言开发系统; ☆ 模块化结构设计; ☆ 高性能和低功耗的先进IC工艺技术; ☆ 新的静电设计结构而获得的低功耗和增强的抗辐射 能力。

Program/Data Buses Program/Data Buses A(23-0) MAC 17 x 17 MPY 40-Bit Adder RND, SAT Shifter 40-Bit Barrel (-16, 31) ALU 40-Bit ALU

CMPS Operator (VITERBI)

Copyright © 2003 Texas Instruments. All rights reserved.

TMS320系列DSP简介 TMS320系列DSP简介

TMS320系列DSP包括定点、浮点、多处理器DSP和定点 DSP控制器。TMS320系列DSP的体系结构专为实时信号处理 而设计,该系列DSP控制器将实时处理能力和控制器外设功能 集于一身,为控制系统应用提供了一个理想的解决方案。下列 特性使TMS320系列DSP成为很多信号处理及控制应用的正确 选择: ☆ 非常灵活的指令集; ☆ 内部操作的灵活性; ☆ 高速运算能力; ☆ 改进的并行结构; ☆ 低功耗; ☆ 面向C语言的软件系统。

Copyrightl rights reserved.

DSP系统的特点

☆ 接口和编程方便灵活; ☆ 稳定性、可靠性好; ☆ 精度高; ☆ 时分复用; ☆ 易于集成;

Copyright © 2003 Texas Instruments. All rights reserved.

DMA

Ch 0 Ch 1 Ch 2 Ch 3 Ch 4 Ch 5 Peripheral Bus Peripheral Bus

Timer Timer 8/16-bit Host Port 8/16-bit Host Port Interface (HPI) Interface (HPI)

Multichannel Buffered Multichannel Buffered Serial Port (McBSP) Serial Port (McBSP) Multichannel Buffered Multichannel Buffered Serial Port (McBSP) Serial Port (McBSP) Multichannel Buffered Multichannel Buffered Serial Port (McBSP) Serial Port (McBSP)