DSP 存储器

DSP工作原理

DSP工作原理一、简介DSP(Digital Signal Processor,数字信号处理器)是一种专门用于数字信号处理的微处理器。

它具有高性能、低功耗和高度可编程的特点,广泛应用于通信、音频、视频、雷达、医疗等领域。

本文将详细介绍DSP的工作原理。

二、DSP的基本组成1. 数据通路(Data Path):数据通路是DSP的核心部分,用于执行算术运算、逻辑运算和数据传输等操作。

数据通路由运算器、寄存器和数据通路控制器组成。

2. 控制器(Controller):控制器用于控制DSP的操作,包括指令的获取、解码和执行等功能。

控制器由指令寄存器、程序计数器和控制单元等组成。

3. 存储器(Memory):存储器用于存储程序代码、数据和中间结果等信息。

存储器包括指令存储器(程序存储器)和数据存储器。

4. 外设接口(I/O Interface):外设接口用于与外部设备进行数据交换,如与传感器、显示器、键盘等设备的连接。

三、DSP的工作流程1. 指令获取阶段:DSP从指令存储器中获取指令,并将其存储到指令寄存器中。

2. 指令解码阶段:DSP解码指令,确定执行的操作类型和操作数。

3. 数据处理阶段:根据指令中的操作类型和操作数,DSP执行算术运算、逻辑运算或数据传输等操作。

这些操作通常涉及数据的加载、存储、运算和传输。

4. 结果存储阶段:DSP将计算结果存储到数据存储器中,以备后续使用。

5. 控制流程阶段:DSP根据控制指令中的条件判断,决定下一条要执行的指令的地址。

6. 循环处理:DSP可以通过循环指令实现对一段代码的重复执行,实现高效的数据处理。

四、DSP的优势1. 高性能:DSP具有专门优化的指令集和硬件结构,能够快速执行复杂的信号处理算法。

2. 低功耗:DSP采用高度优化的架构和电源管理技术,能够在低功耗下实现高性能的信号处理。

3. 高度可编程:DSP具有灵活的指令集和丰富的外设接口,使其能够适应各种不同的应用需求。

DSP存储空间的配置

DSP存储空间的配置在DSP的开发过程中,开发者难免会遇到DSP芯片内部存储器和片外扩展存储器的配置等问题。

本文以TMS320C54x系列DSP为例,讨论DSP存储空间的分配问题。

存储器空间'C54x系列DSP存储器分为三个独立选择的空间—程序、数据和I/O,其中程序存储器存放待执行的指令和执行中所用的系数(常数),可使用片内或片外的RAM、ROM或EPROM等来构成;数据存储器存放指令执行中产生的数据,可使用片内或片外的RAM和ROM来构成。

I/O存储器存放与映象外围接口相关的数据,也可以作为附加的数据存储空间使用。

这三个空间的寻址范围取决于DSP芯片地址线数目。

例如,'C54x系列DSP 从'C548开始,芯片有23根地址线,具有8M字节存储空间寻址能力。

'C54x通过包含在处理器工作方式的状态寄存器(PMST)中的3个状态位,选择片内存储器作为程序空间或数据空间。

这3个状态位是:1.MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM不安排到程序空间。

2.OVLY位。

OVLY=1,则片内RAM安排到程序和数据空间;OVLY=0,则片内RAM只安排到数据存储空间。

3.DROM位。

当DROM=1,则部分片内ROM安排到数据空间;DROM=0,则片内ROM不安排到数据空间。

程序设计者可根据不同的需求,相应的配置这3个位,使系统的存储空间满足应用要求。

同时,为了扩展'C54x系列DSP的寻址空间,还增加了一个额外的存储器映像寄存器—程序计数器扩展寄存器XPC,以及6条寻址扩展程序空间的指令。

以TMS320C5410为例,它的程序空间分成128页面,每页64K字。

该64K字程序空间分为两部分:一部分是公共的32K 字,另一部分是各自独立的32K字。

公共存储器为所有页面共享,每个页面独立的32K字存储器只能按指定的页面号寻址,这个页面号由XPC寄存器设定。

DSP概述及存储器

60% Core Performance Boost Vs C’5409

High Performance

JTAG Test/ JTAG Test/ Emulation Emulation Control Control Muxed GP I/O Muxed GP I/O

Program/Data SRAM Program/Data SRAM 128K Words 128K Words

Copyright © 2003 Texas Instruments. All rights reserved.

TMS320C54x系列DSP TMS320C54x系列DSP

TMS320C54x系列DSP概述

C54x DSP具有很高操作灵活性和速度。它具有先进的修 正哈佛结构(一条程序总线、三条数据总线和四条地址总线)、 专门硬件逻辑的CPU、片内存储器、片内外设和专用的指令集、 将C54x DSP的CPU和片内存储器与外设配置组合在一起的螺 旋结构,使得它可以满足电子市场众多领域的应用要求: C54x DSP具有以下优点:

DSP的应用

DSP已经在信号处理、通信、雷达等领域得到广泛的应 用。目前,DSP的价格越来越低,性能价格比日益提高,具 有巨大的应用潜力。DSP的应用主要有: ☆ 用数字信号处理,如数字滤波、自适应滤波、相关 算、快速傅立叶变换等; ☆ 通信领域,如数据加密、数据压缩、传真、移动电 网络通信等; ☆ 语音处理,如语音编码、语音合成、语音识别、语 增强、语音存储等; ☆ 图形/图像,二维或三维图形处理、图像压缩与传输、 指纹识别、图像识别等;

DSP主要特点

根据数字信号处理的要求,DSP一般具有如下的主要特点: ☆ 在一个指令周期内,可完成一次乘法和一次加法; ☆ 程序和数据空间分开,可以同时访问指令和数据; ☆ 片内具有快速RAM,通常可通过独立的数据总线, 在两块芯片中同时访问; ☆ 具有低开销或无开销循环及跳转的硬件支持; ☆ 快速的中断处理和硬件I/O接口支持; ☆ 具有在单周期内操作的多个硬件地址产生器; ☆ 可以并行执行多个操作; ☆ 支持流水线操作,使取指、译码、取操作数和执行等 操作可以重叠执行。

DSP第2章 'C54x的硬件结构2

2013年8月15日

DSP原理及应用

6

3.工作方式状态寄存器PMST

主要设定和控制处理器的工作方式和存储器的配置,反映 处理器的工作状态。

15~7 6 5 4 AVIS 3 2 1 0 SST

IPTR MP/MC OVLY

DROM CLKOFF SMUL

中 断 向 量 指 针

CPU 工 作 方 式 选 择 位

③ 暂存器SPRAM。

2013年8月15日

DSP原理及应用

14

特殊功能寄存器

功能:主要用于程序的运算处理和寻址方式的选

择和设定。地址范围:0000H~001FH。 外设寄存器 ’C5402的CPU寄存器共有27个,CPU访问这 功能:用来控制片内外设电路的状态和存放数据。 些寄存器时,不需要插入等待时间。 地址范围:0020H~005FH。 包括串行口通信控制寄存器组、定时器定时控 暂存器SPRAM 制寄存器组、时钟周期设定寄存器组等。 功能:用来暂存变量。地址范围:0060H~007FH。

中断屏蔽寄存器 10H 中断标志寄存器 11H 保留 ( 用于测试 ) 12H 保留 ( 用于测试 ) 13H 保留 ( 用于测试 ) 14H 保留 ( 用于测试 ) 15H 状态寄存器0 16H 状态寄存器1 17H 累加器A低字(15~0位) 18H 累加器A高字(31~16位) 19H 累加器A保护位(39~32位) 1AH 累加器B低字(15~0位) 1BH 累加器B高字(31~16位) 1CH 累加器B保护位(39~32位) 1DH 暂存寄存器 1EH DSP原理及应用 状态转移寄存器 1FH

2013年8月15日

存储器映像的CPU寄存器, 存储器映像的外设寄存器 特殊功能寄存器

DSP28335 DMA模块及寄存器中文资料

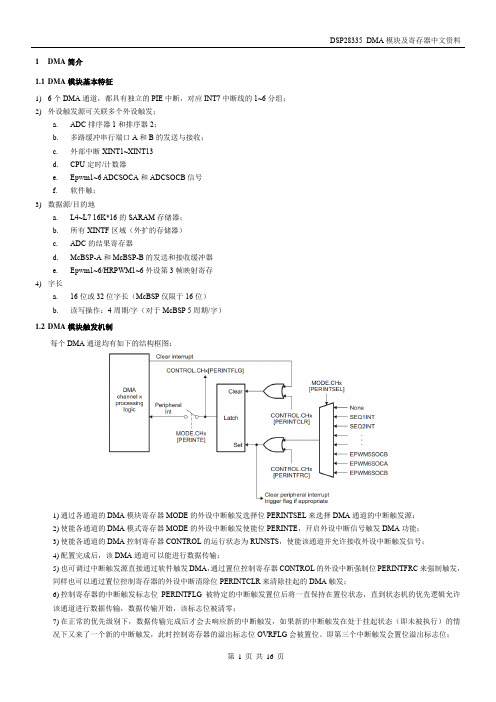

1DMA简介1.1DMA模块基本特征1)6个DMA通道,都具有独立的PIE中断,对应INT7中断线的1~6分组;2)外设触发源可关联多个外设触发;a.ADC排序器1和排序器2;b.多路缓冲串行端口A和B的发送与接收;c.外部中断XINT1~XINT13d.CPU定时/计数器e.Epwm1~6 ADCSOCA和ADCSOCB信号f.软件触;3)数据源/目的地a.L4~L7 16K*16的SARAM存储器;b.所有XINTF区域(外扩的存储器)c.ADC的结果寄存器d.McBSP-A和McBSP-B的发送和接收缓冲器e.Epwm1~6/HRPWM1~6外设第3帧映射寄存4)字长a.16位或32位字长(McBSP仅限于16位)b.读写操作:4周期/字(对于McBSP 5周期/字)1.2DMA模块触发机制每个DMA通道均有如下的结构框图:1)通过各通道的DMA模块寄存器MODE的外设中断触发选择位PERINTSEL来选择DMA通道的中断触发源;2)使能各通道的DMA模式寄存器MODE的外设中断触发使能位PERINTE,开启外设中断信号触发DMA功能;3)使能各通道的DMA控制寄存器CONTROL的运行状态为RUNSTS,使能该通道并允许接收外设中断触发信号;4)配置完成后,该DMA通道可以能进行数据传输;5)也可调过中断触发源直接通过软件触发DMA,通过置位控制寄存器CONTROL的外设中断强制位PERINTFRC来强制触发,同样也可以通过置位控制寄存器的外设中断清除位PERINTCLR来清除挂起的DMA触发;6)控制寄存器的中断触发标志位PERINTFLG被特定的中断触发置位后将一直保持在置位状态,直到状态机的优先逻辑允许该通道进行数据传输,数据传输开始,该标志位被清零;7)在正常的优先级别下,数据传输完成后才会去响应新的中断触发,如果新的中断触发在处于挂起状态(即未被执行)的情况下又来了一个新的中断触发,此时控制寄存器的溢出标志位OVRFLG会被置位。

DSP工作原理

DSP工作原理标题:DSP工作原理引言概述:数字信号处理(DSP)是一种数字化信号处理技术,广泛应用于通信、音频、视频等领域。

DSP工作原理是指数字信号处理器如何处理输入信号并输出处理后的信号的过程。

本文将详细介绍DSP的工作原理。

一、数字信号处理器的输入和输出1.1 输入信号的采集:DSP通过模数转换器将摹拟信号转换为数字信号,以便进行数字信号处理。

1.2 处理信号的算法:DSP通过内置的算法对输入信号进行处理,如滤波、变换、编码等。

1.3 输出信号的重构:DSP通过数模转换器将数字信号转换为摹拟信号,输出处理后的信号。

二、数字信号处理器的运算方式2.1 固定点运算:DSP采用固定点数表示和运算,可以实现高速运算和低成本。

2.2 浮点运算:某些DSP支持浮点运算,可以提高计算精度和动态范围。

2.3 SIMD并行处理:DSP支持单指令多数据流(SIMD)并行处理,可以同时处理多个数据。

三、数字信号处理器的存储结构3.1 数据存储器:DSP内置数据存储器用于存储输入信号、中间结果和输出信号。

3.2 程序存储器:DSP内置程序存储器用于存储处理信号的算法和指令。

3.3 寄存器:DSP具有多个寄存器用于存储中间结果和控制信息。

四、数字信号处理器的时钟和控制4.1 时钟频率:DSP的时钟频率决定了其处理速度和性能。

4.2 控制单元:DSP内置控制单元用于控制数据流和算法执行顺序。

4.3 中断处理:DSP支持中断处理机制,可以及时响应外部事件和优先处理重要任务。

五、数字信号处理器的应用领域5.1 通信系统:DSP广泛应用于调制解调、信道编解码、自适应滤波等通信系统中。

5.2 音频处理:DSP用于音频滤波、均衡、编解码和音频效果处理。

5.3 视频处理:DSP用于视频编解码、图象处理、运动估计和视频增强。

结论:数字信号处理器是一种高效、灵便的信号处理器件,其工作原理涉及输入输出、运算方式、存储结构、时钟控制和应用领域等方面。

DSP外部Flash存储器的自烧写方式研究

自烧 写就是指 烧写程序 将 自身 的一部分 作为代 码烧写 到 D P外部 的 Fah存储 器 中 ,从而实 现在线 或在系 统对 Fah S ls ls 存 储 器 的编程 。这种 方 式可 用 于某 些特 殊 场合 ,如无 外 部

R AM 的单片 D P系统的在线编程。 S

在许 多嵌入式 系统 中 ,由于设 备体 积和成本 考虑 ,在 项

目设 计之初 就尽可 能减 少元器件 的用量 ,以节省 成本 。有 的 项 目由于批量 很大 ,甚 至连 电阻 电容都要讨 价还价到分 以下 。

a u 输入文件名 ,比如 a u* .t o . t/ o a , 丰选项 :指定输 出为 AS I十六进制文件格式 , CI i g 选项 :创建完整的 R M 映像 / ma e O zr eo 选项 :设置地址从零开始 , me it 6 mw d 1 选项 :设定存储器宽度为 l h 6位 / ma e . p ph x ma 选项 :指定输 出映像文件 /

jc d t e e ddi xctbefei po a me t teFahme oyw e eeeu be l i rn i ,op r r et a m d e eeual i rg m di oh l m r h nt xct l fe s u nn t ef m ab n l s r n s h a i g o

DSP芯片应用系列讲座_二_第4讲TMS320F281xDSP的存储器系统

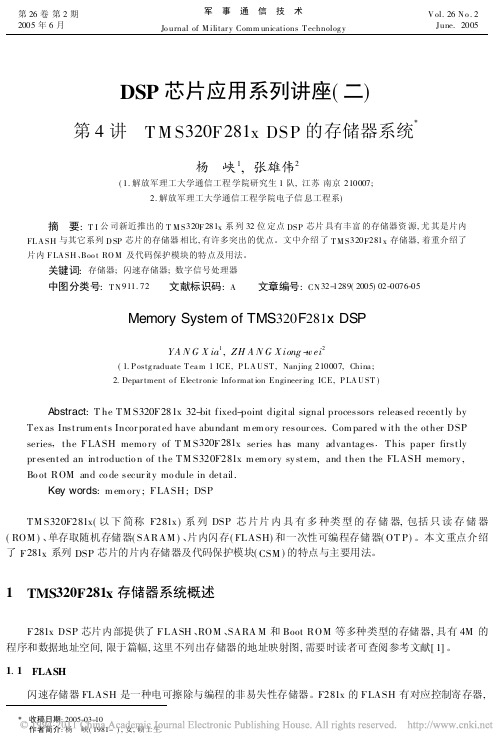

DSP 芯片应用系列讲座(二)第4讲 T M S 320F 281x DSP 的存储器系统杨 峡1,张雄伟2(1.解放军理工大学通信工程学院研究生1队,江苏南京210007;2.解放军理工大学通信工程学院电子信息工程系)摘 要:T I 公司新近推出的T M S 320F 281x 系列32位定点DSP 芯片具有丰富的存储器资源,尤其是片内FL A SH 与其它系列D SP 芯片的存储器相比,有许多突出的优点。

文中介绍了T M S 320F 281x 存储器,着重介绍了片内F LA SH 、Boo t RO M 及代码保护模块的特点及用法。

关键词:存储器;闪速存储器;数字信号处理器中图分类号:T N 911.72文献标识码:A文章编号:CN 32-1289(2005)02-0076-05Memory System of TMS 320F 281x DSPYA N G X ia 1,ZH A N G X iong -w ei 2(1.P ostg raduate T ea m 1ICE,P L A U ST ,Nanjing 210007,China ;2.Depar tment o f Electr onic Info rmat ion Engineer ing ICE,P LA U ST )Abstract :T he TM S320F281x 32-bit fixed-point digital signal processors released recently by Tex as Instrum ents Incor porated have abundant m em ory resour pared w ith the other DSP series ,the FLASH memo ry of T M S 320F 281x series has many advantag es .This paper firstly pr esented an introductio n of the TM S320F281x m em ory sy stem,and then the FLASH memory ,Bo ot ROM and co de secur ity mo dule in detail.Key words :m em ory ;FLASH ;DSPTM S320F281x(以下简称F281x )系列DSP 芯片片内具有多种类型的存储器,包括只读存储器(ROM )、单存取随机存储器(SARAM )、片内闪存(FLASH)和一次性可编程存储器(OT P)。

DSP数据存取试验报告

DSP数据存取试验报告

本文主要介绍DSP数据存取试验的相关内容和试验结果。

试验是在一个半导体公司的开发板上进行的,主要涉及到DSP芯片的数据存取性能测试。

在试验之前,我们需要先了解一些DSP芯片的相关知识。

DSP芯片在数据存取方面有两种方式:DSP本地存储器和外部存储器。

DSP本地存储器包括片上存储器(Internal Memory)和片上寄存器(Internal Registers),而外部存储器包括外部RAM(External Memory)和外部Flash(External Flash)。

DSP本地存储器具有速度快、访问方便等优点,但存储空间相对较小。

而外部存储器则存储容量大,但访问速度相对慢。

因此,在实际应用中需要根据具体情况选择合适的存储器。

试验首先测试了DSP本地存储器的读写速度。

试验采用的是32位的定点数,在DSP本地存储器中存储20000个数,接着进行读写操作。

试验结果如下:

读取速度:10.5MB/s

可以看出,DSP本地存储器的读取速度明显高于写入速度。

这是由于读取时只需要在存储器中查找数据,而写入时需要将数据写入存储器,因此速度较慢。

综上所述,本次试验主要测试了DSP芯片的数据存取性能,对比了DSP本地存储器和外部存储器的性能优劣。

试验结果表明,在数据存取方面,DSP本地存储器的速度明显优于外部存储器,但存储容量较小。

因此,在实际应用中需要根据具体需求选择不同的存储器。

DSP寻址方式

DSP寻址方式DSP(数字信号处理器)是一种专门用于数字信号处理的微处理器,其寻址方式是指DSP芯片对于内部存储器的寻址方式。

DSP寻址方式是DSP系统中非常重要的一部分,它决定了DSP芯片如何有效地访问和处理存储在内部存储器中的数据。

1. 直接寻址方式直接寻址方式是DSP中最简单的寻址方式之一。

在直接寻址方式下,指令中给出的地址直接用于指定待访问的存储单元。

这种寻址方式适用于数据存储单元数量较少且地址连续的情况。

例如,当使用直接寻址方式时,指令可以直接指定访问DSP内部存储器中的某个特定地址,无需进行地址转换或计算。

2. 间接寻址方式间接寻址方式是另一种常用的DSP寻址方式。

在间接寻址方式下,指令中给出的地址并不直接用于指定待访问的存储单元,而是用于指定一个包含存储单元地址的寄存器。

通过间接寻址方式,可以实现更加灵活的地址访问,尤其适用于需要频繁对不同存储单元进行访问的情况。

3. 基址寻址方式基址寻址方式是一种常用的寻址方式,它结合了直接寻址方式和间接寻址方式的优点。

在基址寻址方式下,指令中给出的地址作为“基址”,并结合一个偏移量用于计算访问目标存储单元的实际地址。

通过基址寻址方式,可以实现对存储单元的相对寻址,而无需显式地指定存储单元的具体地址。

4. 变址寻址方式变址寻址方式是一种基于寄存器的寻址方式,它通过使用一个特殊的寄存器,称为“变址寄存器”来实现寻址。

变址寻址方式可以对存储单元的地址进行动态调整,从而实现对存储单元的高效访问。

通过改变变址寄存器中的值,可以改变访问目标存储单元的地址,从而灵活地处理不同的数据访问需求。

5. 直接/间接寻址方式直接/间接寻址方式是一种结合了直接寻址方式和间接寻地址方式的寻址方式。

在直接/间接寻址方式下,指令中既给出了一个直接的地址用于直接寻址,又给出了一个指示寄存器的地址用于间接寻址。

通过使用直接/间接寻址方式,可以在同时满足直接访问和间接访问需求的情况下,提高DSP系统的灵活性和效率。

DSP芯片的基本结构和特征

DSP芯片的基本结构和特征引言DSP芯片(Digital Signal Processor,数字信号处理器)是一种专用于数字信号处理任务的微处理器。

它具有高处理速度和低功耗等特点,广泛应用于音频、视频、通信、雷达、图像处理等领域。

本文将介绍DSP芯片的基本结构和特征,以便读者更好地了解和应用该技术。

1. DSP芯片的基本结构DSP芯片的基本结构通常包括三个主要部分:中央处理单元(CPU)、存储器和数字信号处理模块。

下面将详细介绍这些部分的功能和特点。

1.1 中央处理单元(CPU)中央处理单元是DSP芯片的核心,负责控制和执行指令。

它通常由一个或多个运算单元(ALU)和一个控制单元组成。

ALU负责执行算术和逻辑运算,而控制单元则负责解码和执行指令序列。

中央处理单元是DSP芯片实现高速运算的关键部分。

1.2 存储器存储器是DSP芯片的重要组成部分,用于存储程序代码、数据和中间结果。

它通常包括两种类型的存储器:指令存储器(程序存储器)和数据存储器。

指令存储器用于存储程序代码和指令,而数据存储器用于存储数据和中间结果。

存储器的大小和访问速度对DSP芯片的性能有重要影响。

1.3 数字信号处理模块数字信号处理模块是DSP芯片的核心功能模块,用于执行数字信号处理任务。

它通常包括以下几个功能单元:时钟和定时器单元、数据通路单元、乘法器和累加器(MAC)单元以及控制逻辑单元。

时钟和定时器单元用于提供时序控制和定时功能,数据通路单元用于数据传输和处理,乘法器和累加器单元用于高速乘加运算,控制逻辑单元用于控制和协调各个功能单元的操作。

2. DSP芯片的特征DSP芯片相较于通用微处理器具有一些明显的特征,下面将介绍几个主要特征。

2.1 高速运算能力DSP芯片具有高速运算能力,主要得益于其专门的运算单元和并行处理能力。

相较于通用微处理器,DSP芯片能够更快地执行算术和逻辑运算,满足实时信号处理的需求。

2.2 低功耗设计DSP芯片在设计过程中注重功耗的控制,以满足移动设备和嵌入式系统等低功耗应用的需求。

DSP课件第2章硬件结构

5、电源

采用高性能静态CMOS技术,供电电压为3.3V。 可用IDLE指令进入低功耗模式。

6、在片仿真接口

具有符合IEEEll49.1标准的在片仿真接口(JTAG)。

7、速度

单周期定点指令的执行时间为50ns、35ns或25ns(20MIPS,28.5MIPS, 或40MIPS)。

2.2 TMS320LF240x的总线结构

INTM:中断模式位

用来允许(INTM=0)或禁止(INTM=1)所有的可屏蔽中断。用 SETC OVM或CLRC OVM可将该位置1或清0。LST指令不影响OVM位。

DP:数据页面指针

当使用直接寻址方式时,DP存放存储器的数据页,DP与指令代 码的最低7位构成16位存储器地址。

数据存储器地址

SARAM的地址可以用于数据存储器和程序存储器。可通过软件配置 为外部存储器或内部SARAM。

SARAM在一个机器周期内只能访问一次。当CPU要求多次访问时, SARAM会向CPU提供一个未准备好的信号,然后在每个周期内执行一次 访问。

闪速存储器(Flash) 是电可擦除的、可编程的、可长期保存数据的存储器。

CPU的基本组成包括: 32位中央算术逻辑运算单元(CALU); 32位累加器(ACC);输入与输出数据比例移位器; 16位×16位的乘 法器(MUL)以及乘积比例移位器。

CPU功能结构图

2、输入比例部分

功能:将来自存储器的16位数据左移0~16位送往中央算术逻辑单元 (CALU)。

移位方法:左移后有使用的低位LSB填0,高位MSB填0或用符号 扩展,取决于状态寄存器ST1的符号扩展模式位SXM(D10)。 SXM=0 填0 SXM=1 符号扩展

中央算术逻辑单元

(整理)DSP存储空间的分配问题.

在DSP的开发过程中,开发者难免会遇到DSP芯片内部存储器和片外扩展存储器的配置等问题。

本文以TMS320C54x系列DSP为例,讨论DSP存储空间的分配问题。

存储器空间'C54x系列DSP存储器分为三个独立选择的空间—程序、数据和I/O,其中程序存储器存放待执行的指令和执行中所用的系数(常数),可使用片内或片外的RAM、ROM或EPROM等来构成;数据存储器存放指令执行中产生的数据,可使用片内或片外的RAM和ROM来构成。

I/O存储器存放与映象外围接口相关的数据,也可以作为附加的数据存储空间使用。

这三个空间的寻址范围取决于DSP芯片地址线数目。

例如,'C54x系列 DSP 从'C548开始,芯片有23根地址线,具有8M字节存储空间寻址能力。

'C54x通过包含在处理器工作方式的状态寄存器(PMST)中的3个状态位,选择片内存储器作为程序空间或数据空间。

这3个状态位是:(1)MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM不安排到程序空间。

(2)OVLY位。

OVLY=1,则片内RAM安排到程序和数据空间;OVLY=0,则片内RAM只安排到数据存储空间。

(3)DROM位。

当DROM=1,则部分片内ROM安排到数据空间;DROM=0,则片内ROM不安排到数据空间。

程序设计者可根据不同的需求,相应的配置这3个位,使系统的存储空间满足应用要求。

同时,为了扩展'C54x系列DSP的寻址空间,还增加了一个额外的存储器映像寄存器—程序计数器扩展寄存器XPC,以及6条寻址扩展程序空间的指令。

以TMS320C5410为例,它的程序空间分成128页面,每页64K字。

该64K字程序空间分为两部分:一部分是公共的32K字,另一部分是各自独立的32K字。

公共存储器为所有页面共享,每个页面独立的32K字存储器只能按指定的页面号寻址,这个页面号由XPC寄存器设定。

第2章-DSP内核结构及存储器映射

中央算术逻辑单元执行大部分的算术和逻辑运算功能,并且实现大多数 的功能都只要1个时钟周期,这些功能包括:16位加、16位减、布尔逻辑操作、 位测试、移位和循环功能。有关中央算术逻辑单元的结构框图,如下图。

2.1 CPU内部结构

2.1.4 累计器(ACC)

当CALU工作时,会将计算结果送至32位累加器,累计器负责将结果进行 单移位或者循环移位,然后将结果输出到数据定标移位器。

2.2 存储器和I/O空间

❖ I/O空间的访问都可用IN和OUT指令。当用IN或OUT指令时,信号IS将变成有效, 因此可用信号IS作为外围I/O设备的片选信号。访问外部I/O端口与访问程序存储器、 数据存储器复用相同的地址总线和数据总线。数据总线的宽度为16位,若使用8位 的外设,即可使用高8位数据总线,也可使用低8位数据总线,以适应特定应用的 需要。

块模1C令时。L时块,钟K置O钟时芯使进1U且钟片能行后T正且进该锁引需常正入模相脚要运常那块倍输用行运种时频出户;行低钟的C用P当;功,系软U该当耗以数时件位该模使。钟清值位式当A;0/,为值。C当DL清为0转该K时0P0换位的S,时正=值方禁,0常为法0止禁进01是该止时行对模该4,;倍该块模C当频位L时块该K;写钟时O位当1U。钟值。T。引为检脚0

2.2.5 外部存储器接口及其操作

1. 外部存储器接口简介

这 里 以 TMS320LF2407A 为 例 介 绍 外 部 存 储 器 接 口 及 其 操 作 , TMS320LF2407A包含2K×16位字的SARAM和544×16位字的片上DARAM, 其中DARAM被分成B0、B1和B2三个单元。通过不同的设置,可将SARAM 和DARAM的B0单元用作程序存储器,又可将它们用作数据存储器。当系统 用慢速的程序存储器存放程序时,为提高运行速度,通常将程序放到SARAM 和DARAM的B0单元中;此时这部分RAM映射到程序空间。对于许多应用来 说,仅有的SRAM是不够的,需要进行扩展来作为程序存储器或数据存储器。

TMS320C54x系列DSP的CPU与外设——第3章存储器

TMS320C54x系列DSP的CPU与外设——第3章存储器第3章存储器本章介绍了TMS320C54x DSP存储器的构成和操作。

⼀般来说,C54x器件共有192K 16位字的存储窨,这个空间分成3个专⽤的部分:64K字程序、64K字数据和64K字I/O⼝。

在某些C54x器件中,存储器结构已经通过重叠和分页的⽅法加以改变,这样就增加了存储器空间的容量。

C54x体系结构上的并⾏特点和⽚内RAM的双存取能⼒使C54x可以在任意给定的机器周期内同时进⾏4个存储器操作:⼀条指令的读取操作、两个操作数读操作以及⼀个操作数写操作。

在⽚内存储器中操作有如下⼏个优点:Higher performance because no wait states are requiredLower cost than external memoryLower power than external memoryThe main advantage of operating from off-chip memory is the ability to access a larger memory space.3.1 存储器空间C54x DSP的存储器划分成3种独⽴可选的空间:程序、数据和I/O。

这些空间中的RAM、ROM、EPROM、EEPROM或者存储器映射的外设可以位于⽚内或⽚外。

程序存储器中包含要执⾏的指令和执⾏指令时所需的表,数据存储器空间存储指令所需的数据,I/O存储空间连接外部的存储器映射外设,也可作外部数据存储空间。

按芯⽚各类的不同,C54x的⽚内存储器有这样⼏种类型:双存取RAM(DARAM)、单存取(SARAM)、双向共享RAM和ROM。

RAM总是映射到数据空间,但也可以映射到程序空间。

ROM可以被激活并映射到程序空间,也可部分映射到数据空间。

在CPU状态寄存器中有3位影响存储器的结构。

这3位产⽣的影响因器件不同⽽不同。

如何设计TMS320C32 DSP的存储器接口

S R 1 从 8 1 / 2位 存储 器 中访 问 8 1 / 2位 数 据 , T B能 /63 /63 或 从 1/2 存储器 中执行 3 63 位 2位 程 序 ; S R 是 外 设 IO I T B O /

1 T 30 3 MS 2 0 2的外 部存 储 器接 口的 特 点

TMS 2 C3 3 0 2是 一 个 3 2位 微 处 理 器 , 可 通 过 2 它 4位

图 1中 , 脚 P G 是 用 来 配 置 外 部 程 序 存 储 器 宽 引 R W 度 的 。当 P G 引 脚 为 低 电 平 时 程 序 存 储 器 宽 度 为 1 R W 6

p e mstO. ( 稿专 ) a r eeClc投 用 p @ n.I n 3 .

Mcc t1s me eS t s 7 i。 n。 r&E b d sm r。 re 1 d d ye 5

接口 控制 存器

接

口

B 1

} 62 在1 3 宽度的 / 存储器中

I 访问3位程序 2

面

— — .

在3 位 宽度 的存储器 中访问 2 3 位数据 和3 位 程序 2 2

空间 。其 中, T B 所对应 的存储 映像 区间是不连续的两 S R0

段 区间 , 段 是 0 FH~ 7 F F 一 3 F F FH( 3 . 9 共 1 9 9 MB) 另 一 ,

维普资讯

2 T 30 3 MS 2 C 2的 3种 存 储 器 设 计 方 案

2 1 8位 存储 器 宽 度 .

设 计 为 8 的存 储 器 , 硬 件 接 线 方 案 如 图 2所 示 。 位 其

的存 储 器 中访 问 8 1 / 2 数 据 或 程 序 。也 就 是 说 , 以 /63 位 可 从 任 何 一 个 外 部 存 储 器 中 访 问 任 何 一 种 类 型 的 数 据 。 这 就说 明 可 以通 过 设 置 I S R 、 T 0 S R 1 O T B S RB 和 T B 的选 通 信 号 来 寻 址 整 个 外 部 存 储 器 空 间 。 比如 , 个 3 一 2位 外 部 存

DSP4系统与实验教程_2812存储器

2812的存储器配置本堂课我们来介绍存储器映像及CMD文件的编写,这部分内容较多,也是DSP区别于单片机的主要表现之一。

尤其是CMD文件的编写,工作中很多DSP的工作都是要围绕这个部分的内容进行,编写好的CMD文件也是衡量一个工程师水平高低的最好的体现。

那么我们现在就开始今天的课程。

第一节Memory简介在我们买计算机的时候,硬盘空间的大小是衡量计算机性能指标之一,在嵌入式DSP的工作时,存储器同样也是衡量的标准之一。

1.1What’s the memory?存储器是存放DSP运行过程中指令、代码、数据的地方,存储器的大小也直接影响到我们所编写的程序。

如果我们的程序量较大但选择了存储空间小的DSP时候,(工作中也经常遇到这样的问题,解决的方式之一就是充分的分析代码,看看能否压缩;第二就是将C语言改写成汇编语言)。

1.22812的memory的结构下面我们来看一下2812存储器的结构,是由那几部分组成的。

2812的CPU是不含有存储器的,但他可以访问片内也可访问片外的存储器。

2812的存储器分为这几个方面:1.程序或数据存储器1)单口随机存储器SRAM2)只读存储器ROM3)FLASH(3D 8000~3F 7FFF)共划分为ABCDEFGHIJ.A端地址(3F 6000~3F 7FFF)【注:FlashA】为Flash的高地址段最高的部分用于其他的功能【注:The difference between RAM & FLASH】平时先调试程序的时候,先将程序存放在RAM空间,限电丢失,一方面执行速度较快,另一方面下载速度较快;等到程序调试完毕后,程序下载到FLASH空间中。

他们可以被映射到程序空间或数据空间。

有同学会问“映像”是什么意思,英文“map”,意思是可以被分配用于程序空间(指令代码)或数据空间(数据资源)。

【注:the memory map in 2812】【注:Symbol】我们存储器的容量大小通常使用多少K*16位来表示。

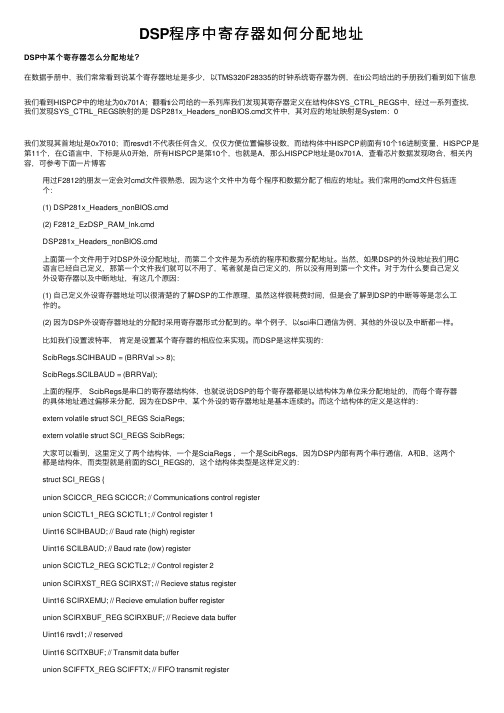

DSP程序中寄存器如何分配地址

DSP程序中寄存器如何分配地址DSP中某个寄存器怎么分配地址?在数据⼿册中,我们常常看到说某个寄存器地址是多少,以TMS320F28335的时钟系统寄存器为例,在ti公司给出的⼿册我们看到如下信息我们看到HISPCP中的地址为0x701A;翻看ti公司给的⼀系列库我们发现其寄存器定义在结构体SYS_CTRL_REGS中,经过⼀系列查找,我们发现SYS_CTRL_REGS映射的是 DSP281x_Headers_nonBIOS.cmd⽂件中,其对应的地址映射是System:0我们发现其⾸地址是0x7010;⽽resvd1不代表任何含义,仅仅⽅便位置偏移设数,⽽结构体中HISPCP前⾯有10个16进制变量,HISPCP是第11个,在C语⾔中,下标是从0开始,所有HISPCP是第10个,也就是A,那么HISPCP地址是0x701A,查看芯⽚数据发现吻合,相关内容,可参考下⾯⼀⽚博客⽤过F2812的朋友⼀定会对cmd⽂件很熟悉,因为这个⽂件中为每个程序和数据分配了相应的地址。

我们常⽤的cmd⽂件包括连个:(1) DSP281x_Headers_nonBIOS.cmd(2) F2812_EzDSP_RAM_lnk.cmdDSP281x_Headers_nonBIOS.cmd上⾯第⼀个⽂件⽤于对DSP外设分配地址,⽽第⼆个⽂件是为系统的程序和数据分配地址。

当然,如果DSP的外设地址我们⽤C 语⾔已经⾃⼰定义,那第⼀个⽂件我们就可以不⽤了,笔者就是⾃⼰定义的,所以没有⽤到第⼀个⽂件。

对于为什么要⾃⼰定义外设寄存器以及中断地址,有这⼏个原因:(1) ⾃⼰定义外设寄存器地址可以很清楚的了解DSP的⼯作原理,虽然这样很耗费时间,但是会了解到DSP的中断等等是怎么⼯作的。

(2) 因为DSP外设寄存器地址的分配时采⽤寄存器形式分配到的。

举个例⼦,以sci串⼝通信为例,其他的外设以及中断都⼀样。

⽐如我们设置波特率,肯定是设置某个寄存器的相应位来实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

F2812各存储器块的地址范围

地址范围 0x000000~0x00003F 0x000040~0x0003FF 0x000400~0x0007FF 0x000800~0x000CFF 0x000D00~0x000DFF 0x000E00~0x001FFF 0x002000~0x003FFF 0x004000~0x005FFF 0x006000~0x006FFF 0x007000~0x007FFF 0x008000~0x008FFF 0x009000~0x009FFF 0x00A000~0x07FFFF 存储器块名称 M0向量RAM (VMAP [ ST1.3)] =0) [ST1.3)] M0 SRAM (1K×16) M1 SRAM (1K×16) 外设帧0 (2K×16) PIE向量 (256 W, VMAP=1; ENPIE=1) 保留空间 外扩的XINTF区0 (8K×16) 外扩的XINTF区1 (8K×16,受EALLOW保护) 外设帧1 (4K×16,受EALLOW保护) 外设帧2 (4K×16,受EALLOW保护) L0 SRAM(4K×16,受CSM保护) L1 SRAM(4K×16,受CSM保护) 保留空间

பைடு நூலகம்

. 外部存储器与扩展接口 §3-2 3-2.

� 对于较复杂的 DSP 应用系统,程序可能较长或需要扩展一些外部存储 器或外部接口如 D/A 转换芯片、 LCD驱动等,这时需要采用外部接口 (XINTF)。 � 外部存储器或接口访问速度等可能差别较大, XINTF提供了时序延长 或加等待机制来确保通过软件配置实现对这些存储器或外设的正确接 口。

. 外部存储器与扩展接口 §3-2 3-2.

,即系统由一个 F2810 DSP 芯片 � 典型的 DSP应用系统多采用 最小系统 最小系统,即系统由一个 加上相应的电源、时钟、复位、 JTAG电路及应用电路构成,这种系 单片系统方案 (Single Chip Solution)。 统也称为 统也称为单片系统方案 单片系统方案( � 在程序调试过程中,可以先将程序放入到 H0 SARAM、L0 SRAM和 仿 时比较方便。仿 L1 SARAM中运行仿真调试,对于程序长度 小于 16K时比较方便。 真调试后再通过修改链接命令文件 (. cmd )等方法,将程序烧进 Flash 中 (.cmd cmd) 运行。 � 如果程序长度大于 16K时,片内的 SARAM的空间用于仿真就不够用 了,需要扩展外部的 RAM 。当然对于编程的高手而言,也可以不经 过仿真阶段,直接将长度超过 16K的程序代码烧进 Flash 中去进行运行 调试。

� XINTF对不同的地址区域进行访问时,可以通过对应 各区的XTIMING寄存器 对访问时序加等待状态进行延 寄存器对访问时序加等待状态进行延 时,等待状态可配置为若干个XTIMCLK 的周期数。

XINTF的寄存器

§3-3. 代码安全模块CSM

1. 代码安全模块的功能

代码安全模块 CSM (Code Security Module) 可以防止未被授权的 人看到片内存储器的内容,防止对受保护的代码进行复制和反向工程。 一般情况下,在开发阶段不需要代码安全保护,只有当软件开发 完毕后,在把代码烧写到 Flash 存储器时需要进行代码保护。

TMS320LF2407 存存储储器器空空间间配配置置

� 通常在系统开发过程中,如果程序长度小于16K时, 仿真时可将程序导入到H0 SARAM和 L0 SARAM、 L1 SARAM中运行,仿真调试后再通过修改链接命 cmd )等方法,将程序烧进Flash中运行。 令文件(. (.cmd cmd) � 如果程序长度大于16K时,片内的SARAM的空间用 于仿真就不够用了,需要扩展外部的RAM。当然对 于编程的高手而言,也可以不经过仿真阶段,直接 将长度超过16K的程序代码烧进Flash中去进行运行 调试。

第三章 存储器 本章内容:

3.1 3.2 3.3 3.4 片内程序/数据存储器 外部存储器与扩展接口 代码安全模块CSM DSP引导模式

第三章 存储器

� 281xDSP采用增强的哈弗总线结构,能够并行访问程序 存储空间和数据存储空间; 统一寻址; � 采用数据存储空间, 程序存储空间, I/O空间 空间统一寻址; 通常把数据存储空间映射到低64K, 程序存储空间映射到高64K; � 281xDSP 采用32位数据地址和22位程序地址,具有最大 寻址空间:4G的数据空间(每字16位)和4M的程序空 间; � 提供外部并行扩展接口

2812 DSP 的的存存储储器器映映射射

不扩展外部存储器的映像图

2812 DSP 的存储器映射 2810 DSP 的存储器映射

. 片内程序/数据存储器 §3-1 3-1.

1. 2812 片内程序/数据存储器 (RAM) 数据存储器(

� 两块单周期快速访问的存储器( SARAM ) : • M0: (00 0000-00 03FFH) , 1KW×16

(M0模块与C240x 器件的B0、B1、B2 RAM 模块地址重叠)

• M1:(00 0400-00 07FFH) , 1KW×16 (复位时,堆栈指针指向 M1的起始位置,即 000400H ) • M0、M1 同时映射到程序空间和数据空间 � 一块单周期访问的存储器 (SARAM),长度为 16KW,分为三块: • L0: (00 8000-00 8FFFH) , 4KW ×16 • L1: (00 9000-00 9FFFH) , 4KW×16 • H0: (3F 8000-3F BFFFH), 8KW ×16 • 每个模块都可以映射到程序空间和数据空间

2812 DSP 外部 接口分区 XINTF

DSP存储器扩展 CY7C1024V33: 256K×16 位 仿真调试程序 (译码电路)

对访问时序进行配置依赖于F2812的工作频率 SYSCLKOUT和XINTF的定时时钟XTIMCLK。

时钟XTIMCLK 和SYSCLKOUT的关系示意图

� XINTF对外访问时序被分成三个阶段,即: • 起始(Lead)阶段 • • 激活(Active)阶段 收尾(Trail)阶段

• 281x 与 24x 的兼容性 ”的存储器地址范围映 � 不论是2812还是2810,“低64K 64K” ”的存储器地址范围映 射到24x的数据空间;“高64K 64K” 射到24x的程序空间。 � 24x兼容的代码只能在“高64K ”存储器中执行,因此 64K” 只有最顶部的32K(0x3F 0000~0x3F 7FFF)的 Flash/ROM和H0 SARAM可以用来运行24x兼容的代 码。

2. 2812 片内程序/数据存储器 (Flash和OTP) 数据存储器(

� Flash : (3D 8000-3F 7FFFH), 128KW, 分为4个8KW模块和6个16KW模块: • 用户可以对各自模块单独擦除、编程和验证 • 可以映射到程序空间,存放执行的程序,也映射到数据空间,存放数据 信息。 • 代码安全保护 • 注意:不同型号的芯片, 片内Flash 的配置不同,例如: 2812 —— 128KW:3D 8000 - 3F 7FFFH 2810 —— 64KW:3E 8000 - 3F 7FFFH � Boot ROM存储器: (3F F000-3F FFFFH), 4KW • 掩模型存储器,在芯片出厂时固化了Boot Loader 引导程序 � 片内外设寄存器:PF0, ( 00 0800-00 0CFFH) , 2KW PIE Vector-RAM: (00 0D00-00 0DFFH ),256W � 中断矢量: � 片内外设寄存器: PF1/2, ( 00 6000-00 7FFFH) ,8KW

程序数据空间

正弦/余弦; 641 x 32(Q30) 规格化翻转; 264 x 32(Q29) 规格化平方根;145 x32(Q30) 规格化ACTAN; 218 x32(Q30) 圆整和饱和度. 180 x 32(Q30) 保留 引导装载功能,ROM版本… 复位向量表; 2 x 16 初始化向量; 62 x 16

F2812各存储器块的地址范围

地址范围 0x080000~0x0FFFFF 0x100000~0x17FFFF 0x180000~0x3D77FF 0x3D7800~0x3D7BFF 0x3D7C00~0x3D7FFF 0x3D8000~0x3F7FF7 0x3F7FF8~0x3F7FFF 0x3F8000~0x3F9FFF 0x3FA000~0x3FEFFF 0x3FF000~0x3FFFBF 0x3FFFC0~0x3FFFFF 0x3FC000~0x3FFFBF 0x3FFFC0~0x3FFFFF 存储器块名称 外扩的XINTF区2 (0.5M×16) 外扩的XINTF区6 (0.5M×16) 保留空间 OTP模块 (1K×16 ,受CSM保护) 保留空间 Flash (128K×16 ,受CSM保护) 128 为密钥 H0 SRAM (8K×16) 保留空间 Boot ROM (4K×16, MP/MC = 0) BROM向量(VMAP=1; MP/MC = 0 ;ENPIE=0 ) 外扩的XINTF区7 (16K×16, MP/MC = 1 ) XINTF向量(VMAP=1; MP/MC = 1 ;ENPIE=0 )

2. 2812 片内程序/数据存储器 (Flash和OTP) 数据存储器(

� Flash 存储器的特点

多个分区。 有代码安全保护。 有低功耗模式。 可根据 CPU 频率调整的等待状态。 可提高性能的流水线模式。 。 � Flash 和OTP的性能 的性能。 16位或 32 位数据空间读操作。 16 位程序空间读操作。 Flash 存储器随机存取。 Flash 存储器页面存取。 OTP操作。

TMS320F2812片内ROM MAP

段地址

0x3F F000 – 0x3F F501 0x3F F502 – 0x3F F711 0x3F F712 – 0x3F F833 0x3F F834 – 0x3F F9E7 0x3F F9E8 – 0x3F FB4F 0x3F FB50 – 0x3F FBFF 0x3F FC00 – 0x3F FFBF 0x3F FFC0 – 0x3F FFC1 0x3F FFC2 – 0x3F FFFF