dsp第三章存储器详解

dsp第三章存储器

WE

--- 外部读信号线

--- 外部写信号线

3.片选信号线:

访问外部器件时,利用信号线来区分: 内部/外部访问 程序/数据空间 局部/全局数据空间 I/O空间

• DS --数据存储器选择信号:当执行访问外部(局部/全局)数据存储器指 令时,该引脚信号低电平有效。 • BR --总线请求信号:当执行访问外部全局数据存储器指令时,该引脚信 号低电平有效。 • P S --程序存储器选择信号:当从外部程序存储器全取指令代码时,该引 脚信号低电平有效。 •

2.程序存储器的配置

3)PON位(SCSR2-D0)

PON = 1 : SARAM被映射到片内程序空间 (8000~87FFh); PON = 0 : SARAM不被映射到片内程序空间。 (SARAM可能被映射到片内数据空 间)

§ 3.3 局部数据存储器

1.C2000器件片内都有3个DARAM块:B0、B1、B2。 B0块有256个字,可配置为数据存储器或程序存储器。

数据写地址总线(DWAB)。

• 3组总线的操作是独立的,因此可以同时访问程序空间和 数据空间,即在一个给定的机器周期里,中央算术逻辑单 元(CALU)可执行3种存储器操作。

§ 3.1 存储器的类型

TMS320C2000器件的片内存储器有4种类型:

(1)片内双访问存储器(DARAM) (2)片内单访问程序/数据存储器(SARAM) (3)掩模型片内ROM存储器 (4)闪速存储器(Flash)

(1)用两组RAM(32K × 16), 一组作为局部数据存储器, 一组作为全局数据存储器 (每组可由两块32K×8的RAM 组成), 地址均为8000h—FFFFh。

2)与外部数据存储器的接口

(2)用GREG作为控制切换信号: 当GREG = xx00h时, 8000h—FFFFh 地址区域被配置为 局部数据存储器, RAM2禁止, RAM1 两个使能信号或门打开,选 中RAM1。 指令举例: LDP SPLK LDP SACL #0 #0000h, GREG #100h 0000h ;ACCL ->8000h

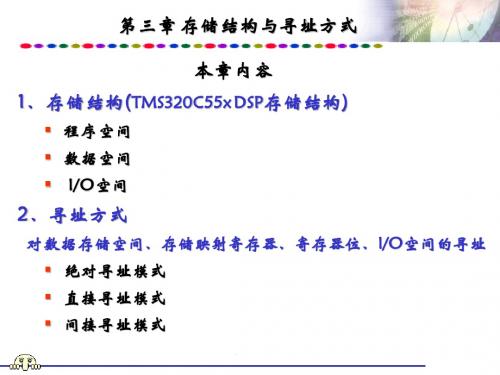

第三章 存储与寻址方式

第三章 存储结构与寻址方式

(1) 指令组织方式 变长指令存放在32 变长指令存放在32比特宽的存储 32比特宽的存储 器中。 器中。指令的地址根据操作码的 最高有效字节的地址确定。例如 最高有效字节的地址确定。 指令A的地址是000101h 指令A的地址是000101h。 000101h。

地址 000100h~000103h 000104h~000107h B(15~8) 00010Ch~00010Fh E(15~8) 字节0 字节0 字节1 字节1 字节2 字节2 字节3 字节3

字地址 000100h~000101h 字0 MSW 字1 LSW

(2) 若MSW的地址是奇地址,则LSW从MSW的前一个地址存取。 的地址是奇地址, 的前一个地址存取。

000102h~000103h LSW MSW

可通过将MSW的最低有效位(LSB)取反来确定LSW地址。 的最低有效位(LSB)取反来确定LSW地址。 (LSB)取反来确定LSW地址

A(23~16) A(15~8) A(7~0) B(7~0) C(31~24) C(23~16) D(7~0) E (23~16)

000108h~00010Bh C(15~8) C(7~0) E(7~0)

第三章 存储结构与寻址方式

(2) 边界对齐关系 在程序空间中存放指令时不用边界对齐,当读取指令时,需按32 在程序空间中存放指令时不用边界对齐,当读取指令时,需按32 比特边界的偶地址对齐(根据前面指令缓冲单元I 的介绍, 比特边界的偶地址对齐(根据前面指令缓冲单元I 的介绍,指令缓冲队列

第三章 存储结构与寻址方式

2、程序空间的指令结构

C55X DSP支持变长指令,其长度可以是8、16、24、 32、 40、 DSP支持变长指令 其长度可以是8 16、24、 32、 40、 支持变长指令,

ch3 F28027的存储空间

扇区B(8K×16位)

扇区A(8K×16位)

当使用CSM模块该区域必须编程为 0x0000

引导至Flash的入口地址 128位的安全密码区

外设帧

外设帧是TMS320F28027的CPU定时器、Flash、中断向量、片内外设( 例 如 SCI 、 SPI 、 ADC 、 ePWM 、 eCAP 及 比 较 ) 等 寄 存 器 的 映 像 空 间 , TMS320F28027的外设帧包含3个外设空间,外设空间分类如下:

Flash & OTP 相关寄存器 FOTPWAIT OTP等待寄存器

3.4 程序的引导装载

上电或复位 芯片设置如下: PIE禁止(ENPIE=0)

VMAP=1 OBJMODE=0

AMODE=0 M0M1MAP=1

Boot ROM

从引导ROM地址0x3F FFC0处读取复位向量

跳转到InitBoot函数 启动引导流程

表3-10 引导模式选择

模式 GPIO37/TDO GPIO34/COMP2OUT

引导装载模式

3

1

2

1

1

0

0

0

EMU

x

1

0

模式获取

0

0

wait

1

0

SCI

0

0

并行I/O

x

1

仿真

1.仿真引导 2.独立引导

表3-14 独立引导模式

GPIO37 GPIO3 OTP KEY OTP BMODE

TDO

4

读0x3D 7BFE 读0x3D 7BFF

对PWL读取判断: 1.All zero: permanently secured

DSP 存储器和IO空间

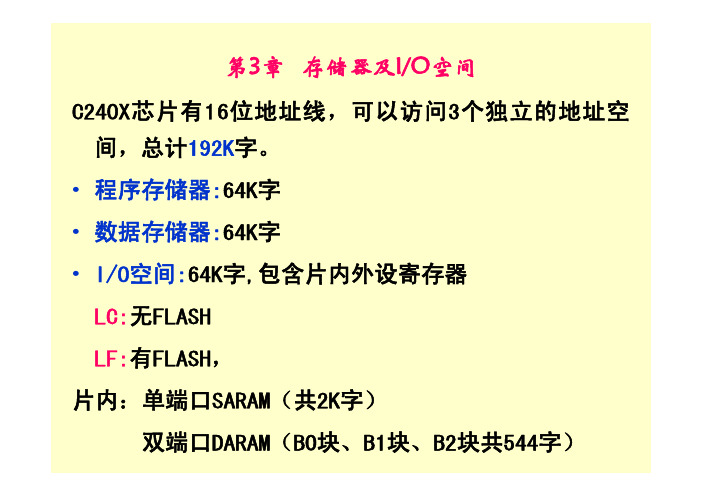

第3章存储器及I/O空间C240X芯片有16位地址线,可以访问3个独立的地址空间,总计192K字。

•程序存储器:64K字•数据存储器:64K字•I/O空间:64K字,包含片内外设寄存器LC:无FLASHLF:有FLASH,片内:单端口SARAM(共2K字)双端口DARAM(B0块、B1块、B2块共544字)改进的哈佛结构,通过3组并行地址总线访问3个空间。

(1)程序地址总线(PAB)(2)数据读地址总线(DRAB)(3)数据写地址总线(DWAB)可同时访问程序和数据空间,一个周期内,CALU可执行多达3次的并行存储器操作。

TMSC206:片内32K Falsh,B0-256个;B1-256个;B2-32个SARAM 4K字TMSC240:片内16K Falsh,B0-256个;B1-256个;B2-32个TMSLF2407A(片内):32K字Falsh,DARAM(双口RAM)为544个字:B0-256个;B1-256个;B2-32个。

SARAM(单口RAM)2K字。

3.1 片内存储器3.1.1 双端口RAM(DARAM)544个字,分为三块:B0、B1、B2。

B0作程序存储器还是作数据存储器,由寄存器ST1的D12位CNF 来决定:CNF=1,B0映射到程序存储器空间CNF=0,B0映射到数据存储器空间DARAM:双访问随机读/写存储器,在单个机器周期内可被访问2次:CPU在时钟的主相写入DARAM;在时钟的从相从DARAM读出数据;大大的提高了运行速度。

3.1.2 单端口RAM(SARAM)2K字单访问随机读/写存储器,在单个机器周期内可被访问1次。

例如,一条指令要将A的值保存,且装载一个新值到A 在SARAM中需两个时钟周期,而在DARAM中需一个时钟周期,3.1.3 FLASH程序存储器LF2407:16K字,映射到程序存储空间。

有片内程序存储器和片外程序存储器之分。

MP/MC*=0,选择片内Falsh存储器MP/MC*=1,选择片外程序存储器,从片外程序存储器开始执行程序。

DSP精品课件

第三章 5402存储器配置

目的:通过对5402的存储器配置与管理 的学习,掌握TMS320系列存储器配置与 管理的特点

DSP芯片的应用

本章主要内容

3-1 3-2 3-3 3-4 3-5 3-6 5402内部存储器配置 5402存储空间 5402存储器空间构成与管理(本章难点) 外部程序存储空间扩展 5402片内ROM组成 5402片内DARAM组成

XPC 为扩展程序指针寄存器,地址为 001EH。XPC 影响 ( A16---A19),为页指针, PC 影响( A15---A0)为页内 指针。复位时,XPC=0000H指向零页,复位后可用软件 修改XPC。 仅有8条指令可以直接影响XPC,直接访问1M程序空间, 分别说明如下:

DSP芯片的应用

DSP芯片的应用

3-1 5402内部存储器配置

5402内部配有: ROM: 4k×16bit

F000H

DARAM:16k×16bit 0000H

FFFFH

3FFFH

DSP芯片的应用

3-2 5402存储空间(包括内部和外部可扩展的) 5402有三个独立的存储空间:程序存储空间、数 据存储空间和I/O存储空间 1、程序存储空间,1M×16bit 00000H

DSP芯片的应用

作用:外部设备接口空间 受数据地址发生器DAGEN管理 受如下引脚控制(地址线、数据线除外) IS:I/O空间选择信号 IOSTRB:I/O空间选通信号 R/W:读写信号 此外,还受 READY:外设数据准备好与慢 速 I/O 设备匹配; BIO:跳转控制输入; XF: CPU输出引线等握手控制。

块重复开始地址

块重复结束地址 状态寄存器 PC扩展寄存器 保留

DSP存储单元DSP存储器的基本结构

在对I/O空间访问时,除了使用数据总线和地址 总线外,还要用到IOTRB、IS和I/W控制线。

IOTRB和IS :用于选通I/O空间; I/W:用于控制访问方向。

通用I/O引脚

’C54x芯片为用户提供了两个通用的I/O引脚。 BIO:用来监控外部设备的运行状态。 在实时控制系统中,通过查询此引脚控制 程序流向,以避免中断引起的失控现象。 XF:用于程序向外设传输标志信息。 通过此引脚的置位或复位,可以控制外设 的工作。

DROM控制的 数据存储空间

程序存储空间

程序存储空间用来存放要执行的指令和执行中所需的 系数表。

’C5402共有20条地址线,可寻址1M字的外部程序存 储器。它的内部ROM和DARAM可通过软件映射到程序空 间。当存储单元映射到程序空间时,CPU可自动地按程序 存储器对它们进行寻址。

如果程序地址生成器(PAGEN)产生的地址处于外部 存储器,CPU可自动地对外部存储器寻址。

1.程序存储空间的配置 ● MP/MC控制位用来决定程序存储空间是否使用内部

存储器。 当MP/ MC=0时,称为微计算机模式。

4000H~EFFFH程序存储空间定义为外部存储器; F000H~FEFFH程序存储空间定义为内部ROM; FF00H~FFFFH程序存储空间定义为内部存储器。

当MP/ MC=1时,称为微处理器模式。 4000H~FFFFH程序存储空间定义为外部存储器 。

2D~2FH

保留

30H TRCV TDM串行口数据接收寄存器

31H TDXR TDM串行口数据发送寄存器

32H TSPC TDM串行口控制寄存器

DSP原理与应用---第3章 EMIF

DRAM是Dynamic RAM的缩写,中文含义为动态随机存取存储器, 需要不断的刷新,才能保存数据。而且是行列地址复用的,许多都有 页模式。SDRAM:Synchronous DRAM,即数据的读写需要时钟 来同步。 一个是静态的,一个是动态的,静态的是用的双稳态触发器来保存信 息,而动态的是用电子,要不时的刷新来保持。

DRAM容量大,SRAM容量小

SDRAM的结构

FLASH ROM

Flash-ROM(闪存)已经成为了目前最成功、流行的一种固态内存,与 EEPROM 相比具有读写速度快,而与 SRAM 相比具有非易失、以及价廉等优 势。而基于 NOR 和 NAND 结构的闪存是现在市场上两种主要的非易失闪存技 术。 Intel 于 1988 年首先开发出 NOR flash 技术,彻底改变了原先由 EPROM 和 EEPROM 一统天下的局面。紧接着,1989 年东芝公司发表了 NAND flash 技术(后将该技术无偿转让给韩国 Samsung 公司),强调降低每比特的成 本,更高的性能,并且象磁盘一样可以通过接口轻松升级。 NOR 的特点是芯片内执行(XIP,eXecute In Place),这样应用程序可以直 接在闪存内运行,不必再把代码读到系统 RAM 中。NOR 的传输效率很高,在 1~4MB 的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影 响了它的性能。 NAND 结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的 速度也很快,这也是为何所有的 U 盘都使用 NAND 闪存做为存储介质的原因。 应用 NAND 的困难在于需要特殊的系统接口。

NAND flash和NOR flash的对比

接口差别 NOR 闪存带有SRAM接口,有足够的地址引脚来寻址,可 以很容易地存取其内部的每一个字节。 NAND闪存使用复杂的I/O口来串行地存取资料,各个产品 或厂商的方法可能各不相同。8个引脚用来传送控制、地 址和资料信息。NAND读和写操作采用512字节的块,这 一点有点像硬盘管理此类操作,很自然地,基于NAND的 闪存就可以取代硬盘或其它块设备。

dsp 第三章2

’C54x存储器操作的各种情况: ③ 执行写单操作数指令 例如:STH

预取指P 加载 PAB 取指F

A,*AR1

译码D 寻址A

;单周期指令, 写单操作数 读数R 执行/写数

通过PB 通过IR 读取指令 指令译码

写地址 数据 加载EAB 写至EB

8

第3章 TMS320C54x的硬件结构

’C54x存储器操作的各种情况: ④ 执行写双操作数指令 例如:DST

i5或NOP a5

i5

X R i5的条件执行 PAB=a5 PB=i5 PB=i5 ;任意单周期,单字指令

T6:XC指令寻址级,求解XC指令的条件。 T4:对XC指令进行取值; T3:XC指令地址a3加载PAB; 注意:① 决定XC指令判断条件的指令应放在i1指令之前; 如果XC指令的判断条件由指令i1和i2的结果给出,则 在T6周期,i1和i2指令还没执行完毕,执行结果不会 若条件满足,则i4和i5指令进入译码级并执行; 会得出错误的判断。 对XC指令的条件判断产生影响。 ② 在条件执行指令前屏蔽所有可能产生的中断或 若不满足,则不对i4和i5指令译码,执行NOP。 其他改变指令规定条件的运算。

1

第3章 TMS320C54x的硬件结构

3.7.2 流水线操作 1. 流水线操作的概念

’C54x的流水线操作是由6个操作阶段或操作周

期组成。在任何一个机器周期内,可以有1 ~ 6条不

同的指令在同时工作,每条指令可在不同的周期内

工作在不同的操作阶段。

2

第3章 TMS320C54x的硬件结构

1. 流水线操作的概念 六个操作阶段: ① 预取指P; ③ 译码D; ⑤ 读数R; 流水线结构:

T1 a1,a2 P T2 T4 T5 T6 T7 T8 T9 T10 BF b1 T3 ;四机器周期,两字的无延迟分支转移指令 D A R X

DSP存储器及扩展接口详解

提示:初始化Flash寄存器的代码必须从RAM中运行,从 Flash中执行将导致不可预测的结果。

11

外设寄存器空间

F281X和C281X器件包含三个外设寄存器空间。这些空间分 为以下三组:

1) Peripheral Frame0: 直接映射到CPU的存储器总线,支持 16位和32位数据访问。 2) Peripheral Frame1: 映射到32位的外设总线,必须采用32 位读写方式(限对偶地址访问)。 3) Peripheral Frame2: 映射到16位的外设总线,仅支持16为 访问。

16

/* Peripheral Frame 2: SYSTEM : origin XINTRUPT : origin GPIOMUX : origin GPIODAT : origin EV_A : origin EV_B : origin MCBSP_A : origin SCI_A : origin SCI_B : origin SPI_A : origin ADC : origin

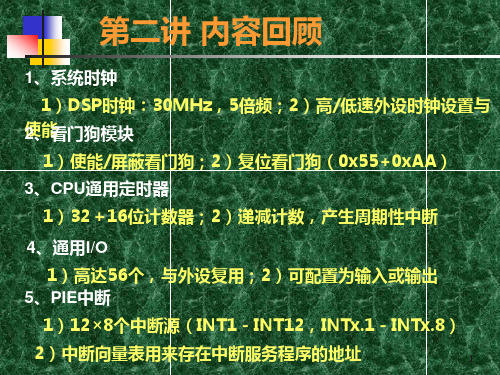

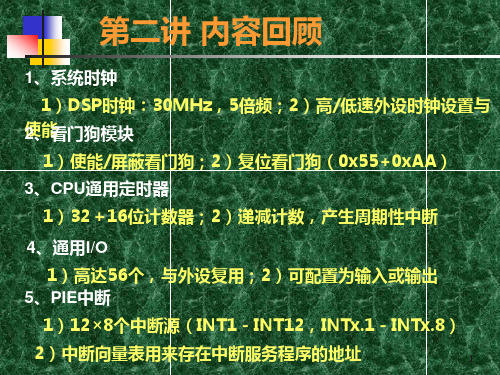

第二讲 内容回顾

1、系统时钟 1)DSP时钟:30MHz,5倍频;2)高/低速外设时钟设置与使能 2、看门狗模块 1)使能/屏蔽看门狗;2)复位看门狗(0x55+0xAA) 3、CPU通用定时器 1)32+16位计数器;2)递减计数,产生周期性中断 4、通用I/O 1)高达56个,与外设复用;2)可配置为输入或输出 5、PIE中断

EPROM FLASH EEPROM DiskOnChip

数据存储器:

SRAM

DRAM EEPROM Dual Port RAM

PC/104兼容的Flash Disk模块

3

F281X的存储器

DSP原理及应用第三章

15~8 7 6~0

操作码

I=0

dmad

堆栈指针SP

16位堆栈指针SP

SP+dmad

16位数据 存储器地址 16位SP+dmad 高 9位

dmad

低 7位

15

DP地址的范围是从0~511(29-1),将存储器分成 512页。 7 位 dmad 范围是从 0~127 ,每页有 128 个可以访 问的单元。 以DP为基准的直接寻址是由DP 值确定是 512 页中 的哪一页,由dmad确定是该页中的哪一个单元。 SP 可以指向存储器中的任意一个地址。 dmad 可 以指向当前页中具体的单元,从而允许访问存储器 任意基地址中的连续的128个单元

循环寻址的有效地址计算

循环缓冲区的参数主要包括:长度寄存器 (BK)、有效基地址(EFB)、尾地址(EOB)。 N>32, 则N=6。 例如:缓冲区长度 R=32 , 若 2 BK:定义了循环缓冲区的大小R。大小为R的循环缓冲 缓冲区开始的地址: xxxx xxxx xx00 0000 B 器其地址要始于最低 N位为零的地址。并且 R要满足下 缓冲区长度 N>R 装入循环缓冲长度寄存器BK中。 面的条件: 2R=32 EFB:循环缓冲器的有效基地址(EFB)就是用户选定 的辅助寄存器(ARx)的低N位置 0后所得到的值。 EOB:是通过用BK的低N位代替ARx的低N位得到。

LD

*(BUFFER),A

9

绝对寻址总结

16位地址表示形式: ① 地址符号,如:TABLE; ② 16位数值,如:89AB、1234。 特点:指令中包含一个固定的16位地址,能寻 址所有数据、程序和I/O存储空间,但 运行速度慢,需要较大的存储空间。 用途:用于对速度要求较低的场合。

第三章 TI TMS320C2000系列DSP存储器及输入输出空间(“存储器”相关文档)共7张

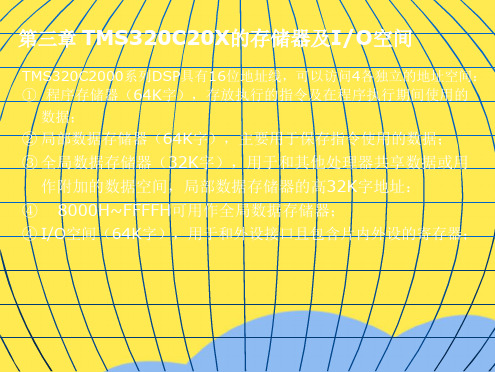

第三章 TMS320C20X的存储器及I/O空间

TMS320C2000系列DSP具有16位地址线,可以访问4各独立的地址空间: ① 程序存储器(64K字),存放执行的指令及在程序执行期间使用的

数据;

② 局部数据存储器(64K字),主要用于保存指令使用的数据; ③ 全局数据存储器(32K字),用于和其他处理器共享数据或用

片内16K flash(1) C全N局F数=1据,存片储内器B0(块3D2KA字RA)M,用于和其他处理器共享数据或用作附加的数据空间,局部数据存储器的高32K字地址: CNF=01保,留片,内CB0N块F=D1A片RA外M 8片0内001H6~KFfFlaFsFhH(0可) M用P作/M全C局=0数据存储器; PON=0,片外4K ROM 800040H~F3FFFhH可用作全局数据存储器; C片N内F=41K,S片AR内ABM0(块PDOANR=A1M) 片CN内F1=61K,片fla内shB(0块1)DARAM CNF=01保,留片,内CB0N块F=D1A片RA外M TMS320F206程序存储器空间映像 CNF=0保留,CNF=1 片外 I8/0O0空0H间~(FF6F4FKH字可)用,作用全于局和数外据设存接储口器且;包含片内外设的寄存器; CNF=0保留,CNF=1 片外 片内16K flash(1) CNF=01保,留片,内CB0N块F=D1A片RA外M

900H~FDFFH FE00H~FEFFH FF00H~FFFFH

片内16K flash(0) MP/MC=0 片内16K flash(1) MP/MC=0 片内 4K SARAM(PON=1) PON=0,片外4K ROM 片外ROM CNF=0保留,CNF=1 片外 CNF=1,片内B0块DARAM CNF=0,片外ROM

DSP-03CPU与存储器

DWEB(16) DRDB(16) PRDB(16)

16 16 16 16 16 16 16 16

数据读总线

程序读总线

MVX:多路转换器

MVX

临时寄存器

TRGE 乘法器

MVX

移位器(32位) 输入定 标器部 分

32

16X16 PREG

乘法器 部分 乘法寄存器

将16位输入与32位的 CALU的数据对齐

7080~708F

SARAM 非法空间

2K

数字I/O控制寄存器

7090~709F

片内外设专用寄存器 2

64字

捕获和QEP寄存器

中断屏蔽 向量 标志寄存器

30K

ADC控制寄存器 非法 CAN控制寄存器 非法

70A0~70BF

7000 7FFF

非法

I/O功能寄存器 及保留空间

40K

非法

片内外设专用寄存器 3

分支转移指令: 由内部硬件把指令中的跳转地址 (立即寻址或累加 器低16位) 子程序调用: PC

入口地址送PC 同时下一条断点地址送堆栈 堆栈为8级硬件中断

第三章 总线、CPU结构及存贮的配置

外部地址总线 PAB DRAB DWAB PRDB DRDB DWEB

外部数据总线

总线结构: PAB: 程序地址总线,程序空间地址 CPU DRAB:程序读总线, 程序存储器内容 CPU DWAB:数据写地址总线, 写数据空间时的地址

PRDB: 程序读数据总线, 读数据空间时的地址 DRDB:数据读总线, 数据存储器内容 CPU DWEB:数据写总线, 数据 数据存储器或程序存储器

主要功能是与中央处理单元并行工作,对8个辅助寄存器(AR0-AR7) 进行算术运算 8个辅助寄存器为DSP提供间接寻址方式,由状态寄存器的ARP(STO)

DSP存储器及扩展接口详解

片内集成了大量的SRAM、ROM、FLASH等存储器, 采用统一编址方式,方便程序开发。

F2812提供了外部并行总线扩展接口,可提供1M字 (三个外部扩展空间:两个512K,一个16K)的寻址空间, 有利于开发较复杂的系统,如扩展FLASH、RAM、 ADC、DAC、RTC、LCD、USB、LAN等。

外设速度特别慢,依靠软件插入等待状态无法满足要求; 一个XINTF区(ZONE)的外设较多,速度快慢差异较大。

讨论:通过软件可以设置的读写周期范围为: 2~54个SYSCLKOUT 。如 果 SYSCLKOUT=150MHz时,对应75MHz~2.78MHz。如果一个外设芯片 的读写周期为500μs,是否需要使用XREADY信号?

12

外设寄存器帧0

16/32

/* Peripheral Frame 0: */ F2812.cmd DEV_EMU : origin = 0x000880, length = 0x000180 XINTF : origin = 0x000B20, length = 0x000020 PIE_CTRL : origin = 0x000CE0, length = 0x000020 PIE_VECT : origin = 0x000D00, length = 0x000100 FLASH_REGS : origin = 0x000A80, length = 0x000060 CSM : origin = 0x000AE0, length = 0x000010 CPU_TIMER0 : origin = 0x000C00, length = 0x000008 CPU_TIMER1 : origin = 0x000C08, length = 0x000008 CPU_TIMER2 : origin = 0x000C10, length = 0x000008

关于DSP的存储空间

关于DSP的存储空间

我对TMS320VC54XX系列的存储空间是这样理解的,

该系列内部均有一定数量的高速物理存储空间,注意,是物理的,也就是说是实实在在存在的。

与”映像“不一样。

我们平时都是把程序和数据存放在内部物理存储区,

我们对片内物理存储器的访问,使通过访问映射存储器来实现的,也就是说,片内物理存储器必须被映射到映射存储器上才能被访问。

DSP系统的映射存储器分为三块:程序区,数据区和IO区。

一般来说,IO区是片外资源,访问空间大小为64K*16bit。

注意,程序区是可以扩展访问的,它分为基本程序区和扩展程序区。

基本程序区都一样,但是由DSP的不同,最大扩展空间也不同。

所以说,DSP系统的映射存储器其实是代表了DSP芯片的一种寻址能力和可访问空间的大小。

我们应该注意,在没有对映射存储器配置前,这些映射存储器空间都是虚拟的,(可以看成是虚拟的),不能用来存储程序和数据。

这就引出了DSP的编译和汇编。

在DSP的编译和汇编之后,连接成目标文件之前,必须加入存储器配置文件,这是为了:将实际的物理存储区空映射到映射存储器空间上。

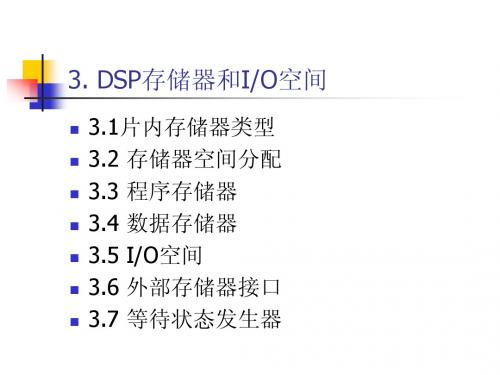

第三章DSP存储器和IO空间

00 01 00、01:总线可视模式关闭 10:数据空间数据和地址总线输出 11:程序空间数据和地址总线输出

3.3 程序存储器

用来存放程序代码 立即数 表

3.3 程序存储器

程序存储器的配置

CNF

CNF=0,B0被映射为数据存储空间 CNF=1,B0被映射为程序存储空间

MP/MC引脚

MP/MC=0,微控制器方式,片内ROM/FLASH可 被访问 MP/MC=1,为微处理器方式,从外部程序存储 器读取复位矢量

3.4 数据存储器

第0页数据页

第0页数据存储器中包括存储器映射寄存器

可以零等待状态访问的映射寄存器:中断屏蔽寄 存器(IMR)和中断标志寄存器(IFR)

测试/仿真保留区被测试和仿真系统用于特 定信息的传输 32个字的B2块

3.4 数据存储器

数据存储器的配置

CNF=0,B0->数据空间 CNF=1,B0->程序空间

SARAM:

在一个周期内只能访问一次。 可用于数据存储器或程序存储器。 PON、DON。

3.1片内存储器类型

FLASH:

电可擦除、可编程、可长期保存信息。

ROM:

工厂可编程的掩模的ROM

BOOT ROM

256W,位于程序空间的0~FFH 复位时引脚BOOT_EN

3.2 存储器空间分配

程序空间 数据空间 I/O空间

3.5 I/O空间

3.6 外部存储器接口

3.7 产生等待状态

两种方式:

READY 等待状态发生器

READY方式

当READY为低,2407A等待一个CLKOUT 周期,并再检测READY,直到READY为 高。 READY可产生任意数量的等待周期。 READY不使用必须拉高。

DSP 存储器

程序数据空间

正弦/余弦; 641 x 32(Q30) 规格化翻转; 264 x 32(Q29) 规格化平方根;145 x32(Q30) 规格化ACTAN; 218 x32(Q30) 圆整和饱和度. 180 x 32(Q30) 保留 引导装载功能,ROM版本… 复位向量表; 2 x 16 初始化向量; 62 x 16

2812 DSP 外部 接口分区 XINTF

DSP存储器扩展 CY7C1024V33: 256K×16 位 仿真调试程序 (译码电路)

对访问时序进行配置依赖于F2812的工作频率 SYSCLKOUT和XINTF的定时时钟XTIMCLK。

时钟XTIMCLK 和SYSCLKOUT的关系示意图

� XINTF对外访问时序被分成三个阶段,即: • 起始(Lead)阶段 • • 激活(Active)阶段 收尾(Trail)阶段

. 外部存储器与扩展接口 §3-2 3-2.

,即系统由一个 F2810 DSP 芯片 � 典型的 DSP应用系统多采用 最小系统 最小系统,即系统由一个 加上相应的电源、时钟、复位、 JTAG电路及应用电路构成,这种系 单片系统方案 (Single Chip Solution)。 统也称为 统也称为单片系统方案 单片系统方案( � 在程序调试过程中,可以先将程序放入到 H0 SARAM、L0 SRAM和 仿 时比较方便。仿 L1 SARAM中运行仿真调试,对于程序长度 小于 16K时比较方便。 真调试后再通过修改链接命令文件 (. cmd )等方法,将程序烧进 Flash 中 (.cmd cmd) 运行。 � 如果程序长度大于 16K时,片内的 SARAM的空间用于仿真就不够用 了,需要扩展外部的 RAM 。当然对于编程的高手而言,也可以不经 过仿真阶段,直接将长度超过 16K的程序代码烧进 Flash 中去进行运行 调试。

DSP概述及存储器

DMA

Ch 0 Ch 1 Ch 2 Ch 3 Ch 4 Ch 5 Peripheral Bus Peripheral Bus

Timer Timer 8/16-bit Host Port 8/16-bit Host Port Interface (HPI) Interface (HPI)

Multichannel Buffered Multichannel Buffered Serial Port (McBSP) Serial Port (McBSP) Multichannel Buffered Multichannel Buffered Serial Port (McBSP) Serial Port (McBSP) Multichannel Buffered Multichannel Buffered Serial Port (McBSP) Serial Port (McBSP)

Small Size

144 TQFP 144 microStar BGA (12 x 12 mm)

Addressing Unit 8 Auxiliary Registers 2 Addressing Units Power Management Power Management

PLL Clock PLL Clock Generator Generator S/W Waitstate S/W Waitstate Generator Generator

Copyright © 2003 Texas Instruments. All rights reserved.

DSP主要特点

根据数字信号处理的要求,DSP一般具有如下的主要特点: ☆ 在一个指令周期内,可完成一次乘法和一次加法; ☆ 程序和数据空间分开,可以同时访问指令和数据; ☆ 片内具有快速RAM,通常可通过独立的数据总线, 在两块芯片中同时访问; ☆ 具有低开销或无开销循环及跳转的硬件支持; ☆ 快速的中断处理和硬件I/O接口支持; ☆ 具有在单周期内操作的多个硬件地址产生器; ☆ 可以并行执行多个操作; ☆ 支持流水线操作,使取指、译码、取操作数和执行等 操作可以重叠执行。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.数据存储器空间配置 (TMS320LF2407型号芯片) 2) DARAM(B0)

2.程序存储器的配置

1) MP/MC引脚: • MP/MC = 0(接地): 微控制器方式, 配置为片内ROM/Flash • MP/MC = 1(接高电平): 微处理器方式,

配置为片外ROM

2.程序存储器的配置

2)CNF位:

决定片内DARAM(B0)的地址映射

• CNF = 1:

256字的片内DARAM(B0)被配置到 程序存储器空间(FF00~FFFFh) • CNF = 0: 无可访问的片内程序DARAM (B0被配置到数据存储器空间) 注意: B0 无论是被配置到程序空间,还是 被配置到数据存储器空间,都是同 一物理存储器块

第三章 存储器与I/O空间

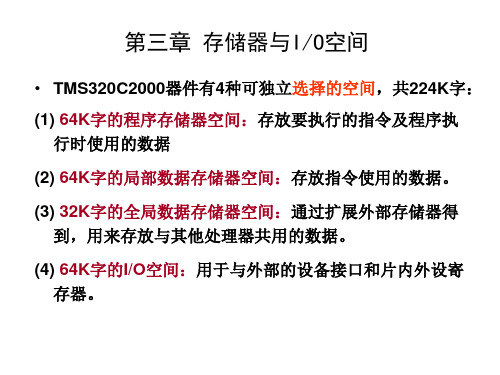

• TMS320C2000器件有4种可独立选择的空间,共224K字: (1) 64K字的程序存储器空间:存放要执行的指令及程序执 行时使用的数据 (2) 64K字的局部数据存储器空间:存放指令使用的数据。 (3) 32K字的全局数据存储器空间:通过扩展外部存储器得 到,用来存放与其他处理器共用的数据。 (4) 64K字的I/O空间:用于与外部的设备接口和片内外设寄 存器。

(4)闪速存储器(Flash):

可被配置为数据存储器,也可配置为程 序存储器。 (只对 B0块)

§ 3.1 存储器的类型

TMS320C2000器件的片内存储器有4种类型:

(1)片内双访问存储器(DARAM)

(2)片内单访问程序/数据存储器(SARAM)

(3)掩模型片内ROM存储器 SARAM:每个机器周期仅能访问一次的存 储器。

0000~003Fh: 中断向量地址

0040~0043h: 保留地址 0044~7FFFh: 片内Flash (32K字)

8000~87FFh: 片内SARAM(2K字)

8800 ~FDFFh:片外ROM FE00~FEFFh: 保留区或片外ROM FF00~FFFFh: 片内DARAM(B0) (256字)或片外ROM

(4)闪速存储器(Flash):

C2000的有些器件内含有SARAM 。

SARAM可配置为程序存储器或数据存储器。

配置为内部程序存储器SARAM时,程序代 码可以从片外ROM调入,并被全速执行。

§ 3.1 存储器的类型

由生产厂家已写好程序的存储 器,用户只能读不能写。

TMS320C2000器件的片内存储器有4种类型:

数据写地址总线(DWAB)。

• 3组总线的操作是独立的,因此可以同时访问程序空间和 数据空间,即在一个给定的机器周期里,中央算术逻辑单 元(CALU)可执行3种存储器操作。

§ 3.1 存储器的类型

TMS320C2000器件的片内存储器有4种类型:

(1)片内双访问存储器(DARAM) (2)片内单访问程序/数据存储器(SARAM) (3)掩模型片内ROM存储器 (4)闪速存储器(Flash)

§ 3.1 存储器的类型

TMS320C2000器件的片内存储器有4种类型:

(1)片内双访问存储器(DARAM)

电可擦除与编程的非易失性程序存储器。 (2)片内单访问程序/数据存储器 (SARAM) 适合系统应用开发。 (3)掩模型片内ROM存储器

(4)闪速存储器(Flash)

§ 3.2 程序存储器

2.程序存储器的配置

3)PON位(SCSR2-D0)

PON = 1 : SARAM被映射到片内程序空间 (8000~87FFh); PON = 0 : SARAM不被映射到片内程序空间。 (SARAM可能被映射到片内数据空 间)

§ 3.3 局部数据存储器

1.C2000器件片内都有3个DARAM块:B0、B1、B2。 B0块有256个字,可配置为数据存储器或程序存储器。§ 3.1 Nhomakorabea储器的类型

TMS320C2000器件的片内存储器有4种类型:

(1)片内双访问存储器(DARAM)

DARAM:单个机器周期可被访问两次 (2)片内单访问程序/数据存储器 (SARAM)

的存储器。

(3)掩模型片内ROM存储器

所有C2000器件都有片内DARAM,分 为三块:B0,B1,B2。

• 程序存储器存放应用程序的代码、表格信息和固定操作数

• TMS320C2000器件可寻址的程序存储器地址有64K字。

• C2000器件的程序存储器类型: 片内DARAM (B0块) 片内SARAM 片内ROM / Flash 片外ROM

1.程序存储器地址分配 (TMS320LF2407型号芯片)

4.数据存储器空间配置 (TMS320LF2407型号芯片)

1)数据存储器第0页地址映射

(地址0000~007Fh)

0000-0003h 0004h 0005h 0006h 0023-0027h 002B-002Fh 0060-007Fh B2 IMR 保留 中断屏蔽寄存器

GREG 全局存储器分配 寄存器 IFR 中断标志寄存器 保留 测试/仿真保留区 DARAMB2 (32字)

有些C2000器件片内有掩模型 ROM作为程序存储器。

(1)片内双访问存储器(DARAM) 如果用户需要定制掩模型片内

(2)片内单访问程序/数据存储器(SARAM)

ROM,可按目标文件格式提供 程序代码或数据,由芯片生产 厂家对ROM进行掩模。

(3)掩模型片内ROM存储器

(4)闪速存储器(Flash)

• 这224K字空间包括 片内存储器、外部存储器和I/O设备。

片内存储器操作的优点:速度快,功耗小。 外部存储器操作的优点:可以访问更大的地址空间。 • TMS320C2000器件设计以改进的哈佛结构为基础,存储 空间可由3组16位的并行总线访问,即 程序地址总线(PAB), 数据读地址总线(DRAB),

B1块有256个字,只能作为数据存储器。

B2块有32个字,只能作为数据存储器。 2.有些C2000器件还有片内SARAM块,它们可用做程序和/或数据 存储器。 3.访问数据存储器有直接寻址模式和间接寻址模式。 使用直接寻址时,将数据有储器按地址分块,每块128个字为一页。 64K数据存储器可分为512个数据页,记为0—511页。页地址由页 地址指针DP决定。