SPI总线使用入门

SPI总线

SPI总线

综述:SPI(Serial Peripheral interface):高速同步串行口。

是一种标准的四线同步

双向串行总线。

Motorola首先在其MC68HCXX系列处理器上定义的在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间。

SPI 接口主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

速率:目前应用中的数据速率可达几Mbps。

通信原理:SPI接口共有4根线:设备选择线SS、时钟线SCLK、串行输出

数据线MISO、传行输入数据线MOSI。

SPI由主机的片选信号SS以低电平选中从机,通过主机控制时钟SCLK同步传输数据。

扩展时只要增加主机的片选信号线如图2所示。

图2

下图为SPI结构图,通过移位寄存器左移输出数据,右移输入数据。

SPI的时序模式:由时钟极性选择位CPOL和时钟相位选择位控制CPHA。

CPOL用于选择空闲状态电平,CPHA选择数据接收端的采样时刻。

具体时序如图3。

图3

SPI接口必须根据具体情况设置匹配的传续时序模式,时序只有匹配,数据传输才能正常进行,如果设置的不匹配,可能导致数据接收方和发送方在同一时钟沿作用,导致数据传输失败。

I2CVSSPI。

(完整)spi总线协议详细说明

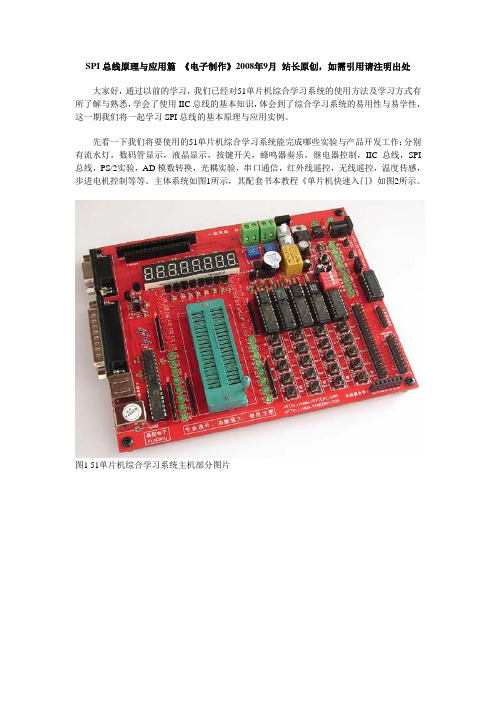

SPI总线原理与应用篇《电子制作》2008年9月站长原创,如需引用请注明出处大家好,通过以前的学习,我们已经对51单片机综合学习系统的使用方法及学习方式有所了解与熟悉,学会了使用IIC总线的基本知识,体会到了综合学习系统的易用性与易学性,这一期我们将一起学习SPI总线的基本原理与应用实例。

先看一下我们将要使用的51单片机综合学习系统能完成哪些实验与产品开发工作:分别有流水灯,数码管显示,液晶显示,按键开关,蜂鸣器奏乐,继电器控制,IIC总线,SPI 总线,PS/2实验,AD模数转换,光耦实验,串口通信,红外线遥控,无线遥控,温度传感,步进电机控制等等。

主体系统如图1所示,其配套书本教程《单片机快速入门》如图2所示。

图1 51单片机综合学习系统主机部分图片图2 51单片机综合学习系统配套书本教程——《单片机快速入门》上图是我们将要使用的51单片机综合学习系统硬件平台,如图1所示,本期实验我们用到了综合系统主机、板载的AT93C46芯片,综合系统其它功能模块原理与使用详见前几期《电子制作》杂志及后期连载教程介绍。

SPI总线简介SPI总线基本概念SPI ( Serial Peripheral Interface ———串行外设接口) 总线是Motorola公司推出的一种同步串行接口技术。

SPI总线系统是一种同步串行外设接口,允许MCU 与各种外围设备以串行方式进行通信、数据交换。

外围设备包括FLASHRAM、A/ D 转换器、网络控制器、MCU 等。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

其工作模式有两种:主模式和从模式。

SPI是一种允许一个主设备启动一个从设备的同步通讯的协议,从而完成数据的交换。

也就是SPI是一种规定好的通讯方式。

这种通信方式的优点是占用端口较少,一般4根就够基本通讯了(不算电源线)。

SPI总线的工作方式及原理详解

SPI总线的工作方式及原理详解SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于CPU与各种外围器件进行全双工、同步串行通讯。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线有四种工作方式(SP0,SP1,SP2,SP3),其中使用的最为广泛的是SPI0和SPI3方式。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设音时钟相位和极性应该一致。

SPI时序详解---SPI接口在模式0下输出第一位数据的时刻SPI接口有四种不同的数据传输时序,取决于CPOL和CPHL这两位的组合。

图1中表现了这四种时序,时序与CPOL、CPHL的关系也可以从图中看出。

图1CPOL是用来决定SCK时钟信号空闲时的电平,CPOL=0,空闲电平为低电平,CPOL=1时,空闲电平为高电平。

SPI怎么玩?搞懂时序,运用自如

SPI怎么玩?搞懂时序,运用自如1、什么是SPI?SPI是串行外设接口(Serial Peripheral Interface)的缩写,是Motorola 公司推出的一种同步串行接口技术,是一种高速、全双工、同步的通信总线。

2、SPI优点支持全双工通信通信简单数据传输速率块3、缺点没有指定的流控制,没有应答机制确认是否接收到数据,所以跟IIC总线协议比较在数据可靠性上有一定的缺陷。

4、特点(1):高速、同步、全双工、非差分、总线式(2):主从机通信模式5、SPI电路连接(1):SPI的通信原理很简单,它以主从方式工作,这种模式通常有一个主设备和一个或多个从设备,有三线制和四线制之分。

信号线包括SDI(串行数据输入Serial Digital IN)、SDO(串行数据输出 Serial Digital OUT)、SCLK(时钟)、CS(片选)。

(2):SDO/MOSI –主设备数据输出,从设备数据输入(3):SDI/MISO –主设备数据输入,从设备数据输出(4):SCLK –时钟信号,由主设备产生; (5):CS/SS –从设备使能信号,由主设备控制。

当有多个从设备的时候,因为每个从设备上都有一个片选引脚接入到主设备机中,当主设备和某个从设备通信时将需要将从设备对应的片选引脚电平拉低(一般低有效)。

6、SPI通信模式分析SPI通信有4种不同的模式,不同的从设备在出厂时配置模式已经固定,这是不能改变的,但通信双方设备必须工作在同一模式下,所以可以对主设备的SPI模式进行配置,通过CPOL(时钟极性)和CPHA(时钟相位)来控制主设备的通信模式。

具体模式具体如下::CPOL=0,CPHA=0Mode1:CPOL=0,CPHA=1Mode2:CPOL=1,CPHA=0Mode3:CPOL=1,CPHA=1模式CPOL CPHAMode0 0 0Mode1 0 1Mode2 1 0Mode3 1 1时钟极性CPOL是用来配置SCLK电平的有效态的;时钟相位CPHA是用来配置数据采样是发生在第几个边沿的。

泰克4000系列示波器SPI总线演示(3GC-20258-1)

按 B1 按钮 把 Bus Type 设置成 SPI 定义 Inputs:把 CH1 设置成 SCLK, CH2 设 把 置成 SS,把 CH3 设置成 MOSI 把 Thresholds 设置成 1.6 V 按 Trigger Menu 按钮 把 Type 设置成 Bus 把 Source 设置成 B1 设置 Trigger On MOSI Data = 17 hex (使用多功能旋钮 输入值) 设置 Trigger mode: Normal 按 Menu Off 按钮 按 Single 按钮

SPI 总线是一条主 / 从 4 线串行通信总线。在两台设备通信时,一个称为“主设 备” ,另一个称为“从设备” 。主设备驱动着串行时钟。它同时传送和接收数据。 SPI 使用 SS 线,指定与哪台设备传送数据。因此,总线上每台唯一的设备都需 要主设备提供自己的 SS 信号。

单主设备硬连线到单从设备

SPI 总线硬件配置

注意示波器在 MOSI Data 17 hex 上触发采集

/partners

手动分组解码

与

DPO4000 自动解码

SPI (串行外设接口)总线

SCLK MOSI MISO SS 串行时钟 主输出 / 从输入 主输入 / 从输出 从设备选择

级联设备

单主设备,多从设备

泰克 4000 系列示波器

SPI 总线演示

SPI 总线 SPI 总线设置和触发

演示培训资料

4000 系列示波器,带 DPO4EMBD 应用模块 DPO Demo 2 电路板(020-2924-00)

使用USB电缆把演示电路板连接到DPO4000上, 在 USB POWER LED 指示灯亮时,电路板启动 使用探头: 把 CH1 连接到 SCLK 把 CH2 连接到 SPI SS 把 CH3 连接到 SPI MOSI 按 Default Setup 按钮 按 Acquire 按钮 把 Record Length 设置成 100k 打开 CH2 和 Ch3 把 CH1、CH2 和 CH3 设置成 2 Volts/div 把波形定位在屏幕上 在必要时调节触发电平 把 Horizontal scale 设置成 1ave Inspector 平移 / 缩放控制功能轻松查看 MOSI 数据包

SPI总线协议介绍

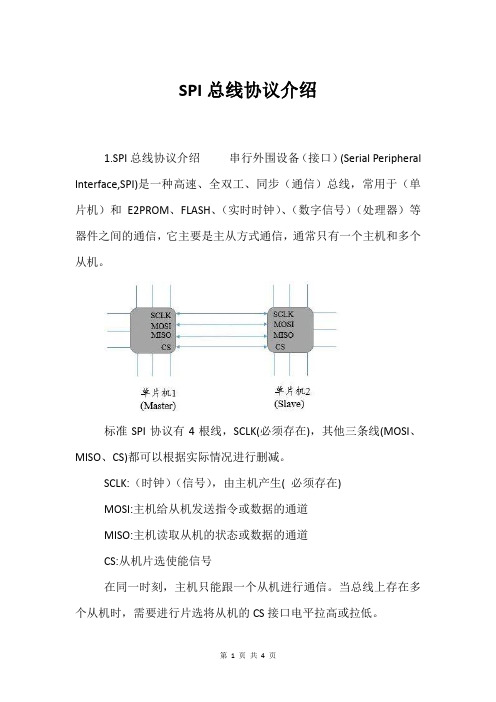

SPI总线协议介绍1.SPI总线协议介绍串行外围设备(接口)(Serial Peripheral Interface,SPI)是一种高速、全双工、同步(通信)总线,常用于(单片机)和E2PROM、FLASH、(实时时钟)、(数字信号)(处理器)等器件之间的通信,它主要是主从方式通信,通常只有一个主机和多个从机。

标准SPI协议有4根线,SCLK(必须存在),其他三条线(MOSI、MISO、CS)都可以根据实际情况进行删减。

SCLK:(时钟)(信号),由主机产生( 必须存在)MOSI:主机给从机发送指令或数据的通道MISO:主机读取从机的状态或数据的通道CS:从机片选使能信号在同一时刻,主机只能跟一个从机进行通信。

当总线上存在多个从机时,需要进行片选将从机的CS接口电平拉高或拉低。

2.SPI总线寻址模式SPI协议和(I2C)协议一样,数据是从高位到低位依次发送,SPI协议中SCLK在空闲时可以是高电平也可以是低电平。

下面以空闲时,SCLK为高电平举例。

当SCLK出现下降沿即从高电平跳到低电平时,进行数据输出;当SCLK出现上升沿即从低电平跳到高电平时,进行数据采样。

SPI总线寻址模式和I2C协议相比,SPI协议没有开始位、停止位、应答位,规则上简单很多。

SPI协议中SCLK在空闲时可以是高电平也可以是低电平,这其实反映了时钟的极性。

上图中,CPOL=1,CPHA=1 。

CPOL时钟极性:CPOL=0,SCLK空闲时状态为低电平CPOL=1,SCLK空闲时状态为高电平时钟的相位:它决定了什么时候进行数据输出,什么时候进行数据采样。

CPHA时钟相位:CPHA=0,每个周期的第一个跳变沿进行数据采样CPHA=1,每个周期的第一个跳变沿进行数据输出。

SPI总线学习

SPI总线学习1、S PI总线速度:波特率可以高达5Mbps,具体速度大小取决于SPI硬件。

例如,Xicor公司的SPI串行器件传输速度能达到5MHz;ATMEL的AT45DB021B,20 MHz Max Clock Frequency;LPC2214的SPI,最大数据位速率为输入时钟速率的1/8。

2、SPI简介:同步外设接口(SPI)是由摩托罗拉公司开发的全双工同步串行总线,该总线大量用在与EEPROM、ADC、FLASH和显示驱动器之类的慢速外设器件通信。

SPI(Serial Peripheral Interface)是一种串行同步通讯协议,由一个主设备和一个或多个从设备组成,主设备启动一个与从设备的同步通讯,从而完成数据的交换。

通讯时,数据由MOSI 输出,MISO输入,数据在时钟的上升或下降沿由MOSI输出,在紧接着的下降或上升沿由MISO读入,这样经过8/16次时钟的改变,完成8/16位数据的传输。

在一次数据传输过程中,接口上只能有一个主机和一个从机能够通信。

并且,主机总是向从机发送一个字节数据,而从机也总是向主机发送一个字节数据。

该总线通信基于主-从配置。

它有4个信号:MOSI:主出/从入MISO:主入/从出SCK:串行时钟SS:从属选择 。

即CS(从使能信号),CS决定了唯一的与主设备通信的从设备,如 没有CS信号,则只能存在一个从设备,主设备通过产生移位时钟来发起通讯。

在SPI传输中,数据是同步进行发送和接收的。

数据传输的时钟基于来自主处理器的时钟脉冲,摩托罗拉没有定义任何通用SPI的时钟规范。

然而,最常用的时钟设置基于时钟极性(CPOL)和时钟相位(CPHA)两个参数,CPOL定义SPI串行时钟的活动状态,而CPHA定义相对于SO-数据位的时钟相位。

CPOL和CPHA的设置决定了数据取样的时钟.3、例子:LPC2214有两个SPI接口。

SPI从机选择信号是一个低有效信号,用于指示被选择参与数据传输的从机。

SPI通信协议(SPI总线)学习

SPI通信协议(SPI总线)学习

SPI(Serial Peripheral Interface)是一种同步的、全双工的通信总线,常用于连接微

控制器和外围设备。

SPI总线的通信协议相对简单,有四根信号线组成:SCLK(时钟

信号)、MOSI(主机输出从机输入信号)、MISO(主机输入从机输出信号)和SS (片选信号)。

SPI总线的工作方式如下:

1. 选择从机:主机通过将片选信号(SS)置低来选择要通信的从机。

通常每个从机都

有独立的片选线。

2. 时钟信号:主机通过时钟信号(SCLK)提供同步时钟给从机,控制数据传输的时钟周期。

3. 主机输出从机输入:主机将要发送给从机的数据通过主机输出从机输入信号(MOSI)发送给从机。

数据按照时钟的上升沿或下降沿传输。

4. 主机输入从机输出:从机将要发送给主机的数据通过主机输入从机输出信号(MISO)传输给主机。

数据按照时钟的上升沿或下降沿传输。

5. 数据传输顺序:数据传输是基于时钟信号的,每个时钟周期传输一个位。

主机和从

机按照特定的数据传输格式进行通信,可以是先传输最高有效位(MSB)或最低有效

位(LSB)。

6. 数据传输模式:SPI总线支持多种数据传输模式,如模式0、模式1、模式2和模式3,不同模式下时钟信号和数据传输的相位和极性不同。

7. 传输完成:主机通过将片选信号(SS)置高来结束通信。

SPI总线的优点是简单、高速、低成本,适用于连接多种外设,如传感器、存储器、显示器等。

然而,SPI总线并没有提供错误检测和纠正机制,需要通过其他方式保证数据的可靠性。

SPI总线协议及SPI时序图详解含实例

SPI 接口有四种不同的数据传输时序,取决于 CPOL 和 CPHL 这两位的组合。图 1 中 表现了这四种时序,

时序与 CPOL、CPHL 的关系也可以从图中看出。

图1

CPOL 是用来决定 SCK 时钟信号空闲时的电平,CPOL=0,空闲电平为低电平,CPOL =1 时,

主器件的输入口 MISO 同样是在时钟的前沿采样从器件输出的 bit1 的,那从器件又是 在何时刻输出 bit1 的呢。

从器件是在 SSEL 信号有效后,立即输出 bit1,尽管此时 SCK 信号还没有起效。关于 上面的主器件

和从器件输出 bit1 位的时刻,可以从图 3、4 中得到验证。

图3 注意图 3 中,CS 信号有效后(低电平有效,注意 CS 下降沿后发生的情况),故意用 延时程序 延时了一段时间,之后再向数据寄存器写入了要发送的数据,来观察主器件输出 bit1 的情况(MOSI)。 可以看出,bit1(值为 1)是在 SCK 信号有效之前的半个时钟周期的时刻开始输出的 (与 CS 信号无关), 到了 SCK 的第一个时钟周期的上升沿正好被从器件采样。

SPI,是一种高速的,全双工,同步的通信总线,其工作模式有两种:主模式和从模式,无 论那种模式,都支持

SPI 接口没有指定的流控制,没有应答机制确认是否接收到数据。

SPI 接口时钟配置: 在主设备这边配置 SPI 接口时钟的时候一定要弄清楚从设备的时钟要求,因为主设备 这边的时钟极性和相位都是以从设备为基准的。因此在时钟极性的配置上一定要搞清楚从设 备是在时钟的上升沿还是下降沿接收数据,是在时钟的下降沿还是上升沿输出数据。但要注 意的是,由于主设备的 SDO 连接从设备的 SDI,从设备的 SDO 连接主设备的 SDI,从设 备 SDI 接收的数据是主设备的 SDO 发送过来的,主设备 SDI 接收的数据是从设备 SDO 发 送过来的,所以主设备这边 SPI 时钟极性的配置(即 SDO 的配置)跟从设备的 SDI 接收数 据的极性是相反的,跟从设备 SDO 发送数据的极性是相同的。下面这段话是 Sychip Wlan8100 Module Spec 上说的,充分说明了时钟极性是如何配置的: The 81xx module will always input data bits at the rising edge of the clock, and the host will always output data bits on the falling edge of the clock. 意思是:主设备在时钟的下降沿发送数据,从设备在时钟的上升沿接收数据。因此主设 备这边 SPI 时钟极性应该配置为下降沿有效。 又如,下面这段话是摘自 LCD Driver IC SSD1289:

第五讲 SPI操作

也许,昨晚你刚看完前面的四讲,学到了VHDL编程的基本功。

结果,第二天一早“老板”需要你接手某项目上的CPLD编程,其中就包括今天要讲解的AT93C46存储芯片的VHDL驱动。

首先,这个芯片采用的是“三线串行接口”,兼容SPI接口。

所谓的SPI就是Serial Peripheral interface的缩写,即串行外围设备接口,是Motorola公司推出的三线同步接口,一种高速的,全双工,同步的通信总线。

该总线广泛应用于EEPROM,FLASH,实时时钟,AD转换器,数字信号处理器(DSP)、数字信号解码器、单片机和诸如ARM 等高端的微处理器中。

所以,这个接口的用处很广,掌握了这类接口操作的操作方法对我们以后的学习有很大的帮助。

我们先了解一下SPI的一些基本知识点。

SPI以主从方式工作,这种模式通常有一个主设备和一个或多个从设备。

进行数据传输时需要如下的信号线:MOSI,MISO,SCK,SS(多个从设备时需要)。

(1)MOSI–主设备数据输出,从设备数据输入(2)MISO–主设备数据输入,从设备数据输出(3)SCK–时钟信号,只能由主设备产生,也就是说谁产生SCLK,谁就是主设备(4)SS–从设备使能信号,由主设备控制如下图是一对一的硬件连接框图:SPI接口在内部硬件实现上就是两个简单的移位寄存器:在主器件产生的SS信号和SCK脉冲下,按位传输,高位在前,低位在后(具体器件应用时的时序可能会变化,这也就是所谓的兼容SPI)。

如在下图中,数据在SCLK的下降沿改变,在SCLK上升沿被采样。

简单了解SPI后,我们再看详细的看其手册,获取对我们有用的信息。

ATMEL公司生产的93C46芯片有1K bit的存储空间,有8位和16位数据模式可选择,即1K bit的存储可分为128×8或64×16,它的电压范围是2.7V到5.5V和1.8V到5.5V,在5V的电压下最高时钟频率可以达到2M,芯片可以进行一百万次的擦写,数据可以保存一百年。

SPI接口详细讲解

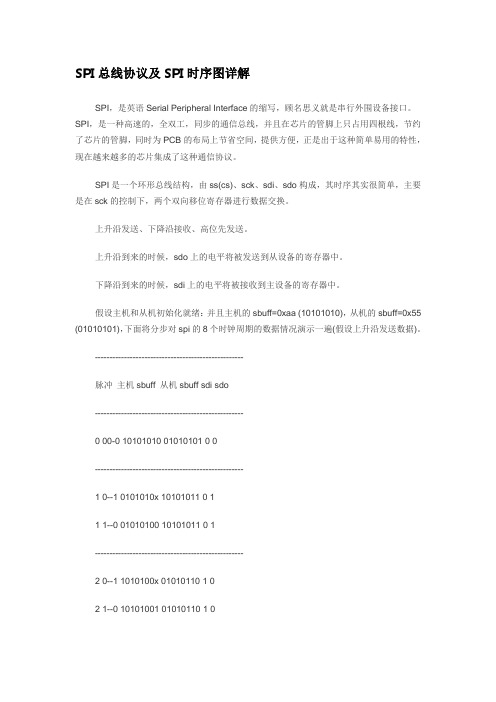

• CPOL(时钟极性)=0; • 上升沿发送、下降沿接收、高位先发送。 • 上升沿到来的时候,MOSI上的电平将被发送到从设备

的寄存器中。 • 下降沿到来的时候,MISO上的电平将被接收到主设备

的寄存器中。 • 假设主机和从机初始化就绪:并且主机的sbuf=0xaa

(10101010),从机的sbuf=0x55 (01010101),下面将分步 对SPI的8个时钟周期的数据情况演示一遍(假设上升沿发 送数据)。Sbuf(串行接收和发射缓冲器)

7

脉冲

0 1↑ 1↓ 2↑ 2↓ 3↑ 3↓ 4↑ 4↓ 5↑ 5↓ 6↑ 6↓ 7↑ 7↓ 8↑

1

2021/6/4

一 SPI接口简介

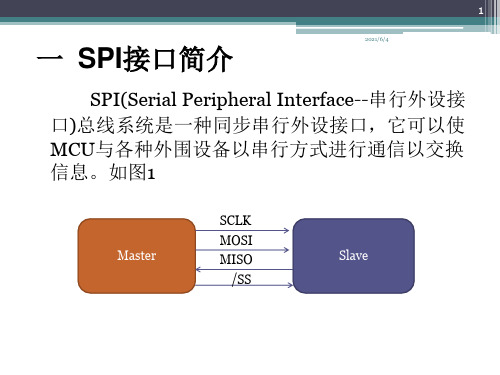

SPI(Serial Peripheral Interface--串行外设接 口)总线系统是一种同步串行外设接口,它可以使 MCU与各种外围设备以串行方式进行通信以交换 信息。如图1

Master

SCLK MOSI Mபைடு நூலகம்SO

/SS

Slave

2

2021/6/4

• (1)MOSI – 主设备数据输出,从设备数据输入 • (2)MISO – 主设备数据输入,从设备数据输出 • (3)SCLK – 时钟信号,由主设备产生 • (4)/SS – 从设备使能信号,由主设备控制

主机sbuff 10101010 0101010X 01010100 1010100X 10101001 0101001X 01010010 1010010X 10100101 0100101X 01001010 1001010X 10010101 0010101X 00101010 0101010X

SPI总线协议介绍(易懂)

SPI总线协议介绍(易懂)目录CONTENTS•SPI总线协议产生背景•SPI总线协议内容介绍•SPI总线协议总结一、SPI总线协议背景12 SPI是由摩托罗拉(Motorola)公司于1979年开发的全双工同步串行总线,是微处理控制单元(MCU)和外围设备之间进行通信的同步串行端口。

主要应用在EEPROM、Flash、实时时钟(RTC)、数模转换器(ADC)、网络控制器、MCU、数字信号处理器(DSP)以及数字信号解码器之间。

SPI,全称Serial Peripheral Interface,中文意思是串行外部设备接口,是一种全双工、高速、同步的通信总线。

SPI 总线器件可直接与各个厂家生产的多种标准外围器件直接接口,一般使用4 条线:串行时钟线SCLK、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI 和低电平有效的从机选择线CS3SPI总线术语及定义,如表(1)所示:表(1) SPI总线术语及定义二、SPI总线协议内容1<1>.SPI总线采用主从模式架构,支持多从设备应用,一般只支持单主设备;<2>.当主设备想要和某从设备进行通信时候,主设备需要先向对应从设备的片选线(CS)山发送使能信号(高电平或者低电平,按从设备而定),表示选中该从设备;<3>.时钟由主设备控制,数据在时钟脉冲下按位传输,高位在前;<4>.目前应用中的数据速率可达几Mbps。

2SPI设备之间采用全双工模式通信,是一个主机和一个或者多个从机的主从模式。

主机负责初始化帧,这个数据传输帧可以用于读与写两种操作,片选线可以从多个从机选择一个来响应主机的请求。

如图(1)、图(2)、图(3)和图(4)所示图(1)SPI连接类型首先Master产生时钟,时钟频率小于或等于Slave支持的最大频率;随后Master通过产生时钟信号(SCLK)来控制数据传输,并通过将特定Slave的芯片选择(CS)线拉低来进行通信。

SPI-4.2总线应用和调试经验谈

⑤接收和发送模块都含有一个FIFO队列,用于缓存数据,队列长度由芯片设计而定。队列的状态信息通过状态链路周期性地发送,接收模块和发送模块的状态信息是独立的。状态信息附加了DIP-2不满16字节的数据(EOP)之外,SPI-4.2总线的数据实行突发传输,以16字节为单位(称为一个数据块),每次传输多个数据块。因为数据宽度是16位,所以一次突发传输至少需要4个时钟周期。数据的高地址位字节先发送(MSB),低地址位字节后发送,数据块传输过程中不会被中断。每次突发传输的间隔期间传送控制包或者训练序列。图2中,TDAT表示数据块,TCTRL表示控制块。控制包长度为16位,包含了前次传输和下次传输的状态信息:包开始标志、包结束标志、逻辑端口地址和DIP-4交织校验码等。数据链路遵循有限状态机进行工作,状态包括5种:控制包传输、数据包传输、空闲包传输、训练序列传输以及训练序列控制。 因为状态链路的宽度是2位,所以每次突发传输至少传输16位数据(4个时钟周期)。反映FIFO队列的状态信息有3种:饱(Satisfied)、饿(Hungry)、极饿(Starving),分别对应二进制数字10、01和00。11表示链路处于失步状态,正在同步过程中。当状态是“饱”时,说明队列几乎满了,只接收当前正在传送的数据包,其他数据包只有等状态更新后才能接收。当状态是“饿”时,可以接收最大MaxBurst2个数据块。当状态是“极饿”时,说明队列几乎空了,可以接收最大MaxBurst1个数据块。MaxBurst1和MaxBurst2是SPI-4.2总线初始化时设定的参数,MaxBurst1不得小于MaxBurst2。2 SPI-4.2总线的初始化和同步 SPI-4.2总线初始化时必须设定一些基本参数,如表1所列。

SPI总线协议及SPI时序图详解

SPI总线协议及SPI时序图详解SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄存器进行数据交换。

上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdo上的电平将被发送到从设备的寄存器中。

下降沿到来的时候,sdi上的电平将被接收到主设备的寄存器中。

假设主机和从机初始化就绪:并且主机的sbuff=0xaa (10101010),从机的sbuff=0x55 (01010101),下面将分步对spi的8个时钟周期的数据情况演示一遍(假设上升沿发送数据)。

---------------------------------------------------脉冲主机sbuff 从机sbuff sdi sdo---------------------------------------------------0 00-0 10101010 01010101 0 0---------------------------------------------------1 0--1 0101010x 10101011 0 11 1--0 01010100 10101011 0 1---------------------------------------------------2 0--1 1010100x 01010110 1 02 1--0 10101001 01010110 1 0---------------------------------------------------3 0--1 0101001x 10101101 0 13 1--0 01010010 10101101 0 1---------------------------------------------------4 0--1 1010010x 01011010 1 04 1--0 10100101 01011010 1 0---------------------------------------------------5 0--1 0100101x 10110101 0 15 1--0 01001010 10110101 0 1---------------------------------------------------6 0--1 1001010x 01101010 1 06 1--0 10010101 01101010 1 0---------------------------------------------------7 0--1 0010101x 11010101 0 17 1--0 00101010 11010101 0 1---------------------------------------------------8 0--1 0101010x 10101010 1 08 1--0 01010101 10101010 1 0---------------------------------------------------这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、sdo相对于主机而言的。

SPI总线详细解析

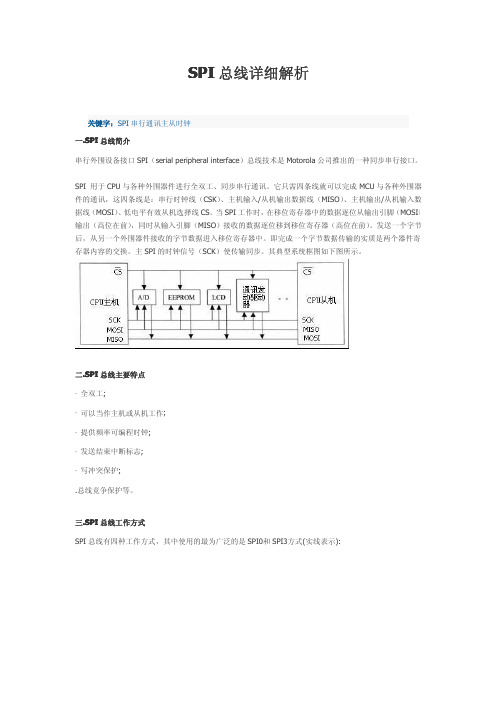

SPI总线详细解析关键字:SPI串行通讯主从时钟一.SPI总线简介串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同步串行接口。

SPI用于CPU与各种外围器件进行全双工、同步串行通讯。

它只需四条线就可以完成MCU与各种外围器件的通讯,这四条线是:串行时钟线(CSK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)、低电平有效从机选择线CS。

当SPI工作时,在移位寄存器中的数据逐位从输出引脚(MOSI)输出(高位在前),同时从输入引脚(MISO)接收的数据逐位移到移位寄存器(高位在前)。

发送一个字节后,从另一个外围器件接收的字节数据进入移位寄存器中。

即完成一个字节数据传输的实质是两个器件寄存器内容的交换。

主SPI的时钟信号(SCK)使传输同步。

其典型系统框图如下图所示。

二.SPI总线主要特点·全双工;·可以当作主机或从机工作;·提供频率可编程时钟;·发送结束中断标志;·写冲突保护;.总线竞争保护等。

三.SPI总线工作方式SPI总线有四种工作方式,其中使用的最为广泛的是SPI0和SPI3方式(实线表示):四种工作方式时序分别为:时序详解:CPOL:时钟极性选择,为0时SPI总线空闲为低电平,为1时SPI总线空闲为高电平CPHA:时钟相位选择,为0时在SCK第一个跳变沿采样,为1时在SCK第二个跳变沿采样工作方式1:当CPHA=0、CPOL=0时SPI总线工作在方式1。

MISO引脚上的数据在第一个SPSCK沿跳变之前已经上线了,而为了保证正确传输,MOSI引脚的MSB位必须与SPSCK的第一个边沿同步,在SPI传输过程中,首先将数据上线,然后在同步时钟信号的上升沿时,SPI的接收方捕捉位信号,在时钟信号的一个周期结束时(下降沿),下一位数据信号上线,再重复上述过程,直到一个字节的8位信号传输结束。

第十五章串行外设接口SPIppt课件全

15.2.6 SPI接收数据寄存器(SPRDATn) ❖ SPI接收数据寄存器如表15-6所列。 ❖ 接收数据寄存器中存放SPI口接收到的数据。

第十五章 串行外设3 参考编程例(详见书中)

第十五章 串行外设接口(SPI)ppt课 件(全)

❖ • 接收数据(2):使能SPCONn的TAGD位, 自动发送虚拟数据模式→确定REDY被置位 后,从读缓冲区中读出数据,之后自动开始 数据传输。

❖ • 置位GPIO引脚(当作nSS的那个引脚), 停止MMC或SD卡。

第十五章 串行外设接口(SPI)ppt课 件(全)

15.1.5 SPI口的传输格式 ❖ S3C2410支持4种不同的数据传输格式,图

B形式。 ❖ • 查询模式,如果接受从设备采用Format B

形式,DATA_READ信号应该比SPICLK延 迟一个相位。

❖ • 中断模式,如果接受从设备采用Format B 形式,DATA_READ信号应该比SPICLK延 迟一个相位。

第十五章 串行外设接口(SPI)ppt课 件(全)

15.2 SPI接口控制寄存器

❖ • 向SPDATn中写10次0xFF来初始化MMC或 SD卡。

❖ • 把一个GPIO(当作nSS)清零来激活 MMC或SD卡。

第十五章 串行外设接口(SPI)ppt课 件(全)

❖ • 发送数据→核查发送准备好标志 (REDY=1),之后向SPDATn中写数据。

❖ • 接收数据(1):禁止SPCONn的TAGD位, 正常模式→向SPDAT中写0xFF,确定REDY 被置位后,从读缓冲区中读出数据。

第十五章 串行外设接口(SPI)ppt课 件(全)

SPI接口是以主从方式工作的,这种模式通常 有一个主器件和一个或多个从器件。接口包 括以下四种信号:

SPI总线学习资料

SPI总线制作人:刘洪利上海电力学院2011.5.20SPI总线R SPI总线是串行外围设备接口,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线.R SPI的通信原理很简单,它以主从方式工作,通常有一个主设备和一个或多个从设备,需要至少4根线。

R SDO–主设备数据输出,从设备数据输入R SDI–主设备数据输入,从设备数据输出R SCLK–用来为数据通信提供同步时钟信号,由主设备产生R CS–从设备使能信号,由主设备控制R SPI接口是全双工、同步、串口、单主机。

2SPI从机的内部结构l SPI从机从主机获得时钟和片选信号,因此cs和sclk都是输入信号。

l SPI接口在内部硬件实际上是个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。

3SPI总线从机没有被选中,,他的数据输出端SDO将处于高R如果一个SPI从机没有被选中阻状态,从而与当前处于激活状态的隔离开。

寻址:MOSI:When master,out line;when slave,in lineMISO:When master,in line;when slave,out line4SPI 从机的内部结构-SPI 接口实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。

-上升沿发送,下降沿接收。

(有的器件是上升沿接收,下降沿发送)5D7....D0D0....D7SPI 总线R SPI 总线中在一次数据传输过程中,,接口上只能有一个主机和一个从机能够通信。

并且并且,,主机总是数据向从机发送一个字节数据,,而从机也总是向主机发送一个数据字节数据。

R 在SPI 传输中,数据是同步进行发送和接收的。

R 数据传输的时钟基于来自主处理器的时钟脉冲,6R 当SPI 接口上有多个SPI 接口的单片机时,应区别其主从地位,在某一时刻只能由一个单片机为主器件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

SPI总线协议及SPI时序图详解【转】

SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的

特性,现在越来越多的芯片集成了这种通信协议。

SPI是一个环形总线结构,由ss(cs)、sck、sdi、sdo构成,其时序其实很简单,主要是在sck的控制下,两个双向移位寄

存器进行数据交换。

上升沿发送、下降沿接收、高位先发送。

上升沿到来的时候,sdo上的电平将被发送到从设备的寄存器中。

下降沿到来的时候,sdi上的电平将被接收到主设备的寄存器中。

假设主机和从机初始化就绪:并且主机的sbuff=0xaa (10101010),从机的sbuff=0x55 (01010101),下面将分步对spi的8

个时钟周期的数据情况演示一遍(假设上升沿发送数据)。

---------------------------------------------------

脉冲主机sbuff 从机sbuff sdi sdo

---------------------------------------------------

0 00-0 10101010 01010101 0 0

---------------------------------------------------

1 0--1 0101010x 10101011 0 1

1 1--0 01010100 10101011 0 1

---------------------------------------------------

2 0--1 1010100x 01010110 1 0

2 1--0 10101001 01010110 1 0

---------------------------------------------------

3 0--1 0101001x 10101101 0 1

3 1--0 01010010 10101101 0 1

---------------------------------------------------

4 0--1 1010010x 01011010 1 0

4 1--0 10100101 01011010 1 0

---------------------------------------------------

5 0--1 0100101x 10110101 0 1

5 1--0 01001010 10110101 0 1

---------------------------------------------------

6 0--1 1001010x 01101010 1 0

6 1--0 10010101 01101010 1 0

---------------------------------------------------

7 0--1 0010101x 11010101 0 1

7 1--0 00101010 11010101 0 1

---------------------------------------------------

8 0--1 0101010x 10101010 1 0

8 1--0 01010101 10101010 1 0

---------------------------------------------------

这样就完成了两个寄存器8位的交换,上面的0--1表示上升沿、1--0表示下降沿,sdi、 sdo相对于主机而言的。

根据以上分析,一个完整的传送周期是16位,即两个字节,因为,首先主机要发送命令过去,然后从机根据主机的名准备数据,主机在下一个

8位时钟周期才把数据读回来。

SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于 CPU与各种外围器件进行全双工、同步串行通讯。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线有四种工作方式(SP0, SP1, SP2, SP3),其中使用的最为广泛的是SPI0和SPI3方式。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果 CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设音时钟相

位和极性应该一致。

SPI时序图详解-SPI接口在模式0下输出第一位数据的时刻

SPI接口在模式0下输出第一位数据的时刻

SPI接口有四种不同的数据传输时序,取决于CPOL和CPHL这两位的组合。

图1中表现了这四种时序,

时序与CPOL、CPHL的关系也可以从图中看出。

图1

CPOL是用来决定SCK时钟信号空闲时的电平,CPOL=0,空闲电平为低电平,CPOL=1时,空闲电平为高电平。

CPHA是用来决定采样时刻的,CPHA=0,在每个周期的第一个时钟沿采样,

CPHA=1,在每个周期的第二个时钟沿采样。

由于我使用的器件工作在模式0这种时序(CPOL=0,CPHA=0),所以将图1简化为图2,

只关注模式0的时序。

图2

我们来关注SCK的第一个时钟周期,在时钟的前沿采样数据(上升沿,第一个时钟沿),

在时钟的后沿输出数据(下降沿,第二个时钟沿)。

首先来看主器件,主器件的输出口(MOSI)输出的数据bit1,在时钟的前沿被从器件采样,那主器件是在何时刻输出bit1的呢?bit1的输出时刻实际上在SCK信号有效以前,比 SCK的上升沿还要早半个时钟周期。

bit1的输出时刻与SSEL信号没有关系。

再来看从器件,主器件的输入口MISO同样是在时钟的前沿采样从器件输出的bit1的,那从器件又是在何时刻输出bit1的呢。

从器件是在SSEL信号有效后,立即输出bit1,尽管此时SCK信号还没有起效。

关于上面的主器件

和从器件输出bit1位的时刻,可以从图3、4中得到验证。

图3

注意图3中,CS信号有效后(低电平有效,注意CS下降沿后发生的情况),故意用延时程序延时了一段时间,之后再向数据寄存器写入了要发送的数据,来观察主器件输出bit1的情况(MOSI)。

可以看出,bit1(值为1)是在SCK信号有效之前的半个时钟周期的时刻开始输出的(与CS信号无关),

到了SCK的第一个时钟周期的上升沿正好被从器件采样。

图4

图4中,注意看CS和MISO信号。

我们可以看出,CS信号有效后,从器件立刻输出了bit1(值为1)。

通常我们进行的spi操作都是16位的。

图5记录了第一个字节和第二个字节间的相互衔接的过程。

第一个字节的最后一位在SCK的上升沿被采样,随后的SCK下降沿,从器件就输出了第二个字节的第一位。

SPI总线协议介绍(接口定义,传输时序)

一、技术性能

SPI接口是Motorola 首先提出的全双工三线同步串行外围接口,采用主从模式(Master Slave)架构;支持多slave模式应用,

一般仅支持单Master。

时钟由Master控制,在时钟移位脉冲下,数据按位传输,高位在前,低位在后(MSB first);SPI接口有2根单向数据线,为全双工通信,目前应用中的数据速率可达几Mbps的水平。

-------------------------------------------------------

二、接口定义

SPI接口共有4根信号线,分别是:设备选择线、时钟线、串行输出数据线、串行输入数据线。

(1)MOSI:主器件数据输出,从器件数据输入

(2)MISO:主器件数据输入,从器件数据输出

(3)SCLK :时钟信号,由主器件产生

(4)/SS:从器件使能信号,由主器件控制

-------------------------------------------------------

三、内部结构

-------------------------------------------------------

四、传输时序

SPI接口在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位,在主器件产生的从器件使能信号和移位脉冲下,按位传输,高位在前,低位在后。

如下图所示,在SCLK的下降沿上数据改变,上升沿一位数据被存入移位寄存器。

SPI接口没有指定的流控制,没有应答机制确认是否接收到数据。