半导体工艺2

SOC材料与工艺2(光刻胶非光学光刻刻湿)精品资料

制版的目的就是产生一套分层的版图掩模,

为将来进行图形转移,即将设计的版图转移到 硅片上去做准备。

制版是通过图形发生器完成图形的缩小和

重复。在设计完成集成电路的版图以后,设计 者得到的是一组标准的制版数据,将这组数据 传送给图形发生器(一种制版设备),图形发生 器(PG-pattern generator)根据数据,将设 计的版图结果分层的转移到掩模版上(掩模版 为涂有感光材料的优质玻璃板),这个过程叫

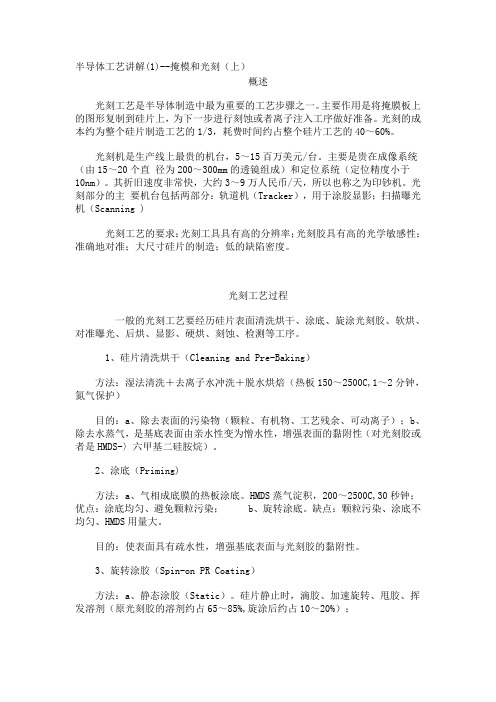

1. Vapor prime

O2

Plasma Strip and clean

Rework

2. Spin coat

3. Soft bake

4. Align and expose

5. Post-exposure bake

Rejected wafers

8. Develop inspect

7. Hard bake

初缩。

人工设计和绘制版图,有利于充分利用芯片面积, 并能满足多种电路性能要求。但是效率低、周期 长、容易出错,特别是不能设计规模很大的电路 版图。因此,该方法多用于随机格式的、产量较 大的MSI和LSI或单元库的建立。

•(DRC-设计规则捡查)

涤沦膜上画图

数字化仪输入

CRT 显示

绘图仪画图

精缩版

初缩版

– 光刻胶受到特定波长光线的作用后,导致其化学结构 发生变化,使光刻胶在某种特定溶液中的溶解特性改 变

• 正胶:分辨率高,在超大规模集成电路工艺中,一般只 采用正胶

• 负胶:分辨率差,适于加工线宽≥3m的线条

半导体器件原理和工艺2

半导体器件

晶体管的频率特性---小信号模型

▪ 小信号工作条件:

➢ 输入信号电压以及输出信号电压都远小于热电压 (kT/q)

vBE VBE vbe iC IC ic

半导体器件

小信号模型-1

i1

i2

v1

T

v2

短路输入导纳 短路反向跨导纳

短路正向跨导纳 短路输出导纳

半导体器件

h参数 短路输入阻抗

小信号模型-2

短路正向电流传输系 数、即电流增益

开路反向电压传输系 数,即电压反馈系致

半导体器件

开路输出导纳

小信号模型-3

共发射极h参数等效电路

b vbe

c vce e

半导体器件

小信号等效电路

▪ 混合模型

g

-g

gm

go

由E-M方程:

正向有源区

半导体器件

混合模型-1

▪ 跨导gm

1. gm正比于Ic,反比于T。 2. gm只决定于工作电流及工作温度,与器件所用材

半导体器件

Bardeen, Brattain, and Schockley 获1956年诺贝尔物理奖

晶体管的特性

半导体器件

半导体器件

理想NPN掺杂分布

▪ 集电结外延, 发射结离子 注入

eb

半导体器件

c

晶体管的静电特性

▪ 两个独立的PN结构成

N+

P

N

半导体器件

背靠背二极管

半导体器件

工作原理

半导体器件

特征频率和截止频率

▪ 特征频率fT和截止频率f 是根据hFE随频率的变化 关系定义的

半导体器件

特征频率和截止频率-1

半导体制造工艺流程简介 (2)

半导体NPN高频小功率晶体管制造的工艺流程为:外延片——编批——清洗——水汽氧化——一次光刻——检查——清洗——干氧氧化——硼注入——清洗——UDO淀积——清洗——硼再扩散——二次光刻——检查——单结测试——清洗——干氧氧化——磷注入——清洗——铝下CVD——清洗——发射区再扩散——三次光刻——检查——双结测试——清洗——铝蒸发——四次光刻——检查——氢气合金——正向测试——清洗——铝上CVD——检查——五次光刻——检查——氮气烘焙——检查——中测——中测检查——粘片——减薄——减薄后处理——检查——清洗——背面蒸发——贴膜——划片——检查——裂片——外观检查——综合检查——入中间库。

PNP小功率晶体管制造的工艺流程为:外延片——编批——擦片——前处理——一次氧化——QC检查(tox)——一次光刻—□□—QC检查——单结测试——磷注入——前处理——发射区氧化——前处理——发射区再扩散——前处理——POCl3预淀积(R□)——后处理——前处理——HCl退火、N2退火——三次光刻——QC检查——双结测试——前处理——铝蒸发——QC检查(t Al)——四次光刻——QC检查——前处理——氮氢合金——氮气烘焙——正向测试(ts)——外协作(ts)——前处理——五次光刻——QC检查——大片测试——测试ts——中测编批——中测——中测检查——入中间库。

变容管制造的工艺流程为:外延片——编批——擦片——前处理——一次氧化——QC检查——N+光刻——QC检查——前处理——干氧氧化——QC检查——P+注入——前处理——N+扩散——P+光刻——QC检查——硼注入1——前处理——CVD(LTO)——QC检查——硼注入2——前处理——LPCVD ——QC检查——前处理——P+扩散——特性光刻——电容测试——是否再加扩——电容测试——......(直到达到电容测试要求)——三次光刻——QC检查——前处理——铝蒸发——QC检查(t Al)——铝反刻——QC检查——前处理——氢气合金——氮气烘焙——大片测试——中测——电容测试——粘片——减薄——QC检查——前处理——背面蒸发——综合检查——入中间库。

半导体八大工艺名称

半导体八大工艺名称1. 硅晶圆制备工艺硅晶圆制备是半导体制造过程的第一步,也是最为关键的一步。

它是指将高纯度的硅材料通过一系列的工艺步骤转化为薄而平整的硅晶圆。

硅晶圆制备工艺主要包括以下几个步骤:(1) 单晶生长单晶生长是将高纯度的硅材料通过熔融和凝固的过程,使其在特定的条件下形成单晶结构。

常用的单晶生长方法包括Czochralski法和区熔法。

(2) 切割切割是将生长好的硅单晶材料切割成薄片的过程。

常用的切割方法是采用金刚石刀片进行切割。

(3) 研磨和抛光研磨和抛光是将切割好的硅片进行表面处理,使其变得平整光滑的过程。

研磨通常使用研磨机进行,而抛光则使用化学机械抛光(CMP)工艺。

(4) 清洗清洗是将研磨和抛光后的硅片进行清洁处理,去除表面的污染物和杂质。

清洗过程通常采用酸洗和溶剂清洗的方法。

2. 光刻工艺光刻工艺是半导体制造中的一项关键工艺,用于将设计好的电路图案转移到硅晶圆上。

光刻工艺主要包括以下几个步骤:(1) 涂覆光刻胶涂覆光刻胶是将光刻胶涂覆在硅晶圆表面的过程。

光刻胶是一种敏感于紫外光的物质,可以通过紫外光的照射来改变其化学性质。

(2) 曝光曝光是将硅晶圆上的光刻胶通过光刻机上的光源进行照射,使其在特定区域发生化学反应。

曝光过程需要使用掩模板来控制光刻胶的曝光区域。

(3) 显影显影是将曝光后的光刻胶进行处理,使其在曝光区域发生溶解或固化的过程。

显影过程通常使用显影液进行。

(4) 清洗清洗是将显影后的硅晶圆进行清洁处理,去除残留的光刻胶和显影液。

3. 离子注入工艺离子注入工艺是将特定的离子注入到硅晶圆中,以改变其电学性质的过程。

离子注入工艺主要包括以下几个步骤:(1) 选择离子种类和能量选择合适的离子种类和能量是离子注入工艺的第一步。

不同的离子种类和能量可以改变硅晶圆的导电性质。

(2) 离子注入离子注入是将选择好的离子通过离子注入机进行注入的过程。

离子注入机通过加速器将离子加速到一定的能量,并将其注入到硅晶圆中。

SOC材料与工艺2(光刻胶非光学光刻刻湿)

微电子器件制造

微电子器件制造中需要高精度的 光刻技术,光刻胶非光学光刻刻 湿技术将有望成为一种重要的解 决方案。

生物医学领域

在生物医学领域,光刻胶非光学 光刻刻湿技术也可用于制造生物 芯片、组织工程和医疗器械等领 域,具有广阔的应用前景。

THANKS

感谢观看

3

制造成本高

由于非光学光刻技术需要高精度的光学系统、电 子束源和精密的年代

非光学光刻技术开始出现,最 初主要应用于高精度掩模版的

制作。

20世纪90年代

随着微电子和微机械的发展, 非光学光刻技术开始应用于集 成电路和微纳器件的制作。

21世纪初

随着纳米技术的不断发展,非 光学光刻技术逐渐成为纳米制 造领域的重要技术之一。

预烘温度和时间

控制预烘过程,使光刻胶与衬底紧密 贴合,防止曝光时产生气泡或脱层现 象。

涂胶厚度

控制光刻胶的涂布厚度,影响最终的 微结构尺寸和精度。

工艺参数

曝光时间和波长

选择合适的曝光时间和波长,以实现最佳的曝 光效果。

显影液成分和浓度

选择合适的显影液成分和浓度,以实现最佳的 显影效果。

坚膜温度和时间

新型材料的应用

为了提高光刻胶非光学光刻刻湿技术的性能,未来将不断 探索和开发新型的光刻胶材料,以提高分辨率、对比度和 稳定性。

智能化和自动化

随着人工智能和机器学习技术的发展,未来光刻胶非光学 光刻刻湿技术将更加智能化和自动化,提高生产效率和良 品率。

技术应用前景

集成电路制造

光刻胶非光学光刻刻湿技术是集 成电路制造中的关键技术之一, 随着集成电路工艺的不断进步, 该技术的应用前景将更加广阔。

量和效率。

降低制造成本

2、半导体工艺原理-扩散

薄层电阻Rs(方块电阻) 表面浓度:扩散层表面的杂质浓度。

扩散层质量参数

方块电阻

方块电阻是标志扩散层质量的另一个重要参数, 一般用R□或Rs表示,单位是Ω/□ 。

2、恒定杂质总量扩散

扩散开始时,表面放入一定量的杂质源,而在以后的扩散

过程中不再有杂质加入。假定扩散开始时硅片表面极薄一层内

单位面积的杂质总量为 QT ,杂质的扩散长度远大于该层厚度,

则杂质的初始分布可取为 函数,扩散方程的初始条件和边界

条件为

0 N (x, t)dx QT

N (,t) 0

2 NS1

D1t1 D2t2

exp

x

2 j

4 D2t2

NB

即可解得

xj 2

D2t2

ln

2 NS1

NB

1

D1t1 D2t2

2

A

D2t2

掺杂分布控制:

3.3 简单理论的修正

前面得出的扩散后的杂质分布是采用理想化假设的结果, 而实际分布与理论分布之间存在着一定的差异,主要有:

1、二维扩散(横向扩散) 实际扩散中,杂质在通过窗口垂直向硅中扩散的同时,也 将在窗口边缘沿表面进行横向扩散。考虑到横向扩散后,要得 到实际的杂质分布,必须求解二维或三维扩散方程。横向扩散 的距离约为纵向扩散距离的 75% ~ 80% 。由于横向扩散的存在, 实际扩散区域大于由掩模版决定的尺寸,此效应将直接影响到 VLSI 的集成度。

2、杂质浓度对扩散系数的影响

前面的讨论假定扩散系数与杂质浓度无关。实际上只有当 杂质浓度比扩散温度下的本征载流子浓度 ni(T) 低时,才可认 为扩散系数与掺杂浓度无关。在高掺杂浓度下各种空位增多, 扩散系数应为各种电荷态空位的扩散系数的总和。

半导体后道工艺简介

目录

后道工艺流程总体简介 减薄工艺介绍 背孔工艺介绍 划片工艺介绍 后道工艺动画展示

后道工艺流程总体简介

上蜡

减薄

下蜡

背面 掩膜 制备

背孔 刻蚀

背金 制备

划片

最终 测试 分选

1. 后道流程主要为以上8个步骤; 2. 后道使用的设备分别有:上蜡设备,减薄设备,热板,光刻

设备,蒸镀设备,电镀设备,刻蚀设备,划片设备及测试分 选设备。 3. 其中减薄工艺及划片工艺为后道工艺特有工艺。减薄设备与 划片设备也成为后道工艺的特有设备。

工艺要点:

刻蚀孔道定位:若发生偏差将影响背金与源极接触。 刻蚀掩膜选择:要求选择刻蚀选择比大的材料做掩膜。 刻蚀孔道:要求孔壁与孔底平整(前道减薄抛光工艺将对孔底平整度有

影响),避免被刻蚀物残留。

划片工艺介绍

贴片

划片

劈裂(可 选)

倒膜

扩张

划片工艺:为将单个器件分离开来,根据材料不同(Si,SiC,

(精抛磨料如高目数的SiO磨料或Al2O3磨料等)。

工艺要点:

上蜡平整度:关系到最终晶圆厚度均匀性。 移除率确认:关系到制程时间,同时影响下蜡时的破片率。 下蜡手法:关系到破片率。 工艺面平整度:关系到后续通孔工艺实施难易程度。

背孔工艺介绍

背面掩膜制备

背孔刻蚀

背金制备

背孔工艺流程如上。背孔工艺:因器件特性需求,背孔工艺可 减少因源极接地时引入的加大串联电感,从而减少一定量因此 而产生的负反馈。

光 阻

掩背膜金

背 金

漏

蜡

栅蜡

源

研磨用衬盘

谢谢!

减薄工艺介绍

上蜡

减薄

下蜡

工艺流程如上。减薄工艺是根据不同材料(如Si,SiC,Al2O3等)选择不同 磨料与材料接触并摩擦,摩擦的过程中磨料对材料产生切削作用,从而到 达减薄或抛光的目的。

复旦半导体工艺教材Chapter-2

3. Selective Doping Technology

Si transistor — product of doping engineering

*Device type and performance--determined by impurity doping profile ( element, concentration, distribution)

➢ Lowest power consumption than all others ➢ Noise resistance and higher reliability ➢ Main stream of VLSI/ ULSI process since late 80’s

BiCMOS

➢ Combination of high speed and low power ➢ High process complexity

Low energy ion implant and shallow junction formation — of vital importance for nano-meter CMOS fabrication

High energy ion implant for n/p wells

Rapid thermal process (RTP) and dopant atom diffusion control

*Double diffused mesa transistor process

*Transistor by planar process

➢Transistor and other circuit elements formed by planar technology

✓On-chip resistor: by diffusion; poly-Si by deposition

半导体公司be2全流程的工作内容

半导体公司be2全流程的工作内容下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!半导体公司 BE2 全流程的工作内容一、设计1. 需求分析与客户沟通,了解产品需求和规格。

半导体制造工艺流程(钽电篇)

对未来发展的展望

01

02

03

04

随着科技的不断发展,半导体 制造工艺流程也在不断进步和 完善。未来,钽电制造工艺流 程将继续向着更高效、更可靠 、更环保的方向发展。

随着科技的不断发展,半导体 制造工艺流程也在不断进步和 完善。未来,钽电制造工艺流 程将继续向着更高效、更可靠 、更环保的方向发展。

随着科技的不断发展,半导体 制造工艺流程也在不断进步和 完善。未来,钽电制造工艺流 程将继续向着更高效、更可靠 、更环保的方向发展。

制造工艺流程的未来发展趋势

随着新材料和新技术的不断涌 现,制造工艺流程将朝着更高 效、更灵活、更环保的方向发 展。

未来制造工艺流程将更加注重 智能化和自动化技术的应用, 以提高生产效率和降低成本。

可持续发展将成为未来制造工 艺流程的重要考虑因素,以减 少对环境的影响并实现绿色生 产。

03

钽电制造工艺流程

制造工艺流程需要高度的技术和管理能力,以确保 生产过程中的一致性和可靠性。

制造工艺流程的重要性

02

01

03

制造工艺流程决定了半导体产品的性能和可靠性,是 实现产品差异化的关键因素。

随着技术的不断进步,制造工艺流程也需要不断更新 和改进,以适应市场需求和竞争环境。

制造工艺流程的优化和创新对于降低成本、提高生产 效率和产品质量具有重要意义。

由于其高熔点、高导电性和高强 度等特性,钽电在制造光电器件 中的电极、窗口材料等方面具有

优势。

在光电器件制造过程中,钽电的 应用能够提高器件的稳定性和可

靠性,延长器件的使用寿命。

钽电在其他领域的应用

除了在集成电路和光电器件制造中应 用外,钽电还广泛应用于其他领域。

这些应用都得益于钽电的高熔点、高 导电性和高强度等特性,使得它在各 种极端条件下都能保持稳定的性能。

6-半导体加工技术-2-刻蚀

向低能级越变: XY∗→XY+hv(光子) 发光性(光学应用)

强碰撞分解:XY+e→X+Y+e

反应性(化学应用)

更强碰撞电离:XY+e→XY++2e

导电性(电学应用)

加速:电子和离子由电场加速

高速粒子(力学应用)

升温:粒子间冲击发热,与固体冲击 高温性(热学应用)

XY*为能级较高的激发态分子;

3、等离子体的应用

RF电源 气瓶

等离子体刻蚀装置

7、溅射刻蚀(sputter etching)

溅射:加速的离子轰击固体

表面,从固体表面溅出原子

的现象。

工件

电离气体:惰性气体(氩) 辉光放电电离: Ar+e→Ar++2e 固体原子获得的能量:

等离子体 电极

刻蚀气体 泵

E2 max

=

4m1m2 (m1 + m2 )

E0

E0为离子轰击前能量;m1和m2为离子与固体原子的质量。

能量

制造、材料

环境、宇宙

<电学应用> 热电子发电 MHD发电 核融合发电 闸流管 点火管

<光学应用> 照明用灯管 霓虹灯 气体激光 等离子体显示器 紫外线源 X射线源

<力学应用> 电子束/离子束源 粒子加速

<热学应用> 电弧焊接 放电加热 等离子体喷射 烧结 微粉体制造

<化学应用> 表面改质 等离子体CVD 等离子体刻蚀(太阳电 池、LSI、MEMS、 DRAM等制造)

• EDP、EPW:(ethylene diamine, pyrocatechol, water)

乙二胺(ethylene diamine): NH2-CH2-CH2-NH2 邻苯二酚(pyrocatechol): C6H4(OH)2 不易操作,有毒性,对SiO2、P++选择性好,气泡少。1.3μm/min(115°C)。

半导体制造工艺 第2版

学习情景三

难以淀积合金材料

由于合金是两种金属材料组成,而两种金 属就会有两种不同的熔点,这使得利用蒸 发使合金材料按原合金比例淀积到硅片上 是不可能的;

常州信息职业技术学院

学习情景三

溅射

概念:

利用等离子体中的离子,对被溅镀物体 (粒子靶)进行轰击,使气相等离子体内 具有被溅镀物体的粒子,这些粒子淀积到 硅晶片上形成溅射薄膜;

常州信息职业技术学院

学习情景三

真空设备

机械泵 又称真空旋转泵,用来获得低真空的一种 抽气设备; 能从一个大气压开始抽气,真空度可达103Torr;

常州信息职业技术学院

机械泵结构示意图

学习情景三

常州信息职业技术学院

油泵扩散

学习情景三

原理:当机械泵抽气达到10-2Torr以后,再要 抽气,就要用到油扩散泵了(它的起始点必 须在10-2Torr); 工作时用电炉加热扩散泵油,使之沸腾, 产生大量油蒸汽; 油蒸汽通过各级喷嘴以较高的速率喷射出 来。系统中的气体分子不断作扩散运动, 一旦与油蒸汽分子相撞,就被油蒸汽分子 带走。因为油蒸汽分子的质量大,并且作 定向运动,所以气体分子就会被油蒸汽分 子带到前方;

常州信息职业技术学院

溅射示意图

学习情景三

常州信息职业技术学院

学习情景三

辉光放电

轰击靶材料的高能粒子是辉光放电产生的; 气,两个电极之间的距离为15cm,电压为 1.5kv,在玻璃管中引入一个电子,这个电 子在两个电极间的电场中加速,这个自由 电子有可能碰撞氩原子,把氩原子中的电 子激发出来,激发出来的电子就是轰击源 材料的轰击源;

常州信息职业技术学院

学习情景三

半导体工艺基础氧化

半导体工艺的重要性

半导体工艺是实现电子器件小型化、高性能化的 关键技术,对于推动电子工业的发展具有重要意 义。

随着科技的不断发展,半导体工艺在信息技术、 通信技术、人工智能等领域的应用越来越广泛, 已经成为现代社会不可或缺的重要技术之一。

半导体工艺的历史与发展

半导体工艺的发展经历了从晶体管到集成电路、再到微电子器件的过程,其发展历程与电子工 业的发展密切相关。

01 湿氧

湿氧气作为氧化剂,具有较高的氧化能力,适用 于大多数硅基材料的氧化。

02 高压氧气

高压氧气可以提高硅片的氧化速率,但设备成本 和维护成本较高。

03 其他氧化剂

如臭氧、二氧化氮等,适用于特定条件下的氧化 工艺。

其他辅助材料选择

01

02

03

添加剂

添加剂可以调节氧化速率 、改善二氧化硅层质量, 如掺氯硅片、掺硼硅片等 。

随着新材料、新技术的不断涌现,半导体工艺也在不断进步和完善,未来将朝着更小尺寸、更 高性能、更低成本的方向发展。

02

氧化工艺原理

氧化工艺定义

01

氧化工艺定义

氧化是半导体制造过程中的一种重要工艺,通过与氧气的反应,在半导

体表面形成一层氧化物薄膜。这层氧化物薄膜具有保护和钝化半导体的

作用,同时也可以作为掺杂的掩蔽膜。

氧化炉的安全操作规范

01 操作前检查

确保炉体、热电偶、温度 传感器等设备正常,无安 全隐患。

03 严格控制温度

避免超温导致设备损坏或

产品质量问题。

02 防止气体泄漏

确保炉膛密封良好,防止

有毒气体泄漏。

04 操作人员培训

操作人员应经过专业培训

,熟悉设备操作和安全规

半导体工艺讲解

半导体工艺讲解(1)--掩模和光刻(上)概述光刻工艺是半导体制造中最为重要的工艺步骤之一。

主要作用是将掩膜板上的图形复制到硅片上,为下一步进行刻蚀或者离子注入工序做好准备。

光刻的成本约为整个硅片制造工艺的1/3,耗费时间约占整个硅片工艺的40~60%。

光刻机是生产线上最贵的机台,5~15百万美元/台。

主要是贵在成像系统(由15~20个直径为200~300mm的透镜组成)和定位系统(定位精度小于10nm)。

其折旧速度非常快,大约3~9万人民币/天,所以也称之为印钞机。

光刻部分的主要机台包括两部分:轨道机(Tracker),用于涂胶显影;扫描曝光机(Scanning )光刻工艺的要求:光刻工具具有高的分辨率;光刻胶具有高的光学敏感性;准确地对准;大尺寸硅片的制造;低的缺陷密度。

光刻工艺过程一般的光刻工艺要经历硅片表面清洗烘干、涂底、旋涂光刻胶、软烘、对准曝光、后烘、显影、硬烘、刻蚀、检测等工序。

1、硅片清洗烘干(Cleaning and Pre-Baking)方法:湿法清洗+去离子水冲洗+脱水烘焙(热板150~2500C,1~2分钟,氮气保护)目的:a、除去表面的污染物(颗粒、有机物、工艺残余、可动离子);b、除去水蒸气,是基底表面由亲水性变为憎水性,增强表面的黏附性(对光刻胶或者是HMDS-〉六甲基二硅胺烷)。

2、涂底(Priming)方法:a、气相成底膜的热板涂底。

HMDS蒸气淀积,200~2500C,30秒钟;优点:涂底均匀、避免颗粒污染;b、旋转涂底。

缺点:颗粒污染、涂底不均匀、HMDS用量大。

目的:使表面具有疏水性,增强基底表面与光刻胶的黏附性。

3、旋转涂胶(Spin-on PR Coating)方法:a、静态涂胶(Static)。

硅片静止时,滴胶、加速旋转、甩胶、挥发溶剂(原光刻胶的溶剂约占65~85%,旋涂后约占10~20%);b、动态(Dynamic)。

低速旋转(500rpm_rotation per minute)、滴胶、加速旋转(3000rpm)、甩胶、挥发溶剂。

半导体工艺等离子体技术

半导体工艺等离子体技术1. 嘿,你知道半导体工艺里的等离子体技术吗?那可真是个超酷的玩意儿!就像一群隐形的小工匠,在微观世界里大显身手。

比如说在芯片制造的时候,等离子体就像一群超级微小的雕刻师,精准地把那些复杂的电路图案刻在硅片上。

这要是没有等离子体技术,就像盖房子没有工人一样,芯片哪能那么精致又好用呢?2. 半导体工艺中的等离子体技术啊,简直是魔法一样的存在!我给你说,这等离子体就像是一群微观世界的精灵,在半导体的材料里穿梭、工作。

你看啊,在蚀刻工艺中,它就像一把把无形的小刷子,把不需要的部分刷掉。

要是没有它,那些半导体器件就会像没整理过的杂乱房间,功能乱七八糟的,多糟心啊!3. 哇塞,半导体工艺的等离子体技术,你可不能小瞧!这就好比是一场微观世界的战斗,等离子体就是那英勇的战士。

比如说在清洗半导体表面的时候,等离子体就像一群清洁小卫士,把脏东西都给赶跑。

如果没有等离子体技术,半导体表面就像沾满灰尘的镜子,什么都看不清楚,还怎么发挥作用呢?4. 你了解半导体工艺里的等离子体技术不?这技术就像一把神奇的钥匙,打开了半导体制造的新世界。

在沉积工艺中,等离子体就像一个个勤劳的小搬运工,把需要的材料一层一层地堆积起来。

要是少了它,这就好比盖楼没有砖头,半导体器件根本就没法成型,这可太可怕了吧!5. 半导体工艺中的等离子体技术哟,那可不得了!它就像一个微观的厨师,精心烹饪着半导体材料。

像掺杂工艺中,等离子体就像调味料一样,精确地给半导体材料添加需要的元素。

要是没了这个技术,半导体就像没放盐的菜,淡而无味,根本没法达到我们想要的性能呢。

6. 嗨,我跟你讲半导体工艺的等离子体技术哈。

这就像是一场微观的音乐会,等离子体是那演奏的音乐家。

在光刻胶去除工艺里,等离子体就像灵动的音符,把光刻胶这个障碍物轻松消除。

要是没有等离子体技术,光刻胶就像卡在齿轮里的小石子,半导体的生产进程就会被卡住,那可太麻烦了!7. 哎呀,半导体工艺中的等离子体技术简直太神奇了!你可以把它想象成一群微观的画家,在半导体的画布上尽情创作。

平坦化工艺2

(5)磨粒尺寸、浓度及硬度

CMP的磨粒一般有SiO2,和Al2O 3其尺寸在 20~200nm 之间。一般情况下, 当磨粒尺寸增加, 抛光速率增加,但磨粒尺寸过小则易凝聚成团, 使硅 片表面划痕增加; 磨粒硬度增加, 抛光速率增加, 但划痕增加, 表面质量下降。磨粒的浓度增加时,材 料去除率也随之增加,但当磨粒浓度超过某一值时, 材料去除率将停止增加,维持一个常数值,这种现象 可称为材料去除饱和,但磨粒浓度增加, 硅片表面缺 陷(划痕)增加, 表面质量降低。

一 传统的平坦化技术

反刻

玻璃回流

旋涂膜层

1.1反 刻

概念:由表面图形形成的表面起伏可以用一层 厚的介质或其它材料作为平坦化的牺牲层来进 行平坦化,这一层牺牲材料填充空洞和表面的 低处,然后用干法刻蚀技术来刻蚀这一层牺牲 层,通过用比低处图形快的刻蚀速率刻蚀掉高 处的图形来使表面平坦化。 反刻不能实现全局的平坦化。

一般的化学机械抛光系统构造整个系统是由三 大部分组成。 1一个旋转的硅片夹持器 2承载抛光垫的工作台 3抛光浆料供给装置

Hale Waihona Puke 化学机械平坦化的原理图平坦化的4个术语

CMP设备

CMP是采用把一个抛光垫粘在转盘的表面来进行平坦化,在抛光的时 候一个磨头装有一个硅片,大多数的生产性抛光机都是有多个转盘合 抛光垫,以适应抛光不同材料的需要。

平坦化工艺

李传第 陈建

周天亮 邓应达

概要:

简单的说就是在晶片的表面保持平整平坦的工艺 随着半导体工业飞速发展,电子器件尺寸缩小, 要求晶片表面可接受的分辨率的平整度达到纳米级 。 传统的平面化技术,如选择淀积、旋转玻璃法等,仅 仅能够局部平面化技术,但是对于微小尺寸特征的电 子器件,必须进行全局平面化以满足上述要求。90年 代兴起的新型化学机械抛光技术则从加工性能和速度 上同时满足了硅片图形加工的要求,是目前几乎唯一 的可以提供全局平面化的技术。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Dopant 五价 Pentavale nt 三价 Trivalent

Materi al Type

n p

纯Si电阻率 2.5×105欧姆.cm

Table 4.2

18

硅中电阻率和掺杂浓度之间的关系

19

区熔法(Float Zone)晶体生长

气体入口Gas inlet (inert) 卡盘Chuck 多晶硅(硅)棒 rod 熔融区Molten zone Traveling RF coil

7

3-D结构的晶胞(Unit Cell in 3-D Structure)

Unit cell

Figure 4.4

8

面心立方晶胞(Faced-centered Cubic (FCC) Unit Cell)

Figure 4.5

9

硅晶胞FCC金刚石结构(Silicon Unit Cell: FCC Diamond Structure)

Wafer Dimensions & Attributes

Diameter (mm) 150 200 300 400 Thickness (μm) 675 ± 20 725 ± 20 775 ± 20 825 ± 20 Area (cm2) 176.71 314.16 706.86 1256.64 Weight (grams/lbs) 28 / 0.06 53.08 / 0.12 127.64 / 0.28 241.56 / 0.53 Weight/25 Wafers (lbs) 1.5 3 7 13

Table 4.3

22

Increase in Number of Chips on Larger Wafer Diameter

88 die 200-mm wafer 232 die 300-mm wafer

目的:降低成本

23

300mm 硅片尺寸和晶向要求的发展

Parameter Diameter Thickness (center point) Warp (max) Nine-Point Thickness Variation (max) Notch Depth Notch Angle Back Surface Finish Edge Profile Surface Finish FQA (Fixed Quality Area – radius permitted on the wafer surface) mm

SiC (s) + SiO2 (s) CO (g) Si (s) + 3HCl (g) heat

Si (l) + SiO(g) +

2

SiHCl3 (g) + H2 (g) +

3

2SiHCl3 (g) + 2H2 (g) (g)

2Si (s) + 6HCl

3

西门子工艺提纯的材料有很高纯度 99.9999999% (共9个9)

26

三种点缺陷 Point Defects

(a) Vacancy defect

(b) Interstitial defect

掺杂也是一种缺陷:填隙原子

(c) Frenkel defect

Figure 4.15

27

硅中的杂质

III族,受主杂质 V族,施主杂质, 集成电路中,主要是替位式固溶体 外来原子造成晶格形变

SiHCl3

Polycrystalline silicon rod 多晶硅 棒

4

4.3晶体结构

非晶材料(不能使用) 纯度,必须是单晶材料 晶胞 多晶和单晶结构 晶向 材料不仅有高

5

晶体的原子排列

Figure 4.2

6

非晶原子结构(Amorphous Atomic Structure)

Figure 4.3

43

厂家给出的硅片参数

The wafers in the section have the following tollerances, Diameter ± 0.5 mm Orientation ± 1° Resistivity is measured in Ohm-cm Thickness is measured in microns TTV <10µm Particle Count - (Prime) <10 @ > .3µm

Figure 4.6

10

多晶和单晶(Polycrystalline and Monocrystalline Structures)

Polycrystalline structure

Monocrystalline structure

Figure 4.7

11

4.4 晶向

Z

1Байду номын сангаас

0

Y

1

X

1

Figure 4.8

Figure 4.10

Molten polysilicon Heat shield Water jacket

15

Silicon Ingot Grown by CZ Method

16

CZ Crystal Puller

Photograph courtesy of Kayex Corp., 300 mm Si crystal puller

39

Polished Wafer Edge

Figure 4.24

40

Chemical Etch of Wafer Surface to Remove Damage

Figure 4.25

41

Double-Sided Wafer Polish

Upper polishing pad

Wafer 浆Slurry Lower polishing pad

28

位错

Dislocations in Unit Cells

Figure 4.16

29

层错 Crystal Slip (Gross Defects)

(a)

(b)

(c)

Redrawn from Sorab K. Ghandi, VLSI Fabrication Principles: Silicon and Gallium Arsenide, 2nd edition, New York, Wiley, 1994, page 49

(111)晶向

37

硅片定位槽 Notch and Laser Scribe

1234567890

Notch

Scribed identification number

200mm以上采用定位槽

38

Internal Diameter Saw

Internal diameter wafer saw

Figure 4.23

44

Particle Count - (Test) <30 @ >.5µm All other specifications not listed are per SEMI Standards Our Test Grade surfaces are not guaranteed for epitaxial growth. P = Polished E = Etched L = Lapped C = As Cut

磨片倒角 磨片倒角 晶体生长 晶体生长 清洗 清洗

整型 整型

腐蚀 腐蚀

检查 检查

切片 切片

抛光 抛光

包装 包装

Figure 4.19

34

硅锭径向研磨

Preparing crystal ingot for grinding

Diameter grind

Flat grind

Figure 4.20

35

硅片标识

24

4.6 硅晶体中的缺陷 Defects

A crystal defect 微缺陷(microdefect) is any interruption in the repetitive nature of the unit cell crystal structure. Three general types of crystal defects in silicon: 1. 点缺陷 -Localized crystal defect at the atomic level 2. 位错-Displaced unit cells 3.层错 -Defects in crystal structure

Figure 4.18

31

硅单晶片参数对电子器件的影响

材料参数 对电子器件的影响 增加漏电流,降低少子寿命 影响双极增益 层错 增加漏电流,造成击穿 降低栅氧化层质量 金属杂质 增加漏电流, 降低栅氧化层质量 降低少子寿命,影响双极增益 电阻率 影响阈值电压,影响击穿电压 方向性 影响表面电荷,影响开启电压

12

Miller Indices of Crystal Planes

Z Z Z

Y X (100) X (110)

Y X (111)

Y

Figure 4.9

13

4.5 单晶硅的生长( Growth)

CZ (Czochralski 切克劳斯基)

CZ 拉单晶炉 Doping Impurity Control

Identifying Flats

P-type (111)

P-type (100)

N-type (111)

Figure 4.21

N-type (100)

36

常用的硅片

1.CMOS

P type (Boron doped) (100)晶向,电阻率: 25~50Ωcm, 浓度:1015cm-3

2. BJT

第四章 硅和硅片的制备

1