Xilinx FPGA全局时钟资源的使用方法

FPGA的时钟输入研究与实现

FPGA的时钟输入研究与实现摘要:本文以xilinx公司的7系列FPGA为例,对FPGA的输入时钟信号进行讲述并使用LVDS、LVPECL格式信号进行验证。

0引言FPGA常用于系统内接口转换、信号处理等,其中时钟作为FPGA工作的基本要素在设计时应注意其电平格式、信号速率等因素,而晶振、时钟管理芯片等输出信号格式多种多样,本文讲述了FPGA输入时钟的设计并对其进行验证。

1 时钟的电平格式用于FPGA的时钟常见的单端电平格式LVCOMS、LVTTL,差分电平格式有LVDS、LVPECL、CML等。

单端电平格式LVCOMS格式低电平约为0.35×VCCO以下,高电平约为0.65×VCC以上,xilinx公司7系列FPGA的VCCO常用值为1.2V、1.5V、1.8V、2.5V、3.3V;单端电平格式LVTTL低电平为0.8V以下,高电平为2V以上。

差分电平格式LVDS特点为低功耗、宽范围的共模电压,信号的驱动器内常为3.5mA电流源,接收器的输入阻抗很高,所以需在接收器处增加100欧姆的中断电阻,形成350mV的差分电压,接收器输入差分门限常为100mV以上。

差分电平格式LVPECL特点为速率高、功耗大、驱动能力强,在使用时需设计匹配电路进行使用,电路相对复杂。

差分电平格式CML特点为速率高(与LVPECL相当)、内部集成了终端匹配电路,电路简单。

2 FPGA的输入要求xilinx公司7系列FPGA的时钟输入支持单端输入也支持差分输入。

在使用单端输入时,建议通过MRCC的P端引脚输入作为全局时钟,输入时钟的电平与bank的VCCO电源匹配,单端输入电平要求如表1所示。

表1 单端输入时钟电平要求差分时钟要求的格式为LVDS格式,7系列中有HR与HP两种bank,在使用时应注意其bank的电压与约束的电平匹配,其时钟输入要求如表2所示。

当bank电压不匹配时,仅输入的信号可以约束为LVDS_25或LVDS,此时需在软件中关闭终端电阻并且在外部增加100欧姆终端电阻。

BUFG和IBUFG的使用教案资料

B U F G和I B U F G的使用BUFG,IBUFG的使用目前,大型设计一般推荐使用同步时序电路。

同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。

为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。

为了适应复杂设计的需要,Xilinx的FPGA中集成的专用时钟资源与数字延迟锁相环(DLL)的数目不断增加,最新的Virtex II器件最多可以提供16个全局时钟输入端口和8个数字时钟管理模块(DCM)。

与全局时钟资源相关的原语常用的与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等,如图1所示。

1. IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。

所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。

IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和 SSTL等多种格式的IO标准。

G 单2. IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。

IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS等多种格式的IO标准。

3. BUFG是全局缓冲,它的输入是IBUFG的输出,BUFG的输出到达FPGA 内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。

4. BUFGCE是带有时钟使能端的全局缓冲。

fpga数字时钟课程设计

fpga数字时钟课程设计FPGA数字时钟课程设计随着科技的不断发展,数字时钟已经成为现代人生活中必不可少的物品。

数字时钟的准确性和便捷性吸引了越来越多的人使用。

而现在,我们可以通过FPGA数字时钟课程设计来实现一个高精度的数字时钟。

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以通过编程实现各种不同的功能。

数字时钟的实现也可以通过FPGA来完成。

在FPGA数字时钟课程设计中,我们需要先确定时钟的基础部分。

时钟的基础部分由时钟信号产生器、时钟分频器、时钟计数器和时钟显示器组成。

时钟信号产生器需要产生一个稳定的时钟信号,以供后续的计数器和分频器使用。

我们可以通过FPGA中的时钟模块来产生一个稳定的时钟信号。

接下来,时钟分频器需要将时钟信号分频,使得计数器可以进行精确的计数。

分频器的分频系数可以通过FPGA中的数码开关进行设置。

然后,时钟计数器需要根据分频器的设定进行精确的计数。

计数器的计数值可以通过FPGA中的计数器模块进行设置。

时钟显示器需要将计数器的计数值进行显示。

我们可以通过FPGA 中的数码管模块来实现时钟的显示功能。

除了基础部分,我们还可以通过添加更多的功能来完善数字时钟。

例如,我们可以添加闹钟功能、日期显示功能等,以增加数字时钟的实用性。

在FPGA数字时钟课程设计中,我们可以使用VHDL(VHSIC Hardware Description Language)语言进行编程。

VHDL是一种硬件描述语言,可以用于FPGA和ASIC的设计。

通过编写VHDL 程序,我们可以实现数字时钟的各种功能。

FPGA数字时钟课程设计是一个非常有趣和实用的课程项目。

通过这个项目,我们可以深入了解数字时钟的工作原理,熟悉FPGA的编程方法,同时也可以锻炼自己的编程能力。

fpga 时钟切换 方法

fpga 时钟切换方法As an FPGA engineer, one of the most critical aspects of designing a system is managing the clock signals. 作为FPGA工程师,系统设计中最关键的一个方面就是时钟信号的管理。

There are various methods for clock switching in FPGA designs. 在FPGA设计中有多种时钟切换的方法。

One commonly used method is clock muxing, which involves using multiplexers to select between different clock sources based on certain conditions. 其中一个常用的方法是时钟多路复用,它需要使用多路复用器根据特定条件来选择不同的时钟源。

Another method is the use of phase-locked loops (PLLs) to generate clock signals with different frequencies. 另一种方法是使用锁相环(PLL)来生成不同频率的时钟信号。

In some cases, clock signals may need to be synchronized across different clock domains, which requires careful consideration of clockdomain crossing techniques. 在某些情况下,时钟信号可能需要在不同的时钟域之间进行同步,这就需要仔细考虑时钟域交叉技术。

When implementing clock switching, it is crucial to consider factors such as clock skew, jitter, and timing constraints to ensure proper functioning of the design. 在实现时钟切换时,必须考虑时钟偏移、抖动和时序约束等因素,以确保设计的正常工作。

基于Xilinx FPGA的时钟管理设计与实现

O 引

一

言

率合 成器 ( F ) 数 字 移 相 器 ( S 和 数 字 频 谱 扩 展 器 D S、 DP )

( S DS )。

个 复 杂 电 子 系 统 , 部 需 要 多 个 时 钟 源 , 且 各 时 内 并

DL L主要 由 1 延 时 线 和控 制 逻 辑组 成 。延 时 线对 个 时钟输入 端 C KI L N产 生 1个 延 时 , 钟 分 布 网线将 该 时 时 钟 分配到 期 间 内的 各个 寄存 器 和 时钟 反 馈 端 C KF 控 L B;

u e n t e p a t a e eo me to PGA y at rn h i h a a tr s d i h r c i ld v l p n fF c b l ig t e r tp r me e . e g

Ke wo d y r s: f e u nc u tplc t0 fe e y d vso FPG A r q e y m li ia i n;r qu nc i iin;

De i n a d i plm e t to fc o k m a a e e t sg n m e n a i n o l c n g m n

b s d O1Xii x FPGA ae 1 ln

Fe g Ya io Li n h n nba u Xi gc un

电

子

测

量

技

术

第 3 3卷 第 1 O期

21 0 0年 1 O月

ELECTR ( N I ) C M EA SU R EM EN T TEC H N 0 L0 C Y

基 于 Xin P A 的 时钟 管 理 设 计 与 实 现 l京 航 空 航 天 大 学 电子 信 息 工程 学院 北 京 1 0 8 ) 0 0 3

fpGa_CPLD设计工具xilinxISE使用详解

1.第一章:FPGA/CPLD简介●FPGA一般是基于SRAM工艺的,其基于可编程逻辑单元通常是由查找表(LUT,look up table)和寄存器(register)组成。

其中内部的查找表通常是4输入的,查找表一般完成纯组合逻辑功能;●Xilinx可编程逻辑单元叫做slice,它由上下两部分组成,每部分都由一个register加上一个LUT组成,被称为LC(logic cell,逻辑单元),两个LC之间有一些共用逻辑,可以完成LC之间的配合工作与级连;●Altera可编程逻辑单元叫做LE(Logic Element,逻辑单元),由一个register加上一个LUT构成;Lattice的底层逻辑单元叫做PFU(programmable Function unit,可编程功能单元),它由8个LUT和9个register组成。

●Ram和dpram/spram/伪双口RAM,CAM(content addressable memory)。

Fpga中其实没有专业的rom硬件资源,实现ROM是对RAM赋初置,并且保存此初值●CAM,即内容地址储存器,在其每个存储单元都包含了一个内嵌的比较逻辑,写入cam的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所以内部数据的地址。

总结:RAM是一种根据地址读/写数据的存储单元;而CAM 和RAM恰恰相反,它返回的是与端口数据相匹配的内部地址。

使用很广,比如路由器中的地址交换表等等●Xilinx块ram大小是4kbit和18kbit两种结构。

Lattice块ram是9kbit●分布式ram适合用于多块小容量的ram的设计;●Dll(delay-locked loop)延迟锁定回环或者pll(phase locked loop)锁相环,可以用以完成时钟的高精度,地抖动的倍频/分频/占空比调整/移相等功能。

Xilinx主要集成的是DLL,叫做CLKDLL,在高端的FPGA中,CLKDLL的增强型模块为DCM (digital clock manager,数字时钟管理模块)。

Xilinx FPGA 设计中的跨时钟域问题

浅谈XLINX FPGA设计中跨时钟域的同步设计问题摘要本文介绍了FPGA设计中的同步设计原则并对FPG A设计中的触发器亚稳态问题进行了阐述本文通过具体的设计实例论证了跨时钟域同步处理的必要性并介绍了一种实现跨时钟域同步处理的方法和其具体电路关键字同步设计异步设计触发器亚稳态时序稳定一同步设计的原则尽量使用同步电路避免使用异步电路这句话是电路设计的几个原则之一同异步设计相比同步设计设计出来的电路更稳定可靠在XILINX FPGA设计中时常有设计人员遇到如下类似的问题设计的电路升级困难可移植性差也就是说一些原本工作正常的电路移植到高端的FPGA中就根本工作不起来了设计的电路一致性差同一电路设计每次布线后工作的结果不同设计的电路时序仿真正常但实际电路上却工作不起来设计的电路极易受毛刺的干扰通常这些类似的问题都于电路的异步设计有关二亚稳态图1 触发器的亚稳态示意图对于触发器当时钟沿到来时其输入要求是稳定的这时其输出也是稳定的但假如时钟沿到来时其输入也正在变化即翻转这时触发器会瞬时进入亚稳态通常触发器对输入信号都有一个建立时间的要求也即setup时间当这一建立时间得不到满足时触发器也会进入瞬时亚稳态如图1通常触发器即使进入亚稳态也会很快进入稳态但其输出值是不定的这有可能对使我们设计的FPGA模块尤其是哪些有复杂状态机的模块产生错误的逻辑对于亚稳态问题我们还应明白亚稳态问题并非指输出结果数据的不确定性而是指输出变化的时序不确定性遵循同步设计的原则有助于解决亚稳态问题使我们设计出稳定可靠的电路模块对于单时钟系统我们可以很方便地设计出稳定易于设计及仿真的同步单一时钟系统但在电信和数据通讯领域中我们设计的系统中往往具有多个时钟往往需要将数据或时序由一个时钟域传到另一个时钟域这类设计的难点在于实现不同时钟域之间数据和时序变化的稳定可靠地传递采用经验证的设计技术可以实现跨时钟域的同步设计进而设计出可靠工作的电路三跨时钟域的异步设计案例本人曾经设计过如下几个模块这些模块中的几个子模块分别工作在各自的时钟域中但在他们之间有着数据和时序的传递在设计这些模块的初始时并没有考虑到跨时钟域时序和数据传递的特殊性使得在系统上使用这些模块时出现过一些较为棘手的问题现把它们列举出来供大家研究模块一名称:芯片配置模块模块功能从平行口接收从PC 机下传的命令和参数产生相应的控制时序完成单板上芯片的配置模块结构框图图2 同步处理前芯片配置模块结构框图各子模块简介模块A 实现同PC 的平行接口PC 机控制程序通过操作并行口各个引脚把各个参数信息如数据地址信息传递到参数控制总线上并且发出相应的命令如start, write 等命令启动下层模块模块B 是一个状态机clk 是状态机的主时钟模块B 根据模块A 传来的命令启动相应的状态机完成从参数传递总线上获取参数信息或产生相应的配置时序完成芯片的正确配置在上图中模块A 中各寄存器都受控于并行口各引脚的状态它们在并行口引脚中stroble 引脚的上跳沿发生状态的迁移可以说stroble 引脚是模块A 的主时钟信号由上分析得模块A 和模块B 分属于两不同的时钟域时钟域A 和时钟域B中时钟域A 的主时钟为stroble, 时钟域B 的主时钟为clk 两时钟域的主时钟stroble 和clk 是不相关的它们之间的信号就为跨时钟域A 和时钟域B 之间的信号线其中write 信号线,start 信号线及回馈握手信号线用于实现控制时序的传递而参数传递总线用于实现数据的传递在如上的设计中没有对跨时钟域的时序控制线进行同步处理在系统使用此模块时出现如下的问题Parrel port with PCPC机上芯片配置命令并不能总是成功的启动模块B 中相应的状态机也即PC机上芯片配置命令并不能总是成功地实现芯片的正确配置芯片配置时序的不稳定性故障的偶然性故障的不可重复性模块二名称:突发调制器模块模块功能完成数据的突发调制模块结构框图图3 同步处理前突发调制器模块框图各子模块简介模块A 为突发调制器主控模块它的主时钟为CLKA它利用CLKA定时产生周期的Send_data信号去启动模块B中的状态机模块B为突发调制器时序控制模块它的主时钟是从专用调制器芯片送来的TXBITCLK时钟信号模块B根据模块A的触发信号启动相应的状态机产生相应的调制器控制时序专用调制芯片中的DPLL(数字锁相环)根据相应的设置参数以CLKB为参考时钟产生TXBITCLK时钟信号上图中R1R2为跳接电阻通过R1R2不同的焊剂方式可以改变CLKB时钟信号的时钟源在如上的设计中没有对跨时钟域的时序控制进行同步处理在系统使用此模块时出现如下的问题在R1短接R2断开情况下CLKA时钟信号和CLKB时钟信号共用一个时钟源晶体A,上述模块工作正常稳定在R1断开R2短接情况下CLKA 时钟信号的时钟源为晶体A CLKB 时钟信号的时钟源为晶体B 晶体A 和B 是两个独立不相关的晶体这时模块A 和模块B 工作于不同的时钟域(时钟域A 和时钟域B) 它们之间的信号就为跨时钟域A 和时钟域B 之间的信号线Send_data 信号和回馈握手信号线用于实现两时钟域之间控制时序的传递此时上述模块工作很不稳定模块B 中的状态机经常进入一种未知状态不能产生正确的调制器控制时序四 跨时钟域的同步设计的方法经对上述案例仔细地仿真和深入分析后笔者发现作成上述两模块工作不稳定的主要原因是没有按照同步设计的原则对跨时钟域的时序控制信号进行同步处理可以有好几种电路用于实现跨时钟域的时序控制信号的同步处理下面的电路模块Asy_syc 可以用于跨时钟域时序控制信号的同步处理Asy_inSyc_clkSyc_outTime periphery图4 Asy_syc 电路原理图上述电路的时序仿真图如下:图5 Asy_syc 时序仿真图由时序仿真图可以看出主时钟Syc_clk 的异步输入信号Asy_in 经该电路后输出同步于主时钟Syc_clk 的Syc_out 信号, 从而实现了异步信号的同步处理按照同步设计原则利用Asy_syc 模块对上述模块二(突发调制器模块)中跨时钟域的信号线Send_data 进行同步处理同步处理模块示意图如图6经实际电路验证得: 同步处理后突发调制器模块运行可靠稳定同样按同样的处理方式对上述模块一(芯片配置模块) 中跨时钟域的信号线进行同步处理经实际电路验证得: 同步处理后,芯片配置模块模块运行可靠稳定图6 同步处理后突发调制器模块框图五总结同步处理模块Asy_syc是一个很好的模块笔者用它和其它的简单模块实现了如下的功能:1. 上沿同步2. 脉冲同步3. 异步系统同步解决了好多Xilinx FPGA设计中棘手的问题参考资料XILINX FUNDATION3.1 TRAINING跨越异步时钟边界传输数据的解决方案 Peter Alfke。

Xilinx约束学习笔记(二)——定义时钟

Xilinx约束学习笔记(⼆)——定义时钟2. 定义时钟2.1 关于时钟为了获得最佳精度路径覆盖信息,必须正确定义时钟。

时钟要定义在时钟树的根 pin 或 port 上,称为 source point。

时钟的边缘应该由周期和波形进⾏组合描述。

周期使⽤纳秒做为单位进⾏定义。

它对应于波形重复的时间。

波形是⼀系列的上升沿和下降沿绝对时间列表,单位为纳秒,并且所有时间在⼀个时钟周期内。

列表必须包含偶数个值。

第⼀个值始终对应于第⼀个上升边缘。

如果没有指定波形,波形的默认占空⽐为 50%,相移为 0。

2.1.1 传播时钟周期和波形属性只展现出了时钟的理想特性。

当时钟进⼊ FPGA 并通过时钟树传播时,时钟边沿被延缓,并受噪声和硬件⾏为引影响。

这些特性称为时钟⽹络延迟和时钟不确定性。

时钟的不确定性包括:时钟抖动(clock jitter)相位错误⽤户指定添加的不确定性默认情况下,Vivado 在做时序分析时,始终将时钟视为传播时钟,即⾮理想时钟,以此提供准确的余量值,其中包括时钟树插⼊延迟和不确定性。

2.1.2 专⽤硬件资源FPGA 有⼤量专⽤的时钟管脚,这个管脚可以专门⽤来做时钟的输⼊。

FPGA 内部包含有 MMCM、PLL 和 BUR 之类的时钟资源。

2.2 基准时钟(Primary Clock)基准时钟是通过 FPGA 输⼊端⼝或千兆收发器输出引脚(例如,恢复时钟)进⼊设计的时钟。

基准时钟只能通过 create_clock 指令进⾏定义。

(为什么是千兆收发器?下⾯的话应该可以解释,7 系列的 GT 恢复时钟不能⾃动推导,必须⼿动定义。

⽽ US 和 USP 系列的可以⾃动推导,不需要⼈为定义)Primary clocks must be defined on a gigabit transceiver output only for Xilinx® 7 series FPGAs. For UltraScale and UltraScale+™ devices, the timer automatically derives clocks on the GT output ports.基准时钟必须附加到⽹表对象。

FPGA全局时钟资源相关原语及其使用(BUFG)

FPGA全局时钟资源相关原语及其使用FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。

为了适应复杂设计的需要,Xilinx的FPGA中集成的专用时钟资源与数字延迟锁相环(DLL)的数目不断增加,最新的Virtex II器件最多可以提供16个全局时钟输入端口和8个数字时钟管理模块(DCM)。

与全局时钟资源相关的原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM 等。

1. IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。

所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。

IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX 和SSTL等多种格式的IO标准。

2. IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。

IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL 和ULVDS等多种格式的IO标准。

3. BUFG是全局缓冲,它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。

4. BUFGCE是带有时钟使能端的全局缓冲。

它有一个输入I、一个使能端CE和一个输出端O。

只有当BUFGCE的使能端CE有效(高电平)时,BUFGCE才有输出。

5. BUFGMUX是全局时钟选择缓冲,它有I0和I1两个输入,一个控制端S,一个输出端O。

当S为低电平时输出时钟为I0,反之为I1。

需要指出的是BUFGMUX的应用十分灵活,I0和I1两个输入时钟甚至可以为异步关系。

Vivado个人学习笔记001_利用clocking

Vivado个⼈学习笔记001_利⽤clocking wizard与计数器完成较⾼精度的分频个⼈原创声明:本⽂为本⼈原创⽂章,未经本⼈允许请勿⽆端转载,转载请注明来源。

由于实际需求,⼯程中经常需要⼀些精度较⾼的频率的时钟,⽐如115.2khz等。

⽽我们初次接触fpga时看到的分频⽅法,也就是最基本的计数分频,⼀般是只有整数倍的分频。

那么如何实现⼀个实际输出波形较为规则的、精度较⾼的时钟信号呢?⾸先先声明我个⼈使⽤的软硬件平台。

由于现在还处于初学阶段,硬件上使⽤的是DIGILENT公司的Arty™ FPGA Board Reference Manual,其使⽤的芯⽚是赛灵思的7a系的Xilinx Artix-35T FPGA (xc7a35ticsg324-1L)。

下⾯是官⽅⽂档的介绍与个⼈实际拍摄的照⽚。

软件则是使⽤的Xilinx的官⽅平台Vivado 2015.4.接下来就步⼊正题。

计数分频原理在各个教材与⽹站上都有详细的说明,代码也有很多现成的,这⾥就不多做赘述。

下⾯介绍⼀下本⽂的重点,IP核clocking wizard(CLK_WIZ).⾸先,在vivado主界⾯左侧的Project Manager⼀栏中打开IP Catalog,搜索clk ,即可找到clocking wizard这个ip核,双击即可点开配置该ip核。

在clocking options中,可以选择MMCM与PLL。

MMCM是混合时钟管理器,PLL即锁相环Phase Locked Loop。

PLL的原理百度⼀下就可以搜到,⾄于这两者的关系,MMCM⼀般来说是包含PLL在内的拥有更多功能的⼀个东西,具体的内容就要看datasheet了,本⼈也没有仔细看过,所以如有不严谨的地⽅请多包涵。

在Input Clock Information中,可以选择输⼊时钟,可以使⽤多个输⼊。

其他的功能如有需求再作调整,本⼈在此就不做过多介绍了。

fpga 设计中对时钟的使用

fpga 设计中对时钟的使用FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,可以随意定制电路,称为“现场可编程门阵列”。

FPGA极大地促进了数字设计的发展,主要原因是它们具有高度灵活性和可编程性,在快速原型开发和快速市场推出方面具有重要作用。

时钟在FPGA设计中扮演重要的角色。

本文将介绍FPGA设计中时钟的使用。

一、时钟的概念和应用时钟通常被定义为一个周期性的信号,在数字电路中用于同步各个电路元素的运行。

FPGA设计中,时钟是同步时序逻辑电路的核心,因为它是控制数字逻辑电路元素的节拍。

当时钟沿上升或下降到达某一特定的时刻时,整个系统将同步更新到该时刻。

在FPGA设计中时钟决定了操作的速度,这个速度主要取决于FPGA芯片本身的异步延迟,不受时钟频率控制。

可以通过增加时钟频率来提高FPGA系统的速度,但也会造成增加功耗和热量。

时钟频率是由同步电路的最慢电路决定的。

如果时钟频率超过了最慢的同步电路,就会出现数据丢失或不稳定的情况,因此时钟频率需要在同步电路的最慢电路范围内进行选择。

时钟的应用包括以下几个方面:1.同步器:时钟作为同步器,在FPGA的硬件代码中用于实现逻辑延迟。

2.复位电路:时钟也可以用于生成复位信号,当时钟初次上升到达时,复位电路可以将系统重置为已知的状态。

3.频率分频:时钟信号可以通过分频器降低频率。

可以将一个高速时钟信号分裂成几个低速时钟信号,用于驱动各自的模块。

4. 数据采样模块:数据采样模块要求适当的时钟方式和时钟控制。

二、时钟对FPGA设计中的影响FPGA设计中时钟的正确使用对整个设计非常重要。

时钟频率的选择直接影响到FPGA芯片工作的稳定性和可靠性。

时钟信号的漏掉、翻转或者缺失将会导致逻辑分支的错误,从而影响到整个系统的正常运行。

为了保证时钟的稳定和可靠,一般采用以下方法:1.时钟源选择:FPGA芯片的时钟源需要选择稳定、精确的时钟源。

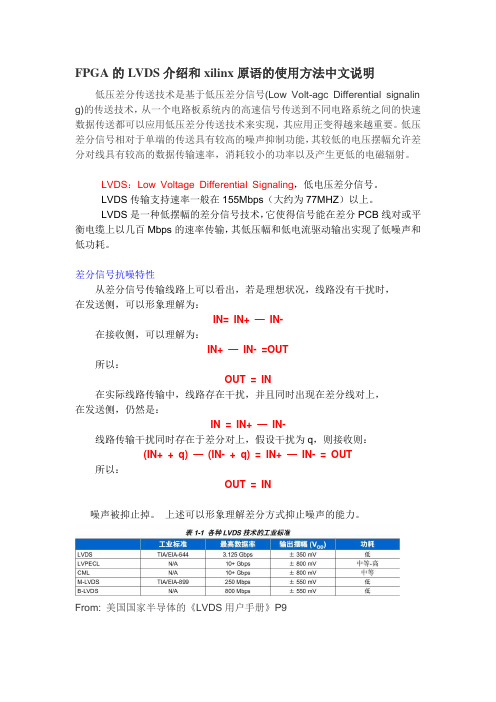

FPGA的LVDS介绍和xilinx原语的使用方法中文说明

FPGA的LVDS介绍和xilinx原语的使用方法中文说明低压差分传送技术是基于低压差分信号(Low Volt-agc Differential signalin g)的传送技术,从一个电路板系统内的高速信号传送到不同电路系统之间的快速数据传送都可以应用低压差分传送技术来实现,其应用正变得越来越重要。

低压差分信号相对于单端的传送具有较高的噪声抑制功能,其较低的电压摆幅允许差分对线具有较高的数据传输速率,消耗较小的功率以及产生更低的电磁辐射。

LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

差分信号抗噪特性从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:IN= IN+ —IN-在接收侧,可以理解为:IN+ —IN- =OUT所以:OUT = IN在实际线路传输中,线路存在干扰,并且同时出现在差分线对上,在发送侧,仍然是:IN = IN+ —IN-线路传输干扰同时存在于差分对上,假设干扰为q,则接收则:(IN+ + q) —(IN- + q) = IN+ —IN- = OUT 所以:OUT = IN噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。

From: 美国国家半导体的《LVDS用户手册》P9FPGA中的差分管脚为了适用于高速通讯的场合,现在的FPGA都提供了数目众多的LVDS接口。

如Spartan-3E系列FPGA提供了下列差分标准:LVDSBus LVDSmini-LVDSRSDSDifferential HSTL (1.8V, Types I and III)Differential SSTL (2.5V and 1.8V, Type I)2.5V LVPECL inputs所拥有的差分I/O管脚数目如下From:Spartan-3E FPGA Family:Complete Data Sheet p5I/O管脚的命名方式:From:Spartan-3E FPGA Family:Complete Data Sheet p164From:Spartan-3E FPGA Family:Complete Data Sheet p18 Spartan-3E系列FPGA器件差分I/O接口输入工作的特性参数:From:Spartan-3E FPGA Family:Complete Data Sheet p126 Spartan-3E系列FPGA器件差分I/O接口输出工作的特性参数:From:Spartan-3E FPGA Family:Complete Data Sheet p127Xilinx公司差分原语的使用(原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C+ +中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。

Spartan6的时钟资源使用总结

Spartan6的时钟资源使用总结使用XILINX公司的Spartan6芯片,也是最近半年的事情。

该芯片由于上市时间不长,在使用该芯片的时候各位网友分享的心得也比较少;再加上第一次开发使用它,开发过程肯定会遇到很多很多棘手头疼的问题。

可以说Spartan6芯片的使用者对它是又爱又恨呐!1.Spartan6芯片的时钟资源,种类比较多,而且使用它的游戏规则也有不少变化。

XILINX 公司关于Spartan6芯片提供了一篇文档Xilinx UG382 Spartan-6 FPGA Clocking Resources User Guide ,里面有详细的说明和解析。

本文就是对该文进行浓缩,将几个关键问题用图表的方式重新解释一番。

1.弄清楚目前Spartan6提供哪些时钟资源和时钟BUFFER资源。

2.弄清楚各种时钟BUFFER 的输入输出情况。

这是最重要的,因为这些资源对信号从哪里来,到哪里去,给哪些对象使用是有硬性要求的。

下面一段是XILINX提供的关于各种时钟BUFFER使用规则。

一定要把这几句话弄懂。

原因首先是,它提供了时钟BUFFER的类型;其次,它定义各种时钟BUFFER的输入输出。

Understand the use of each clock buffer type and how they can work best for your design1. BUFG/BUFGMUX Global Clock; Clock of Fabric; legal support for IDDR2、ODDR2 clocking。

2. BUFH Increases number or global clock rouTIng resources; CMT outputs if BUFGs not used。

3. BUFIO2 High speed clocking of IOSERDES/IOLOGIC (without DCM/PLL); Dedicated rouTIng to DCM/PLL/BUFG。

XilinxFPGA配置clocking时钟动态相位输出

XilinxFPGA配置clocking时钟动态相位输出

开发平台基于Vivado2017.3,器件使⽤的是Kintex7。

先贴个时序图:

如何动态配置clocking输出时钟相位,⾸先在ip核设置界⾯,勾选Dynamic Phase Shift,在左侧接⼝总览⾥⾯可以看到多出来4个信号,psclk:⽤于相移控制信号的驱动时钟,psen:控制相位偏移的使能信号,psincdec:⽤于相位正负偏移的信号,1表⽰正向偏移,0表⽰负向偏移。

最后psdone是相位偏移完成标志信号。

权威的接⼝说明可以⾃⾏查阅xilinx 官⽅⼿册pg065。

标题

在第⼆页输出时钟最后勾选Use Fine PS,

标题

关注⼀下VCO的频率,⼀个psen⾼脉冲,输出相位偏移1/56个VCO周期。

标题

然后例化⼀下,写个testbench,我看clocking这个ip核的example中,psclk的频率设置的是100Mhz。

仿真使⽤的Vivado⾃带的仿真器,因为Modelsim仿真时,psdone信号死活不拉⾼,估计是有BUG。

仿真波形如下,⼀个psen,输出时钟相位偏移20ps。

刚好等于1/891Mhz/56

标题

标题。

FPGA的LVDS介绍和xilinx原语的使用方法中文说明

FPGA的LV DS介绍和x i linx原语的使用方法中文说明低压差分传送技术是基于低压差分信号(Low Volt-agc Differe ntialsignali ng)的传送技术,从一个电路板系统内的高速信号传送到不同电路系统之间的快速数据传送都可以应用低压差分传送技术来实现,其应用正变得越来越重要。

低压差分信号相对于单端的传送具有较高的噪声抑制功能,其较低的电压摆幅允许差分对线具有较高的数据传输速率,消耗较小的功率以及产生更低的电磁辐射。

LVDS:Low Voltage Differe ntialSignali ng,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MH Z)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

差分信号抗噪特性从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:IN= IN+ —IN-在接收侧,可以理解为:IN+ —IN- =OUT所以:OUT = IN在实际线路传输中,线路存在干扰,并且同时出现在差分线对上,在发送侧,仍然是:IN = IN+ —IN-线路传输干扰同时存在于差分对上,假设干扰为q,则接收则:(IN+ + q) —(IN- + q) = IN+ —IN- = OUT所以:OUT = IN噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。

From: 美国国家半导体的《LVDS用户手册》P9FPGA中的差分管脚为了适用于高速通讯的场合,现在的FPGA都提供了数目众多的LVDS接口。

如Spartan-3E系列FPG A提供了下列差分标准:LVDSBus LVDSmini-LVDSRSDSDiffere ntialHSTL (1.8V, Types I and III)Differe ntialSSTL (2.5V and 1.8V, Type I)2.5V LVPECLinputs所拥有的差分I/O管脚数目如下From:Spartan-3E FPGA Family:Complet e Data Sheet p5I/O管脚的命名方式:From:Spartan-3E FPGA Family:Complet e Data Sheet p164From:Spartan-3E FPGA Family:Complet e Data Sheet p18 Spartan-3E系列FPG A器件差分I/O接口输入工作的特性参数:From:Spartan-3E FPGA Family:Complet e Data Sheet p126 Spartan-3E系列FPG A器件差分I/O接口输出工作的特性参数:From:Spartan-3E FPGA Family:Complet e Data Sheet p127Xilinx公司差分原语的使用(原语,其英文名字为P rimiti ve,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilin x公司为用户提供的库函数,类似于C+ +中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。

fpga时钟相位

FPGA时钟相位1. 什么是FPGA时钟相位?在了解FPGA时钟相位之前,首先需要了解FPGA和时钟的基本概念。

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据用户的需求重新配置内部的逻辑电路。

它由可编程逻辑单元(PLU)和可编程互连资源(PIR)组成,可以用于实现各种数字逻辑电路。

时钟是FPGA中非常重要的一个概念,它是FPGA内部逻辑电路运行的基准,用于同步各个逻辑单元的操作。

时钟信号的频率决定了FPGA的工作速度和性能。

FPGA时钟相位是指时钟信号的相对时间偏移量。

在FPGA中,时钟信号会被分发到各个逻辑单元,时钟相位的不同会导致不同逻辑单元在不同时间点上进行操作,从而影响FPGA的功能和性能。

2. FPGA时钟相位的重要性FPGA时钟相位对于FPGA的功能和性能至关重要。

合理地控制时钟相位可以避免时序问题,提高FPGA的工作稳定性和性能。

2.1 时序问题时序问题是指在FPGA中由于时钟相位不正确而导致的电路操作错误。

当时钟信号到达逻辑单元时,逻辑单元的输入信号必须满足一定的时间要求,否则逻辑单元可能无法正确地完成操作。

时序问题主要包括以下几种情况:•setup violation:逻辑单元的输入信号在时钟上升沿之前就发生了变化,导致逻辑单元无法正确读取输入信号。

•hold violation:逻辑单元的输入信号在时钟上升沿之后才发生变化,导致逻辑单元在时钟上升沿之后仍然读取上一时钟周期的输入信号。

•clock skew:时钟信号在传输过程中由于电路延迟不均匀而导致的相位差异,可能导致时序问题。

2.2 时钟频率和性能FPGA的时钟频率决定了其工作速度和性能。

时钟频率越高,FPGA的工作速度越快,性能越好。

然而,时钟频率的提高也会增加时序问题的可能性。

合理地控制时钟相位可以提高FPGA的时钟频率和性能,同时确保电路的正确运行。

3. FPGA时钟相位的调整方法FPGA时钟相位的调整方法主要有以下几种:3.1 时钟分频时钟分频是通过改变时钟信号的频率来调整时钟相位的一种方法。

xilinx 跨时钟域设计 概述及解释说明

xilinx 跨时钟域设计概述及解释说明1. 引言:1.1 概述跨时钟域设计是现代电路设计中一个重要且复杂的问题。

在集成电路中,不同的模块可能会使用不同频率的时钟信号进行操作,这就导致了时钟信号之间存在着不同的域。

在进行数据传输或者协同工作时,跨越不同时钟域之间的数据传输问题变得非常重要。

1.2 文章结构本文将首先介绍跨时钟域设计的概念和相关背景知识。

接下来,我们将详细讨论为什么需要对时钟域进行划分以及Xilinx跨时钟域设计的意义。

然后,我们将介绍跨时钟域设计的原理与方法,包括同步与异步信号传输方式、锁存器与触发器的使用注意事项以及时序约束设置与优化策略。

此外,我们还会提供一些实际案例来演示Xilinx跨时钟域设计的实践应用和效果展示。

最后,我们将总结文章,并提出对于跨时钟域设计在Xilinx器件中应用前景的展望。

1.3 目的本文的目标是为读者提供关于Xilinx跨时钟域设计相关知识和技术方案,并通过实例和案例展示,帮助读者更好地理解并应用这些技术。

同时,我们也希望引起读者对跨时钟域设计的重视,并认识到其在现代电路设计中的重要性和必要性。

通过本文的阅读,读者将能够掌握Xilinx跨时钟域设计的基本原理与方法,并应用于实际工程项目中,提高电路的可靠性和性能。

2. 跨时钟域设计概述:2.1 什么是时钟域:时钟域是指由一个主时钟信号驱动的一组逻辑电路。

在数字电路设计中,系统通常包含多个时钟域,每个时钟域都有独立的主时钟信号。

由于不同时钟域之间存在着频率和相位差异,因此跨越不同时钟域的信号传输需要特殊的设计策略和技术支持。

2.2 时钟域划分的必要性:在复杂的数字系统中,为了提高系统性能和可靠性,常常需要将整个系统划分为多个独立的时钟域。

这种划分可以使各模块按照不同的时间精度进行操作,并且能够减少信号互联、功耗消耗以及故障引入等问题。

同时,通过合理地划分和管理时钟域,能够降低系统开发复杂度,并确保数据在稳定状态下进行正确传输。

FPGA DCM使用详解

FPGA DCM使用详解DCM(Digital Clock Manager)即基础时钟管理模块,是基于Xilinx的FPGA普遍采用的DLL(Delay Lock Loop)模块,在时钟管理与控制方面,DCM功能更加强大,使用更加灵活。

一、DCM主要功能1.分频倍频:DCM可以将输入时钟进行multiply或者divide,从而得到新的输出时钟。

2.去skew:DCM还可以消除clock的skew,所谓skew就是由于传输引起的同一时钟到达不同地点的延迟差。

3.相移:DCM还可以实现对输入时钟的相移输出,这个相移一般是时钟周期的一个分数。

4.全局时钟:DCM和FPGA内部的全局时钟分配网络紧密结合,因此性能优异。

5.电平转换:通过DCM,可以输出不同电平标准的时钟。

DCM的特点与能力(Spartan-3系列为例)数量:4DCM/FPGA(也有例外)应该够用了数字频率综合器输入(CLKIN):1-280MHz延迟锁相环输入(CLKIN):18-280MHz时钟输入源(CLKIN):1)Global buffer input pad2)Global buffer output3)General-purpose I/O(no deskew)4)Internal logic(no deskew)最后两个分别是外部的普通IO口和内部逻辑,没有deskew,所以时钟质量不会很好。

频率综合器输出(CLKFX、CLKFX180):是CLKIN的M/D倍,其中M=2..32D=1..32这样看来最大能倍频32倍,最小能16分频。

时钟dividor输出(CLKDV):是CLKIN的下列分频1.5,2,2.5,3,3.5,4,4.5,5,5.5,6,6.5,7,7.5,8,9,10,11,12,13,14,15,or16由此可见,最大的分频也是16,不过能支持半分频,比用频率综合器方便。

倍频输出(CLK2X、CLK2X180):CLKIN的2倍频时钟conditioning、占空比调整:这个对所有时钟输出都施加,占空比为50%。

fpga 相邻bank参考时钟复用

fpga 相邻bank参考时钟复用

在 Xilinx 的7系列FPGA中,每个 I/O Bank 包含支持时钟的输入引脚,将用户时钟带到7系列FPGA时钟路由资源上。

与专用时钟缓冲器一起,时钟输入管脚将用户时钟引入到以下位置:

- 器件相同上/下半部分的全局时钟线;

- 相同 I/O Bank 和垂直相邻的 I/O Bank 的时钟线;

- 相同时钟区域和垂直相邻的时钟区域的区域时钟线;

- 同一时钟区域内的 CMT 和有限制的情况下的垂直相邻的时钟区域。

每个7系列FPGA都有区域时钟树和I/O时钟树,可以为一个时钟区域内对所有时序资源提供时钟。

每个器件还具有多时钟区域缓冲器(BUFMR),允许区域和I/O时钟跨越最多三个垂直相邻的时钟区域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目前,大型设计一般推荐使用同步时序电路。

同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的要求。

为了满足同步时序设计的要求,一般在FPGA设计中采用全局时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。

FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。

为了适应复杂设计的需要,Xilinx的FPGA 中集成的专用时钟资源与数字延迟锁相环(DLL)的数目不断增加,最新的Virtex II器件最多可以提供16个全局时钟输入端口和8个数字时钟管理模块(DCM)。

与全局时钟资源相关的原语常用的与全局时钟资源相关的Xilinx器件原语包括:IBUFG、IBUFGDS、BUFG、BUFGP、BUFGCE、BUFGMUX、BUFGDLL和DCM等,如图1所示。

1. IBUFG即输入全局缓冲,是与专用全局时钟输入管脚相连接的首级全局缓冲。

所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错。

IBUFG支持AGP、CTT、GTL、GTLP、HSTL、LVCMOS、LVDCI、LVDS、LVPECL、LVTTL、PCI、PCIX和SSTL等多种格式的IO标准。

2. IBUFGDS是IBUFG的差分形式,当信号从一对差分全局时钟管脚输入时,必须使用IBUFGDS作为全局时钟输入缓冲。

IBUFG支持BLVDS、LDT、LVDSEXT、LVDS、LVPECL和ULVDS等多种格式的IO标准。

3. BUFG是全局缓冲,它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。

4. BUFGCE是带有时钟使能端的全局缓冲。

它有一个输入I、一个使能端CE和一个输出端O。

只有当BUFGCE的使能端CE有效(高电平)时,BUFGCE才有输出。

5. BUFGMUX是全局时钟选择缓冲,它有I0和I1两个输入,一个控制端S,一个输出端O。

当S为低电平时输出时钟为I0,反之为I1。

需要指出的是BUFGMUX的应用十分灵活,I0和I1两个输入时钟甚至可以为异步关系。

6. BUFGP相当于IBUG加上BUFG。

7. BUFGDLL是全局缓冲延迟锁相环,相当于BUFG与DLL的结合。

BUFGDLL在早期设计中经常使用,用以完成全局时钟的同步和驱动等功能。

随着数字时钟管理单元(DCM)的日益完善,目前BUFGDLL 的应用已经逐渐被DCM所取代。

(Q08. DCM即数字时钟管理单元,主要完成时钟的同步、移相、分频、倍频和去抖动等。

DCM与全局时钟有着密不可分的联系,为了达到最小的延迟和抖动,几乎所有的DCM 应用都要使用全局缓冲资源。

DCM可以用Xilinx ISE软件中的Architecture Wizard直接生成。

全局时钟资源的使用方法全局时钟资源的使用方法(五种)

1:IBUFG + BUFG的使用方法:IBUFG后面连接BUFG的方法是最基本的全局时钟资源使用方法,由于IBUFG组合BUFG相当于BUFGP,所以在这种使用方法也称为BUFGP方法。

2. IBUFGDS + BUFG的使用方法:(C8t0a8U u0当输入时钟信号为差分信号时,需要使用IBUFGDS 代替IBUFG。

3. IBUFG + DCM + BUFG的使用方法:这种使用方法最灵活,对全局时钟的控制更加有效。

通过DCM 模块不仅仅能对时钟进行同步、移相、分频和倍频等变换,而且可以使全局时钟的输出达到无抖动延迟。

4. Logic +BUFG的使用方法:BUFG不但可以驱动IBUFG的输出,还可以驱动其它普通信号的输出。

当某个信号(时钟、使能、快速路径)的扇出非常大,并且要求抖动延迟最小时,可以使用BUFG驱动该信号,使该信号利用全局时钟资源。

但需要注意的是,普通IO的输入或普通片内信号进入全局时钟布线层需要一个固有的延时,一般在10ns左右,即普通IO和普通片内信号从输入到BUFG输出有一个约10ns 左右的固有延时,但是BUFG的输出到片内所有单元(IOB、CLB、选择性块RAM)的延时可以忽略不计为“0”ns。

5.Logic + DCM + BUFG的使用方法:DCM同样也可以控制并变换普通时钟信号,即DCM的输入也可以是普通片内信号。

使用全局时钟资源的注意事项全局时钟资源必须满足的重要原则是:使用IBUFG 或IBUFGDS的充分必要条件是信号从专用全局时钟管脚输入。

换言之,当某个信号从全局时钟管脚输入,不论它是否为时钟信号,都必须使用IBUFG或IBUFGDS;如果对某个信号使用了IBUFG或IBUFGDS硬件原语,则这个信号必定是从全局时钟管脚输入的。

如果违反了这条原则,那么在布局布线时会报错。

这条规则的使用是由FPGA的内部结构决定的:IBUFG和IBUFGDS的输入端仅仅与芯片的专用全局时钟输入管脚有物理连接,与普通IO和其它内部CLB等没有物理连接。

另外,由于BUFGP相当于IBUFG和BUFG 的组合,所以BUFGP的使用也必须遵循上述的原则。

全局时钟资源的例化方法全局时钟资源的例化方法大致可分为两种:

一是在程序中直接例化全局时钟资源;

二是通过综合阶段约束或者实现阶段约束实现对全局时钟资源的使用;

第一种方法比较简单,用户只需按照前面讲述的5种全局时钟资源的基本使用方法编写代码或者绘制原理图即可。

第二方法是通过综合阶段约束或实现阶段的约束完成对全局时钟资源的调用,这种方法根据综合工具和布局布线工具的不同而异。