四种亮灯方式自由切换的跑马灯(用verilog hdl语言编写的跑马灯程序)

Verilog HDL 跑马灯电路

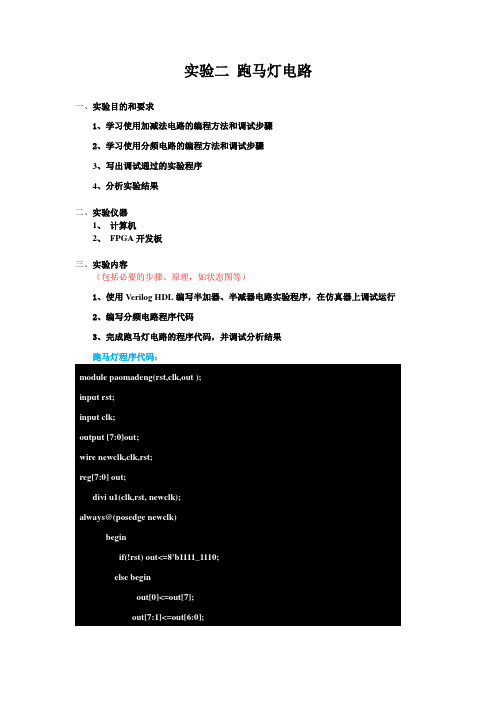

实验二跑马灯电路一、实验目的和要求1、学习使用加减法电路的编程方法和调试步骤2、学习使用分频电路的编程方法和调试步骤3、写出调试通过的实验程序4、分析实验结果二、实验仪器1、计算机2、FPGA开发板三、实验内容(包括必要的步骤、原理,如状态图等)1、使用Verilog HDL编写半加器、半减器电路实验程序,在仿真器上调试运行2、编写分频电路程序代码3、完成跑马灯电路的程序代码,并调试分析结果跑马灯程序代码:➢创建新的项目:[File]->[New Project] 选择器件属性➢创建源文件:[Project]->[New Source]->Verilog Module 输入跑马灯程序代码(上图所示)➢设计综合:使用ISE自带的综合工具XST 检查程序是否有误➢调试仿真波形仿真✓创建测试矢量波形文件:[Project]->[New Source]->Test Bench Waveform✓初始化输入波形✓启动ModelSim进行行为仿真➢设计实现✓启动设计实现:[Implement Design]✓可以在布局规划器(Floorplanner)中查看设计布局:[Place & Route]->[View/Edit Placed Design(Floorplanner)]➢下载调试将Verilog程序完成的电路配置到芯片里,并让芯片运行,观察并调试结果四、实验结果(说明实验的结果显示,最好包括波形和文字的)五、小结(对实验的心得,以及在试验中碰到的问题,你是如何解决这个问题的)➢ 进行软件仿真时要注意源程序代码的修改✓ if(count==25000000) 把数值设的小一点,比如令count=5,不然在短的时间内是看不到仿真效果的。

✓ if(!rst)begincount<=0;newclk<=0; end 在不能同时进行阻塞性赋值和非阻塞性赋值,不然程序会出现错误。

跑马灯设计 说明

基于VHDL的跑马灯设计说明1.设计思路:通过给定系统一个时钟,来控制8个LED灯的亮暗,灯亮暗的快慢可以通过改变给定的系统时钟频率。

2.功能分析:通过一个中间变量flag的状态来改变灯亮暗的方式,此次设计灯亮暗的方式总共有3种:(1)灯从左到右依次点亮,然后再从右到左依次熄灭;(2)灯从中间2个开始向两边亮,然后再从两边向中间熄灭;(3)灯按照7…4,3…0亮,其中最初7和3 亮,然后6和2亮…..以此类推,最后全部熄灭,进入下一轮循环。

3.模式选择:选择的为模式5。

4. 引脚锁定如下:灯对应实验板上从左到右为:light7,light6,……light0;Clk1对应实验板上clock05. 程序说明:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity light isport(clk1: in std_logic; --系统给的时钟light: buffer std_logic_vector(7 downto 0));end light;architecture behv of light isconstant len: integer:=7; --定义一个常量signal banner: std_logic:='0'; --中间信号signal clk,clk2: std_logic;beginclk<=(clk1 and banner) or (clk2 and not banner);process(clk1)beginif clk1'event and clk1='1' then --clk1是上升沿时,clk2取反clk2<=not clk2;end if;end process;process(clk)variable flag: bit_vector(2 downto 0):="000";--定义一个状态变量flag;beginif clk'event and clk='1' then --clk是上升沿if flag="000" then --flag为000时,从左到右点亮light<='1' & light(len downto 1); --并置成8位if light(1)='1' then --状态变量flag改变flag:="001";end if;elsif flag="001" then -- flag为001时,从右到左熄灭light<=light(len-1 downto 0) & '0';if light(6)='0' thenflag:="010";end if;elsif flag="010" then -- flag为010时,从中间向两边点亮light(len downto 4)<=light(len-1 downto 4)&'1';light(len-4 downto 0)<='1'&light(len-4 downto 1);if light(1)='1' thenflag:="011";end if;elsif flag="011" then -- flag为011时,从两边向中间熄灭light(len downto 4)<='0'&light(len downto 5);light(len-4 downto 0)<=light(len-5 downto 0)&'0';if light(2)='0' thenflag:="100";end if;elsif flag="100" then -- flag为100时,按7,3先亮,6,2再亮…..light(len downto 4)<='1'&light(len downto 5);light(len-4 downto 0)<='1'&light(len-4 downto 1);if light(1)='1' thenflag:="101";end if;elsif flag="101" then -- flag为101时,全部熄灭light<="00000000";flag:="110";elsif flag="110" then --进入下一轮循环banner<=not banner;flag:="000";end if;end if;end process;end behv;注:以上是自己通过看书和向同学请教后对程序的理解,可能有不当之处,望老师可以进行指出,十分感谢。

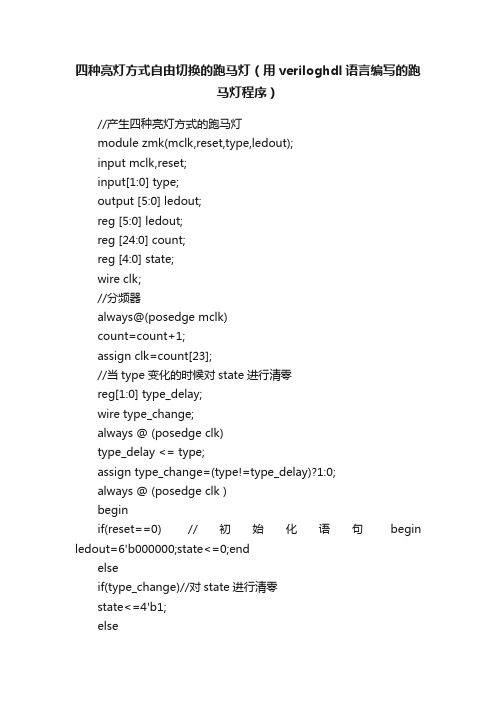

四种亮灯方式自由切换的跑马灯(用veriloghdl语言编写的跑马灯程序)

四种亮灯方式自由切换的跑马灯(用veriloghdl语言编写的跑马灯程序)//产生四种亮灯方式的跑马灯module zmk(mclk,reset,type,ledout);input mclk,reset;input[1:0] type;output [5:0] ledout;reg [5:0] ledout;reg [24:0] count;reg [4:0] state;wire clk;//分频器always@(posedge mclk)count=count+1;assign clk=count[23];//当type变化的时候对state进行清零reg[1:0] type_delay;wire type_change;always @ (posedge clk)type_delay <= type;assign type_change=(type!=type_delay)?1:0;always @ (posedge clk )beginif(reset==0) //初始化语句begin ledout=6'b000000;state<=0;endelseif(type_change)//对state进行清零state<=4'b1;elsebegincase(state)4'b0001:ledout=6'b011111;//第一个灯亮4'b0010:ledout=6'b101111;//第二个灯亮4'b0011:ledout=6'b110111;//第三个灯亮4'b0100:ledout=6'b111011;//第四个灯亮4'b0101:ledout=6'b111101;//第五个灯亮4'b0110:ledout=6'b111110;//第六个灯亮4'b0111:ledout=6'b111101;//第五个灯亮4'b1000:ledout=6'b111011;//第四个灯亮4'b1001:ledout=6'b110111;//第三个灯亮4'b1010:ledout=6'b101111;//第二个灯亮default :ledout=6'b000000;endcasestate=state+1; //计数器产生state的各种状态if(state==4'b1011)state=5'b00001;endelseif(type==2'b01)begincase(state)4'b0001:ledout=6'b101010;4'b0010:ledout=6'b010101;default :ledout=6'b000000;endcasestate=state+1;if(state==4'b0011)state=5'b00001;endelsebegincase(state)4'b0001:ledout=6'b110011;4'b0010:ledout=6'b101101;4'b0011:ledout=6'b011110;4'b0100:ledout=6'b101101; default :ledout=6'b000000; endcasestate=state+1;if(state==4'b0101)state=5'b00001; endelseif(type==2'b11)begincase(state)5'b00001:ledout=6'b111110;5'b00010:ledout=6'b111101;5'b00011:ledout=6'b111011;5'b00100:ledout=6'b110111;5'b00101:ledout=6'b101111;5'b00110:ledout=6'b011111;5'b00111:ledout=6'b001111;5'b01000:ledout=6'b010111;5'b01001:ledout=6'b011011;5'b01010:ledout=6'b011101;5'b01011:ledout=6'b011110;5'b01100:ledout=6'b011100;5'b01101:ledout=6'b011010;5'b01110:ledout=6'b010110;5'b01111:ledout=6'b001110;5'b10000:ledout=6'b000110;5'b10001:ledout=6'b001010;5'b10010:ledout=6'b001100;5'b10011:ledout=6'b001000;5'b10100:ledout=6'b000100;5'b10101:ledout=6'b001000;5'b10110:ledout=6'b000000;5'b10111:ledout=6'b111111;5'b11000:ledout=6'b000000;5'b11001:ledout=6'b111111;5'b11010:ledout=6'b000000;default :ledout=6'b000000;endcasestate=state+1;if(state==5'b11011)state=5'b00001; end endendmodule。

EDA实验 跑马灯

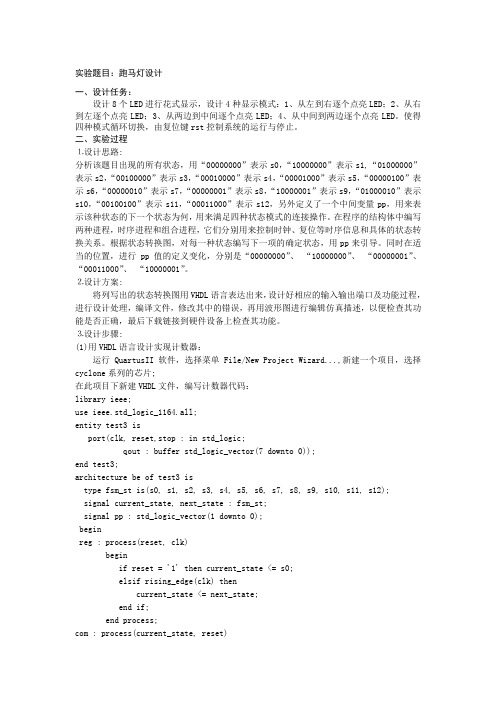

实验题目:跑马灯设计一、设计任务:设计8个LED进行花式显示,设计4种显示模式:1、从左到右逐个点亮LED;2、从右到左逐个点亮LED;3、从两边到中间逐个点亮LED;4、从中间到两边逐个点亮LED。

使得四种模式循环切换,由复位键rst控制系统的运行与停止。

二、实验过程⒈设计思路:分析该题目出现的所有状态,用“00000000”表示s0,“10000000”表示s1,“01000000”表示s2,“00100000”表示s3,“00010000”表示s4,“00001000”表示s5,“00000100”表示s6,“00000010”表示s7,“00000001”表示s8,“10000001”表示s9,“01000010”表示s10,“00100100”表示s11,“00011000”表示s12,另外定义了一个中间变量pp,用来表示该种状态的下一个状态为何,用来满足四种状态模式的连接操作。

在程序的结构体中编写两种进程,时序进程和组合进程,它们分别用来控制时钟、复位等时序信息和具体的状态转换关系。

根据状态转换图,对每一种状态编写下一项的确定状态,用pp来引导。

同时在适当的位置,进行pp值的定义变化,分别是“00000000”、“10000000”、“00000001”、“00011000”、“10000001”。

⒉设计方案:将列写出的状态转换图用VHDL语言表达出来,设计好相应的输入输出端口及功能过程,进行设计处理,编译文件,修改其中的错误,再用波形图进行编辑仿真描述,以便检查其功能是否正确,最后下载链接到硬件设备上检查其功能。

⒊设计步骤:(1)用VHDL语言设计实现计数器:运行QuartusII软件,选择菜单File/New Project Wizard...,新建一个项目,选择cyclone系列的芯片;在此项目下新建VHDL文件,编写计数器代码:library ieee;use ieee.std_logic_1164.all;entity test3 isport(clk, reset,stop : in std_logic;qout : buffer std_logic_vector(7 downto 0));end test3;architecture be of test3 istype fsm_st is(s0, s1, s2, s3, s4, s5, s6, s7, s8, s9, s10, s11, s12);signal current_state, next_state : fsm_st;signal pp : std_logic_vector(1 downto 0);beginreg : process(reset, clk)beginif reset = '1' then current_state <= s0;elsif rising_edge(clk) thencurrent_state <= next_state;end if;end process;com : process(current_state, reset)begincase current_state iswhen s0 => qout <= "00000000";if( reset ='0' and stop='0') then next_state <= s1; pp <= "00"; end if;when s1 => qout <= "10000000";if (pp = "00" and stop='0') then next_state <= s2;elsif (pp = "01" and stop='0')then next_state <= s9; pp <= "10"; end if;when s2 => qout <= "01000000";if (pp = "00" and stop='0')then next_state <= s3;elsif (pp = "01" and stop='0')then next_state <= s1;end if;when s3 => qout <= "00100000";if (pp = "00" and stop='0') then next_state <= s4;elsif (pp = "01" and stop='0')then next_state <= s2;end if;when s4 => qout <= "00010000";if (pp = "00" and stop='0')then next_state <= s5;elsif( pp = "01" and stop='0')then next_state <= s3;end if;when s5 => qout <= "00001000";if( pp = "00" and stop='0')then next_state <= s6;elsif (pp = "01" and stop='0')then next_state <= s4;end if;when s6 => qout <= "00000100";if (pp = "00" and stop='0')then next_state <= s7;elsif( pp = "01" and stop='0')then next_state <= s5;end if;when s7 => qout <= "00000010";if (pp = "00" and stop='0')then next_state <= s8;elsif (pp = "01" and stop='0')then next_state <= s6;end if;when s8 => qout <= "00000001";if (pp = "00" and stop='0')then next_state <= s7; pp <= "01"; end if;when s9 => qout <= "10000001";if (pp = "10" and stop='0')then next_state <= s10;elsif (pp = "11" and stop='0')then next_state <= s1; pp <= "00"; end if;when s10 => qout <= "01000010";if (pp = "10" and stop='0')then next_state <= s11;elsif (pp = "11" and stop='0')then next_state <= s9;end if;when s11 => qout <= "00100100";if (pp = "10" and stop='0')then next_state <= s12;elsif (pp = "11" and stop='0')then next_state <= s10;end if;when s12 => qout <= "00011000";if (pp = "10" and stop='0') then next_state <= s11; pp <= "11"; end if;when others => null;end case;end process;end be;(2)将此文件进行编译.(3)新建一个vector waveform form波形图文件,设置为波形仿真。

花式跑马灯汇编语言

花式跑马灯汇编语言一、引言花式跑马灯是一种以灯光为媒介,通过不同的变化方式展示出各种图案和文字的装饰性效果。

在汇编语言中,我们可以使用特定的指令和技巧来实现花式跑马灯效果,从而给人一种炫目的视觉体验。

二、实现思路为了实现花式跑马灯效果,我们需要控制灯光的亮灭和变化,以展示出不同的图案和文字。

在汇编语言中,我们可以通过操作特定的寄存器和端口来控制灯光的状态。

我们需要定义一个存储灯光状态的变量,用来保存当前灯光的亮灭情况。

然后,我们可以使用循环结构来不断改变灯光的状态,从而实现灯光的闪烁效果。

三、具体实现1. 定义变量我们可以使用汇编语言中的数据段来定义一个变量,用来保存灯光的状态。

例如,我们可以定义一个字节变量“light”,用来表示灯光的亮灭状态,其中1表示亮,0表示灭。

2. 控制灯光为了控制灯光的状态,我们可以使用汇编语言中的端口操作指令来向特定的端口发送信号。

例如,我们可以使用OUT指令将灯光状态写入到特定的端口,从而控制灯光的亮灭。

3. 循环控制为了实现花式跑马灯效果,我们需要使用循环结构来不断改变灯光的状态。

例如,我们可以使用汇编语言中的循环指令来控制灯光的闪烁次数和速度,从而实现不同的效果。

四、示例代码下面是一个简单的示例代码,用来实现一个基本的花式跑马灯效果:```assembly.datalight db 1.codemain:mov ah, 0x0E ; 设置光标位置mov al, 'A' ; 设置要显示的字符int 0x10 ; 调用BIOS中断显示字符mov al, lightout 0x80, al ; 控制灯光状态xor al, 1 ; 取反灯光状态mov light, aljmp main ; 循环控制end main```五、总结通过使用汇编语言的指令和技巧,我们可以实现各种花式跑马灯效果。

通过控制灯光的亮灭和变化,我们可以展示出不同的图案和文字,从而给人一种炫目的视觉体验。

跑马灯

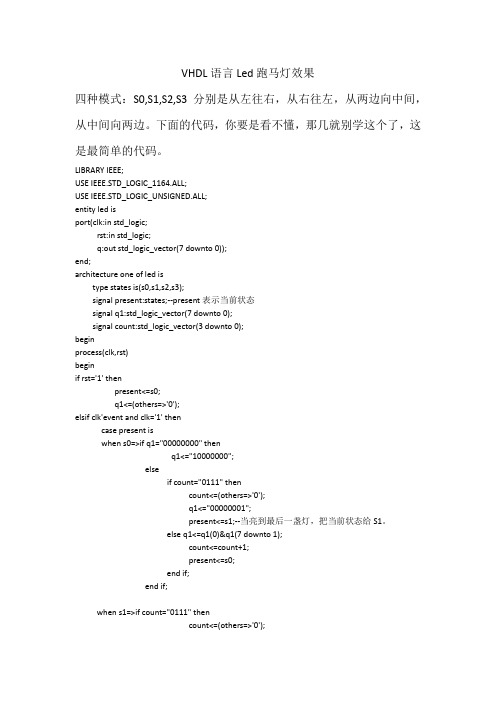

VHDL语言Led跑马灯效果四种模式:S0,S1,S2,S3分别是从左往右,从右往左,从两边向中间,从中间向两边。

下面的代码,你要是看不懂,那几就别学这个了,这是最简单的代码。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;entity led isport(clk:instd_logic;rst:instd_logic;q:out std_logic_vector(7 downto 0));end;architecture one of led istype states is(s0,s1,s2,s3);signal present:states;--present表示当前状态signal q1:std_logic_vector(7 downto 0);signalcount:std_logic_vector(3 downto 0);beginprocess(clk,rst)beginifrst='1' thenpresent<=s0;q1<=(others=>'0');elsifclk'event and clk='1' thencase present iswhen s0=>if q1="00000000" thenq1<="10000000";elseif count="0111" thencount<=(others=>'0');q1<="00000001";present<=s1;--当亮到最后一盏灯,把当前状态给S1。

else q1<=q1(0)&q1(7 downto 1);count<=count+1;present<=s0;end if;end if;when s1=>if count="0111" thencount<=(others=>'0');q1<="10000001";present<=s0;else q1<=q1(6 downto 0)&q1(7);count<=count+1;present<=s1;end if;when s2=>if count="0111" thencount<=(others=>'0');q1<="00011000";present<=s3;else q1(7 downto 4)<=q1(4)&q1(7 downto 5);q1(3 downto 0)<=q1(2 downto 0)&q1(3);count<=count+1;present<=s2;end if;when s3=>if count="0111" thencount<=(others=>'0');q1<="10000000";present<=s3;else q1(7 downto 4)<=q1(6 downto 4)&q1(7);q1(3 downto 0)<=q1(0)&q1(3 downto 1);count<=count+1;present<=s3;end if;end case;end if;end process;q<=q1;end;。

verilog语言的FPGA变速花样流水灯设计

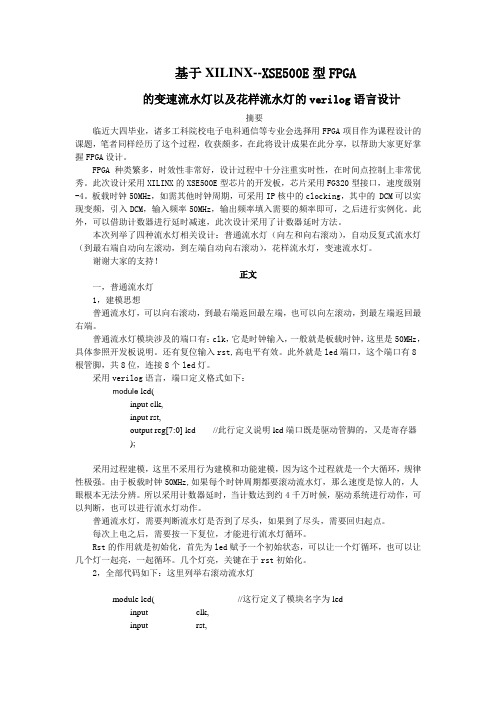

基于XILINX--XSE500E型FPGA的变速流水灯以及花样流水灯的verilog语言设计摘要临近大四毕业,诸多工科院校电子电科通信等专业会选择用FPGA项目作为课程设计的课题,笔者同样经历了这个过程,收获颇多,在此将设计成果在此分享,以帮助大家更好掌握FPGA设计。

FPGA种类繁多,时效性非常好,设计过程中十分注重实时性,在时间点控制上非常优秀。

此次设计采用XILINX的XSE500E型芯片的开发板,芯片采用FG320型接口,速度级别-4。

板载时钟50MHz,如需其他时钟周期,可采用IP核中的clocking,其中的 DCM可以实现变频,引入DCM,输入频率50MHz,输出频率填入需要的频率即可,之后进行实例化。

此外,可以借助计数器进行延时减速,此次设计采用了计数器延时方法。

本次列举了四种流水灯相关设计:普通流水灯(向左和向右滚动),自动反复式流水灯(到最右端自动向左滚动,到左端自动向右滚动),花样流水灯,变速流水灯。

谢谢大家的支持!正文一,普通流水灯1,建模思想普通流水灯,可以向右滚动,到最右端返回最左端,也可以向左滚动,到最左端返回最右端。

普通流水灯模块涉及的端口有:clk,它是时钟输入,一般就是板载时钟,这里是50MHz,具体参照开发板说明。

还有复位输入rst,高电平有效。

此外就是led端口,这个端口有8根管脚,共8位,连接8个led灯。

采用verilog语言,端口定义格式如下:module led(input clk,input rst,output reg[7:0] led //此行定义说明led端口既是驱动管脚的,又是寄存器);采用过程建模,这里不采用行为建模和功能建模,因为这个过程就是一个大循环,规律性极强。

由于板载时钟50MHz,如果每个时钟周期都要滚动流水灯,那么速度是惊人的,人眼根本无法分辨。

所以采用计数器延时,当计数达到约4千万时候,驱动系统进行动作,可以判断,也可以进行流水灯动作。

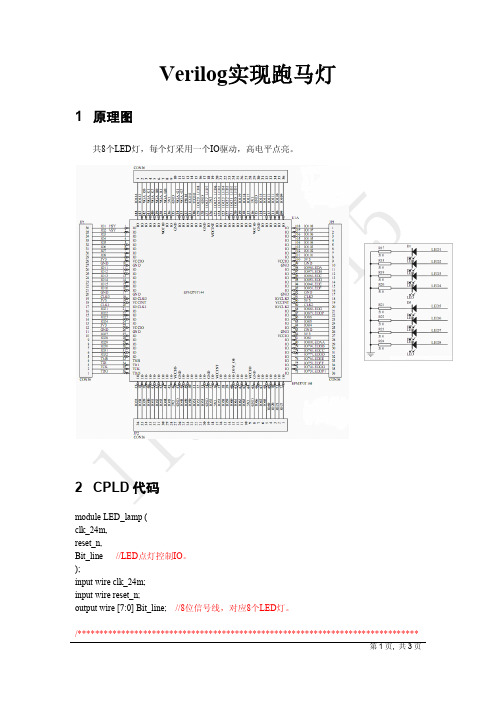

【Easy CPLD570】Verilog实现跑马灯

Verilog实现跑马灯1 原理图共8个LED灯,每个灯采用一个IO驱动,高电平点亮。

2 CPLD代码module LED_lamp (clk_24m,reset_n,Bit_line //LED点灯控制IO。

);input wire clk_24m;input wire reset_n;output wire [7:0] Bit_line; //8位信号线,对应8个LED灯。

/******************************************************************************24M时钟分频,用于内部控制及计数等。

******************************************************************************/ reg [16:0] count_div1;wire condition_183; //183 Hz时钟信号。

always @ (posedge clk_24m or negedge reset_n)beginif(reset_n == 1'b0)count_div1 <= 16'h00000;elsecount_div1 <= count_div1 + 16'h00001;end/****************************************************************************** condition_183:183Hz时钟信号,高电平持续一个24MHz时钟周期,其余时间为低电平。

******************************************************************************/ assign condition_183 = &count_div1[16:0]; //24MHz/2^17=183Hz。

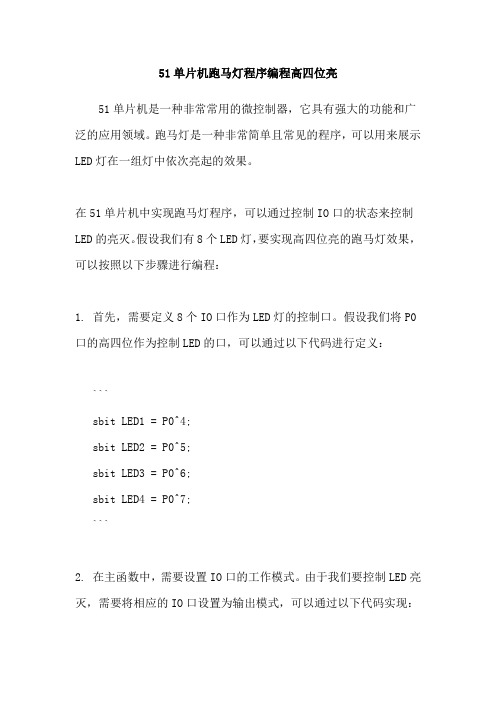

51单片机跑马灯程序编程高四位亮

51单片机跑马灯程序编程高四位亮51单片机是一种非常常用的微控制器,它具有强大的功能和广泛的应用领域。

跑马灯是一种非常简单且常见的程序,可以用来展示LED灯在一组灯中依次亮起的效果。

在51单片机中实现跑马灯程序,可以通过控制IO口的状态来控制LED的亮灭。

假设我们有8个LED灯,要实现高四位亮的跑马灯效果,可以按照以下步骤进行编程:1. 首先,需要定义8个IO口作为LED灯的控制口。

假设我们将P0口的高四位作为控制LED的口,可以通过以下代码进行定义:```sbit LED1 = P0^4;sbit LED2 = P0^5;sbit LED3 = P0^6;sbit LED4 = P0^7;```2. 在主函数中,需要设置IO口的工作模式。

由于我们要控制LED亮灭,需要将相应的IO口设置为输出模式,可以通过以下代码实现:```LED1 = LED2 = LED3 = LED4 = 0; // 初始化为低电平P0M0 = P0M1 = 0; // P0口设置为推挽输出模式```3. 接下来,可以编写一个循环来实现跑马灯效果。

在每一次循环中,将高四位中的一个LED口设置为高电平,其他的LED口设置为低电平,通过不断循环改变高四位LED口的状态,从而实现跑马灯效果。

可以通过以下代码实现:```while (1) {LED1 = 1; // 第一个LED口亮LED2 = 0; // 其他LED口灭LED3 = 0;LED4 = 0;Delay(500); // 延时一段时间,控制灯的亮灭速度LED1 = 0; // 第一个LED口灭LED2 = 1; // 第二个LED口亮LED3 = 0;LED4 = 0;Delay(500);// 依次类推...}```通过以上代码,就可以在51单片机上实现高四位亮的跑马灯效果。

通过改变循环中的延时时间,还可以调节灯的亮灭速度。

此外,还可以通过调节亮灭的顺序,改变跑马灯的效果,使其更加多样化。

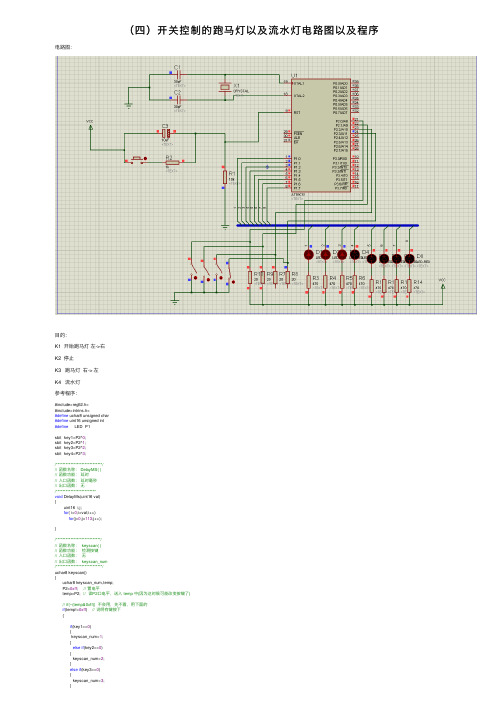

(四)开关控制的跑马灯以及流水灯电路图以及程序

(四)开关控制的跑马灯以及流⽔灯电路图以及程序电路图:⽬的:K1 开始跑马灯左->右K2 停⽌K3 跑马灯右-> 左K4 流⽔灯参考程序:#include<reg52.h>#include<intrins.h>#define uchar8 unsigned char#define uint16 unsigned int#define LED P1sbit key1=P2^0;sbit key2=P2^1;sbit key3=P2^2;sbit key4=P2^3;/*****************************/// 函数名称: DelayMS( )// 函数功能:延时// ⼊⼝函数:延时毫秒// 出⼝函数:⽆/************************* void DelayMs(uint16 val){uint16 i,j;for( i=0;i<val;i++)for(j=0;j<113;j++);}/****************************/// 函数名称: keyscan( )// 函数功能:检测按键// ⼊⼝函数:⽆// 出⼝函数: keyscan_num/*****************************/uchar8 keyscan(){uchar8 keyscan_num,temp;P2=0xff; // 置电平temp=P2; // 读P2⼝电平,送⼊ temp 中(因为这时候可能改变按键了)// if(~(temp&0xff)) 不会⽤,先不看,⽤下⾯的if(temp!=0xff) // 说明有键按下{if(key1==0){keyscan_num=1;}else if(key2==0){keyscan_num=2;}else if(key3==0){keyscan_num=3;}else if(key4==0){keyscan_num=4;}else{keyscan_num=2;}}return keyscan_num;}void main(){uchar8 key_num , temp , i ;while(1){key_num = keyscan(); // 将按键扫描的键值送⼊ key_num 中switch(key_num){case1: goto function0;case2: goto function1;case3: goto function2;case4: goto function3;default: break ;}function0: // 跑马灯从左向右⾛temp=0x01; // 0000 0001for(i=0;i<8;i++){LED= ~temp;DelayMs(1000);temp=temp<<1;}key_num = keyscan(); // 将按键扫描的键值送⼊ key_num 中switch(key_num){case1: goto function0;case2: goto function1;case3: goto function2;case4: goto function3;default: goto function0;break ;}function1: //停⽌LED=0xff;key_num = keyscan(); // 将按键扫描的键值送⼊ key_num 中switch(key_num){case1: goto function0;case2: goto function1;case3: goto function2;case4: goto function3;default: goto function1;break ;}function2: // 从右向左temp=0x80; // 1000 0000for(i=0;i<8;i++){LED= ~temp;DelayMs(1000);temp=temp>>1;}key_num = keyscan(); // 将按键扫描的键值送⼊ key_num 中switch(key_num){case1: goto function0;case2: goto function1;case3: goto function2;case4: goto function3;default: goto function2;break ;}function3: // 流⽔灯LED=0xff ; // 这⾥端⼝全被设置为 1111 1111 ,相当于全灭for(i=0;i<8;i++){LED=LED<<1; // 选择了左移循环DelayMs(1000);}key_num = keyscan(); // 将按键扫描的键值送⼊ key_num 中switch(key_num){case1: goto function0;case2: goto function1;case3: goto function2;case4: goto function3;default: goto function3;break ;}}}分析以及相关疑点:1、按键按下,是遵循实验现象了,但是不太好,按其他键不能⽴即响应,当然我们不要求2、实际⽤弹性开关,⽐较好,具体⾃⼰体会,⼀按下松开对程序没影响,。

EDA课程设计跑马灯设计

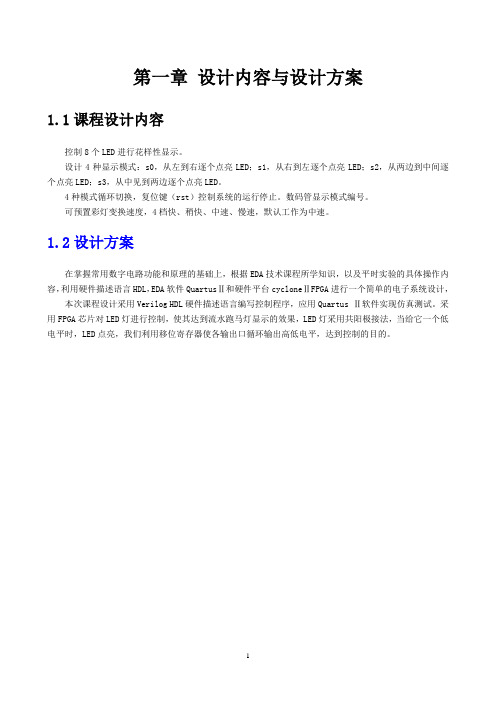

第一章设计内容与设计方案1.1课程设计内容控制8个LED进行花样性显示。

设计4种显示模式:s0,从左到右逐个点亮LED;s1,从右到左逐个点亮LED;s2,从两边到中间逐个点亮LED;s3,从中见到两边逐个点亮LED。

4种模式循环切换,复位键(rst)控制系统的运行停止。

数码管显示模式编号。

可预置彩灯变换速度,4档快、稍快、中速、慢速,默认工作为中速。

1.2设计方案在掌握常用数字电路功能和原理的基础上,根据EDA技术课程所学知识,以及平时实验的具体操作内容,利用硬件描述语言HDL,EDA软件QuartusⅡ和硬件平台cycloneⅡFPGA进行一个简单的电子系统设计,本次课程设计采用Verilog HDL硬件描述语言编写控制程序,应用Quartus Ⅱ软件实现仿真测试。

采用FPGA芯片对LED灯进行控制,使其达到流水跑马灯显示的效果,LED灯采用共阳极接法,当给它一个低电平时,LED点亮,我们利用移位寄存器使各输出口循环输出高低电平,达到控制的目的。

2.1设计原理及设计流程本次试验我所完成的内容是跑马灯的设计,下面我简单的进行一下原理的阐述。

跑马灯课程设计的要求是控制8个LED进行花样显示,设计四种显示模块:第一种显示是从左向右逐个点亮LED。

第二种显示:从右向左逐个点亮LED。

第三种显示:从两边向中间逐个点亮LED。

第四种显示:从中间到两边逐个点亮LED。

四种显示模式循环切换,并带有一位复位键控制系统的运行停止。

为了完成要求的效果显示,由于要求比较简单,所以不用分为很多模块来具体控制,所以我先择利用移位寄存器来完成灯的点亮,我们将LED灯采用共阳极接法,当给于低电平时点亮,那么当我们需要点亮某位LED灯时,只需在该位上赋予低电平即可,比如:如果我们要实现8个数码灯从左到右依次点亮,那么我们就可以给这8个数码灯分别赋值10000000,经过一段时间的延时后再给其赋值01000000,再经过一段时间延时后再给其赋值00100000,依次类推,则最后一种赋值状态为00000001,这样就得到了相应的现象。

verilog HDL跑马灯报告

跑马灯设计一、实验目的:1.熟悉利用QuartusII开发数字电路的基本流程和QuartusII软件的相关操作;2.掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,利用JTAG/AS进行下载的基本操作;3.了解VerilogHDL语言设计或原理图色剂方法。

二、设计内容使LED成流水的方式,在不同的状态中间进行转换,本设计中主要是让LED显示灯按照一定时间间断来显示,通过这样的间隔来使LED按流水方式显示并循环。

三、实验用到的软件和器材软件:QuartusII软件硬件:实验开发板,计算机四、实验步骤1. 创建工程,选择目标芯片,设置合适的参数,编写设计程序并编译。

源程序如下:module led#(parameter max_length=8)(input clk,rst,output reg[max_length-1:0]led_out);always@(posedge clk,posedge rst)if(rst)led_out<={max_length{1'b0}};elseif(led_out=={max_length{1'b1}})led_out<={max_length{1'b0}};elseled_out<={1'b1,led_out[max_length-1:1]};endmodule2. 编译无误后进行时序仿真,仿真无误后管脚锁定。

管脚锁定图如下:3 .将程序下载至EP1C6+EPCS1 试验箱,观察实验结果。

实验箱上LED灯按照一定的时间间隔顺次点亮,按流水方式显示并循环。

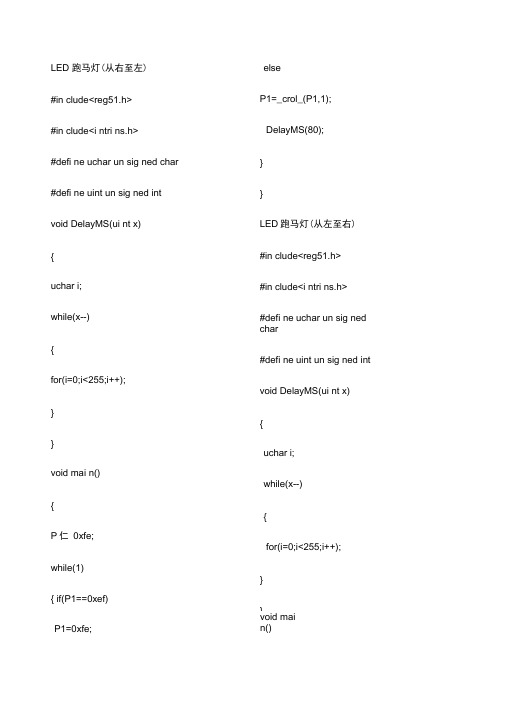

跑马灯程序大全

LED 跑马灯(从右至左)#in clude<reg51.h>#in clude<i ntri ns.h>#defi ne uchar un sig ned char #defi ne uint un sig ned int void DelayMS(ui nt x){uchar i;while(x--){for(i=0;i<255;i++);}}void mai n(){P仁0xfe;while(1){ if(P1==0xef)P1=0xfe; void main()elseP1=_crol_(P1,1);DelayMS(80);}}LED跑马灯(从左至右)#in clude<reg51.h>#in clude<i ntri ns.h>#defi ne uchar un sig ned char#defi ne uint un sig ned intvoid DelayMS(ui nt x) {uchar i;while(x--){for(i=0;i<255;i++);}}{P仁Oxef;while(1){ if(Pl==0x7f)P仁Oxef;elseP1=_cror_(P1,1); DelayMS(40);}}LED跑马灯(左右循环)#in clude<reg51.h>#in clude<i ntri ns.h>#defi ne uchar un sig ned char#defi ne uint un sig ned int void DelayMS(ui nt x) {uchar i;while(x--){for(i=0;i<255;i++); }}void mai n(){uchar i;P仁0xef;while(1){for(i=0;i<4;i++){P1=_cror_(P1,1);DelayMS(40); }P1=0xfe;DelayMS(40); for(i=0;i<3;i++){P1=_crol_(P1,1);DelayMS(40); } P仁}单个LED的闪烁#in elude <reg52.h>#defi ne uchar un sig ned char#defi ne uint un sig ned int sbit LED = P1A0;void DelayMS(ui nt x) {uchar i;while(x--){for(i=120;i>0;i--);}}void mai n(){while(1){LED = ~LED;DelayMS(150);}}连绵灯#in clude<reg51.h>#in clude<i ntri ns.h>#defi ne uchar un sig ned char#defi ne uint un sig ned int void DelayMS(ui nt x) {uchar i;while(x--){for(i=0;i<255;i++);}}void mai n(){P仁0x0e;while(1){ if(P1==0xb1)P1=0x0e;elseP1=_crol_(P1,1); DelayMS(80);}}。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

//产生四种亮灯方式的跑马灯

module zmk(mclk,reset,type,ledout);

input mclk,reset;

input[1:0] type;

output [5:0] ledout;

reg [5:0] ledout;

reg [24:0] count;

reg [4:0] state;

wire clk;

//分频器

always@(posedge mclk)

count=count+1;

assign clk=count[23];

//当type变化的时候对state进行清零

reg[1:0] type_delay;

wire type_change;

always @ (posedge clk)

type_delay <= type;

assign type_change=(type!=type_delay)?1:0;

always @ (posedge clk )

begin

if(reset==0) //初始化语句begin ledout=6'b000000;state<=0;end

else

if(type_change)//对state进行清零

state<=4'b1;

else

if(type==2'b00)

begin

case(state)

4'b0001:ledout=6'b011111;//第一个灯亮

4'b0010:ledout=6'b101111;//第二个灯亮

4'b0011:ledout=6'b110111;//第三个灯亮

4'b0100:ledout=6'b111011;//第四个灯亮

4'b0101:ledout=6'b111101;//第五个灯亮

4'b0110:ledout=6'b111110;//第六个灯亮

4'b0111:ledout=6'b111101;//第五个灯亮

4'b1000:ledout=6'b111011;//第四个灯亮

4'b1001:ledout=6'b110111;//第三个灯亮

4'b1010:ledout=6'b101111;//第二个灯亮

default :ledout=6'b000000;

endcase

state=state+1; //计数器产生state的各种状态if(state==4'b1011)state=5'b00001;

end

else

if(type==2'b01)

begin

case(state)

4'b0001:ledout=6'b101010;

4'b0010:ledout=6'b010101;

default :ledout=6'b000000;

endcase

state=state+1;

if(state==4'b0011)state=5'b00001;

end

else

if(type==2'b10)

begin

case(state)

4'b0001:ledout=6'b110011;

4'b0010:ledout=6'b101101;

4'b0011:ledout=6'b011110;

4'b0100:ledout=6'b101101;

default :ledout=6'b000000;

endcase

state=state+1;

if(state==4'b0101)state=5'b00001;

end

else

if(type==2'b11)

begin

case(state)

5'b00001:ledout=6'b111110;

5'b00010:ledout=6'b111101;

5'b00011:ledout=6'b111011;

5'b00100:ledout=6'b110111;

5'b00101:ledout=6'b101111;

5'b00110:ledout=6'b011111;

5'b00111:ledout=6'b001111;

5'b01000:ledout=6'b010111;

5'b01001:ledout=6'b011011;

5'b01010:ledout=6'b011101;

5'b01011:ledout=6'b011110;

5'b01100:ledout=6'b011100;

5'b01101:ledout=6'b011010;

5'b01110:ledout=6'b010110;

5'b01111:ledout=6'b001110;

5'b10000:ledout=6'b000110;

5'b10001:ledout=6'b001010;

5'b10010:ledout=6'b001100;

5'b10011:ledout=6'b001000;

5'b10100:ledout=6'b000100;

5'b10101:ledout=6'b001000;

5'b10110:ledout=6'b000000;

5'b10111:ledout=6'b111111;

5'b11000:ledout=6'b000000;

5'b11001:ledout=6'b111111;

5'b11010:ledout=6'b000000;

default :ledout=6'b000000;

endcase

state=state+1;

if(state==5'b11011)state=5'b00001; end

end

endmodule。