四输入与非门电路版图设计

IC课程设计 四位与非门电路设计

兰州交通大学电子与信息工程学院I C 课程设计报告课题一:四位与非门电路设计课题二:三输入加法器电路专业电子科学与技术班级电子1001学号 201010024学生姓名牛昕炜设计时间 2012—2013学年第二学期目录目录------------------------------------------------------------- 2课程一四位与非门的电路设计------------------------------------ 4一概要--------------------------------------------------- 4二设计的原理---------------------------------------------- 41 两输入与非门--------------------------------------- 42 四输入与非门符号图及原理--------------------------- 43 电路图--------------------------------------------- 6三、课程设计的过程----------------------------------------- 61 网表文件-------------------------------------------- 62 打开网表文件仿真----------------------------------- 73 延时分析:------------------------------------------ 8课程二组合逻辑加法器------------------------------------------- 8一设计目的------------------------------------------------ 8二设计原理------------------------------------------------ 81 加法器真值表:-------------------------------------- 92 逻辑图---------------------------------------------- 93 电路图--------------------------------------------- 10三课程设计的过程---------------------------------------- 101 网表文件------------------------------------------ 102 打开网表文件仿真----------------------------------- 113 仿真分析(延时分析)------------------------------- 12四课程设计总结------------------------------------------- 13课程一四位与非门的电路设计一概要随着微电子技术的快速发展,人们生活水平不断提高,使得科学技术已融入到社会生活中每一个方面。

四输入或非门电路和版图设计说明

成绩评定表课程设计任务书目录目录 (III)1.绪论 (1)1.1 设计背景 (1)1.2 设计目标 (1)2.四输入或非门 (2)2.1 四输入或非门电路结构 (2)2.2 四输入或非门电路仿真 (3)2.3 四输入或非门的版图绘制 (4)2.4 四输入或非门的版图电路仿真 (5)2.5 LVS检查匹配 (6)总结 (7)附录一:原理图网表 (9)附录二:版图网表 (10)1.绪论1.1 设计背景Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit 版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。

L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

1.2 设计目标1.用tanner软件中的原理图编辑器S-Edit编辑四输入或非门电路原理图。

2.用tanner软件中的TSpice对四输入或非门电路进行仿真并观察波形。

3.用tanner软件中的L-Edit绘制四输入或非门版图,并进行DRC验证。

2输入四与非门

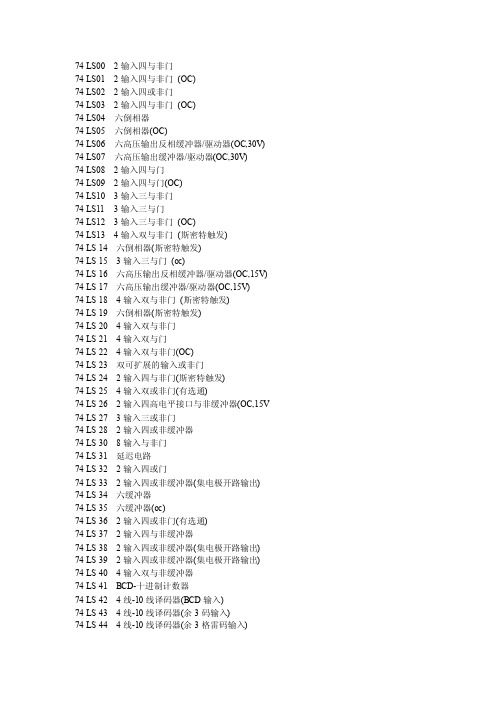

74ls00 2输入四与非门74ls01 2输入四与非门(oc)74ls02 2输入四或非门74ls03 2输入四与非门(oc)74ls04 六倒相器74ls05 六倒相器(oc)74ls06 六高压输出反相缓冲器/驱动器(oc,30v) 74ls07 六高压输出缓冲器/驱动器(oc,30v)74ls08 2输入四与门74ls09 2输入四与门(oc)74ls10 3输入三与非门74ls11 3输入三与门74ls12 3输入三与非门(oc)74ls13 4输入双与非门(斯密特触发)74ls14 六倒相器(斯密特触发)74ls15 3输入三与门(oc)74ls16 六高压输出反相缓冲器/驱动器(oc,15v) 74ls17 六高压输出缓冲器/驱动器(oc,15v)74ls18 4输入双与非门(斯密特触发)74ls19 六倒相器(斯密特触发)74ls20 4输入双与非门74ls21 4输入双与门74ls22 4输入双与非门(oc)74ls23 双可扩展的输入或非门74ls24 2输入四与非门(斯密特触发)74ls25 4输入双或非门(有选通)74ls26 2输入四高电平接口与非缓冲器(oc,15v) 74ls27 3输入三或非门74ls28 2输入四或非缓冲器74ls30 8输入与非门74ls31 延迟电路74ls32 2输入四或门74ls33 2输入四或非缓冲器(集电极开路输出) 74ls34 六缓冲器74ls35 六缓冲器(oc)74ls36 2输入四或非门(有选通)74ls37 2输入四与非缓冲器74ls38 2输入四或非缓冲器(集电极开路输出) 74ls39 2输入四或非缓冲器(集电极开路输出) 74ls40 4输入双与非缓冲器74ls41 bcd-十进制计数器74ls42 4线-10线译码器(bcd输入)74ls43 4线-10线译码器(余3码输入)74ls44 4线-10线译码器(余3葛莱码输入)74ls45 bcd-十进制译码器/驱动器74ls46 bcd-七段译码器/驱动器74ls47 bcd-七段译码器/驱动器74ls48 bcd-七段译码器/驱动器74ls49 bcd-七段译码器/驱动器(oc)74ls50 双二路2-2输入与或非门(一门可扩展)74ls51 双二路2-2输入与或非门74ls51 二路3-3输入,二路2-2输入与或非门74ls52 四路2-3-2-2输入与或门(可扩展)74ls53 四路2-2-2-2输入与或非门(可扩展)74ls53 四路2-2-3-2输入与或非门(可扩展)74ls54 四路2-2-2-2输入与或非门74ls54 四路2-3-3-2输入与或非门74ls54 四路2-2-3-2输入与或非门74ls55 二路4-4输入与或非门(可扩展)74ls60 双四输入与扩展74ls61 三3输入与扩展74ls62 四路2-3-3-2输入与或扩展器74ls63 六电流读出接口门74ls64 四路4-2-3-2输入与或非门74ls65 四路4-2-3-2输入与或非门(oc)74ls70 与门输入上升沿jk触发器74ls71 与输入r-s主从触发器74ls72 与门输入主从jk触发器74ls73 双j-k触发器(带清除端)74ls74 正沿触发双d型触发器(带预置端和清除端)74ls75 4位双稳锁存器74ls76 双j-k触发器(带预置端和清除端)74ls77 4位双稳态锁存器74ls78 双j-k触发器(带预置端,公共清除端和公共时钟端) 74ls80 门控全加器74ls81 16位随机存取存储器74ls82 2位二进制全加器(快速进位)74ls83 4位二进制全加器(快速进位)74ls84 16位随机存取存储器74ls85 4位数字比较器74ls86 2输入四异或门74ls87 四位二进制原码/反码/oi单元74ls89 64位读/写存储器74ls90 十进制计数器74ls91 八位移位寄存器74ls92 12分频计数器(2分频和6分频)74ls93 4位二进制计数器74ls94 4位移位寄存器(异步)74ls95 4位移位寄存器(并行io)74ls96 5位移位寄存器74ls97 六位同步二进制比率乘法器74ls100 八位双稳锁存器74ls103 负沿触发双j-k主从触发器(带清除端)74ls106 负沿触发双j-k主从触发器(带预置,清除,时钟) 74ls107 双j-k主从触发器(带清除端)74ls108 双j-k主从触发器(带预置,清除,时钟)74ls109 双j-k触发器(带置位,清除,正触发)74ls110 与门输入j-k主从触发器(带锁定)74ls111 双j-k主从触发器(带数据锁定)74ls112 负沿触发双j-k触发器(带预置端和清除端)74ls113 负沿触发双j-k触发器(带预置端)74ls114 双j-k触发器(带预置端,共清除端和时钟端) 74ls116 双四位锁存器74ls120 双脉冲同步器/驱动器74ls121 单稳态触发器(施密特触发)74ls122 可再触发单稳态多谐振荡器(带清除端)74ls123 可再触发双单稳多谐振荡器74ls125 四总线缓冲门(三态输出)74ls126 四总线缓冲门(三态输出)74ls128 2输入四或非线驱动器74ls131 3-8译码器74ls132 2输入四与非门(斯密特触发)74ls133 13输入端与非门74ls134 12输入端与门(三态输出)74ls135 四异或/异或非门74ls136 2输入四异或门(oc)74ls137 八选1锁存译码器/多路转换器74ls138 3-8线译码器/多路转换器74ls139 双2-4线译码器/多路转换器74ls140 双4输入与非线驱动器74ls141 bcd-十进制译码器/驱动器74ls142 计数器/锁存器/译码器/驱动器74ls145 4-10译码器/驱动器74ls147 10线-4线优先编码器74ls148 8线-3线八进制优先编码器74ls150 16选1数据选择器(反补输出)74ls151 8选1数据选择器(互补输出)74ls152 8选1数据选择器多路开关74ls153 双4选1数据选择器/多路选择器74ls154 4线-16线译码器74ls155 双2-4译码器/分配器(图腾柱输出)74ls156 双2-4译码器/分配器(集电极开路输出)74ls157 四2选1数据选择器/多路选择器74ls158 四2选1数据选择器(反相输出)74ls160 可预置bcd计数器(异步清除)74ls161 可预置四位二进制计数器(并清除异步)74ls162 可预置bcd计数器(异步清除)74ls163 可预置四位二进制计数器(并清除异步)74ls164 8位并行输出串行移位寄存器74ls165 并行输入8位移位寄存器(补码输出)74ls166 8位移位寄存器74ls167 同步十进制比率乘法器74ls168 4位加/减同步计数器(十进制)74ls169 同步二进制可逆计数器74ls170 4*4寄存器堆74ls171 四d触发器(带清除端)74ls172 16位寄存器堆74ls173 4位d型寄存器(带清除端)74ls174 六d触发器74ls175 四d触发器74ls176 十进制可预置计数器74ls177 2-8-16进制可预置计数器74ls178 四位通用移位寄存器74ls179 四位通用移位寄存器74ls180 九位奇偶产生/校验器74ls181 算术逻辑单元/功能发生器74ls182 先行进位发生器74ls183 双保留进位全加器74ls184 bcd-二进制转换器74ls185 二进制-bcd转换器74ls190 同步可逆计数器(bcd,二进制)74ls191 同步可逆计数器(bcd,二进制)74ls192 同步可逆计数器(bcd,二进制)74ls193 同步可逆计数器(bcd,二进制)74ls194 四位双向通用移位寄存器74ls195 四位通用移位寄存器74ls196 可预置计数器/锁存器74ls197 可预置计数器/锁存器(二进制)74ls198 八位双向移位寄存器74ls199 八位移位寄存器74ls210 2-5-10进制计数器74ls213 2-n-10可变进制计数器74ls221 双单稳触发器74ls230 八3态总线驱动器74ls231 八3态总线反向驱动器74ls240 八缓冲器/线驱动器/线接收器(反码三态输出)74ls241 八缓冲器/线驱动器/线接收器(原码三态输出)74ls242 八缓冲器/线驱动器/线接收器74ls243 4同相三态总线收发器74ls244 八缓冲器/线驱动器/线接收器74ls245 八双向总线收发器74ls246 4线-七段译码/驱动器(30v)74ls247 4线-七段译码/驱动器(15v)74ls248 4线-七段译码/驱动器74ls249 4线-七段译码/驱动器74ls251 8选1数据选择器(三态输出)74ls253 双四选1数据选择器(三态输出)74ls256 双四位可寻址锁存器74ls257 四2选1数据选择器(三态输出)74ls258 四2选1数据选择器(反码三态输出)74ls259 8为可寻址锁存器74ls260 双5输入或非门74ls261 4*2并行二进制乘法器74ls265 四互补输出元件74ls266 2输入四异或非门(oc)74ls270 2048位rom (512位四字节,oc)74ls271 2048位rom (256位八字节,oc)74ls273 八d触发器74ls274 4*4并行二进制乘法器74ls275 七位片式华莱士树乘法器74ls276 四jk触发器74ls278 四位可级联优先寄存器74ls279 四s-r锁存器74ls280 9位奇数/偶数奇偶发生器/较验器74ls28174ls283 4位二进制全加器74ls290 十进制计数器74ls291 32位可编程模74ls293 4位二进制计数器74ls294 16位可编程模74ls295 四位双向通用移位寄存器74ls298 四-2输入多路转换器(带选通)74ls299 八位通用移位寄存器(三态输出)74ls348 8-3线优先编码器(三态输出)74ls352 双四选1数据选择器/多路转换器74ls353 双4-1线数据选择器(三态输出)74ls354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74ls365 6总线驱动器74ls366 六反向三态缓冲器/线驱动器74ls367 六同向三态缓冲器/线驱动器74ls368 六反向三态缓冲器/线驱动器74ls373 八d锁存器74ls374 八d触发器(三态同相)74ls375 4位双稳态锁存器74ls377 带使能的八d触发器74ls378 六d触发器74ls379 四d触发器74ls381 算术逻辑单元/函数发生器74ls382 算术逻辑单元/函数发生器74ls384 8位*1位补码乘法器74ls385 四串行加法器/乘法器74ls386 2输入四异或门74ls390 双十进制计数器74ls391 双四位二进制计数器74ls395 4位通用移位寄存器74ls396 八位存储寄存器74ls398 四2输入端多路开关(双路输出) 74ls399 四-2输入多路转换器(带选通)74ls422 单稳态触发器74ls423 双单稳态触发器74ls440 四3方向总线收发器,集电极开路74ls441 四3方向总线收发器,集电极开路74ls442 四3方向总线收发器,三态输出74ls443 四3方向总线收发器,三态输出74ls444 四3方向总线收发器,三态输出74ls445 bcd-十进制译码器/驱动器,三态输出74ls446 有方向控制的双总线收发器74ls448 四3方向总线收发器,三态输出74ls449 有方向控制的双总线收发器74ls465 八三态线缓冲器74ls466 八三态线反向缓冲器74ls467 八三态线缓冲器74ls468 八三态线反向缓冲器74ls490 双十进制计数器74ls540 八位三态总线缓冲器(反向)74ls541 八位三态总线缓冲器74ls589 有输入锁存的并入串出移位寄存器74ls590 带输出寄存器的8位二进制计数器74ls591 带输出寄存器的8位二进制计数器74ls592 带输出寄存器的8位二进制计数器74ls593 带输出寄存器的8位二进制计数器74ls594 带输出锁存的8位串入并出移位寄存器74ls595 8位输出锁存移位寄存器74ls596 带输出锁存的8位串入并出移位寄存器74ls597 8位输出锁存移位寄存器74ls598 带输入锁存的并入串出移位寄存器74ls599 带输出锁存的8位串入并出移位寄存器74ls604 双8位锁存器74ls605 双8位锁存器74ls606 双8位锁存器74ls607 双8位锁存器74ls620 8位三态总线发送接收器(反相)74ls621 8位总线收发器74ls622 8位总线收发器74ls623 8位总线收发器74ls640 反相总线收发器(三态输出)74ls641 同相8总线收发器,集电极开路74ls642 同相8总线收发器,集电极开路74ls643 8位三态总线发送接收器74ls644 真值反相8总线收发器,集电极开路74ls645 三态同相8总线收发器74ls646 八位总线收发器,寄存器74ls647 八位总线收发器,寄存器74ls648 八位总线收发器,寄存器74ls649 八位总线收发器,寄存器74ls651 三态反相8总线收发器74ls652 三态反相8总线收发器74ls653 反相8总线收发器,集电极开路74ls654 同相8总线收发器,集电极开路74ls668 4位同步加/减十进制计数器74ls669 带先行进位的4位同步二进制可逆计数器74ls670 4*4寄存器堆(三态)74ls671 带输出寄存的四位并入并出移位寄存器74ls672 带输出寄存的四位并入并出移位寄存器74ls673 16位并行输出存储器,16位串入串出移位寄存器74ls674 16位并行输入串行输出移位寄存器74ls681 4位并行二进制累加器74ls682 8位数值比较器(图腾柱输出)74ls683 8位数值比较器(集电极开路)74ls684 8位数值比较器(图腾柱输出)74ls685 8位数值比较器(集电极开路)74ls686 8位数值比较器(图腾柱输出)74ls687 8位数值比较器(集电极开路)74ls688 8位数字比较器(oc输出)74ls689 8位数字比较器74ls690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74ls691 计数器/寄存器(带多转换,三态输出)74ls692 同步十进制计数器(带预置输入,同步清除)74ls693 计数器/寄存器(带多转换,三态输出)74ls696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除) 74ls697 计数器/寄存器(带多转换,三态输出)74ls698 计数器/寄存器(带多转换,三态输出)74ls699 计数器/寄存器(带多转换,三态输出)74ls716 可编程模n十进制计数器74ls718 可编程模n十进制计数器。

四输出与非门版图

作业报告作业题目:画一个4输入与非门的版图,w=5~20. L =2~10.作业要求:(1)画出版图并进行设计规则检查,提取T-spice 网表文件(2)根据从版图中提取的参数,用T-space软件进行仿真,观测器输出波形。

(3)采用CMOS 2 um工艺。

(4)撰写设计报告,设计报告如有雷同均视为不及格,请各位妥善保管好自己的设计文档。

(5)提交报告的最后截止日期位6月10号。

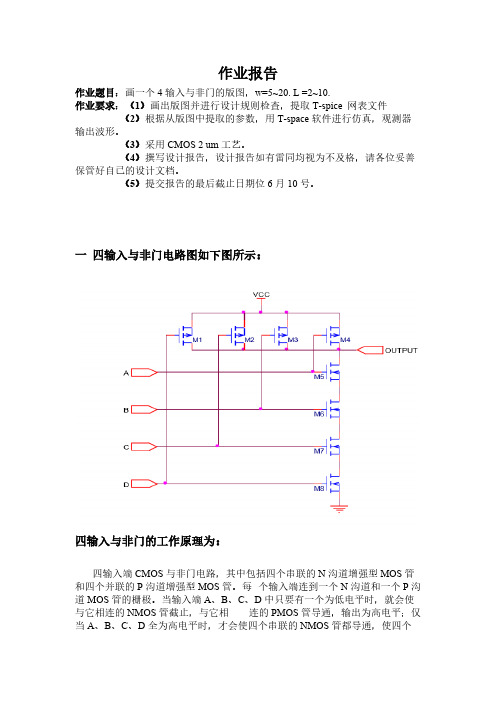

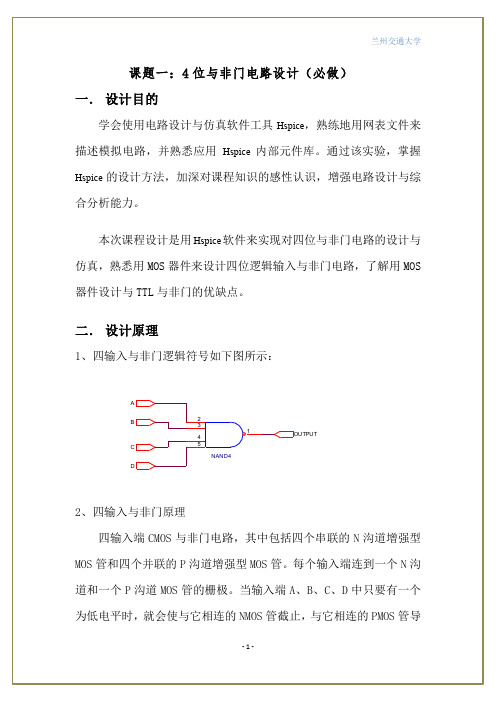

一四输入与非门电路图如下图所示:四输入与非门的工作原理为:四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。

每个输入端连到一个N沟道和一个P沟道MOS管的栅极。

当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。

真值表如下所示:二版图的绘制这次作业要求四输入与非门的宽和长的范围是w=5~20. L =2~10。

我绘制的版图选取W=16 um L=2um ,绘制的过程为:(1)绘制接合端口Abut(2)绘制电源Vdd和Gnd,以及相应端口(3)绘制Nwell层(4)绘制N阱节点(5)绘制衬底节点(6)绘制Nselect区和Pselect区(7)绘制NMOS有源区和PMOS有源区(8)绘制多晶硅层(9)绘制NAND 4 的输入口(10)绘制NAND 4 的输出口(11)绘制NMOS有源区和PMOS的源极三T-spice仿真在绘制完版图之后,经过设计规则检查无误后就可以提取网表进行仿真了。

(1)版图的网表提取结果为:* Circuit Extracted by Tanner Research's L-Edit Version 13.00 / Extract Version 13.00 ; * TDB File: D:\20113250\youwenhao-NAND4.tdb* Cell: Cell0Version 1.03* Extract Definition File: D:\Tanner EDA\Tanner Tools v13.0\ExampleSetup\lights.ext* Extract Date and Time: 06/10/2014 - 01:20.include "C:\Users\Administrator\Desktop\ml5_20.md"V1 Vdd Gnd 5va A Gnd PULSE (0 2.5 100n 2.5n 2.5n 100n 200n)vb B Gnd PULSE (0 2.5 50n 2.5n 2.5n 50n 100n)vc C Gnd PULSE (0 2.5 25n 2.5n 2.5n 25n 50n)vd D Gnd PULSE (0 2.5 12.5n 2.5n 2.5n 12.5n 25n).tran 1n 400n.print tran v(A) v(B) v(C) v(D) v(Out)* Warning: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly1-Poly2 Capacitor ID>* NODE NAME ALIASES* 1 = GND (34.5 , -41.5)* 2 = vdd (32, 15)* 3 = OUT (47.5 , 9)* 4 = D (84 , -6)* 5 = C (70.5 , -5.5)* 6 = B (59.5 , -6)* 7 = A (38 , -5)V1 Vdd Gnd 5va A Gnd PULSE (0 12.5 500n 12.5n 12.5n 5100n 1000n)vb B Gnd PULSE (0 12.5 250n 12.5n 12.5n 250n 500n)vc C Gnd PULSE (0 12.5 125n 12.5n 12.5n 125n 250n)vd D Gnd PULSE (0 12.5 62.5n 12.5n 12.5n 62.5n 125n).tran 1n 1000n.print tran v(D) v(C) v(B) v(A) v(Out)M1 Vdd 4 Out Vdd PMOS L=2u W=16u AD=88p PD=47u AS=60p PS=23.5u $ (44 37 46 53)M2 Out 5 Vdd Vdd PMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 37 36.5 53)M3 Vdd 6 Out Vdd PMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 37 27.5 53)M4 Out 7 Vdd Vdd PMOS L=2u W=16u AD=112p PD=30u AS=88p PS=47u $ (9.5 37 11.5 53)M5 Out 4 Out Gnd NMOS L=2u W=16u AD=120p PD=47u AS=60p PS=23.5u $ (44 0 46 16) M6 Out 5 Out Gnd NMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 0 36.5 16)M7 Out 6 Out Gnd NMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 0 27.5 16)M8 Out 7 Gnd Gnd NMOS L=2u W=16u AD=112p PD=30u AS=92p PS=47u $ (9.5 0 11.5 16)* Pins of element D1 are shorted:* D1 vdd vdd D_lateral $ (88 18.5 91 26.5)* Pins of element D2 are shorted:* D2 vdd vdd D_lateral $ (36 18.5 39.5 26.5)* Total Nodes: 11* Total Elements: 10* Total Number of Shorted Elements not written to the SPICE file: 0* Output Generation Elapsed Time: 0.001 sec* Total Extract Elapsed Time: 0.746 sec.END(2)提取的网表经过T-spice运行后的文件为:T-Spice - Tanner SPICET-Spice - Tanner SPICEVersion 13.00Standalone hardware lockProduct Release ID: T-Spice Win32 13.00.20080321.01:01:33Copyright ?1993-2008 Tanner EDAOpening output file "C:\Users\Administrator\Desktop\游文浩20113250\youwenhao-NAND4.out"Parsing "C:\Users\Administrator\Desktop\游文浩20113250\youwenhao-NAND4.spc"Initializing parser from header file "C:\Users\Administrator\Desktop\游文浩20113250\header.sp"Including "C:\Users\Administrator\Desktop\ml5_20.md"Loaded MOSLevel2 model library, SPICE Level 2 MOSFET revision 1.0Warning : Pulse period is too small, reset to rt + ft + pw = 5.125e-006Accuracy and Convergence options:numndset|dchold = 100Timestep and Integration options:relq|relchgtol = 0.0005Model Evaluation options:dcap = 2 defnrb = 0 [sq] defnrd = 0 [sq]defnrs = 0 [sq] tnom = 25 [deg C]General options:search = C:\Users\Administrator\Desktop temp = 25 [deg C]threads = 4Output options:acout = 1 ingold = 0Device and node counts:MOSFETs - 8 MOSFET geometries - 8BJTs - 0 JFETs - 0MESFETs - 0 Diodes - 0Capacitors - 0 Resistors - 0Inductors - 0 Mutual inductors - 0Transmission lines - 0 Coupled transmission lines - 0Voltage sources - 5 Current sources - 0VCVS - 0 VCCS - 0CCVS - 0 CCCS - 0 V-control switch - 0 I-control switch - 0Macro devices - 0 External C model instances - 0HDL devices - 0Subcircuits - 0 Subcircuit instances - 0Independent nodes - 5 Boundary nodes - 6Total nodes - 11*** 1 WARNING MESSAGE GENERATED DURING SETUPParsing 0.00 secondsSetup 0.01 secondsDC operating point 0.00 secondsTransient Analysis 0.11 secondsOverhead 1.50 seconds-----------------------------------------Total 1.62 secondsSimulation completed with 1 Warning(3)仿真结果为:四作业总结:完成这次作业之后,我对于集成电路版图的绘制有了一个全新的认识,初步掌握了Tunner软件的使用以及T-spice仿真软件的使用。

四输入与非门版图

作业报告作业题目:画一个4输入与非门的版图,w=5~20. L =2~10.作业要求:(1)画出版图并进行设计规则检查,提取T-spice 网表文件(2)根据从版图中提取的参数,用T-space软件进行仿真,观测器输出波形。

(3)采用CMOS 2 um工艺。

(4)撰写设计报告,设计报告如有雷同均视为不及格,请各位妥善保管好自己的设计文档。

(5)提交报告的最后截止日期位6月10号。

一四输入与非门电路图如下图所示:四输入与非门的工作原理为:四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。

每个输入端连到一个N沟道和一个P沟道MOS管的栅极。

当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。

真值表如下所示:二版图的绘制这次作业要求四输入与非门的宽和长的范围是w=5~20. L =2~10。

我绘制的版图选取W=16 um L=2um ,绘制的过程为:(1)绘制接合端口Abut(2)绘制电源Vdd和Gnd,以及相应端口(3)绘制Nwell层(4)绘制N阱节点(5)绘制衬底节点(6)绘制Nselect区和Pselect区(7)绘制NMOS有源区和PMOS有源区(8)绘制多晶硅层(9)绘制NAND 4 的输入口(10)绘制NAND 4 的输出口(11)绘制NMOS有源区和PMOS的源极三T-spice仿真在绘制完版图之后,经过设计规则检查无误后就可以提取网表进行仿真了。

(1)版图的网表提取结果为:* Circuit Extracted by Tanner Research's L-Edit Version 13.00 / Extract Version 13.00 ; * TDB File: D:\20113250\youwenhao-NAND4.tdb* Cell: Cell0 Version 1.03* Extract Definition File: D:\Tanner EDA\Tanner Tools v13.0\ExampleSetup\lights.ext* Extract Date and Time: 06/10/2014 - 01:20.include "C:\Users\Administrator\Desktop\ml5_20.md"V1 Vdd Gnd 5va A Gnd PULSE (0 2.5 100n 2.5n 2.5n 100n 200n)vb B Gnd PULSE (0 2.5 50n 2.5n 2.5n 50n 100n)vc C Gnd PULSE (0 2.5 25n 2.5n 2.5n 25n 50n)vd D Gnd PULSE (0 2.5 12.5n 2.5n 2.5n 12.5n 25n).tran 1n 400n.print tran v(A) v(B) v(C) v(D) v(Out)* Warning: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly1-Poly2 Capacitor ID>* NODE NAME ALIASES* 1 = GND (34.5 , -41.5)* 2 = vdd (32, 15)* 3 = OUT (47.5 , 9)* 4 = D (84 , -6)* 5 = C (70.5 , -5.5)* 6 = B (59.5 , -6)* 7 = A (38 , -5)V1 Vdd Gnd 5va A Gnd PULSE (0 12.5 500n 12.5n 12.5n 5100n 1000n)vb B Gnd PULSE (0 12.5 250n 12.5n 12.5n 250n 500n)vc C Gnd PULSE (0 12.5 125n 12.5n 12.5n 125n 250n)vd D Gnd PULSE (0 12.5 62.5n 12.5n 12.5n 62.5n 125n).tran 1n 1000n.print tran v(D) v(C) v(B) v(A) v(Out)M1 Vdd 4 Out Vdd PMOS L=2u W=16u AD=88p PD=47u AS=60p PS=23.5u $ (44 37 46 53)M2 Out 5 Vdd Vdd PMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 37 36.5 53)M3 Vdd 6 Out Vdd PMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 37 27.5 53)M4 Out 7 Vdd Vdd PMOS L=2u W=16u AD=112p PD=30u AS=88p PS=47u $ (9.5 37 11.5 53)M5 Out 4 Out Gnd NMOS L=2u W=16u AD=120p PD=47u AS=60p PS=23.5u $ (44 0 46 16)M6 Out 5 Out Gnd NMOS L=2u W=16u AD=60p PD=23.5u AS=56p PS=23u $ (34.5 0 36.5 16)M7 Out 6 Out Gnd NMOS L=2u W=16u AD=56p PD=23u AS=112p PS=30u $ (25.5 0 27.516)M8 Out 7 Gnd Gnd NMOS L=2u W=16u AD=112p PD=30u AS=92p PS=47u $ (9.5 0 11.5 16)* Pins of element D1 are shorted:* D1 vdd vdd D_lateral $ (88 18.5 91 26.5)* Pins of element D2 are shorted:* D2 vdd vdd D_lateral $ (36 18.5 39.5 26.5)* Total Nodes: 11* Total Elements: 10* Total Number of Shorted Elements not written to the SPICE file: 0* Output Generation Elapsed Time: 0.001 sec* Total Extract Elapsed Time: 0.746 sec.END(2)提取的网表经过T-spice运行后的文件为:T-Spice - Tanner SPICET-Spice - Tanner SPICEVersion 13.00Standalone hardware lockProduct Release ID: T-Spice Win32 13.00.20080321.01:01:33Copyright ?1993-2008 Tanner EDAOpening output file "C:\Users\Administrator\Desktop\游文浩20113250\youwenhao-NAND4.out"Parsing "C:\Users\Administrator\Desktop\游文浩20113250\youwenhao-NAND4.spc"Initializing parser from header file "C:\Users\Administrator\Desktop\游文浩20113250\header.sp"Including "C:\Users\Administrator\Desktop\ml5_20.md"Loaded MOSLevel2 model library, SPICE Level 2 MOSFET revision 1.0Warning : Pulse period is too small, reset to rt + ft + pw = 5.125e-006Accuracy and Convergence options:numndset|dchold = 100Timestep and Integration options:relq|relchgtol = 0.0005Model Evaluation options:dcap = 2 defnrb = 0 [sq] defnrd = 0 [sq]defnrs = 0 [sq] tnom = 25 [deg C]General options:search = C:\Users\Administrator\Desktop temp = 25 [deg C]threads = 4Output options:acout = 1 ingold = 0Device and node counts:MOSFETs - 8 MOSFET geometries - 8BJTs - 0 JFETs - 0MESFETs - 0 Diodes - 0Capacitors - 0 Resistors - 0Inductors - 0 Mutual inductors - 0Transmission lines - 0 Coupled transmission lines - 0V oltage sources - 5 Current sources - 0VCVS - 0 VCCS - 0CCVS - 0 CCCS - 0V-control switch - 0 I-control switch - 0Macro devices - 0 External C model instances - 0HDL devices - 0Subcircuits - 0 Subcircuit instances - 0Independent nodes - 5 Boundary nodes - 6Total nodes - 11*** 1 WARNING MESSAGE GENERATED DURING SETUPParsing 0.00 secondsSetup 0.01 secondsDC operating point 0.00 secondsTransient Analysis 0.11 secondsOverhead 1.50 seconds-----------------------------------------Total 1.62 secondsSimulation completed with 1 Warning(3)仿真结果为:四作业总结:完成这次作业之后,我对于集成电路版图的绘制有了一个全新的认识,初步掌握了Tunner软件的使用以及T-spice仿真软件的使用。

输入与非门、或非门版图设计

课程名称Course 集成电路设计技术项目名称Item二输入与非门、或非门版图设计与非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(直流分析):或非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u* M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u* M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext* Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(直流分析):课程名称Course集成电路设计技术项目名称Item二输入与非门、或非门版图设计目的Objective 1. 掌握利用E-EDIT进行IC设计方法,设计二输入与非门版图并仿真2. 掌握利用L-EDIT进行IC设计方法,设计二输入或非门版图并仿真3. 领会并掌握版图设计最优化实现方法。

设计一四位与非门的电路设计

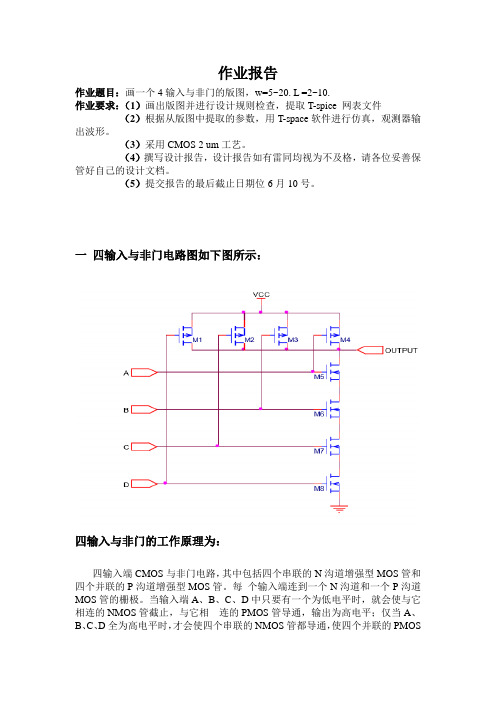

四位与非门的电路设计一、课程设计的目的1、学会使用电路设计与仿真软件工具Hspice,纯熟地用网表文件来描绘模拟电路,并熟悉应用Hspice内部元件库。

通过该实验,掌握Hspice的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析才能。

2、本次课程设计是用Hspice软件来实现对四位与非门电路的设计与仿真,熟悉用MOS器件来设计四位逻辑输入与非门电路,理解用MOS器件设计与TTL与非门的优缺点。

二、课程设计的内容和要求1、内容:用仿真软件HSPICE,用网表文件来描绘模拟电路;2、要求:用MOS器件来设计四位逻辑输入与非门电路。

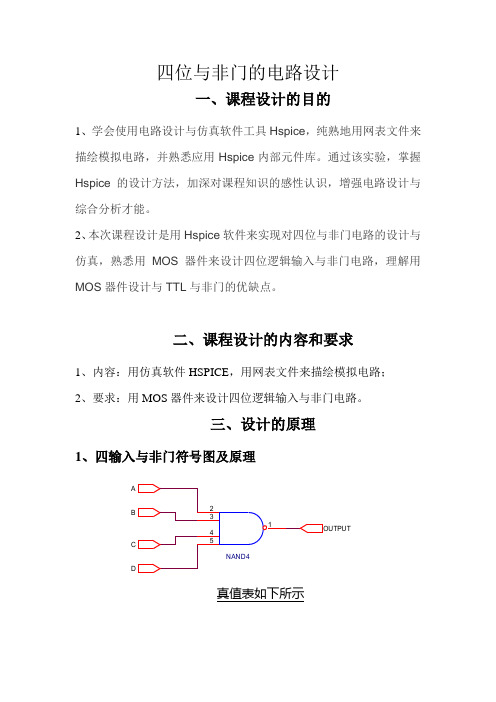

三、设计的原理1、四输入与非门符号图及原理AB真值表如下所示四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。

每个输入端连到一个N沟道和一个P沟道MOS管的栅极。

当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。

设计电路图如以下图所示:2、输入网表文件〔*.sp〕Hspice读入一个输入网表文件,并将模拟结果存在一个输出列表文件或图形数据文件中,输入文件<*.sp>包含以下内容:〔1〕电路网表〔子电路和宏、电源等〕〔2〕声明所要使用的库〔3〕说明要进展的分析〔4〕说明所要求的输出输入网表文件和库文件可以由原理图的四、课程设计的过程1、网表文件首先在orCAD中将上述原理图绘制出,仿真后确保电路图正确且可以实现与非功能,然后生成网表文件。

在文本文档中写出HSPICE 软件所要求的网表文件,并另存为*.sp文件。

网表文件如下:1ADDER Circuit.OPTIONS LIST NODE POST.TRAN 200P 60NM1 1 A VCC VCC PCH L=2u W=4u M2 2 B VCC VCC PCH L=2u W=4u M3 3 0 VCC VCC PCH L=2u W=4u M4 4 0 VCC VCC PCH L=2u W=4u M5 0 A 1 1 NCH L=2u W=4uM6 0 B 2 2 NCH L=2u W=4uM7 5 2 3 3 NCH L=2u W=4uM8 0 1 5 5 NCH L=2u W=4uM9 6 B 3 3 NCH L=2u W=4uM10 0 A 6 6 NCH L=2u W=4uM11 0 2 4 4 NCH L=2u W=4uM12 0 1 4 4 NCH L=2u W=4uM13 7 3 VCC VCC PCH L=2u W=4u M14 8 C VCC VCC PCH L=2u W=4u M15 S 0 VCC VCC PCH L=2u W=4u M16 10 0 VCC VCC PCH L=2u W=4u M17 0 3 7 7 NCH L=2u W=4uM18 0 C 8 8 NCH L=2u W=4uM19 11 8 S S NCH L=2u W=4uM20 0 7 11 11 NCH L=2u W=4uM21 12 C S S NCH L=2u W=4uM22 0 3 12 12 NCH L=2u W=4uM23 0 8 10 10 NCH L=2u W=4uM24 0 7 10 10 NCH L=2u W=4uM25 13 0 VCC VCC PCH L=2u W=4uM26 C1 13 VCC VCC PCH L=2u W=4uM27 0 4 13 13 NCH L=2u W=4uM28 0 10 13 13 NCH L=2u W=4uM29 0 13 C1 C1 NCH L=2u W=4u注释:第三行.TRAN 200P 60N 表示瞬态分析步长为200ps,时间为60ns第四~十一行为电路连接关系描绘语句。

四输入或非门课程设计

四输入或非门专项实践任务书学生姓名:专业班级:指导教师:工作单位:题目: 四输入或非门的设计初始条件:计算机、ORCAD软件,L-EDIT软件要求完成的主要任务:(包括集成电路专项实践工作量及其技术要求,以及说明书撰写等具体要求)1、集成电路专项实践工作量:1周2、技术要求:(1)学习ORCAD软件,L-EDIT软件。

(2)设计一个四输入或非门电路。

(3)利用ORCAD软件,L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2015.6.19布置集成电路专项实践任务、选题;讲解集成电路专项实践具体实施计划与课程设计报告格式的要求;集成电路专项实践答疑事项。

2015.6.19-6.24学习ORCAD软件,L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

2015.6.24-7.1用ORCAD软件设计四输入或非门电路并进行仿真工作,再利用L-EDIT 软件绘制其版图,完成集成电路专项实践报告的撰写。

2015.7.1 提交集成电路专项实践报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日设计项目::四路彩灯显示系统设计目录摘要 .............................................................................................................................................................................. Abstract (I)1 绪论 02 设计内容及要求 (1)2.1 设计的目的及主要任务 (1)2.2 设计思路 (1)3软件介绍 (1)3.1 OrCAD简介 (1)3.2 L-Edit简介 (3)4四输入或非门 (4)4.1 四输入或非门电路结构 (4)4.2 四输入或非门电路仿真 (5)4.3 四输入或非门的版图绘制 (6)4.3.1 NMOS管 (6)4.3.2 PMOS管 (7)4.3.3 输出端口 (7)总结 (9)参考文献 (11)摘要或非门是一种非常常用的数字门电路,本文详细介绍了基于CMOS管的L-EDIT环境下的四输入或非门电路设计仿真及版图布局设计验证。

2、3、4输入或非门版图设计

《集成电路工艺与版图设计》课堂作业班级:电子科学与技术01班姓名:曾海学号:201031722、3、4输入异或门版图设计如下:一、二输入异或门:(1)原理图:<2>L-edit中进行设计的如下二输入或非门版图<3>提取后在T-SPICE中进行参数及输入输出设置如下:VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0)VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<4>在W-EDIT中得到仿真波形图:二、三输入或非门<1>三输入异或门版图<3>参数及输入输出设置VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0) VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<3>仿真图三、四输入或非门<1>版图设计<2>参数及输入输设置Vdd Vdd GND 5VA A GND BIT ({1001} pw=20N lt=10N ht=10N on=5 off= 0)VB B GND BIT ({1010} pw=20N lt=10N ht=10N on=5 off= 0)VC C GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off= 0)VD D GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off= 0).tran 20N 100N.print tran v(OUT) v(A) v(B) v(C) v(D)<3>仿真图4、版图设计总结(1)本次设计中,由仿真图可以看出,仿真波形不是标准的方波图形,而是有相应的误差,可能是由于版图的设计中,布线或器件的放置不合理导致的。

四输入或非门电路和版图设计

成绩评定表课程设计任务书目录目录 .......................................................................................................... 错误!未定义书签。

1.绪论 ....................................................................................................... 错误!未定义书签。

设计背景 ........................................................................................ 错误!未定义书签。

设计目标 ........................................................................................ 错误!未定义书签。

2.四输入或非门 ......................................................................................... 错误!未定义书签。

四输入或非门电路结构 ................................................................ 错误!未定义书签。

四输入或非门电路仿真 ................................................................ 错误!未定义书签。

四输入或非门的版图绘制 ............................................................ 错误!未定义书签。

四输入或非门版图设计

四输入或非门课程设计学生姓名:专业班级:指导教师:工作单位:题目: 四输入或非门的设计初始条件:计算机、ORCAD软件,L-EDIT软件要求完成的主要任务:(包括集成电路专项实践工作量及其技术要求,以及说明书撰写等具体要求)1、集成电路专项实践工作量:1周2、技术要求:(1)学习ORCAD软件,L-EDIT软件。

(2)设计一个四输入或非门电路。

(3)利用ORCAD软件,L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2015.6.19布置集成电路专项实践任务、选题;讲解集成电路专项实践具体实施计划与课程设计报告格式的要求;集成电路专项实践答疑事项。

2015.6.19-6.20学习ORCAD软件,L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

2015.6.21-6.25用ORCAD软件设计四输入或非门电路并进行仿真工作,再利用L-EDIT软件绘制其版图,完成集成电路专项实践报告的撰写。

2015.6.26 提交集成电路专项实践报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 .............................................................................................................................................. Abstract . (I)1 绪论 02 四输入或非门 (1)2.1 四输入或非门的电路结构 (1)2.2 四输入或非门的电路设计与仿真 (2)2.2.1 ORCAD软件介绍 (2)2.2.2 绘制电路图 (2)2.2.3 电路仿真 (3)2.4 四输入或非门的版图绘制 (5)2.4.1 L-EDIT软件介绍 (5)2.4.2 版图绘制 (5)3 总结 (9)参考文献 (10)摘要性能优越的四输入或非门是数字电路中很常见的一种逻辑电路,可广泛应用于算术逻辑单元等电路中。

四输入与非门电路版图设计

成绩评定表学生姓名班级学号专业电子科学与技术课程设计题目四输入与非门电路和版图设计评语组长签字:成绩日期2013年月日课程设计任务书学院信息科学与工程学院专业电子科学与技术学生姓名杨光锐班级学号1003040106课程设计题目四输入与非门电路和版图设计实践教学要求与任务:1.用tanner软件中的S-Edit编辑四输入与非门电路原理图。

2.用tanner软件中的TSpice对四输入与非门电路进行仿真并观察波形。

3.用tanner软件中的L-Edit绘制四输入与非门版图,并进行DRC验证。

4.用tanner软件中的TSpice对版图电路进行仿真并观察波形。

5.用tanner软件中的layout-Edit对电路网表进行LVS检验观察原理图与版图的匹配程度。

工作计划与进度安排:第一周周一:教师布置课设任务,学生收集资料,做方案设计。

周二:熟悉软件操作方法。

周三~四:画电路图周五:电路仿真。

第二周周一~二:画版图。

周三:版图仿真。

周四:验证。

周五:写报告书,验收。

指导教师:2012年月日专业负责人:2013年月日学院教学副院长:2013年月日目录1 绪论 (1)1.1设计背景 (1)1.2设计目标 (1)2 四输入与非门电路 (2)2.1电路原理图 (2)2.2四输入与非门电路仿真观察波形 (2)2.3四输入与非门电路的版图绘制 (3)2.4四输入与非门版图电路仿真观察波形 (4)2.5LVS检查匹配 (5)总结 (7)参考文献 (8)附录一:电路原理图网表 (9)附录二:版图网表 (10)1绪论1.1 设计背景tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

设计一 四位与非门的电路设计

四位与非门的电路设计一、课程设计的目的1、学会使用电路设计与仿真软件工具Hspice ,熟练地用网表文件来描述模拟电路,并熟悉应用Hspice 内部元件库。

通过该实验,掌握Hspice 的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析能力。

2、本次课程设计是用Hspice 软件来实现对四位与非门电路的设计与仿真,熟悉用MOS 器件来设计四位逻辑输入与非门电路,了解用MOS 器件设计与TTL 与非门的优缺点。

二、课程设计的内容和要求1、内容:用仿真软件HSPICE ,用网表文件来描述模拟电路;2、要求:用MOS 器件来设计四位逻辑输入与非门电路。

三、设计的原理1、四输入与非门符号图及原理A OUTPUTNAND412345DC B真值表如下所示A B C D Y0 0 0 0 10 0 0 1 10 0 1 0 10 0 1 1 10 1 0 0 10 1 0 1 10 1 1 0 10 1 1 1 11 0 0 0 11 0 0 1 11 0 1 0 11 0 1 1 11 1 0 0 11 1 0 1 11 1 1 0 11 1 1 1 0四输入端CMOS与非门电路,其中包括四个串联的N沟道增强型MOS管和四个并联的P沟道增强型MOS管。

每个输入端连到一个N沟道和一个P沟道MOS管的栅极。

当输入端A、B、C、D中只要有一个为低电平时,就会使与它相连的NMOS管截止,与它相连的PMOS管导通,输出为高电平;仅当A、B、C、D全为高电平时,才会使四个串联的NMOS管都导通,使四个并联的PMOS管都截止,输出为低电平。

设计电路图如下图所示:2、输入网表文件(*.sp)Hspice读入一个输入网表文件,并将模拟结果存在一个输出列表文件或图形数据文件中,输入文件<*.sp>包含以下内容:(1)电路网表(子电路和宏、电源等)(2)声明所要使用的库(3)说明要进行的分析(4)说明所要求的输出输入网表文件和库文件可以由原理图的网表生成器或文本编辑器产生。

4位数字密码锁的设计

1技术指标用与非门设计一个4位或多位代码的数字锁,要求如下:A: 设计一个保险箱用的多位代码数字锁,比如4位代码ABCD四个输入端和一个开锁用的钥匙插孔输入端E,当开箱时(E=1),如果输入代码(例如ABCD=1010)与设定的代码相同,则保险箱被打开,即输出端Z=1,否则电路发出报警信号:B: 进行电路仿真,并说明其工作原理。

2方案比较方案一:由4个单刀双掷开关构成密码开关,用户可以通过控制开关来控制A、B、C、D四个输入端的电平的高低,进而控制输出电平的高低以及报警信号的工作。

当输入端与3 Proteus软件介绍Proteus软件是来自英国Labcenter electronics公司的EDA工具软件。

Proteus软件有十多年的历史,在全球广泛使用,除了其具有和其它EDA工具一样的原理布图、PCB自动或人工布线及电路仿真的功能外,其革命性的功能是,他的电路仿真是互动的,针对微处理器的应用,还可以直接在基于原理图的虚拟原型上编程,并实现软件源码级的实时调试,如有显示及输出,还能看到运行后输入输出的效果,配合系统配置的虚拟仪器如示波器、逻辑分析仪等,您不需要别的,Proteus为您建立了完备的电子设计开发环境!尤其重要的是Proteus Lite可以完全免费,也可以花微不足道的费用注册达到更好的效果;功能最强的Proteus专业版也非常便宜,人人用得起,对高校还有更多优惠。

Proteus组合了高级原理布图、混合模式SPICE仿真,PCB设计以及自动布线来实现一个完整的电子设计系统。

此系统受益于15年来的持续开发,被《电子世界》在其对PCB设计系统的比较文章中评为最好产品—“The Route to PCB CAD”。

Proteus 产品系列也包含了我们革命性的VSM技术,用户可以对基于微控制器的设计连同所有的周围电子器件一起仿真。

用户甚至可以实时采用诸如LED/LCD、键盘、RS232终端等动态外设模型来对设计进行交互仿真。

4位与非门电路设计

(3)说明要进行的分析(4)说明所要求的输出输入网表文件和库文件可以由原理图的网表生成器或文本编辑器产生。

输入网表文件中的第一行必须是标题行,并且.ALTER辅助模型只能出现在文件最后的.END语句之前,除此之外,其它语句可以按任意顺序排列。

三.设计步骤1、写网表文件首先在orcad中将上述原理图绘制出,仿真后确保电路图正确且能够实现与非功能,然后生成网表文件。

在文本文档中写出Hspice软件所要求的网表文件,并另存为*.sp文件。

网表文件如下所示:NANDMOS Circuit.OPTIONS LIST NODE POST.TRAN 200P 60NM1 OUT 4 VCC VCC PCH L=1U W=20UM2 OUT 5 VCC VCC PCH L=1U W=20UM3 OUT 6 VCC VCC PCH L=1U W=20UM4 OUT 7 VCC VCC PCH L=1U W=20UM5 1 4 0 0 NCH L=1U W=20UM6 2 5 1 1 NCH L=1U W=20UM7 3 6 2 2 NCH L=1U W=20UM8 OUT 7 3 3 NCH L=1U W=20UVCC VCC 0 5V1 4 0 PULSE .2 4.8 2N 1N 1N 5N 20NV2 5 0 PULSE .2 4.8 2N 1N 1N 5N 20NV3 6 0 PULSE .2 4.8 2N 1N 1N 5N 20NV4 7 0 PULSE .2 4.8 2N 1N 1N 5N 20NC OUT 0 .01p.MODEL PCH PMOS LEVEL=1.MODEL NCH NMOS LEVEL=1.END注释:第三行.TRAN 200P 60N表示瞬态分析步长为200ps,时间为60ns 第四~十二行为电路连接关系描述语句。

第十三行VCC VCC0 5表示在节点VCC,0之间加5v直流电压。

四输入或非门的版图设计教材

四输入或非门课程设计学生姓名:专业班级:指导教师:工作单位:题目: 四输入或非门的设计初始条件:计算机、ORCAD软件,L-EDIT软件要求完成的主要任务:(包括集成电路专项实践工作量及其技术要求,以及说明书撰写等具体要求)1、集成电路专项实践工作量:1周2、技术要求:(1)学习ORCAD软件,L-EDIT软件。

(2)设计一个四输入或非门电路。

(3)利用ORCAD软件,L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2015.6.19布置集成电路专项实践任务、选题;讲解集成电路专项实践具体实施计划与课程设计报告格式的要求;集成电路专项实践答疑事项。

2015.6.19-6.20学习ORCAD软件,L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

2015.6.21-6.25用ORCAD软件设计四输入或非门电路并进行仿真工作,再利用L-EDIT软件绘制其版图,完成集成电路专项实践报告的撰写。

2015.6.26 提交集成电路专项实践报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)Abstract (II)1 绪论 (1)2 四输入或非门 (2)2.1 四输入或非门的电路结构 (2)2.2 四输入或非门的电路设计与仿真 (3)2.2.1 ORCAD软件介绍 (3)2.2.2 绘制电路图 (3)2.2.3 电路仿真 (4)2.4 四输入或非门的版图绘制 (6)2.4.1 L-EDIT软件介绍 (6)2.4.2 版图绘制 (6)3 总结 (10)参考文献 (11)摘要性能优越的四输入或非门是数字电路中很常见的一种逻辑电路,可广泛应用于算术逻辑单元等电路中。

CMOS集成电路由于工艺技术的进步以及功耗低、稳定性高、抗干扰性强、噪声容限大、可适应较宽的环境温度和电源电压等一系列的优点,成为现在IC 设计的主流技术。

2、3、4输入或非门版图设计

《集成电路工艺与版图设计》课堂作业班级:电子科学与技术01班姓名:曾海学号:201031722、3、4输入异或门版图设计如下:一、二输入异或门:(1)原理图:<2>L-edit中进行设计的如下二输入或非门版图<3>提取后在T-SPICE中进行参数及输入输出设置如下:VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0)VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<4>在W-EDIT中得到仿真波形图:二、三输入或非门<1>三输入异或门版图<3>参数及输入输出设置VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0) VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<3>仿真图三、四输入或非门<1>版图设计<2>参数及输入输设置Vdd Vdd GND 5VA A GND BIT ({1001} pw=20N lt=10N ht=10N o n=5 off=0)VB B GND BIT ({1010} pw=20N lt=10N ht=10N o n=5 off=0)VC C GND BIT ({1011} pw=20N lt=10N ht=10N o n=5 off=0)VD D GND BIT ({1011} pw=20N lt=10N ht=10N o n=5 off=0).tran 20N 100N.print tran v(OUT) v(A) v(B) v(C) v(D)<3>仿真图4、版图设计总结(1)本次设计中,由仿真图可以看出,仿真波形不是标准的方波图形,而是有相应的误差,可能是由于版图的设计中,布线或器件的放置不合理导致的。

74ls002输入四与非门

74 LS00 2输入四与非门74 LS01 2输入四与非门(OC)74 LS02 2输入四或非门74 LS03 2输入四与非门(OC)74 LS04 六倒相器74 LS05 六倒相器(OC)74 LS06 六高压输出反相缓冲器/驱动器(OC,30V) 74 LS07 六高压输出缓冲器/驱动器(OC,30V)74 LS08 2输入四与门74 LS09 2输入四与门(OC)74 LS10 3输入三与非门74 LS11 3输入三与门74 LS12 3输入三与非门(OC)74 LS13 4输入双与非门(斯密特触发)74 LS 14 六倒相器(斯密特触发)74 LS 15 3输入三与门(oc)74 LS 16 六高压输出反相缓冲器/驱动器(OC,15V) 74 LS 17 六高压输出缓冲器/驱动器(OC,15V)74 LS 18 4输入双与非门(斯密特触发)74 LS 19 六倒相器(斯密特触发)74 LS 20 4输入双与非门74 LS 21 4输入双与门74 LS 22 4输入双与非门(OC)74 LS 23 双可扩展的输入或非门74 LS 24 2输入四与非门(斯密特触发)74 LS 25 4输入双或非门(有选通)74 LS 26 2输入四高电平接口与非缓冲器(OC,15V 74 LS 27 3输入三或非门74 LS 28 2输入四或非缓冲器74 LS 30 8输入与非门74 LS 31 延迟电路74 LS 32 2输入四或门74 LS 33 2输入四或非缓冲器(集电极开路输出) 74 LS 34 六缓冲器74 LS 35 六缓冲器(oc)74 LS 36 2输入四或非门(有选通)74 LS 37 2输入四与非缓冲器74 LS 38 2输入四或非缓冲器(集电极开路输出) 74 LS 39 2输入四或非缓冲器(集电极开路输出) 74 LS 40 4输入双与非缓冲器74 LS 41 BCD-十进制计数器74 LS 42 4线-10线译码器(BCD输入)74 LS 43 4线-10线译码器(余3码输入)74 LS 44 4线-10线译码器(余3格雷码输入)74 LS 45 BCD-十进制译码器/驱动器74 LS 46 BCD-七段译码器/驱动器74 LS 47 BCD-七段译码器/驱动器74 LS 48 BCD-七段译码器/驱动器74 LS 49 BCD-七段译码器/驱动器(OC)74 LS 50 双二路2-2输入与或非门(一门可扩展)74 LS 51 双二路2-2输入与或非门74 LS 51 二路3-3输入,二路2-2输入与或非门74 LS 52 四路2-3-2-2输入与或门(可扩展)74 LS 53 四路2-2-2-2输入与或非门(可扩展)74 LS 53 四路2-2-3-2输入与或非门(可扩展)74 LS 54 四路2-2-2-2输入与或非门74 LS 54 四路2-3-3-2输入与或非门74 LS 54 四路2-2-3-2输入与或非门74 LS 55 二路4-4输入与或非门(可扩展)74 LS 60 双四输入与扩展74 LS 61 三3输入与扩展74 LS 62 四路2-3-3-2输入与或扩展器74 LS 63 六电流读出接口门74 LS 64 四路4-2-3-2输入与或非门74 LS 65 四路4-2-3-2输入与或非门(OC)74 LS 70 与门输入上升沿JK触发器74 LS 71 与输入R-S主从触发器74 LS 72 与门输入主从JK触发器74 LS 73 双JK触发器(带清除端)74 LS 74 正沿触发双D型触发器(带预置端和清除端)74 LS 75 4位双稳锁存器74 LS 76 双JK触发器(带预置端和清除端)74 LS 77 4位双稳态锁存器74 LS 78 双JK触发器(带预置端,公共清除端和公共时钟端) 74 LS 80 门控全加器74 LS 81 16位随机存取存储器74 LS 82 2位二进制全加器(快速进位)74 LS 83 4位二进制全加器(快速进位)74 LS 84 16位随机存取存储器74 LS 85 4位数字比较器74 LS 86 2输入四异或门74 LS 87 四位二进制原码/反码/IO单元74 LS 89 64位读/写存储器74 LS 90 十进制计数器74 LS 91 八位移位寄存器74 LS 92 12分频计数器(2分频和6分频)74 LS 93 4位二进制计数器74 LS 94 4位移位寄存器(异步)74 LS 95 4位移位寄存器(并行IO)74 LS 96 5位移位寄存器74 LS 97 六位同步二进制比率乘法器74 LS 100 八位双稳锁存器74 LS 103 负沿触发双JK主从触发器(带清除端)74 LS 106 负沿触发双JK主从触发器(带预置,清除,时钟) 74 LS 107 双JK主从触发器(带清除端)74 LS 108 双JK主从触发器(带预置,清除,时钟)74 LS 109 双JK触发器(带置位,清除,正触发)74 LS 110 与门输入JK主从触发器(带锁定)74 LS 111 双JK主从触发器(带数据锁定)74 LS 112 负沿触发双JK触发器(带预置端和清除端)74 LS 113 负沿触发双JK触发器(带预置端)74 LS 114 双JK触发器(带预置端,共清除端和时钟端) 74 LS 116 双四位锁存器74 LS 120 双脉冲同步器/驱动器74 LS 121 单稳态触发器(施密特触发)74 LS 122 可再触发单稳态多谐振荡器(带清除端)74 LS 123 可再触发双单稳多谐振荡器74 LS 125 四总线缓冲门(三态输出)74 LS 126 四总线缓冲门(三态输出)74 LS 128 2输入四或非线驱动器74 LS 131 3-8线译码器74 LS 132 2输入四与非门(斯密特触发)74 LS 133 13输入端与非门74 LS 134 12输入端与门(三态输出)74 LS 135 四异或/异或非门74 LS 136 2输入四异或门(OC)74 LS 137 八选1锁存译码器/多路转换器74 LS 138 3-8线译码器/多路转换器74 LS 139 双2-4线译码器/多路转换器74 LS 140 双4输入与非线驱动器74 LS 141 BCD-十进制译码器/驱动器74 LS 142 计数器/锁存器/译码器/驱动器74 LS 145 4-10译码器/驱动器74 LS 147 10线-4线优先编码器74 LS 148 8线-3线八进制优先编码器74 LS 150 16选1数据选择器(反补输出)74 LS 151 8选1数据选择器(互补输出)74 LS 152 8选1数据选择器多路开关74 LS 153 双4选1数据选择器/多路选择器74 LS 154 4线-16线译码器74 LS 155 双2-4译码器/分配器(图腾柱输出)74 LS 156 双2-4译码器/分配器(集电极开路输出)74 LS 157 四2选1数据选择器/多路选择器74 LS 158 四2选1数据选择器(反相输出)74 LS 160 可预置BCD计数器(异步清除)74 LS 161 可预置四位二进制计数器(并清除异步) 74 LS 162 可预置BCD计数器(异步清除)74 LS 163 可预置四位二进制计数器(并清除异步) 74 LS 164 8位并行输出串行移位寄存器74 LS 165 并行输入8位移位寄存器(补码输出)74 LS 166 8位移位寄存器74 LS 167 同步十进制比率乘法器74 LS 168 4位加/减同步计数器(十进制)74 LS 169 同步二进制可逆计数器74 LS 170 4*4寄存器堆74 LS 171 四D触发器(带清除端)74 LS 172 16位寄存器堆74 LS 173 4位D型寄存器(带清除端)74 LS 174 六D触发器74 LS 175 四D触发器74 LS 176 十进制可预置计数器74 LS 177 2-8-16进制可预置计数器74 LS 178 四位通用移位寄存器74 LS 179 四位通用移位寄存器74 LS 180 九位奇偶产生/校验器74 LS 181 算术逻辑单元/功能发生器74 LS 182 先行进位发生器74 LS 183 双保留进位全加器74 LS 184 BCD-二进制转换器74 LS 185 二进制-BCD转换器74 LS 190 同步可逆计数器(BCD,二进制)74 LS 191 同步可逆计数器(BCD,二进制)74 LS 192 同步可逆计数器(BCD,二进制)74 LS 193 同步可逆计数器(BCD,二进制)74 LS 646 八位总线收发器,寄存器74 LS 647 八位总线收发器,寄存器74 LS 648 八位总线收发器,寄存器74 LS 649 八位总线收发器,寄存器74 LS 651 三态反相8总线收发器74 LS 652 三态反相8总线收发器74 LS 653 反相8总线收发器,集电极开路74 LS 654 同相8总线收发器,集电极开路74 LS 668 4位同步加/减十进制计数器74 LS 669 带先行进位的4位同步二进制可逆计数器74 LS 670 4*4寄存器堆(三态)74 LS 671 带输出寄存的四位并入并出移位寄存器74 LS 672 带输出寄存的四位并入并出移位寄存器74 LS 673 16位并行输出存储器,16位串入串出移位寄存器74 LS 674 16位并行输入串行输出移位寄存器74 LS 681 4位并行二进制累加器74 LS 682 8位数值比较器(图腾柱输出)74 LS 683 8位数值比较器(集电极开路)74 LS 684 8位数值比较器(图腾柱输出)74 LS 685 8位数值比较器(集电极开路)74 LS 686 8位数值比较器(图腾柱输出)74 LS 687 8位数值比较器(集电极开路)74 LS 688 8位数字比较器(OC输出)74 LS 689 8位数字比较器74 LS 690 同步十进制计数器/寄存器(带数选,三态输出,直接清除)74 LS 691 计数器/寄存器(带多转换,三态输出)74 LS 692 同步十进制计数器(带预置输入,同步清除)74 LS 693 计数器/寄存器(带多转换,三态输出)74 LS 696 同步加/减十进制计数器/寄存器(带数选,三态输出,直接清除) 74 LS 697 计数器/寄存器(带多转换,三态输出)74 LS 698 计数器/寄存器(带多转换,三态输出)74 LS 699 计数器/寄存器(带多转换,三态输出)74 LS 716 可编程模N十进制计数器74 LS 718 可编程模N十进制计数器74 LS 194 四位双向通用移位寄存器74 LS 195 四位通用移位寄存器74 LS 196 可预置计数器/锁存器74 LS 197 可预置计数器/锁存器(二进制)74 LS 198 八位双向移位寄存器74 LS 199 八位移位寄存器74 LS 210 2-5-10进制计数器74 LS 213 2-N-10可变进制计数器74 LS 221 双单稳触发器74 LS 230 八3态总线驱动器74 LS 231 八3态总线反向驱动器74 LS 240 八缓冲器/线驱动器/线接收器(反码三态输出)74 LS 241 八缓冲器/线驱动器/线接收器(原码三态输出)74 LS 242 八缓冲器/线驱动器/线接收器74 LS 243 4同相三态总线收发器74 LS 244 八缓冲器/线驱动器/线接收器74 LS 245 八双向总线收发器74 LS 246 4线-七段译码/驱动器(30V)74 LS 247 4线-七段译码/驱动器(15V)74 LS 248 4线-七段译码/驱动器74 LS 249 4线-七段译码/驱动器74 LS 251 8选1数据选择器(三态输出)74 LS 253 双四选1数据选择器(三态输出)74 LS 256 双四位可寻址锁存器74 LS 257 四2选1数据选择器(三态输出)74 LS 258 四2选1数据选择器(反码三态输出)74 LS 259 8为可寻址锁存器74 LS 260 双5输入或非门74 LS 261 4*2并行二进制乘法器74 LS 265 四互补输出元件74 LS 266 2输入四异或非门(oc)74 LS 270 2048位ROM (512位四字节,OC)74 LS 271 2048位ROM (256位八字节,OC)74 LS 273 八D触发器74 LS 274 4*4并行二进制乘法器74 LS 275 七位片式华莱士树乘法器74 LS 276 四JK触发器74 LS 278 四位可级联优先寄存器74 LS 279 四S-R锁存器74 LS 280 9位奇数/偶数奇偶发生器/较验器74 LS 28174 LS 283 4位二进制全加器74 LS 290 十进制计数器74 LS 291 32位可编程模74 LS 293 4位二进制计数器74 LS 294 16位可编程模74 LS 295 四位双向通用移位寄存器74 LS 298 四-2输入多路转换器(带选通)74 LS 299 八位通用移位寄存器(三态输出)74 LS 348 8-3线优先编码器(三态输出)74 LS 352 双四选1数据选择器/多路转换器74 LS 353 双4-1线数据选择器(三态输出)74 LS 354 8输入端多路转换器/数据选择器/寄存器,三态补码输出74 LS 355 8输入端多路转换器/数据选择器/寄存器,三态补码输出74 LS 356 8输入端多路转换器/数据选择器/寄存器,三态补码输出74 LS 357 8输入端多路转换器/数据选择器/寄存器,三态补码输出74 LS 365 6总线驱动器74 LS 366 六反向三态缓冲器/线驱动器74 LS 367 六同向三态缓冲器/线驱动器74 LS 368 六反向三态缓冲器/线驱动器74 LS 373 八D锁存器74 LS 374 八D触发器(三态同相)74 LS 375 4位双稳态锁存器74 LS 377 带使能的八D触发器74 LS 378 六D触发器74 LS 379 四D触发器74 LS 381 算术逻辑单元/函数发生器74 LS 382 算术逻辑单元/函数发生器74 LS 384 8位*1位补码乘法器74 LS 385 四串行加法器/乘法器74 LS 386 2输入四异或门74 LS 390 双十进制计数器74 LS 391 双四位二进制计数器74 LS 395 4位通用移位寄存器74 LS 396 八位存储寄存器74 LS 398 四2输入端多路开关(双路输出)74 LS 399 四-2输入多路转换器(带选通)74 LS 422 单稳态触发器74 LS 423 双单稳态触发器74 LS 440 四3方向总线收发器,集电极开路74 LS 441 四3方向总线收发器,集电极开路74 LS 442 四3方向总线收发器,三态输出74 LS 443 四3方向总线收发器,三态输出74 LS 444 四3方向总线收发器,三态输出74 LS 445 BCD-十进制译码器/驱动器,三态输出74 LS 446 有方向控制的双总线收发器74 LS 448 四3方向总线收发器,三态输出74 LS 449 有方向控制的双总线收发器74 LS 465 八三态线缓冲器74 LS 466 八三态线反向缓冲器74 LS 467 八三态线缓冲器74 LS 468 八三态线反向缓冲器74 LS 490 双十进制计数器74 LS 540 八位三态总线缓冲器(反向)74 LS 541 八位三态总线缓冲器74 LS 589 有输入锁存的并入串出移位寄存器74 LS 590 带输出寄存器的8位二进制计数器74 LS 591 带输出寄存器的8位二进制计数器74 LS 592 带输出寄存器的8位二进制计数器74 LS 593 带输出寄存器的8位二进制计数器74 LS 594 带输出锁存的8位串入并出移位寄存器74 LS 595 8位输出锁存移位寄存器74 LS 596 带输出锁存的8位串入并出移位寄存器74 LS 597 8位输出锁存移位寄存器74 LS 598 带输入锁存的并入串出移位寄存器74 LS 599 带输出锁存的8位串入并出移位寄存器74 LS 604 双8位锁存器74 LS 605 双8位锁存器74 LS 606 双8位锁存器74 LS 607 双8位锁存器74 LS 620 8位三态总线发送接收器(反相)74 LS 621 8位总线收发器74 LS 622 8位总线收发器74 LS 623 8位总线收发器74 LS 640 反相总线收发器(三态输出)74 LS 641 同相8总线收发器,集电极开路74 LS 642 同相8总线收发器,集电极开路74 LS 643 8位三态总线发送接收器74 LS 644 真值反相8总线收发器,集电极开路74 LS 645 三态同相8总线收发器CD4001 4二输入或非门CD4002 双4输入或非门CD4006 18位静态移位寄存器CD4007 双互补对加反相器CD4009 六缓冲器/转换-倒相CD4010 六缓冲器/转换-正相CD4011 四2输入与非门CD4012 双4输入与非门CD4013 置/复位双D型触发器CD4014 8位静态同步移位寄存CD4015 双4位静态移位寄存器CD4016 四双向模拟数字开关CD4017 10译码输出十进制计数器CD4018 可预置1/N计数器CD4019 四与或选择门CD4020 14位二进制计数器CD4021 8位静态移位寄存器CD4022 8译码输出8进制计数器CD4023 三3输入与非门CD4024 7位二进制脉冲计数器CD4025 三3输入与非门CD4026 十进制/7段译码/驱动CD4027 置位/复位主从触发器CD4028 BCD十进制译码器CD4029 4位可预置可逆计数器CD4030 四异或门CD4031 64位静态移位寄存器CD4032 三串行加法器CD4033 十进制计数器/7段显示CD4034 8位静态移位寄存器CD4035 4位并入/并出移位寄存器CD4038 3位串行加法器CD4040 12位二进制计数器CD4041 四原码/补码缓冲器CD4042 四时钟D型锁存器CD4043 四或非R/S锁存器CD4044 四与非R/S锁存器CD4046 锁相环CD4047 单非稳态多谐振荡器CD4048 可扩充八输入门CD4049 六反相缓冲/转换器CD4050 六正相缓冲/转换器CD4051 单8通道多路转换/分配CD4052 双4通道多路转换/分配CD4053 三2通道多路转换/分配CD4056 7段液晶显示译码/驱动CD4060 二进制计数/分频/振荡CD4063 四位数值比较器CD4066 四双相模拟开管CD4067 16选1模拟开关CD4068 8输入端与非/与门CD4069 六反相器CD4070 四异或门CD4071 四2输入或门CD4072 双四输入或门CD4073 三3输入与门CD4075 三3输入与门CD4076 4位D型寄存器CD4077 四异或非门CD4078 八输入或/或非门CD4081 四输入与门CD4082 双4输入与门CD4085 双2组2输入与或非门CD4086 可扩展2输入与或非门CD4093 四与非斯密特触发器CD4094 8位移位/贮存总线寄存CD4096 3输入J-K触发器CD4098 双单稳态触发器CD4099 8位可寻址锁存器CD40103 同步可预置减法器CD40106 六斯密特触发器CD40107 双2输入与非缓冲/驱动CD40110 计数/译码/锁存/驱动CD40174 6D触发器CD40175 4D触发器CD40192 BCD可预置可逆计数器CD40193 二进制可预置可逆计数器CD40194 4位双相移位寄存器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

成绩评定表课程设计任务书目录1 绪论ﻩ11、1设计背景ﻩ11.2设计目标 (1)2四输入与非门电路 (2)2、1电路原理图ﻩ22、2四输入与非门电路仿真观察波形 (2)2、3四输入与非门电路的版图绘制ﻩ32、4四输入与非门版图电路仿真观察波形 (4)2、5LVS检查匹配 (5)总结ﻩ7参考文献 (8)附录一:电路原理图网表ﻩ9附录二:版图网表 (10)1绪论1.1 设计背景tanner就是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分就是应用Spice程序来完成的,而tanner软件就是一款学习阶段应用的版图绘制软件,对于初学者就是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件就是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro就是Tanner EDA软件公司所出品的一个IC设计与验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS L ibrary、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。

L-Edit Pro丰富完善的功能为每个IC设计者与生产商提供了快速、易用、精确的设计系统。

1.2设计目标1、用tanner软件中的原理图编辑器S-Edit编辑四输入与非门电路原理图。

2、用tanner软件中的W-Edit对四输入与非门电路进行仿真,并观察波形。

3、用tanner软件中的L-Edit绘制四输入与非门版图,并进行DRC验证。

4.用W-Edit对四输入与非门的版图电路进行仿真并观察波形。

5、用tanner软件中的layout-Edit对四输入与非门进行LVS检验观察原理图与版图的匹配程度。

2 四输入与非门电路2.1电路原理图用CMOS实现四输入与非门电路,PMOS与NMOS管进行全互补连接方式,栅极相连作为输入,电路上面就是四个PMOS并联,PMOS的漏极与下面NMOS的漏极相连作为输出,POMS管的源极与衬底相连接高电平,NMOS管的源极与衬底相连接低电平;原理图如图2、1所示。

图2.1 四输入与非门电路原理图2、2与非门电路仿真观察波形给四输入与非门的输入加激励,高电平为Vdd=5V,低电平为Gnd,并添加输入输出延迟时间,进行仿真,并输出波形;波形图如下图2、2所示。

图2、2 四输入与非门电路输入输出波形图由波形可以瞧出,当输入A,B,C,D都为高电平时,输出低电平;其它情况,也就就是只要有一个零输出就为高电平。

2、3与非门电路的版图绘制用L-Edit版图绘制软件对电路进行四输入与非门电路版图绘制,同时进行DRC验证,查瞧输出结果,检查有无错误;版图与输出结果如下图2、3所示。

图2、3 四输入与非门电路版图2、4四输入与非门版图仿真观察波形同四输入与非门电路原理图仿真相同,添加激励、电源与地,同时观察输入输出波形;波形如下图2、4所示。

图2、4四输入与非门电路版图输入输出波形图由波形可以瞧出,输入A,B,C,D都为高电平时,输出低电平;其它情况,也就就是只要有一个零输出就为高电平。

四输入与非门电路的版图仿真波形与原理图的仿真输出波形基本一致,并且符合输入输出的逻辑关系,电路的设计正确无误。

2、5 LVS检查匹配用layout-Edit对反相器进行LVS检查验证,首先添加输入输出文件,选择要查瞧的输出,观察输出结果检查反相器电路原理图与版图的匹配程度;输出结果如下图2、5所示。

图2、5 四输入与非门电路LVS检查匹配图总结通过本次模拟电路版图课程设计,我受益匪浅。

不仅巩固我们已学的版图工艺的理论知识,提高我们电子电路的设计水品,而且加强我们综合分析问题与解决问题的能力,进一步培养我们的实验技能与动手能力,启发我们创新意识及创新思维。

在设计过程中我们将理论联系实际,在不断的改进设计中提高自己,完善自己的技能,达到了理论与实际的真正结合、、..、、在版图设计的后期,模拟出波形时,还就是遇到了一些困难,可能就是因为移动文件改变了路径而出不了波形,但就是在老师悉心的指导及同学的热情帮助下,我最终找出了问题的根源并顺利完成设计、、、、、、参考文献[1] 钟文耀,郑美珠、CMOS电路模拟与设计—基于tanner、全华科技图书股份有限公司印行,2006、[2] 刘刚等著.微电子器件与IC设计基础、第二版.科学出版社,2009、[3]Alan Hastings、The Art of Analog Layout.Second Edition、电子工业出版社、2013附录一:电路原理图网表*SPICE netlist written by S-Edit Win32 7.03* Written on Jul 5, 2013at08:54:09*Waveform probingcommands.probe、options probe"D:\study\tanner\S-Edit\tutorial\Q\guang、dat"+probesdbfile="D:\study\tanner\S-Edit\tutorial\Q\guang、sdb"+probetopmodule="Module0"* Main circuit: Module0M1Y D N16Gnd NMOSL=2u W=22uAD=66p PD=24u AS=66p PS=24uM2 N16 C N19 GndNMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM3 N19 BN22 Gnd NMOS L=2u W=22u AD=66pPD=24u A S=66p PS=24uM4 N22A GndGnd NMOS L=2u W=22u AD=66pPD=24u AS=66p PS=24uM5 Y CVddVddPMOS L=2uW=22uAD=66p PD=24uAS=66p PS=24uM6 Y D Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM7 Y B Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66pPS=24uM8 Y A Vdd Vdd PMOSL=2u W=22uAD=66pPD=24u AS=66pPS=24u、include "D:\study\tanner\TSpice70\models\ml2_125.md"、tran/op 2n 500n method=bdf、printtranv(Y)v(A) v(B)v(C) v(D)Vsoue Vdd Gnd 5VsssA A GndPULSE(0 5 2n 2n 2n50n 100n)VsssB BGnd PULSE (052n2n2n 60n 120n)VsssCC Gnd PULSE(0 5 2n2n 2n80n150n)VsssD D Gnd PULSE(052n2n 2n 110n 160n)*End of main circuit:Module0附录二:版图网表*Circuit Extracted by Tanner Research's L-Edit Version 9.00 / Extract Version 9、00 ;*TDB File: D:\study\tanner\S-Edit\tutorial\Q\guang、tdb*Cell: Cell0 Version1.22* ExtractDefinition File:D:\study\tanner\LEdit90\Samples\SPR\example1\lights、ext*ExtractDate and Time:07/05/2013 - 08:53.includeD:\study\tanner\TSpice70\models\ml2_125.md* Warning: Layers with UnassignedAREACapacitance、*<Poly Resistor ID>*<Poly2Resistor ID>*<NDiff ResistorID>*<PDiff ResistorID>*<PBase ResistorID>* <N Well Resistor ID>*Warning: Layers with Unassigned FRINGECapacitance.* <Pad Comment>*<Poly1-Poly2CapacitorID>* <Poly ResistorID>*<Poly2Resistor ID>* <NDiff Resistor ID>*<P DiffResistorID>*<P BaseResistor ID>* <N Well Resistor ID>* Warning: Layers with Zero Resistance、* <Pad Comment>*<Poly1-Poly2Capacitor ID>* <NMOS Capacitor ID>* <PMOS CapacitorID>M8 1 103 1 PMOS L=2u W=7u*M8DRAIN GATESOURCEBULK (62 4.564 11、5)M7 39 11PMOS L=2u W=7u*M7 DRAIN GATESOURCE BULK (544、5 5611、5)M6 1 8 31 PMOS L=2uW=7u* M6 DRAIN GATE SOURCEBULK(464、54811.5)M537 1 1 PMOS L=2u W=7u*M5 DRAINGATESOURCEBULK(38 4、540 11、5) M4 310 6 2 NMOS L=2uW=7u*M4 DRAINGATE SOURCE BULK (62 -23、564-16.5) M3 6 9 5 2NMOS L=2uW=7u*M3 DRAINGATE SOURCE BULK (54-23、5 56-16.5)M258 4 2 NMOS L=2u W=7u*M2DRAIN GATE SOURCE BULK (46 -23、548 -16、5) M147 22NMOS L=2uW=7u* M1DRAIN GATESOURCE BULK (38 -23.5 40 -16、5)*Total Nodes: 10* Total Elements: 8*TotalNumber ofShorted Elements notwrittento the SPICE file: 0*Extract Elapsed Time: 0 seconds、include"D:\study\tanner\TSpice70\models\ml2_125、md".tran/op 2n500n method=bdf.print tran v(Y)v(A) v(B) v(C) v(D)VsoueVdd Gnd 5VsssAAGnd PULSE (052n 2n 2n50n 100n)VsssBBGnd PULSE(052n 2n2n60n120n)VsssC C Gnd PULSE(0 5 2n 2n2n80n150n)VsssDDGndPULSE (05 2n2n 2n 110n160n)、END。