二输入与非门、或非门版图设计

模拟电路实验框架图

CD4046B锁相环CC4526B可预置二进制1/N计数器

CD4027双J-K触发器

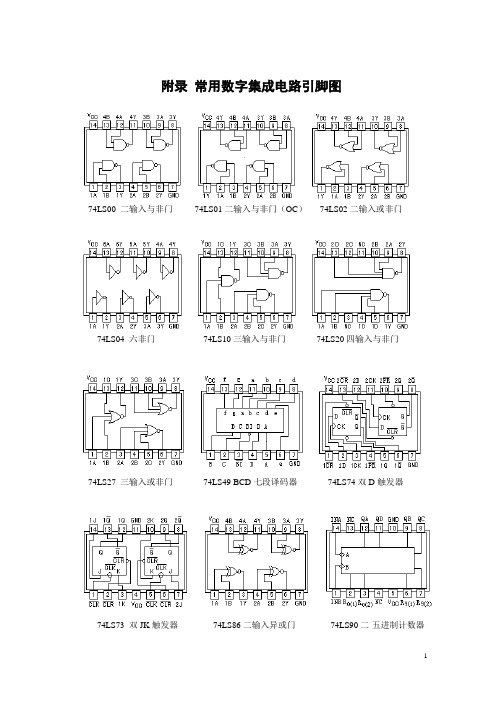

附录常用数字集成电路引脚图

74LS00二输入与非门74LS01二输入与非门(OC)74LS02二输入或非门

74LS04六非门74LS10三输入与非门74LS20四输入与非门

74LS27三输入或非门74LS49 BCD七段译码器74LS74双D触发器

74LS73双JK触发器74LS86二输入异或门74LS90二-五进制计数器

74LS93四位二进制计数器74LS125四三态门74LS183双全加器

74LS138 3-8译码器74LS139双2-4译码器

74LБайду номын сангаас153二4选1数据选择器74LS163同步4位二进制计数器

74LS169 4位二进制可逆计数器74LS194 4位双向移位寄存器

74LS248带上拉BCD七段译码器74LS283四位全加器

二输入与非门、或非门版图设计

课程名称Course 集成电路设计技术项目名称Item二输入与非门、或非门版图设计与非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(直流分析):或非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(直流分析):内容(方法、步骤、要求或考核标准及所需工具、设备等)一、实训设备与工具1.PVI计算机一台;2.Tanner Pro集成电路设计软件二、实训方法、步骤与要求1.二输入与非门电路的线路结构2.二输入或非门电路的线路结构3.CMOS倒相器电路的版图4.根据与非门、或非门线路结构,在一个工程中,重新新建两个新CELL,分别对应与非门和或非门版图,并设计与非门、或非版图结构。

二输入端与非门设计.ppt

(6) 引入输入和输出脚:按步骤 (5) 选出2个输入脚

和1个输出脚。

第5章

组合逻辑电路设计

(7) 更 改 输 入 和 输 出 脚 的 脚 位 名 称 : 在 PIN_NAME 处双击鼠标左键,进行更名,输入脚为A、 B,输出脚为C。

Edit画面,2输入端与非门的电路符号如图5-2所示。

第5章

组合逻辑电路设计

(14) 创建电路包含文件:选取窗口菜单 File→Create Default Include File,产生用来代表目前所 设计电路的nand2.inc文件,供其他VHDL编译时使用, 如图5-3所示。 (15) 时间分析:选取窗口菜单Utilities→Analyze

(2) 保存:选取窗口菜单 File→Save ,出现对话框,

键入文件名nand2.gdf,单击OK按钮。

第5章

组合逻辑电路设计

(3) 指定项目名称,要求与文件名相同:选取窗口

菜单File→Project→Name,键入文件名nand2,单击OK 按钮。

(4) 确定对象的输入位置:在图形窗口内单击鼠标

电路的nand2 .inc文件,供其他VHDL编译时使用。 (11) 时间分析:选取窗口菜单Utilities→Analyze

第5章

组合逻辑电路设计

(6) 保存并查错:选取窗口菜单

File→Project→Save&Check,即可针对电路文件进行检查。 (7) 修改错误:针对Massage-Compiler窗口所提供的 信息修改电路文件,直到没有错误为止。 (8) 保存并编译:选取窗口菜单 File→Project→Save&Compile,即可进行编译,产生 nand2.sof烧写文件。

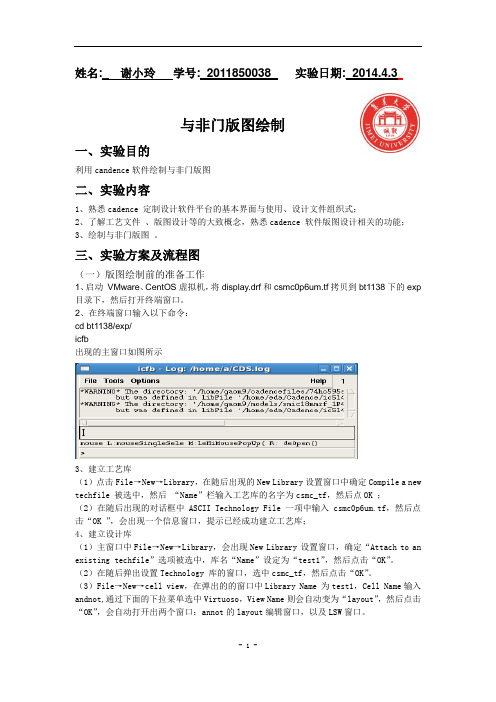

实验二 二输入与非门版图绘制

姓名:_ 谢小玲学号:_2011850038_ 实验日期:_2014.4.3与非门版图绘制一、实验目的利用candence软件绘制与非门版图二、实验内容1、熟悉cadence 定制设计软件平台的基本界面与使用、设计文件组织式;2、了解工艺文件、版图设计等的大致概念,熟悉cadence 软件版图设计相关的功能;3、绘制与非门版图。

三、实验方案及流程图(一)版图绘制前的准备工作1、启动VMware、CentOS虚拟机,将display.drf和csmc0p6um.tf拷贝到bt1138下的exp 目录下,然后打开终端窗口。

2、在终端窗口输入以下命令:cd bt1138/exp/icfb出现的主窗口如图所示3、建立工艺库(1)点击File→New→Library,在随后出现的New Library设置窗口中确定Compile a new techfile 被选中,然后“Name”栏输入工艺库的名字为csmc_tf,然后点OK ;(2)在随后出现的对话框中ASCII Technology File 一项中输入 csmc0p6um.tf,然后点击“OK ”,会出现一个信息窗口,提示已经成功建立工艺库;4、建立设计库(1)主窗口中File→New→Library,会出现New Library 设置窗口,确定“Attach to an existing techfile”选项被选中,库名“Name”设定为“test1”,然后点击“OK”。

(2)在随后弹出设置Technology 库的窗口,选中csmc_tf,然后点击“OK”。

(3)File→New→cell view,在弹出的的窗口中Library Name 为test1,Cell Name输入andnot,通过下面的下拉菜单选中Virtuoso,View Name则会自动变为“layout”,然后点击“OK”,会自动打开出两个窗口:annot的layout编辑窗口,以及LSW窗口。

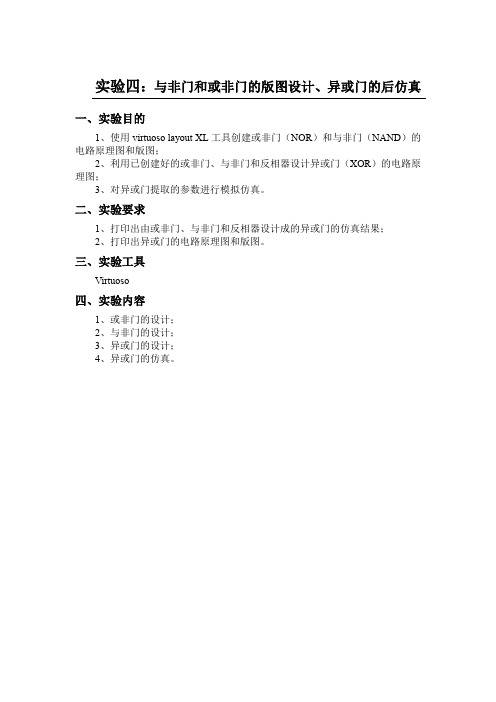

与非门、或非门和异或门的版图设计

实验四:与非门和或非门的版图设计、异或门的后仿真一、实验目的1、使用virtuoso layout XL工具创建或非门(NOR)和与非门(NAND)的电路原理图和版图;2、利用已创建好的或非门、与非门和反相器设计异或门(XOR)的电路原理图;3、对异或门提取的参数进行模拟仿真。

二、实验要求1、打印出由或非门、与非门和反相器设计成的异或门的仿真结果;2、打印出异或门的电路原理图和版图。

三、实验工具Virtuoso四、实验内容1、或非门的设计;2、与非门的设计;3、异或门的设计;4、异或门的仿真。

1、或非门的设计step1:创建或非门的电路原理图,其中,NMOS的宽度120nm为PMOS的宽度为480nm.图1 或非门的电路原理图step2:验证或非门是否可以正常工作,即创建SPICE netlist.图2 验证或非门图3验证成功产生的报告step3:创建一个layout view,并选择菜单栏上Tools->Lyaout XL,此时刚刚保存的电路原理图会自动弹出来,接着选择菜单栏上的Connectivity->Updata->Components and Nets,在弹出得对话框中修改参数,修改完成后点击OK,将会出现如下图所示布局。

图4 利用virtuoso XL工具生成的布局step4:参照前面的实验,在矩形边框内画上电源轨道和NWELL,并创建M1_PSUB 和MI_NWELL,将vdd!、gnd!移至电源轨道上,再将其他原件也移至矩形边框内。

对照电路原理图将NMOS、PMOS、电源、地、以及输入输出端口连接起来,在连线时,注意观察电路原理图,确保不会出现短路情况,连接好的版图如下图所示。

图5 连接好的或非门版图step5:对画好的版图进行DRC,成功后验证提取参数并做LVS验证,再生成网表文件。

图6 或非门版图的DRC验证图7 或非门的参数提取视图图8 或非门的LVS验证图9 或非门的网表文件2、与非门的设计与或非门的设计类似,在此不再赘述,直接给出与非门的电路原理图、版图以及DRC、LVS验证。

输入与非门、或非门版图设计

课程名称Course 集成电路设计技术项目名称Item二输入与非门、或非门版图设计与非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:03.include H:\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6.5)* 4 = F (42.5,6.5)* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u* M1 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u* M2 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M3 F B 5 GND NMOS L=2u W=9.5u AD=52.25p PD=30u AS=57p PS=31u * M3 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)M4 5 A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=52.25p PS=30u * M4 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(直流分析):或非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u* M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u* M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit V7.12 / Extract V4.00 ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\morbn20.ext* Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\ml2_125.mdVPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 0.02 vb 0 5 0.02.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A (29.5,6.5)* 3 = B (55.5,6)* 4 = F (42.5,6.5)* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=49.5p PS=29u* M1 DRAIN GATE SOURCE BULK (39.5 14.5 41.5 23.5)M2 F B 6 VDD PMOS L=2u W=9u AD=49.5p PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULK (47.5 14.5 49.5 23.5)M3 F A GND GND NMOS L=2u W=9.5u AD=57p PD=31u AS=104.5p PS=60u * M3 DRAIN GATE SOURCE BULK (39.5 -18 41.5 -8.5)M4 GND B F GND NMOS L=2u W=9.5u AD=104.5p PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK (47.5 -18 49.5 -8.5)* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(直流分析):课程名称Course集成电路设计技术项目名称Item二输入与非门、或非门版图设计目的Objective 1. 掌握利用E-EDIT进行IC设计方法,设计二输入与非门版图并仿真2. 掌握利用L-EDIT进行IC设计方法,设计二输入或非门版图并仿真3. 领会并掌握版图设计最优化实现方法。

二输入端与非门设计

二输入端与非门设计

二输入端与非门是一种基本的逻辑门电路,用于将输入的逻辑信号进行反转。

它由两个输入端和一个输出端组成,当两个输入信号中的任意一个为高电平时,输出信号为低电平;只有当两个输入信号都为低电平时,输出信号才会为高电平。

1.原理

在二输入端与非门中,当输入信号的两个输入端之一或者同时为高电平时,输入电阻将会导通,将电流流向负载电阻,并将输出线上的电压拉低,表示低电平。

当输入信号两个输入端都为低电平时,两个输入电阻都截止,负载电阻上没有电流流过,输出线上的电压被拉高,表示高电平。

2.设计

首先,选择一个适合的晶体管,常用的有NPN型和PNP型晶体管。

在这里,我们选择一个NPN型晶体管。

接下来,连接两个输入端。

一个输入端通过电阻接到电源电压(Vcc),另一个输入端通过电阻接到地线,同时这两个输入端也与晶体管的基极连接。

然后,将晶体管的发射极接地,集电极与输出端相连接。

负载电阻连接在输出端到电源电压(Vcc)之间。

最后,根据需要添加外部电路。

例如,可以添加降噪电路、电流限制电路等。

3.工作原理

当输入信号的两个输入端之一或者同时为高电平时,输入电阻导通,晶体管的基极-发射极之间的电压使得晶体管导通,导通时的饱和电压使得输出端电压拉低,表示低电平。

当输入信号的两个输入端都为低电平时,两个输入电阻截止,晶体管的基极-发射极之间的电压使得晶体管截止,输出端上的电压由于负载电阻拉高,表示高电平。

总结:。

2、3、4输入或非门版图设计

《集成电路工艺与版图设计》课堂作业班级:电子科学与技术01班姓名:曾海学号:201031722、3、4输入异或门版图设计如下:一、二输入异或门:(1)原理图:<2>L-edit中进行设计的如下二输入或非门版图<3>提取后在T-SPICE中进行参数及输入输出设置如下:VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0)VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<4>在W-EDIT中得到仿真波形图:二、三输入或非门<1>三输入异或门版图<3>参数及输入输出设置VA A GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off=0) VB B GND BIT ({0010} pw=20N lt=10N ht=10N on=5 off=0)Vdd Vdd GND 5.tran 10N 100N.print tran v(OUT) v(A) v(B)<3>仿真图三、四输入或非门<1>版图设计<2>参数及输入输设置Vdd Vdd GND 5VA A GND BIT ({1001} pw=20N lt=10N ht=10N on=5 off= 0)VB B GND BIT ({1010} pw=20N lt=10N ht=10N on=5 off= 0)VC C GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off= 0)VD D GND BIT ({1011} pw=20N lt=10N ht=10N on=5 off= 0).tran 20N 100N.print tran v(OUT) v(A) v(B) v(C) v(D)<3>仿真图4、版图设计总结(1)本次设计中,由仿真图可以看出,仿真波形不是标准的方波图形,而是有相应的误差,可能是由于版图的设计中,布线或器件的放置不合理导致的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程名称Course 集成电路设计技术项目名称Item二输入与非门、或非门版图设计与非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit / Extract ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\ * Extract Date and Time: 05/25/2011 - 10:03.include H:\VPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A ,* 3 = B ,* 4 = F ,* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u * M1 DRAIN GATE SOURCE BULKM2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u * M2 DRAIN GATE SOURCE BULKM3 F B 5 GND NMOS L=2u W= AD= PD=30u AS=57p PS=31u* M3 DRAIN GATE SOURCE BULK -18M4 5 A GND GND NMOS L=2u W= AD=57p PD=31u AS= PS=30u* M4 DRAIN GATE SOURCE BULK -18* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit / Extract ;* TDB File: E:\cmos\yufeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\ * Extract Date and Time: 05/25/2011 - 10:03.include H:\VPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 vb 0 5.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Pad Comment>* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A ,* 3 = B ,* 4 = F ,* 6 = GND (25,-22)M1 VDD B F VDD PMOS L=2u W=9u AD=99p PD=58u AS=54p PS=30u * M1 DRAIN GATE SOURCE BULKM2 F A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS=99p PS=58u * M2 DRAIN GATE SOURCE BULKM3 F B 5 GND NMOS L=2u W= AD= PD=30u AS=57p PS=31u* M3 DRAIN GATE SOURCE BULK -18M4 5 A GND GND NMOS L=2u W= AD=57p PD=31u AS= PS=30u* M4 DRAIN GATE SOURCE BULK -18* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END与非门电路仿真波形图(直流分析):或非门电路的版图:.spc文件(瞬时分析):* Circuit Extracted by Tanner Research's L-Edit / Extract ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\* Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\VPower VDD GND 5va A GND PULSE (0 5 0 5n 5n 100n 200n)vb B GND PULSE (0 5 0 5n 5n 50n 100n).tran 1n 400n.print tran v(A) v(B) v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A ,* 3 = B ,6)* 4 = F ,* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS= PS=29u * M1 DRAIN GATE SOURCE BULKM2 F B 6 VDD PMOS L=2u W=9u AD= PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULKM3 F A GND GND NMOS L=2u W= AD=57p PD=31u AS= PS=60u * M3 DRAIN GATE SOURCE BULK -18M4 GND B F GND NMOS L=2u W= AD= PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK -18* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(瞬时分析):.spc文件(直流分析):* Circuit Extracted by Tanner Research's L-Edit / Extract ;* TDB File: E:\cmos\huofeimen, Cell: Cell0* Extract Definition File: C:\Program Files\Tanner EDA\L-Edit\spr\ * Extract Date and Time: 05/25/2011 - 10:04.include H:\CMOS\VPower VDD GND 5va A GND 5vb B GND 5.dc va 0 5 vb 0 5.print dc v(F)* WARNING: Layers with Unassigned AREA Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <P Base Resistor>* WARNING: Layers with Unassigned FRINGE Capacitance.* <Poly Resistor>* <Poly2 Resistor>* <N Diff Resistor>* <P Diff Resistor>* <N Well Resistor>* <Pad Comment>* <P Base Resistor>* <Poly1-Poly2 Capacitor>* WARNING: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor>* <NMOS Capacitor>* <PMOS Capacitor>* NODE NAME ALIASES* 1 = VDD (34,37)* 2 = A ,* 3 = B ,6)* 4 = F ,* 5 = GND (25,-22)M1 6 A VDD VDD PMOS L=2u W=9u AD=54p PD=30u AS= PS=29u * M1 DRAIN GATE SOURCE BULKM2 F B 6 VDD PMOS L=2u W=9u AD= PD=29u AS=54p PS=30u* M2 DRAIN GATE SOURCE BULKM3 F A GND GND NMOS L=2u W= AD=57p PD=31u AS= PS=60u * M3 DRAIN GATE SOURCE BULK -18M4 GND B F GND NMOS L=2u W= AD= PD=60u AS=57p PS=31u * M4 DRAIN GATE SOURCE BULK -18* Total Nodes: 6* Total Elements: 4* Extract Elapsed Time: 0 seconds.END或非门电路仿真波形图(直流分析):课程名称Course集成电路设计技术项目名称Item二输入与非门、或非门版图设计目的Objective 1. 掌握利用E-EDIT进行IC设计方法,设计二输入与非门版图并仿真2. 掌握利用L-EDIT进行IC设计方法,设计二输入或非门版图并仿真3. 领会并掌握版图设计最优化实现方法。