第二章 MSP430F149基本时钟系统

MSP430F149 定时器

MSP430F149 定时器(1)利用定时器A的模式2(连续)实现的定时资料利用定时器A的模式2(连续)实现的定时资料在程序中对TACTL的控制,当TACTL为如下的赋值时TACTL = TASSEL_2 + MC_2 + TAIE; // SMCLK, contmode, interrupt可以改变TASSEL_X来实现不同的定时,当为TASSEL_1时选ACLK为定时时钟,可以实现最短2S的定时,其次为2S的倍数的定时。

当为TASSEL_2时选SMCLK为定时时钟,定时取决于SMCLK的时钟源,1、SMCLK选DCO = 800KHZ为时钟源,最短定时时间为0.08S 的定时,其次为其倍数。

2、SMCLK选XT2也即外部高频晶振,此时定时取决于晶振频率,及其对分频的设置上。

主要是设置BCSCTL1及BCSCTS2.BCSCTL1 &= ~XT2OFF;BCSCTL2 |= SELS + DIVS_3;通过对上面两句的不同设置,可实现不同的延时。

/****************************************************************************** // MSP-FET430P140 Demo - Timer_A, Toggle P3.4, Overflow ISR, DCO SMCLK//// Description: Toggle P3.4 using software and Timer_A overflow ISR.// In this example an ISR triggers when TA overflows. Inside the TA// overflow ISR P3.4 is toggled. Toggle rate is approximatlely 12Hz.// Proper use of the TAIV interrupt vector generator is demonstrated.// ACLK = n/a, MCLK = SMCLK = TACLK = default DCO ~800kHz//// MSP430F149// ---------------// /|| XIN|-// | | |// --|RST XOUT|-// | |// | P3.4|-->LED//// Dasheng// LiTian Electronic Inc.// Feb 2008// Built with IAR Embedded Workbench Version: 3.42A功能: 由定时器A,采用800KHz的DCO,来实现近一秒的定时中断;计算方法: T = 1/800,000 = 1.25uS so 根据连续计数模式,当计到0XFFFF时,发生溢出中断因此溢出一次的时间是: 65536*1.25 = 0.0819S,所以计时1秒需12次溢出。

MSP430F149中文资料--部分

基于MSP430F149的GPS

(芯片篇)

1、系统功能框图

2芯片资料:

MSP430F149:

低电源电压范围:1.8~3.6V

超低功耗:待机模式:1.6uA 关闭模式(RAM保持):0.1uA 活动模式:280uA at 1MHz,2.2V

5种省电模式

6us内从待机模式唤醒

16位RISC结构,125ns指令周期

带内部参考,采样保持和自动扫描特性的12位A/D转换器

有7个捕获/比较寄存器的16位定时器Timer_B 有3个捕获/比较寄存器的16位定时器Timer_A

片内集成比较器

串行在线编程,无需外部编程电压,安全熔丝可编程代码保护.

器件系列包括:–MSP430F133:8KB+256B闪速存储器,256B的RAM –MSP430F135:16KB+256B闪速存储器,512B的RAM –MSP430F147,MSP430F1471:32KB+256B闪速存储器,1KB的RAM –MSP430F148, MSP430F1481:48KB+256B闪速存储器,2KB的RAM –MSP430F149, MSP430F1491:60KB+256B闪速存储器,2KB的RAM

可用封装:64脚方形扁平封装(QFP).

功能框图。

第2章MSP430F149单片机基础知识

2.2 Flash操作 2.2.1 存储空间组织 存储器中的数据: 字节数据可以定位在偶 地址或奇地址; 字数据定位在偶地址: 低字节在偶地址,高字节 在下一个奇地址。

片内RAM、FLASH组织

其余空间:0~200h用于外围接口及部件的地址

2.2.2 Flash操作

Flash存储器: Flash存储器分为信息Flash和程序Flash 以MSP430F449为例: 信息Flash的地址为1000h~10FFh(256字节),程 序Flash的地址为1100h~FFFFh(60K)。 从硬件和功能上来说,信息Flash和程序Flash没有本 质的不同,程序首地址可以是1100h,也可以是1000h; 信息也可以放在1000h~FFFFh的任何位置。

ROM 0FF16h 0FF14h 0FF12h 00000h 4AEBh 0xxxxh PC

0FA34h 0FA32h 0FA30h

0xxxxh 05BC1h 0xxxxh

寄存器 R10 R11 0FA33h

002A8h 002A7h

0xxh 012h 0xxh

002A8h 002A7h 002A6h

//定义Flash 写操作安全值(高位0xA5)

//定义Flash 段擦除允许位(低位0x02)

#define LOCK

(0x0010)

//擦除锁存位,Lock = 1:Flash被锁存(只读)

char *addr; addr = 0xA000;

//申明地址指针变量 //指针指向0xA000

while(FCTL3 & BUSY){} //测试等待BUSY复位位 FCTL1 = FWKEY + ERASE; //允许FLASH段擦除 FCTL3 = FWKEY; //清楚写锁存位 for(addr =(char *) 0xA000;addr<(char *)0xB000; addr += 0x200) *addr = 0;

MSP430F149最全中文资料

西安邮电学院 63# 710061

陈小忠

3

MSP430 单片机的开发及应用

(1) .汇编是对源程序而言的,因此必须打开一个源文件才能汇编,而连接是对一个工程文件而言 的,连接是对工程文件的所有源代码(包括多个源文件)和数据的定位,因此连接必须打开一个工程 文件才能连接. (2) 连接中必须将库文件的路径改正确,且必须选定 C—SPY 的驱动方式,即在 project 中的 options 的 xlink 的 include 下修改(先选中)xcl 的库路径为 $TOOLKIT_DIR$\icc430\msp430F149A.xcl ,选择 C—SPY 的驱动 drive 为 simulator 或 FLASH EMULATION TOOL ,当没连接 430 片子时可以选 simulator,当连接 430 片子时,选 FLASH EMULATION TOOL 进行在线下载调试. (3) 由于 430 支持汇编语言和 C 语言两种语言,因此可以在一个工程文件 中同时用两种语言,但 建议用汇编语言,因为便于在调试时寻找逻辑和指令的联系及地址的定位正确与否. (4) 在在线的 C—SPY 的调试中,单步需要将 Control 的 Reatime 前的勾取消才能进行单步测试. (5) 在线调试时,不能将 58 管脚(复位/非屏蔽中断) 外部变高,否则,会强制退出调试环境.

第二章

MSP430 F149 语言介绍

MSP430 是德州公司的新产品,有独特的开发环境和自身语言,下面是我在毕业设计中对 F149 的开发环境熟悉中遇到的一些问题的处理和汇编语言的用法及程序中遇到的问题的体会.

第一节 开发环境及程序下载

1.开发环境:在 EW23 环境下进行编程,汇编,连接,在 C—SPY 环境下进行调试,下载是在连 接之后,调试之前,通过计算机的串口下载的.关于环境的操作,可以参考有关资料,其中可能遇到的 问题及解决方法有:

MSP430F149寄存器整理

各个模块的寄存器:1)CPU内部寄存器(状态寄存器SR)2)外围模块寄存器和特殊寄存器中断使能寄存器(IE1)UTXIE0USART0模块的传输中断使能控制比特。

置1时模块的中断使能,0时关闭URXIE0USART0接收中断控制。

1中断使能、0中断关闭ACCVIEFLASH 存储器非法访问中断使能控制比特位。

1使能、0时关闭。

NMIE 非屏蔽中断使能控制。

1使能、0关闭OFIE 晶体出错中断使能控制。

1使能、0关闭WDTIE看门狗中断使能控制。

1使能看门狗中断、0关闭中断使能寄存器(IE2)****UTXIE15URXIE14********UTXIE1USART1模块传输中断使能控制。

1使能、0关闭URXIE1USART1模块接收中断使能控制。

1使能、0关闭中断标志寄存器(IFG1)UTXIFG07URXIFG 06**NMIIFG4****OFIFG 1WDTIFGUTXIFG0USART0传输中断标志位。

1时有中断产生、0没有URXIFG0USART0接收中断标志位。

1时有中断产生、0没有NMIIFG非屏蔽中断标志位。

1时有中断产生、0没有UTXIE07URXIE06ACCVIE5NMIIE4**3**2OFIE1WDTIEOFIFG晶体出错中断标志位。

1时有中断产生、0没有WDTIFG看门狗中断标志。

1时有中断产生、0时没有中断标志寄存器(IFG2)****UTXIFG15URXIFG14********UTXIFG1USART1传输中断标志位。

1时有中断产生、0时没有URXIFG1USART1接收中断标志位。

1时有中断产生、0时没有模块使能寄存器1(ME1)UTXE0 7URXE0USPIE0************UTXE0USART0的传输使能。

1时USART0传输模块使能、0时不工作URXE0 USPIE0USART作为UART时,该比特控制UART的接收功能,设置为1时接收模块使能,0时不工作;作为SPI时,设置为1,则SPI使能,0时SPI不工作。

MSP430时钟系统详解

2

while(1) { P1OUT = 0x40; _delay_cycles(100); P1OUT = 0; _delay_cycles(5000); } }

// 开启 LED // 关闭 LED

2、CPU 运行在晶振(32768Hz)时钟下: 时钟下: 晶体频率为 32768 赫兹,约 3 倍的 VLO。如果我们在前面的代码中使用晶振,指示灯应闪 烁大约每秒一次。 你知道为什么 32768 赫兹是一个标准?这是因为这个数字是 2 的 15 次方, 因此很容易用简单的数字计数电路,以每秒一次获得率 ——手表和其他时间时基。认识到 ACLK 来自外部晶振时钟。 #include <msp430g2231.h> void main(void) { WDTCTL = WDTPW + WDTHOLD; // 关闭看门狗定时器 P1DIR = 0x41; // P1.0 和 P1.6 配置输出 P1OUT = 0x01; // 开启 P1.0 BCSCTL3 |= LFXT1S_0; // LFXT1 = 32768Hz 晶振 while(IFG1 & OFIFG) { IFG1 &= ~OFIFG; // 清除 OSCFault 标志 _delay_cycles(100000); // 为可见的标志延时 } P1OUT = 0; // 关闭 P1 __bis_SR_register(SCG1 + SCG0); // 关闭 DCO BCSCTL2 |= SELM_3 + DIVM_3; // MCLK = 32768/8 while(1) { P1OUT = 0x40; // 开启 LED _delay_cycles(100); P1OUT = 0; / / 关闭 LED _delay_cycles(5000); } } 3、CPU 运行在晶振(32768Hz)和 DCO 时钟下: 时钟下: 最慢的频率,我们可以运行 DCO 约在 1MHz(这也是默认速度) 。因此,我们将开始切换 MCLK 到 DCO 下。在大多数系统中,你会希望 ACLK 上运行的 VLO 或 32768 赫兹晶振。 由于 ACLK 在我们目前的代码是在晶体上运行,我们会打开 DCO 计算。

MSP430F149数据手册

AVAILABLE OPTIONS PACKAGED DEVICES TA PLASTIC 64-PIN QFP (PM) MSP430F133IPM MSP430F135IPM MSP430F147IPM MSP430F1471IPM MSP430F148IPM MSP430F1481IPM MSP430F149IPM MSP430F1491IPM PLASTIC 64-PIN QFP (PAG) PLASTIC 64-PIN QFN (RTD) MSP430F133IRTD MSP430F135IRTD MSP430F147IRTD MSP430F1471IRTD MSP430F148IRTD MSP430F1481IRTD MSP430F149IRTD MSP430F1491IRTD

D Serial Communication Interface (USART),

Functions as Asynchronous UART or Synchronous SPI Interface − Two USARTs (USART0, USART1) — MSP430x14x(1) Devices − One USART (USART0) — MSP430x13x Devices Family Members Include: − MSP430F133: 8KB+256B Flash Memory, 256B RAM − MSP430F135: 16KB+256B Flash Memory, 512B RAM − MSP430F147, MSP430F1471†: 32KB+256B Flash Memory, 1KB RAM − MSP430F148, MSP430F1481†: 48KB+256B Flash Memory, 2KB RAM − MSP430F149, MSP430F1491†: 60KB+256B Flash Memory, 2KB RAM Available in 64-Pin Quad Flat Pack (QFP) and 64-pin QFN For Complete Module Descriptions, See the MSP430x1xx Family User’s Guide, Literature Number SLAU049

MSP430F149介绍文档

P3DIR |= BIT4; //将P3.4设置为输出方向

P3OUT |= BIT3; //使P3.4输出高电平(实验板上初始化灯的状态为熄//灭)

while(1) {

P3OUT ^= BIT4; //灯的状态取反

Delay(); //调用延时子程序

}

}

/*******以下是一个不精确的延时子程序****(i=0;i<1000;i++)

for(j=0;j<110;j++);

}

将该程序烧入MSP430测试,看现象。

开发板给出的源码程序通常使用以下程序作为延时程序

i=50000;

do(i--);

while(i!=0);

课程入门介绍

MSP430引脚介绍(芯片图参考数据手册第3页)

58脚RST/NMI为430单片机的复位引脚(低电平有效)。

1脚DVCC,63脚DVSS为数字电源接口。

64脚AVCC,62脚AVSS为模拟电源接口。

注意:MSP430系列单片机的供电电压为1.8V~3.6V。

说明(在MSP430小系统中数字电源地与模拟电源地必须通过0欧电阻连接起来以防止数字电路产生的高频信号对模拟电路造成影响)

54脚TDO/TDI,55脚TDI/TCLK,56脚TMS,57脚TCK为JTAG接口(同时拥有仿真器和编程器的功能),用于下载程序并实现硬件在线仿真。

具体引脚功能参考《MSP430英文数据手册.pdf》8页

I/O口的操作

P1~P6的公有寄存器位为PXSEL,PXDIR,PXOUT,PXIN。

其中P1,P2相对于P3,P4,P5,P6还多出了3个寄存器PXIE,PXIES,PXIFG,这三个寄存器是用于设置开启P1,P2的外部触发中断使用的(其中X可以为1,2,3,4,5,6)。

MSP430时钟分析

MSP430时钟分析最近开始学习MSP430,在所有单片机学习中,时钟的设置无疑是最基本的一项工作!尤其对于现在的单片机,外部有低速,高速两种晶振,内部还有PLL 的内部时钟源,设置好系统工作的时钟则是工作完美开始的表现。

我一共用了两种系列的430 单片机,MSP430F149 和MSP430F437,系列的不同,时钟的设置也略有不同,下面从149 的时钟一步一步来说吧!在f149 中,基础时钟是被叫做basic clock module,其一共有三个时钟源:一个LFXT1CLK,为低速/高速晶振源,通常接32.768khz,也可以接(400khz~8Mhz)一个为XT2CLK,外接标准高速晶振,通常是接8Mhz,也可以接(400khz~8Mhz)还有一个叫DCOCLK,为内部晶振,有RC震荡回路构成。

在430 内部一共有三个时钟系统一个为ACLK,通常由LFXT1CLK 作为时钟源,可以通过软件控制改时钟的分频系树。

一个为MCLK,即Main CLK,一听就知道是主时钟单元,为系统内核提供时钟,它可以通过软件从三个时钟源选择,一个为SMCLK,称作辅助主时钟,也是可以由软件选择时钟源。

Basic Clock Module Registers(基础时钟寄存器)DCO control register DCOCTLBasic clock system control 1 BCSCTL1Basic clock system control 2 BCSCTL2SFR interrupt enable register 1 IE1SFR interrupt flag register 1 IFG1DCOCTL 寄存器是用来配置DCOCLK 的,这里暂且不提BCSCTL1 与BCSCTL2 寄存器则显得比较重要,这两个寄存器控制了你整个系统中430 的工作时钟系统。

BCSCTL1 寄存器:7 654 3 210XT2OFF XTS DIVAx XT5V RSELxXT20FF:用来控制XT2 晶振的开启和关闭,置1 时关闭,置0 时,开启XTS:用来选择低速晶体的工作模式(可忽略)DIVAx:用来选择ACLK 的分频系数XT5V: 无用。

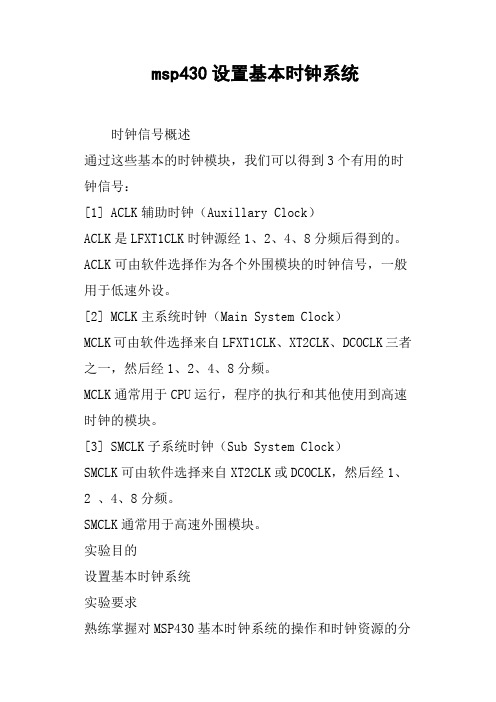

msp430设置基本时钟系统

/* DCOCTL 的位定义 */ #define MOD0 (0x01) /* Modulation Bit 0 */ #define MOD1 (0x02) /* Modulation Bit 1 */ #define MOD2 (0x04) /* Modulation Bit 2 */ #define MOD3 (0x08) /* Modulation Bit 3 */ #define MOD4 (0x10) /* Modulation Bit 4 */ #define DCO0 (0x20) /* DCO Select Bit 0 */ #define DCO1 (0x40) /* DCO Select Bit 1 */ #define DCO2 (0x80) /* DCO Select Bit 2 */ /* BCSCTL1 的位定义 */ #define RSEL0 (0x01) /* Resistor Select Bit 0 */ #define RSEL1 (0x02) /* Resistor Select Bit 1 */ #define RSEL2 (0x04) /* Resistor Select Bit 2 */ #define XT5V (0x08) /* XT5V should always be reset */ #define DIVA0 (0x10) /* ACLK Divider 0 */ #define DIVA1 (0x20) /* ACLK Divider 1 */ #define XTS (0x40) /* LFXTCLK 0:Low Freq. / 1: High Freq. */ #define XT2OFF (0x80) /* Enable XT2CLK */ /* BCSCTL1 的 DIVA 的功能定义 */ #define DIVA_0 (0x00) /* ACLK Divider 0: 0x20) /* MCLK Divider 2: /4 */ #define DIVM_3 (0x30) /* MCLK Divider 3: /8 */ /* BCSCTL1 的 SELM 的功能定义 */ #define SELM_0 (0x00) /* MCLK Source Select 0: DCOCLK */ #define SELM_1 (0x40) /* MCLK Source Select 1: DCOCLK */ #define SELM_2 (0x80) /* MCLK Source Select 2: XT2CLK/LFXTCLK */ #define SELM_3 (0xC0) /* MCLK Source Select 3: LFXTCLK */ #endif ///////////////////////////////////////////////// ///////////////////////////////////////////////// //////////////// #include; #include "BoardConfig.h" #include "SetClock.h" // 时钟设置函数// 系统时钟设定 void BCSInit (void) {

MSP430F149时钟操作

#define uint unsigned int

void main() {

uint a; WDTCTL=WDTHOLD+WDTPW;//关闭看门狗 BCSCTL1&=~XT2OFF;//首先打开外部晶体振荡器。也就是将 XT2OFF 清零。

OFIE:检测晶体振荡器是否正常工作使能控制。0 关;1 开。(产生的是非可屏蔽中断。) 5. IFG1:

OFIFG:晶体振荡是否正常工作中断标志位。(就算不打开使能端也只能置位,打开使 能端只是能够进行打断 CPU,使 CPU 进入中断程序。)

4) 转换到外部晶体振荡器的操作方式。

也就是: 1. 打开外部晶体振荡器,因为它默认是关闭的。 2. 清除晶体振荡器失效标志 OFIFG 标志。 3. 等待 50us,等待外部晶体振荡器正常工作。 4. 检测晶体振荡器失效标志 OFIFG,如果它没有失效,那说明外部晶体振荡器正常工

//置一用或,清零用于。 do {

IFG1&=~OFIFG;//清除晶体振荡器失效标志 OFIFG 标志 for(a=0xff;a>0;a--);//等待 50us,等待晶体振荡器正常工作 } while((IFG1 & OFIFG));//当 OFIFG 等于 0 的时候结束,说明晶体振荡器正

//常工作了 while(1) { //这里就可以写用户的程序指令了。 } }

2. 子系统时钟(SMCLK);子系统时钟可以有两个来源:外部高速和 DCO。 3. 辅助系统时钟(ACLK);只有一个来源:外部低速。 他们都可以进行各自分频。

3) 时钟的寄存器。

1. DCOCTL

MSP430F149开发板说明

MSP430F149开发板说明一,MSP430F149自带硬件资源:(1) 基础时钟模块,包括1个数控振荡器(DCO)和2个晶体振荡器;(2) 看门狗定时器Watchdog Timer,可用作通用定时器:(3) 带有3个捕捉/比较寄存器的16位定时器Timer-A;(4) 带有7个捕捉/比较寄存器的16位定时器Timer_B;(5) 2个具有中断功能的8位并行端口:P1与P21(6) 6个8位端口:P1、P2、P3、P4、P5、P6。

(7) 模拟比较器COMPARATOR_A;(8) 12位A/D转换器;(9) 2通道串行通信接口(软件选择UART/SPI模式);(10) 1个硬件乘法器;(11) 60KB+256字节FLASH,2KBRAM。

二,MSP430F149开发板外围电路和硬件:1、两种可选供电方式(标准5V稳压器接口、USB接口)2、3.3V和5V电平接口3、一个兼容USB2.0规范、符合USB1.1规范的标准USB接口4、一个12864液晶显示屏接口5、一个JTAG仿真调试下载端口6、一个蜂鸣器7、一个NRF905射频通信模块接口8、一个8位的LED指示灯模块9、一个8路12-Bit模数转换(ADC)接口10、一个ZIGBEE(型号SZ05)无线通信接口11、一个IR红外串口无线通信模块12、一个8位数码管显示和4X4键盘模块13、一个L298电机驱动模块(可驱动两个电机)14、一个IIC模块包含:PCF8563时钟、LM75温度传感器、AT24C02数据存储15、一个单路输出10位DA转换芯片(TLC5615)16、一个标准的MAX3232接口17、一个的MAX485接口三,MSP430F149的性能MSP430系列单片机最显著的特点就是它的超低功耗。

在1.8—3.6V 电压、1MHz的时钟条件下运行。

耗电电流在0.1—400mA.之间,RAM 在节电模式耗电为0.1mA,等待模式下仅为0.7mA。

MSP430F149多点无线数据采集系统设计

MSP430F149多点无线数据采集系统设计数据收集是与传感器、信号处理、计算机一起形成现代检测技术基础的信息科学的重要领域。

我设计了一个基于MSP430的无线数据收集系统,并实现了解决有线数据采集模式移动性差和现场环境的电缆铺设极限的问题。

由数据采集器和一些数据集中器构成的无线主从数据获取网络,易于调整和平衡每个节点的通信距离。

广泛应用于工业数据采集之中,当它被用于狭窄的环境(例如隧道、封闭的走廊等)时,它可以减少了散射波的干扰,大大提升数据传输的可靠性。

利用MSP430F149和NRF905设计的多点无线数据采集系统,通过MSP430F149单片机片上ADC模块实现对外界模拟信号的采集,并将采集的模拟电压值转换成数字电压值。

对片外nRF905无线模块的控制实现数据在不同单片机之间的传输,最终通过单片机的串口传输到PC上显示,说明了链路控制方案和实际应用中应考虑的问题,最终达到无线多点无线数据采集的目的。

本次设计主要涉及到MSP430对UART和SPI串口的配置,单片机对无线模块的命令控制和数据经NRF905向中心节点传输,中心节点将多节点接收的数据通过串口向PC机传输。

无线数据收集(Wireless data acquisition)是指利用无线数据收集模块或设备记录及传输输出电流或者电压电压,无线数据采集器大多为便携型,可以将现场采集的数据实时发送给电脑。

与普通的便携式数据采集器相比,无线数据采集器提高了计算机的工作效率。

操作人员将数据从原始本地检查移动到远程控制中,并实时发送。

无线数据收集器的通信数据是实时高效的。

随着通信技术的蓬勃发展,人们对更先进便捷的通信技术的需要日益增大,摆脱有线网络的束缚实现无线通信始终是大家关心的问题,当今无线通信研究越来越热,应用非常广泛,使人与人之间的通信更加方便快捷,更具有市场发展前景。

在科学研究领域,数据采集与监测已成为一项越来越重要的检测技术。

在许多工业测控机械、医疗仪器以及消费电子产品中,都对数据采集系统的效率和能量消耗提出了更高的要求:即在满足微功耗、微型化的总体设计原则的基础上,又要能准确及时地反映现场采集数据的变化。

基于msp430f149和DS1302的12864时钟设计

基于msp430f149和DS1302的12864时钟设计本设计系统由主控模块、时钟模块、显示模块、红外解码控制模块、温度模块、掉电存储模块共6个模块组成,主控芯片使用TI系列msp430f149单片机,时钟芯片使用美国DALLAs公司推出的一种高性能、低功耗、带RAM的实时时钟DSl302。

采用DSl 302作为主要计时芯片,可以做到计时准确。

更重要的是,DSl302可以在很小电流的后备电源(2.5—5.5v电源,在2.5v时耗电小于300 nA)下继续计时,并可编程选择多种充电电流来对后备电源进行慢速充电,可以保证后备电源基本不耗电。

显示模块采用12864液晶,控制采用红外遥控器实现调整功能,温度模块采用DS18B20,掉电存储采用msp430f149内部自带的flash实现闹钟数据的掉电保存。

MSP430单片机概述MSP430 系列单片机是美国德州仪器(TI)1996 年开始推向市场的一种16 位超低功耗的混合信号处理器(Mixed Signal Pocessor)。

称之为混合信号处理器,主要是由于其针对实际应用需求,把许多模拟电路、数字电路和微处理器集成在一个芯片上,以提供“单片”解决方案。

MSP430 系列单片机的特点虽然MSP430系列单片机推出时间不是很长,但由于其卓越的性能,在短短几年时间里发展极为迅速,应用也日趋广泛。

MSP430系列单片机针对各种不同应用,包括一系列不同型号的器件。

主要特点有:1.超低功耗MSP430系列单片机的电源电压采用~低电压,RAM 数据保持方式下耗电仅,活动模式耗电250pA/MIPS(MIPS:每秒百万条指令数),IO输入端口的漏电流最大仅50nA。

MSP430系列单片机有独特的时钟系统设计,包括两个不同的时钟系统:基本时钟系统和锁频环(FLL和FLL+)时钟系统或DCO 数字振荡器时钟系统。

由时钟系统产生CPU和各功能模块所需的时钟,并且这些时钟可以在指令的控制下打开或关闭,从而实现对总体功耗的控制。

基于MSP430F149的单片机最小系统设计

基于MSP430F149的单片机最小系统设计0 引言单片机芯片配以必要的外部器件,一般包括电源供入及电源开关、复位电路、晶振、输入输出电路等就能构成最小系统。

MSP430F149 芯片是美国TI 公司推出的超低功耗微处理器,有60KB+256 字节FLASH,2KBRAM,包括基本时钟模块、看门狗定时器、带 3 个捕获/比较寄存器和PWM 输出的16 位定时器、带7 个捕获/比较寄存器和PWM 输出的16 位定时器、2 个具有中断功能的8 位并行端口、4 个8 位并行端口、模拟比较器、12 位A/D 转换器、2 个串行通信接口等模块。

MSP430F149 芯片具有如下特点:1)功耗低:电压2.2V、时钟频率1MHz 时,活动模式为200μA;关闭模式时仅为0.1A,且具有5 种节能工作方式。

2)高效16 位RISC-CPU,27 条指令,8MHz 时钟频率时,指令周期时间为125ns,绝大多数指令在一个时钟周期完成;32kHz 时钟频率时,16 位MSP430 单片机的执行速度高于典型的8 位单片机20MHz 时钟频率时的执行速度。

3)低电压供电、宽工作电压范围:1.8~3.6V;4)灵活的时钟系统:两个外部时钟和一个内部时钟;5)低时钟频率可实现高速通信;6)具有串行在线编程能力;7)强大的中断功能;8)唤醒时间短,从低功耗模式下唤醒仅需6μs;9)ESD 保护,抗干扰力强;10)运行环境温度范围为-40~+85℃,适合于工业环境。

MSP430 系列单片机的所有外围模块的控制都是通过特殊寄存器来实现的,故其程序的编写相对简单。

编程开发时通过专用的编程器,可以选择汇编或C 语言编程,IAR 公司为MSP430 系列的单片机开发了专用的C430 语言,可以通过WORKBENCH 和C-SPY 直接编译调试,使用灵活简单。

1 系统总体设计最小系统是由保证处理器可靠工作所必须的基本电路组成的,主要包括电源电路、时钟电路、复位电路、通信接口电路、数据存储电路组成,其硬件框图如图1 所示。

【设置】基于msp430f149和DS1302的12864时钟设计

【关键字】设置基于msp430f149和DS1302的12864时钟设计本设计系统由主控模块、时钟模块、显示模块、红外解码控制模块、温度模块、掉电存储模块共6个模块组成,主控芯片使用TI系列msp149单片机,时钟芯片使用美国DALLAs 公司推出的一种高性能、低功耗、带RAM的实时时钟DSl302。

采用DSl 302作为主要计时芯片,可以做到计时准确。

更重要的是,DSl302可以在很小电流的后备电源(2.5—5.5v 电源,在2.5v时耗电小于300 nA)下继续计时,并可编程选择多种充电电流来对后备电源进行慢速充电,可以保证后备电源基本不耗电。

显示模块采用12864液晶,控制采用红外遥控器实现调整功能,温度模块采用DS18B20,掉电存储采用msp149内部自带的flash实现闹钟数据的掉电保存。

MSP430单片机概述MSP430 系列单片机是美国德州仪器(TI)1996 年开始推向市场的一种16 位超低功耗的混合信号处理器(Mixed Signal Pocessor)。

称之为混合信号处理器,主要是由于其针对实际应用需求,把许多模拟电路、数字电路和微处理器集成在一个芯片上,以提供“单片”解决方案。

1.1 MSP430 系列单片机的特点虽然MSP430系列单片机推出时间不是很长,但由于其卓越的性能,在短短几年时间里发展极为迅速,应用也日趋广泛。

MSP430系列单片机针对各种不同应用,包括一系列不同型号的器件。

主要特点有:1.超低功耗MSP430系列单片机的电源电压采用1.8~3.6V低电压,RAM 数据保持方式下耗电仅0.1uA,活动模式耗电250pA/MIPS(MIPS:每秒百万条指令数),IO输入端口的漏电流最大仅50nA。

MSP430系列单片机有独特的时钟系统设计,包括两个不同的时钟系统:基本时钟系统和锁频环(FLL和FLL+)时钟系统或DCO 数字振荡器时钟系统。

由时钟系统产生CPU和各功能模块所需的时钟,并且这些时钟可以在指令的控制下打开或关闭,从而实现对总体功耗的控制。

msp430f149 TIMERA的几点说明

TACTL|=TASSEL_1+TACLR+ID0+ID1+MC0;//选择ACLK的8分频作为定时器的时钟,定时器为增加模式

//SMCLK+TimerA_Clear+8分频+增加模式+中断使能

CCTL0 = CCIE; //使能CCR0中断

CCIE:This bit enables the interrut request of the corresponding CCIFG flag

增计数模式。(产生两个中断标志)

当计数到TACCR0的时候,产生中断标志位CCIFG;而当TACCR0变为0时,计数器溢出,产生中断标志位AIFG

使用不同中断标志,程序不一样:

/************************

溢出中断,TAIE使能,中断入口也不一样

************************/

//定时初始化

void int_timer(void)

{ //注:宏定义TASSEL_1=TASSEL0

TACCR0=2047;//定时0.5s

}

#pragma vector = TIMERA0_VECTOR

__interrupt void Timer_A (void)

{

P2OUT ^= 0xff; //P2口输出取反

}

break;

default: break;

}

}

/************************

CCIFG中断,CCIE使能 中断入口也不一样

************************/

//定时初始化

MSP430F149中文资料--部分

基于MSP430F149的GPS

(芯片篇)

1、系统功能框图

2芯片资料:

MSP430F149:

低电源电压范围:1.8~3.6V

超低功耗:待机模式:1。

6uA 关闭模式(RAM保持):0。

1uA 活动模式:280uA at 1MHz,2。

2V

5种省电模式

6us内从待机模式唤醒

16位RISC结构,125ns指令周期

带内部参考,采样保持和自动扫描特性的12位A/D转换器

有7个捕获/比较寄存器的16位定时器Timer_B 有3个捕获/比较寄存器的16位定时器Timer_A

片内集成比较器

串行在线编程,无需外部编程电压,安全熔丝可编程代码保护。

器件系列包括:–MSP430F133:8KB+256B闪速存储器,256B的RAM –MSP430F135:16KB+256B闪速存储器,512B的RAM –MSP430F147,MSP430F1471:32KB+256B闪速存储器,1KB的RAM –MSP430F148, MSP430F1481:48KB+256B闪速存储器,2KB的RAM –MSP430F149, MSP430F1491:60KB+256B闪速存储器,2KB的RAM

可用封装:64脚方形扁平封装(QFP).

功能框图。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DCOR DIVS0 DIVS1 SELS DIVM0 DIVM1 SELM0 SELM1

(0x01) /* DCO 外部电阻使能 */ (0x02) /* SMCLK 2 分频 */ (0x04) /* SMCLK 4 分频*/ (0x08) /* SMCLK 时钟源选择 0:DCOCLK / 1:XT2CLK/LFXT1CLK */ (0x10) /* MCLK 2 分频 */ (0x20) /* MCLK 4 分频 */ (0x40) /* MCLK 时钟源选择 01:DCOCLK*/ (0x80) /* MCLK 时钟源选择 10:有 XT2 则选择 XT2CLK 否则选择 LFXT1CLK*/

/*************************************************

*BCSCTL2 控制位定义

**************************************************/

#define #define #define #define #define #define #define #define

/* Modulation Bit 0 */ /* Modulation Bit 1 */ /* Modulation Bit 2 */ /* Modulation Bit 3 */ /* Modulation Bit 4 */ /* DCO Select Bit 0 */ /* DCO Select Bit 1 */ /* DCO Select Bit 2 */

0——禁止中断

1——允许中断

说明:IE1 中其余位可能被其它模块使用。

5、IFG1:中断标志寄存器 1

7

6

5

4

3

OFIFG:晶振错误中断标志位。

0——无中断发生

1——有中断发生

2

1

0

OFIE

rw-0

2

1

0

OFIFG

rw-1

说明:1、IFG1 中其余位可能被其它模块使用。 2、OFIG 必须通过软件来清零,在没有 XT2 的器件上,LFXT1 低频模式下不能 被清零(只要 XT2 或 LFXT1 高频模式停止,晶振失效侦测电路立刻侦测到 晶振失效)

00——选择 DCOCLK

01——选择 DCOCLK

10——选择 XT2CLK(若片上有 XT2),若没有则选择 LFXT1CLK

11——选择 LFXT1

DIVMx:MCLK 分频控制位

00——1 分频

01——2 分频

10——4 分频

11——8 分频

SELS:SMCLK 时钟源选择控制位。

0——选择 DCOCLK

§2.3 MSP430F149 基本时钟系统应用

一、基本时钟系统寄存器控制位定义

基本时钟模块寄存器相应控制位在头文件 msp430x14x.h 中定义,各相关定义如下:

#define DEFC(name, address) sfrb name = address;

#define DEFW(name, address) sfrw name = address;

/****************************************************************

*DCOCTL 控制位定义,设定 DCO 频率

****************************************************************/

选择 8 个离散的频率阶中选择哪一个(每一个名义频率范围都可由 DCOx 划分 8 个小范围)。

MODx:调制系数选择位,这些位用来决定在 32 个 DCO 时钟周期中 tDCO+1 占多少个。

注意:当 MODx=0 时调制器关闭,DCOx=7 时,由于此时没有下一个更高的频率范围 fDCO+1

可用,因此 MODx 无效不可用。(t=(32-MODx)×tDCO+MODx×tDCO+1)

1——选择 XT2CLK(若片上有 XT2),若没有则选择 LFXT1CLK。

DIVSx:SMCLK 分频控制位

00——1 分频

01——2 分频

10——4 分频

11——8 分频

DCOR:DCO 振荡电阻选择控制位

0——选择内部电阻

1——选择外部电阻

4、IE1:中断使能寄存器 1

7

6

5

4

3

OFIE:晶振错误中断使能控制位。

(0x0057u) /* Basic Clock System Control 1 */ , BCSCTL1_) /*定义一个字节特殊功能寄存器 BCSCTL1*/ (0x0058u) /* Basic Clock System Control 2 */ , BCSCTL2_) /*定义一个字节特殊功能寄存器 BCSCTL2*/

/* DCO 名义频率范围选择 1 */ /* DCO 名义频率范围选择 2 */ /* DCO 名义频率范围选择 4 */ /* XT5V 总是为 0 */ /* ACLK 2 分频 */ /* ACLK 4 分频 */ /* LFXT1CLK 0:低频/ 1: 高频 */ /* XT2CLK 开关,0:开启,1:关闭*/ /* ACLK 1 分频 */ /* ACLK 2 分频 */ /* ACLK 4 分频 */ /* ACLK 8 分频 */

§2.2 MSP430F149 基本时钟系统寄存器 一、基本时钟模块寄存器

寄存器 DCO 控制寄存器 基本时钟系统控制器 1 基本时钟系统控制器 2 中断使能寄存器(特殊功能寄存器)

中断标致寄存器(特殊功能寄存器)

缩写形式

DCOCTL BCSCTL1 BCSCTL2

IE1 IFG1

类型

读/写 读/写 读/写 读/写 读/写

#define DEFC( #define DEFC( #define DEFC(

DCOCTL_ DCOCTL BCSCTL1_ BCSCTL1 BCSCTL2_ BCSCTL2

(0x0056u) /* DCO Clock Frequency Control */ , DCOCTL_) /*定义一个字节特殊功能寄存器 DCOCTL*/

二、基本时钟模块构成 三个时钟源: LFXT1CLK:低频/高频振荡器,使用 32768Hz 手表晶振或 450KHz~8MHz 标准晶体或振荡器。 XT2CLK:可选高频振荡器,使用 450KHz~8MHz 标准晶体、振荡器或外部 时钟。 DCOCLK:内部 RC 数控振荡器。 三个时钟信号: ACLK:辅助时钟信号,LFXT1 时钟源经 1,2,4,8 分频得到,由软件选择作

DIVM_0 DIVM_1 DIVM_2 DIVM_3

(0x00) (0x10) (0x20) (0x30)

#define #define #define #define

DIVS_0 DIVS_1 DIVS_2 DIVS_3

(0x00) (0x02) (0x04) (0x06)

/* SMCLK /* SMCLK /* SMCLK /* SMCLK

1 分频*/ 2 分频*/ 4 分频 */ 8 分频*/

#define #define #define #define

第二章 MSP430F149 基本时钟系统 本章主要内容:

一、MSP430F149 基本时钟系统组成 二、MSP430F149 基本时钟寄存器 三、MSP430F149 基本时钟系统应用

本章重点内容:

MSP430F149 基本时钟寄存器

§2.1 MSP430F149 基本时钟系统组成

一、基本时钟模块的特点: 1、支持低系统开销、低功耗; 2、产生 3 个系统时钟信号:ACLK、SMCLK、MCLK 3、通过软件配置选择系统性能和低功耗的最佳平衡; 4、在软件控制下配置实现无外部元件,用一个外部电阻,一个或两个外部晶体, 或者外部振荡器运行;

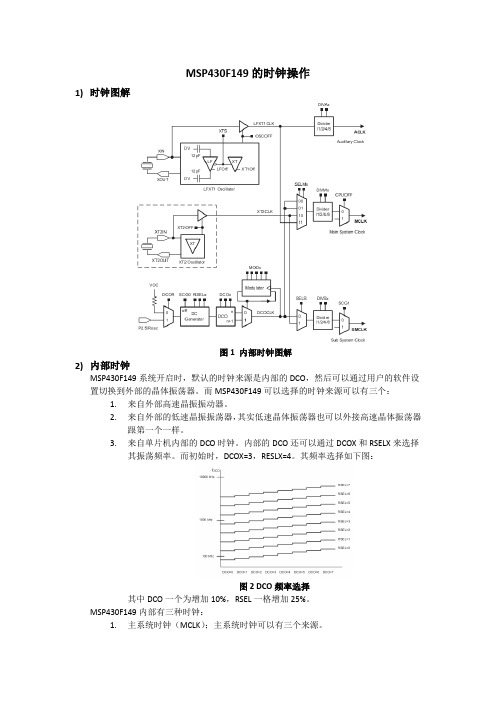

图 2-2 典型的 DCOx 范围和 RSELx 阶

3、BCSCTL2:基本时钟系统控制寄存器 2 (负责 MCLK、SMCLK 时钟源和分频选择)

7

6

SELMx

rw-0

rw-0

5

4

DIVMx

rw-0

rw-0

3 SE-0

rw-0

0 DCOR rw-0

SELMx:MCLK 时钟源选择控制位。

为各个低速外设模块时钟。 SMCLK:子系统时钟信号,由软件选择 LFXT1CLK、XT2CLK(如果可用)、DCOCLK

时钟源,经 1,2,4,8 分频得到,由软件选择作为各个外设模块时钟。 MCLK:主时钟信号,由软件选择 LFXT1CLK、XT2CLK(如果可用)、DCOCLK 时

钟源,经 1,2,4,8 分频得到,由软件选择作为 CPU 和系统时钟。 基本时钟模块结构图如图 2-1 所示:

……

/************************************************************

* Basic Clock Module

************************************************************/

#define __MSP430_HAS_BASIC_CLOCK__ /* Definition to show that Module is available */

图 2-1 MSP430F149 基本时钟模块

系统产生一个 PUC 后 DCOCLK 作为 MCLK、SMCLK 时钟源,频率为 800KHz; ACLK 时钟源为 LFXT1CLK 并且默认为低频模式。

基本时钟可由软件在程序执行的任何期间进行配置。例如: BCSCTL1=RSEL2+RSEL1+RSEL0;//设置 DCO 最大频率 DCOCTL=DCO2+DCO1+DCO0;//设置 DCO 最大频率