微纳电子器件3-1(总第九次课)

集成电路芯片封装技术培训课程(ppt-35页)全

微电子技术发展对封装的要求

四、高密度化和高引脚数

高密度和高I/O数造成单边引脚间距缩短、封装难

度加大:焊接时产生短路、引脚稳定性差

解决途径:

采用BGA技术和TCP(载带)技术

成本高、难以进行外观检查等。

微电子技术发展对封装的要求

五、适应恶劣环境

密封材料分解造成IC芯片键合结合处开裂、断路

解决办法:寻找密封替代材料

Ceramic

Ceramic or

Thin Film on Ceramic

Thin Film on PWB

PWB-D

•Integration to

BEOL

•Integration in

Package level

PWB-Microation at

System level

1、电源分配:传递电能-配给合理、减少电压损耗

2、信号分配:减少信号延迟和串扰、缩短传递线路

3、提供散热途径:散热材料与散热方式选择

4、机械支撑:结构保护与支持

5、环境保护:抵抗外界恶劣环境(例:军工产品)

确定封装要求的影响因素

成本

外形与结构

产品可靠性

性能

类比:人体器官的构成与实现

微电子封装技术的技术层次

芯片,但两类芯片的可靠性和成本不同。

封装材料

芯片封装所采用的材料主要包括金属、陶瓷、

高分子聚合物材料等。

问题:如何进行材料选择?

依据材料的电热性质、热-机械可靠性、技术和

工艺成熟度、材料成本和供应等因素。

表1.2-表1.4

封装材料性能参数

介电系数:表征材料绝缘程度的比例常数,相对值,通常介

电系数大于1的材料通常认为是绝缘材料。

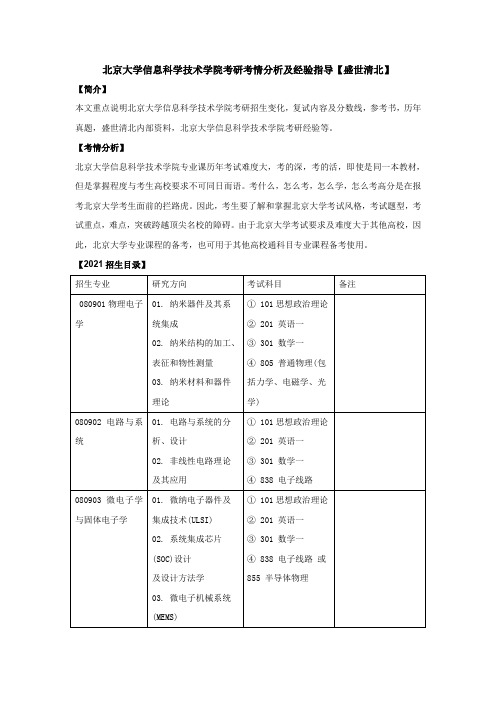

北京大学信息科学技术学院考研考情分析及经验指导【盛世清北】

北京大学信息科学技术学院考研考情分析及经验指导【盛世清北】【简介】本文重点说明北京大学信息科学技术学院考研招生变化,复试内容及分数线,参考书,历年真题,盛世清北内部资料,北京大学信息科学技术学院考研经验等。

【考情分析】北京大学信息科学技术学院专业课历年考试难度大,考的深,考的活,即使是同一本教材,但是掌握程度与考生高校要求不可同日而语。

考什么,怎么考,怎么学,怎么考高分是在报考北京大学考生面前的拦路虎。

因此,考生要了解和掌握北京大学考试风格,考试题型,考试重点,难点,突破跨越顶尖名校的障碍。

由于北京大学考试要求及难度大于其他高校,因此,北京大学专业课程的备考,也可用于其他高校通科目专业课程备考使用。

【2021招生目录】【院系招生变化】对比北京大学信息科学技术学院2021年与2020年招生目录,总结出:1、招生专业不变;2、各专业研究方向不变;3、信号与信息处理、计算机系统结构、计算机软件与理论、计算机应用技术专业的招生目录备注增加招生计划人数情况;4、考试科目由801计算机专业基础变为408计算机学科专业基础综合;912半导体物理或934 数字与模拟电路变更为838电子线路或 855半导体物理;5、统招人数发生变化:电磁场与微波技术专业的招生人数增加1人,通信与信息系统专业招生人数增加1人,信号与信息处理专业招生人数减少1人,计算机软件与理论专业招生人数增加3人,其他专业招生人数不变;6、科目代码发生变化,即866变更为838,806变更为805,总数,北大信息科学技术学院招生变化较大,备考考生注意报考。

【复试分数线】【复试内容】一、复试规则1. 复试基本内容:包括专业知识、科研能力、逻辑思维与表达能力、英语听力及口语测试等。

2. 成绩权重:初试成绩占总成绩的50%,复试成绩占总成绩的50%。

3. 外语听力及口语测试均在复试中进行,成绩计入复试总成绩。

4. 总成绩计算公式:总成绩=50%×初试总成绩/5+复试成绩(百分制)×50%。

微纳光电子学 教学大纲

微纳光电子学一、课程说明课程编号:140510Z10课程名称:微纳光电子学/ Micro- and Nano- Optoelectronics课程类别:专业核心课程学时/学分:48/3先修课程:固体物理、信息光学、光电子技术适用专业:光电信息科学与工程教材、教学参考书:1.原荣,邱琪编著.光子学与光电子学.北京: 机械工业出版社.2014年;2. 傅竹西编著.固体光电子学.合肥: 中国科学技术大学出版社(第2版).2012年;3. 周治平著.硅基光电子学.北京: 北京大学出版社.2012年;4. 刘旭等编著.光电子学.杭州: 浙江大学出版社.2014年。

二、课程设置的目的意义光子学、光电子学、和光电子技术是目前信息时代不可或缺的关键技术,产生了大量的光与电相结合的新型器件如手机、电脑、激光雷达、导航设备、光电探测器、太阳能电池等等,不一而足,为人们的生活和工作提供了极大的便利。

光子与电子的结合与相互调制是今后信息技术发展的一个重要方向,特别是由于半导体技术和微纳制作技术的兴起,光电子器件朝功能更强、尺寸更小的方向发展。

本课程重点讲述特征尺寸在微米或纳米级别的光与电相结合的新型光电子器件及其原理,结构、和应用等,使光电信息科学与工程等专业的学生能够了解和掌握有关微纳光电子学方面的最新进展和知识,为更好地适应以后相关的学习深造和研发工作打下坚实的专业基础。

三、课程的基本要求知识:本课程从光学原理如光的传播、干涉、衍射、偏振、双折射、光电效应、电光效应、非线性效应等出发,重点讲述所涉及到的当前微纳光电子学领域基本的、主要的、常用的器件,如波导、半导体激光器、滤波器、调制器、探测器、CCD、探测器等的原理、结构、及应用等。

能力:要求学生学习这些器件的基本结构、工作原理、主要特性及应用等知识时,不仅需了解微纳光电子器件的基本知识,还要能够举一反三、触类旁通、和具备进一步深入学习、研究及设计微纳光电子器件的能力,并能将器件知识与实际应用相结合。

微纳光电子系统_第二章微纳光电器件简介

16

2010-9-5

32×32微测辐射热计SEM照片

×200 倍

×500倍

测试系统原理图

17

2010-9-5

像元编号

像元黑体响应电压 (µ V)

像元响应率 (V/W) 1.52×104 1.23×104 1.11×104 1.46×104 1.42×104 1.35×104 0.99×104 1.44×104 1.56×104 1.28×104

读出电路 X 向电极

11

2010-9-5

微桥结构设计

• 热学设计 低热导和合适的热响应时间 • 光学设计 提高填充系数和红外吸收率 • 力学设计 确保结构的机械力学稳定性

1. 00 0. 90

吸 0. 70 收 0. 60 率 0. 50 ( 0. 40 %) 0. 30

0. 20 0. 10 0. 00 1. 0 3. 0 5. 0 7. 0 9. 0 11. 0 13. 0 15. 0

硅 3.4

400μm 4μm 1 8 2π 1.67μm 1.96

硅 3.4

400μm 4μm 1 8 1.7 π 1.42μm 2.35

硅 3.4

400μm 4μm 1 8 0.95π 0.798μm 2.35

石英 1.47

400μm 0.5μm 1 8 2π 1.06μm 4.5

性能测试

衍射效率

微测辐射热计物理模型

微测辐射热计热学模型

热绝缘微桥结构

V dV I 0 dR dT I 0 R = dQ dT dQ Geff

微桥结构 50 μm Y 向电极 红外 辐射 0.5μm

Gleg kleg

Aleg l

探测器响应率与探测 器和衬底间的热导G 呈反比,利用微桥结 构降低二者间的热导

[精品]数字集成电路分析与设计教学大纲.doc

![[精品]数字集成电路分析与设计教学大纲.doc](https://img.taocdn.com/s3/m/14361b0afab069dc5122014d.png)

数字集成电路分析与设计一、课程基本情况课程编号40260103开课单位微纳电子学系课程名称中文名称数字集成电路分析与设计英文名称Digital Integrated Circuit Analysis and Design教学目的与重点教学目的:1)让学生掌握数字集成电路的工作原理与分析方法2)让学生掌握数字集成电路与系统的设计流程和基本方法3)培养学生实际设计数字集成电路与系统的能力教学重点:1) CMOS反相器的特性,数字集成电路分析与设计的关键问题2)组合逻辑链的性能优化3)互连线的延时模型与分析4)同步时序电路的分析和设计5)数据通路运算单元的分析与设计6)存储器的工作原理的理解与分析课程负责人刘雷波吴行军课程类型□文化素质课□公共基础课□学科基础课□专业基础课■专业课□其它教学方式■讲授为主□实验/实践为主□专题讨论为主□案例教学为主□自学为主□其它授课语言■中文口中文+英文(英文授课>50%)□英文□其他外语学分学时学分 3 总学时48考核方式及成绩评定标准作业:15%,课程设计:15%,期中考试(闭卷):30%,期末考试(闭卷):40%教材及主要参考书中文外文教材数字集成电路一电路、系统与设计(第二版),JanM.Rabaey等著,周润德等译,电子工业出版社。

Jan M. Rabaey etc. “Digital Integrated Circuits , A Design Perspective (Second Edition)", Prentice Hall , 2003.主要参考书CMOS数字集成电路一分析与设计(第3版),Sung-Mo Kang等著,王志功等译,清华大学出版社(影Sung-Mo Kang, Yusuf Leblebici,"CMOS Digital IntegratedCircuits-Analysis and Design(ThirdEdition)".三、课程主要教学内容9.4高级互连技术9. 5综述9.6总结第10章存储器(6学时)(教材第12章)10.1分类10.2结构10.3内核--- 存储单元和阵列10.4外围电路10.5可靠性10.6总结。

微电子器件

微电子器件1. 概述微电子器件是一种尺寸远小于传统电子器件的电子元件。

它们在微纳尺度下制造,通常采用半导体材料(如硅)制成。

微电子器件在现代科技中起着至关重要的作用,广泛应用于电子、通信、计算机、医疗和能源等领域。

2. 基本概念微电子器件的尺寸通常在微米至纳米级别,其特点包括: - 小尺寸:微电子器件通常具有毫米或更小的尺寸,这使得它们可以在集成电路中实现高密度布局。

- 快速响应:由于尺寸小,微电子器件的响应速度通常很快,这使得它们适用于高速信号处理和通信应用。

- 低功耗:微电子器件通常具有低功耗特性,这使得它们在便携设备和低功耗电路中非常受欢迎。

3. 常见的微电子器件3.1 MOSFET金属-氧化物-半导体场效应晶体管(MOSFET)是一种常见的微电子器件。

它由金属栅极、绝缘层和半导体材料组成,通过调节栅极电压来控制电流。

MOSFET广泛应用于集成电路和数字电子领域。

3.2 MEMS微机电系统(MEMS)是一种将机械、电子和传感器结合在一起的微型系统。

它由微型机械结构和微电子器件组成。

MEMS通常用于传感、加速度计、惯性导航和微型机器人等领域。

3.3 CCD电荷耦合器件(CCD)是一种用于图像传感和成像的微电子器件。

它通过将光信号转换为电荷进行图像采集和存储。

CCD广泛应用于数码相机、摄像机和天文观测等领域。

3.4 LED发光二极管(LED)是一种能够将电能转换为光能的微电子器件。

LED具有高效率、长寿命和低功耗的优点,因此广泛应用于照明、显示和通信等领域。

4. 微电子器件制造技术微电子器件的制造通常涉及以下关键技术: - 硅工艺:硅工艺是制造微电子器件最常用的方法之一,它涉及光刻、薄膜沉积、扩散和离子注入等过程。

- 薄膜技术:微电子器件通常需要在半导体表面上沉积各种功能膜层,薄膜技术是实现这一目标的重要方法。

- 纳米制造技术:纳米制造技术是制造纳米尺度器件的关键技术,包括纳米光刻、纳米精细加工和纳米材料制备等方面。

《微电子技术》课件

微电子技术用于制造军事设备 ,如导弹制导系统、雷达、通

信设备等。

微电子技术的发展趋势

纳米技术

随着芯片上元件尺寸的 不断缩小,纳米技术成 为微电子技术的重要发

展方向。

3D集成

通过将多个芯片垂直集 成在一起,实现更高的

性能和更低的功耗。

柔性电子

柔性电子是将电子器件 制造在柔性材料上的技 术,具有可弯曲、可折

将杂质元素引入半导体材料中的 技术。

离子注入掺杂

利用离子注入机将杂质离子注入 到半导体材料中的技术。

化学气相掺杂

利用化学气相沉积的方法,将含 有杂质元素的化合物沉积到半导

体材料中的技术。

04

集成电路设计

集成电路设计流程

需求分析

明确设计要求,分析性能指标,确定设计规 模和复杂度。

逻辑设计

根据规格说明书,进行逻辑设计,包括算法 设计、逻辑电路设计等。

《微电子技术》 ppt课件

contents

目录

• 微电子技术概述 • 微电子器件 • 微电子工艺技术 • 集成电路设计 • 微电子封装技术 • 微电子技术发展面临的挑战与机遇

01

微电子技术概述

微电子技术的定义

微电子技术是一门研究在微小 尺寸下制造电子器件和系统的 技术。

它涉及到利用半导体材料、器 件设计和制造工艺,将电子系 统集成在微小尺寸的芯片上。

02

微电子技术领域的竞争非常激烈,企业需要不断提升自身的技

术水平和产品质量,以获得竞争优势。

客户需求多样化

03

客户需求多样化,要求企业提供更加定制化的产品和服务,以

满足不同客户的需求。

新材料、新工艺的机遇

新材料的应用

微纳电子器件制造技术的研究与应用

微纳电子器件制造技术的研究与应用近年来,微纳电子器件在电子工业中越来越受到重视,成为了求解当前热点问题的新选择。

浅谈微纳电子器件制造技术的研究与应用对于我们深入了解微纳电子器件的制造原理和应用场景,有着重要的意义。

一、微纳电子器件制造技术简要介绍微纳电子器件是指在微米甚至纳米级的范围内制造的电子元器件,主要采用微细加工技术和材料技术制造。

其制造涉及多个学科领域,包括微机电系统、材料科学与工程、化学工程、电子物理等。

微纳电子器件具有尺寸小、性能优良、功耗低、可靠性高等特点,具有广阔的应用前景。

微纳电子器件制造技术的研究主要分为以下几个方面:1.微电子加工技术微电子加工技术是微纳电子器件制造技术中的核心技术,包括半导体工艺和微机电系统工艺两大类。

常用的微电子加工技术有光刻、蒸镀、离子注入、化学蚀刻等。

这些技术的优化和改进,对于微纳电子器件的生产与提升具有重要意义。

2.材料技术微纳电子器件所使用的材料不同于传统电子器件,需要具有特殊的性质和特点。

微纳电子器件制造中常用的材料有氮化硅、氮化铝、氮化镓等。

这些材料的制备、加工和性能优化,是微纳电子器件制造中重要研究方向之一。

3.模拟设计技术微纳电子器件的复杂性和成本高昂,需要采用模拟设计工具对其进行仿真,在实际制造前进行模型验证,以降低失败率并提高成功率。

常用的仿真软件有COMSOL Multiphysics等。

4.封装与测试技术微纳电子器件在制造完成后,需要进行封装和测试,以确保其性能和可靠性。

因器件的封装和测试通常引起信号传输的损失,因此封装和测试技术的研究成为了微纳电子器件制造的重要方向之一。

二、微纳电子器件制造技术的应用场景1.通信和通讯微波通讯、红外通讯、量子通讯等都是微纳电子器件在通信行业中的应用。

此外,微纳电子器件还被应用于数字通讯、光通讯、射频通讯等领域。

2.能源微纳电子器件在太阳能电池领域的应用可将太阳辐射能转化为电能,实现了绿色能源利用。

清华大学微电子本科生培养课程设置

•一、简介微纳电子系本科生一级学科名称为电子科学与技术,二级学科名称为微电子学。

二、课程设置课程编号:30260093 课程名称:固体物理学课程属性:专业核心课开课学期:09秋任课教师:王燕内容简介:固体物理学是固体材料和固体器件的基础。

该课程主要研究晶体的结构及对称性,晶体中缺陷的形成及特征,晶格动力学,能带理论的基础知识以及晶体中的载流子输运现象等。

是微纳电子专业的核心课。

课程编号:40260103 课程名称:数字集成电路分析与设计课程属性:专业核心课开课学期:09秋任课教师:吴行军内容简介:本课程从半导体器件的模型开始,然后逐渐向上进行,涉及到反相器,复杂逻辑门(NAND,NOR,XOR),功能模块(加法器,乘法器,移位器,寄存器)和系统模块(数据通路,控制器,存储器)的各个抽象层次。

对于这些层次中的每一层,都确定了其最主要的设计参数,建立简化模型并除去了不重要的细节。

课程编号:40260173 课程名称:数字集成电路分析与设计(英)课程属性:专业核心课开课学期:09秋任课教师:刘雷波内容简介:数字集成电路的分析与设计,包括:CMOS反相器、组合和时序逻辑电路分析与设计、算术运算逻辑功能部件、半导体存储器的结构与实现、互连线模型与寄生效应的分析。

并介绍常用数字集成电路的设计方法和流程。

课程编号:30260072 课程名称:微电子工艺技术课程属性:专业核心课开课学期:09秋任课教师:岳瑞峰内容简介:本课程授课目的是使学生掌握微电子制造的各单项工艺技术,以及亚微米CMOS集成电路的工艺集成技术。

本课程讲授微电子制造工艺各单项工艺的基本原理(包括氧化、扩散、离子注入、薄膜淀积、光刻、刻蚀、金属化工艺等),并介绍常用的工艺检测方法和MEMS加工技术、集成电路工艺集成技术和工艺技术的发展趋势等问题。

另通过计算机试验,可学习氧化、扩散、离子注入等工艺设备的简单操作和模拟。

课程编号:40260054 课程名称:半导体物理与器件课程属性:专业核心课开课学期:09春任课教师:许军内容介绍:主要讲授半导体材料的基本物理知识,半导体器件的工作原理以及现代半导体器件的新进展。

微纳电子器件的制备和应用

微纳电子器件的制备和应用随着科技的发展,微观世界日渐引人注目。

微电子技术的发展,使得人们对于电子器件的制造精度和功能性有了更高的要求。

微纳电子技术作为电子技术的新方向,将成为未来电子工业的重要组成部分。

本文将介绍微纳电子器件的制备过程和常见的应用。

一、微纳电子器件的制备过程微纳电子器件是通过利用微纳加工技术将电路设计转化为三维结构,纳米尺度的各种功能元件,如电阻、电容、管子、二极管、三极管等制备而成。

1.微纳加工技术微纳加工技术是微纳电子器件的核心技术之一,包括各种加工方法,如电子束曝光、光刻、湿法蚀刻、干法蚀刻、电化学加工、气溶胶沉积等。

其中,电子束曝光技术是微纳加工技术中最早、最成熟的技术之一,能够在微纳米尺度下实现高精度、高分辨率的器件制备。

2.相关技术微纳电子器件的制备还需要相关技术的支持,如精密仪器的设计和制造,材料科学的发展,电子学、物理学和计算机技术等综合运用。

这些技术的进步,不仅提高了微电子器件的制造精度,而且能够满足制造高质量器件的要求。

3.应用现在,已经有许多微纳电子器件被制造出来并应用到了各个领域。

比如,红外探测器、生物芯片、微型加速器、纳米滤网、烟雾探测器等,这些器件的应用程度已经高达了80%以上。

二、常见的微纳电子器件应用1.生物芯片生物芯片作为生物技术的重要应用,是一种集微电子技术和生物科学于一体的新型技术。

通过生物芯片,可以对微生物、DNA、蛋白质等生物体系进行检测和分析。

2.红外探测器红外探测器是一种分子结构、量子离子和原子谱学原理为基础的新型光学节目。

与其他光学检测方式相比,红外探测器具有相对非常特别的特性,如对物体的热辐射敏感,可测量物体的温度等。

红外探测器不仅可以应用到军事领域,如导弹、火控系统等,而且也可以用于民用领域,如夜视设备、红外报警器等。

3.微型加速器微型加速器是一种可以将带电粒子高速加速的装置,它可以应用于核物理分析、放射性检测、核废料处理、环境监测等多个领域。

微纳电子器件的设计及应用

微纳电子器件的设计及应用随着科技的发展,纳米级电子器件的应用越来越广泛。

微纳电子器件指的是在微米或纳米尺度下设计制造的电子器件,具有高性能、低功耗、低成本等优点。

其应用范围涵盖信息通信、医疗健康、能源环保、智能物联网等领域。

本文将介绍微纳电子器件的设计及应用。

一、微纳电子器件的设计微纳电子器件的设计是在微米或纳米级别下进行的,需要采用一些高级技术,并且要考虑到这些器件的特殊性质。

以下是一些常用的微纳电子器件设计技术。

1. 工艺制造工艺制造是微纳电子器件设计的重要一环。

在此过程中,需要采用先进的技术,比如光刻、氧化、金属蒸镀等,制造出所需的器件。

这些技术需要在非常高的精度下操作,以确保器件的性能和稳定性。

2. 模拟和数字信号处理模拟和数字信号处理是微纳电子器件设计的另一个重要环节。

模拟信号处理会涉及到耦合、噪声、伪信号等问题,而数字信号处理则会处理器件的复杂性和性能问题。

这两种信号处理技术需要采用相应的算法和模型,以优化器件的响应和性能。

3. 有限元分析有限元分析是微纳电子器件设计中常用的计算机辅助工具。

该技术利用有限元法来模拟器件的行为和特性。

在此过程中,需要采用一些先进的计算机软件和工具,以分析器件在不同状况下的表现,从而优化微纳器件的性能。

二、微纳电子器件的应用微纳电子器件已经被应用于多个领域中。

1. 信息通信微纳电子器件在信息通信领域中被广泛使用。

举个例子,微纳光纤滤波器可以用于分析和处理光通信中的信号。

这些器件可以被制造成非常小的尺寸,并可以处理高速、大量的数据。

再比如,微纳电子器件可以使用在制造晶体管和LED等器件中。

2. 医疗健康微纳电子器件在医疗和健康领域中也有广泛的应用。

例如,微型无创血糖仪可以通过皮肤获得血液样本而无需刺破皮肤;微型药物传递系统可以将药物递送到需要治疗的地方,从而减少不必要的损伤和疼痛。

3. 能源环保微纳电子器件可以被用于能源生产和环保中。

例如,太阳能电池板可以通过微纳器件设计,以最高效率获取和存储能源。

微电子专业介绍及就业方向1 (1)

微电子专业毕业生应具备 的知识和能力

1.掌握数学、物理等方面的基本理论和基本知识;

2.掌握固体物理学、电子学和VLSI设计与制造等方面的基本理论和基 本知识,掌握集成电路和其它半导体器件的分析与设计方法,具有独 立进行版图设计、器件性能分析和了解VLSI工艺流程的基本能力; 3.了解相近专业的一般原理和知识; 4.了解VLSI和其它新型半导体器件的理论前沿、应用前景和最新发展 动态,以及电子产业发展状况; 5.掌握资料查询、文献检索及运用现代信息技术获取相关信息的基本 方法;具有一定的实验设计,创造实验条件,归纳、整理、分析实验 结果,撰写论文,参与学术交流的能力。

光纤通信集成电路设计(王志功 教授)

模拟集成电路设计(陈莹梅 副教授)

东大信息科学与工程学院招生目录

电路与系统方向: 01 超高速集成电路研究 02 射频、微波集成电路研究 03 光电集成电路研究 04 通讯网络VLSI研究 专业课:专业基础综合(信号与系统、数字电路) 复试科目: 模拟电子线路

要求学习者掌握半导体物理、器件与工艺的理论和技术;掌

握集成器件的设计方法与制造工艺;熟练使用计算机,有较 强的科研能力和一定的解决实际问题的能力。

既需要丰富的物理基础知识,也能熟练操作微电子器件测试

实验。

微电子的研究方向

微电子的研究方向分为两大类:工艺和设计。

细分为: 电路设计方向; 电路的模拟工具(CAD方向); 电路构成的系统(SOC或系统方向);

国内微电子领域知名高校

1. 清华 2. 北大 3. 复旦大学

4. 上海交通大学

5. 华中科技大学 6. 浙江大学

7. 东南大学 (指东南无线电系的射光所,有两大导师:王志功\黄凤仪,其 中王志功为国内射频集成电路第一人。 )

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微纳电子器件

陈 军

课程内容简介

• 微纳电子器件发展

1. 2. 3. MEMS/NEMS器件 柔性微纳电子器件 真空微纳电子器件

1. 硅基CMOS器件 的发展 2. 小尺寸硅基 CMOS器件面临 的问题 3. 硅基纳米CMOS 器件技术 1. 碳纳米管和纳米线器件 2. 石墨烯纳米电子器件 3. 其它新型纳电子器件

1

答 疑

• 动态功耗与短路功耗区别 • DRAM芯片面积为什么要增大? • 冗余技术如何实现?

第三章 硅基纳米CMOS器件技术

2

小尺寸MOS器件的物理效应

• 栅氧化层减薄的限制 • 短沟道效应(SCE) • DIBL效应与源漏穿通及次开启 • 热载流子效应(HCE) • 栅感应漏极漏电(GIDL) • 源漏区串联电阻的影响 • 迁移率的退化和漂移速度饱和 • 量子效应的影响 • 杂质随机分布的影响: discrete effects • 软失效 • ……………..

器件尺寸缩小造成的副效应分类

• 一类是灾难性的,即影响器件的功能和可靠性

• Heat death • 热载流子效应 • 软失效效应

• 一类是尺寸缩小并不能改善VLSI的性能,而是起 反作用

• 连线RC延迟 • 单个器件的性能下降

– 载流子速度饱和 – S/D的串联电阻

6

3

Economics: factory cost also follows Moore’s law!

Limits

4

如何解决器件缩小受到的限制? 如何集成更多的器件?

解决方案

• 器件层面

– 新材料,新结构,新工艺

• 芯片系统层面

– MCM(多芯片组装) – 多核(Multicore MPU) – SiP(System in Package) – 3D-IC(三维集成)

• 相关问题:散热:微流体

5

解决方案

• 器件层面

– 新材料,新结构,新工艺

• 芯片系统层面

– MCM(多芯片组装) – 多核(Multicore MPU) – SiP(System in Package) – 3D-IC(三维集成)

• 相关问题:散热:微流体

新材料与新结构举例

• 新材料

– new channel materials: strained Si, Si/SiGe heterostructures – new gate insulators: high-K dielectric, such as HfO – new gate conductors: metal gate, such as fully silicided gate(FUSI)

• 新器件结构

– SOI, double gate, trigate (FInFET、nanowire)

6

场效应晶体管技术和工艺的发展举例 (Intel)

从第二节起仔 细介绍

解决方案

• 器件层面

– 新材料,新结构,新工艺

• 芯片系统层面

– MCM(多芯片组装) – 多核(Multicore MPU) – SiP(System in Package) – 3D-IC(三维集成)

• 相关问题:散热(微流体)

7

Nature 2016.2.11

本章内容

1、MOSFET的演变(历史) 2、亚微米、 深亚微米MOS器件(85’-) 3、新型MOS器件(00’-) 4、SiP与3D集成(10’-)

8

1、MOSFET的演变(历史)

• 先了解发展的总体picture

70年代早期,金属栅极PMOS

•

From MIT课件

9

1975,金属栅极NMOS

1980,CMOS with self-aligned poly-Si gate

Gate-first

10

1985,Lightly-doped drain

MOSFET (LDD-MOSFET) Silicide(self-aligned silicide)

MOSFET

MOSFET with p-pocket or halo

implants

Sub-0.1 μm MOSFET

New device architecture: Silicon-on-

Insulator (SOI)

A

Figure 25.1.1 in: Shahidi, G.G., et al. “Partially-depleted SOI Technology for Digital Logic.” International Solid-State Circuits Conference, San Francisco, CA, Feb. 15-17, 1999. Digest of Technical Papers. New York, NY: Institute of Electrical and Electronics Engineers, 1999, pp. 426-427

New device architecture:

Dual-gate MOSFET

Figure 26&29 in Taur, Y., et al. "CMOS Scaling into the Nanometer Regime."

Proceedings of the IEEE 85, no. 4 (1997): 486-504

Intel’s current (public) view of

MOSFET scaling...

Chau, R., et.al. “Advanced CMOS Transistors in the Nanotechnology Era for High-Performance, Low-Power Logic Applications.” In Proceedings of the 7th International Conference on Solid-State and Integrated Circuit Technology. Beijing, China: IEEE Press, 2004, pp. 26-30.

Key conclusions

•MOSFET scaling has taken place in a harmonious way with。