CPU针脚定义

CPU针脚定义

23. REQ[4:0]# •

這些訊號由CPU接到NB(北橋),當總線擁有者開始一個新 的交易時,由它來定義交易的命令。

23. RESET# •

I

Reset(重置訊號)

當Reset為High時CPU內部被重置到一個已知的狀態並且開 始從位址0FFFFFFF0H讀取重置後的第一個指令。CPU內部 的TLB(位址轉換參考暫存器)、BTB(分歧位址暫存器) 以及SDC(區段位址轉換快取記憶體)當重置發生時內部資 料全部都變成無效。 I Response Status(響應狀態)

7.) FERR# (浮點運算錯誤): 此PIN為一輸出訊號,當CPU內部浮點運算器發生一個Non-Masked Floating Point Error (不遮蔽的浮點運算錯誤) 時,FERR#會被CPU驅 動為LOW。 FERR#的功能與Intel387 Math Coprocessor ( 術學輔助處理器 ) 的 ERROR#訊號相同,為與DOS應用程式相容且提供DOS系統報告浮點 運算錯誤相同的模式。 動作說明 : 一 . Type : output 二 . Normal Voltage Status : High (1.5 V ) 三 . High Min Level : 0.8 V 四 . High Man Level : 1.2 V

當CPU的溫度傳感器偵測到CPU的溫度超過它設定的最高度 溫度時,這個訊號將會變Low,相應的CPU的溫度控制電路 就會動作。 I Power Good(電源OK)

22. PWRGOOD •

這個訊號通常由ICH(南橋)發給CPU,來告訴CPU電源已 OK,若這個訊號沒有供到CPU,CPU將不能動作。 I/O Command Request(命令請求)

CPU脚信号定义

re:WT6014CGC 1 PARAL...WT6014CGC1 PARAL 平行四边形校正2 BRI 亮度控制3 CON 对比度控制4 RESET 复位5 VDD 5V电源6 GND 地7 OSCO 晶振8 OSCI 晶振9 SCORRECT2 S校正电容切换控制10 OFF 停机信号输出11 SUSPEND 待机控制信号输出12 MUTE 保护信号输出13 PB1 数据输入1,接存储器93C56的3脚14 PB0 数据输入0,接存储器93C56的2脚15 IRQ16 PCI S校正电容切换控制17 K1 键控信号输入18 K2 键控信号输入19 K3 键控信号输入20 K4 键控信号输入21 LED1 键控显示信号输出122 LED2 键控显示信号输出223 PB0 接存储器93C56的1脚24 SDA I2C总线串行数据25 SCL I2C总线串行时钟26 H-PHA 行相位调整27 ROTATE 旋转控制28 NC 空脚29 R-GAIN 红色增益控制30 G-GAIN 绿色增益控制31 B-GAIN 蓝色增益控制32 SCORRECT3 S校正电容切换控制33 S S校正电容切换控制34 H-SIZE 行幅控制35 TAPE 梯形校正输入36 V-SIZE 场幅控制37 VCENT 场中心控制38 E.W 枕形校正信号输出39 HSYNC 行同步信号输入40 VSYNC 场同步信号输入WT60P11 MUTE 静噪2 BRIGHT 亮度控制3 NC 空脚4 RESET 复位5 VCC 电源6 GND 地7 OSCIN 晶振8 OSCOUT 晶振9 SDA I2C总线串行数据10 SCL I2C总线串行时钟11 EABLE 存储器写控制12 LED 指示灯控制13 NC 空脚14 NC 空脚15 KEY 键输入16 KEY 键输入17 HSYNC 行同步信号检测18 NC 空脚19 NC 空脚20 SUSP 电源挂起控制21 OFF 电源ON/OFF控制22 KEY 键输入23 NC 空脚24 SDA1 显示器接口I2C总线串行数据25 SCL1 显示器接口I2C总线串行时钟26 ROTA 旋转控制27 CS1 S校正电容切换控制28 CS2 S校正电容切换控制29 CS0 S校正电容切换控制30 ABL 自动射束电流限制31 DEG 消磁控制32 VSOUT 场同步信号输出33 HSOUT 行同步信号输出34 HIS 行幅控制35 CONGTRAST 对比度控制36 BCON 白平衡蓝色控制37 GCON 白平衡绿色控制38 RCON 白平衡红色控制39 HIN 行同步信号输入40 VIN 场同步信号输入re:ST6369 1 V-SIZE 场幅...ST63691 V-SIZE 场幅调整2 V-CENT 场中心调整3 H-SIZE 行幅调整4 PIN 枕形失真调整5 HPOS 行相位调整6 NC 空脚7 CS1 S校正电容控制8 CS2 S校正电容控制9 KEY 键扫描信号10 NC 空脚11 NC 空脚12 NC 空脚13 NC 空脚14 CON 节能控制15 NC 空脚16 KEY 键扫描信号17 KEY 键扫描信号18 KEY 键扫描信号19 KEY 键扫描信号20 KEY 键扫描信号21 GND 地22 CON 节能控制23 CON 节能控制24 NC 空脚25 NC 空脚26 VIN 正极性场同步信号输入27 NC 空脚28 OSCIN 晶振29 OSCOUT 晶振30 RESET 复位31 NC 空脚32 NC 空脚33 HIN 正极性行同步信号输入34 NC 空脚35 NC 空脚36 HSYNC 行同步信号输入37 VSYNC 场同步信号输入38 SDA 串行数据39 SCL 串行时钟40 VDD 5V供电ST637711 H-SIZE 行幅控制2 V-POSI 场中心控制3 H-POSI 行中心控制4 RESET 复位5 VDD 5V电源6 M-DEFECT 显示器检测7 GND 地8 EXTAL 晶振9 XTAL 晶振10 EEPDATA 存储器数据11 EEPCLK 存储器时钟12 PS1 电源控制113 PS2 电源控制214 DEGAUSS 消磁控制15 LED 指示灯控制16 VCC 5V电源17 S-RASTER 自检光栅控制18 S4 S校正电容控制19 S3 S校正电容控制20 S2 S校正电容控制21 S1 S校正电容控制22 WP 存储器读写控制23 OSD-MUTE 屏显静噪24 MIKE-MUTE 话筒静噪25 SDA 串行数据26 SCL 串行时钟27 V-LIN 场线性28 TILT 倾斜控制29 KEY1 键输入130 KEY2 键输入231 ACL 自动对比度控制32 S-DC-OUT 音量控制33 VSYNC1 场同步信号输出34 HSYNC1 行同步信号输出35 PIN-BAL 枕形失真平衡控制36 PARA 平行四边形失真控制37 CLAMP 钳位脉冲38 TRAP 梯形失真控制39 S-PIN 左右枕形失真控制40 V-SIZE 场幅控制41 HSYNC 行同步输入42 VSYNC 场同步输入ST7272N5B11 VDD 电源2 EWPCC 枕校控制3 H.DUTY 行激励脉冲占空比直流控制4 BA1 枕校控制5 PINBAL 枕校不平衡直流控制6 KEYBAL 平行四边形直流控制7 PIN 左右枕校幅度控制端8 KEY 梯形失真校正控制端9 V.CENT 场中心控制10 V.SIZE 场幅控制11 VS.CENT 场S校正幅度直流控制端12 VS.AMP 场S校正幅度直流控制端13 RXD 接收信号,通过外接接口和主机相连,用于测试显示器14 PB6 接高电平15 ABL.DET ABL检测16 HV.DET 高压检测17 LK/ULK 锁定/非锁定18 SW.DATA2 按键输入19 SW.DATA1 按键输入20 V.RTRC 场逆程脉冲输入21 DEG 消磁控制22 CLMP 空23 BAL0 行定时电阻控制24 H.SHIFT 行相位控制25 RESET 复位26 V.SYNCO 场同步信号输出27 V.SYNCI1 场同步信号输入28 VDD 电源29 H.SYNCI1 行同步信号输入30 H.TRIG 行同步信号输出31 GSYNCI 从绿信号中分离出的复合同步信号输入32 OSCOUT 振荡输出33 OSCIN 振荡输入34 ROTA 旋转控制输出35 NC 空36 V.SYNCI2 接主机CPU地37 SAVINGLED 节能指示灯控制38 POWERLED 电源工作指示灯控制39 ON/OFF 关闭控制40 H.STBY 灯丝电压控制41 S4 S校正电容控制442 TXD 发射信号,通过外接接口和主机相连,用于测试显示器43 S3 S校正电容控制344 S0 S校正电容控制045 S1 S校正电容控制146 S2 S校正电容控制247 H.CENT 行中心控制48 TEST 测试端49 HFBACK 行逆程脉冲输入50 H.SYNCI2 用于脱机检测51 SCL 串行时钟,和主机相连52 SDA 串行数据,和主机相连53 DATA 串行数据,和数模转换电路SNY425相连54 CLK 串行时钟,和数模转换电路SNY425相连55 VSS 地56 VSS 地re:NT68P61A 1 RCON 红增...NT68P61A1 RCON 红增益输出2 GCON 绿增益输出3 BRIGHT 亮度控制输出4 RESET 复位5 VCC 电源6 GND 地7 XIN 晶振8 XOUT 晶振9 SDA I2C总线串行数据,接存储器10 SCL I2C总线串行时钟,接存储器11 NC 空脚12 CON 12V电压控制输出13 KEY1 按键114 KEY2 按键215 NC 空脚16 接存储器1脚17 NC 空脚19 DEG 消磁控制输出(H:消磁;L:正常)20 接存储器7脚21 CS0 S校正电容切换控制端022 CS1 S校正电容切换控制端123 CS2 S校正电容切换控制端224 SDA 显示器接口I2C总线串行数据25 SCL 显示器接口I2C总线串行时钟26 ROTA 旋转控制27 NC 空脚28 NC 空脚29 H-SIZE 行幅控制输出30 TRAPEZOID 梯形失真控制输出31 PINCUSHION 枕形失真控制输出32 VSOUT 场同步信号输出33 HSOUT 行同步信号输出34 H-CENT 行中心控制输出35 V-SIZE 场幅控制输出36 V-CENT 场中心控制输出37 CONTRAST 对比度控制输出38 BCON 蓝增益控制输出39 HIN 行同步信号输出40 VIN 场同步信号输出P83C280AER1 NC 空脚2 NC 空脚3 H-EHT 高压补偿控制(补偿高压变化对行幅的影响)4 Q3 S校正电容切换控制5 Q2 S校正电容切换控制6 Q1 S校正电容切换控制7 NC 空脚8 NC 空脚9 XTAL1 晶振10 XTAL2 晶振11 VDD 电源13 HSYNCIN 行同步信号输入14 HSYNCOUT 行同步信号输出15 CSYNCIN 复合同步信号输入16 VSYNCIN 场同步信号输入17 VSYNCOUT 场同步信号输出18 HUNLOCK 行同步失锁状态信号输入19 BLANKING 消隐信号输出20 NC 空脚21 STBY 待机(指示灯)控制22 OFF 电源(待机)控制23 DEGAUSS 消磁控制24 NC 空脚25 NC 空脚26 RESET 复位27 NC 空脚28 HDCSHIFT 光栅水平中心控制29 ROT 光栅旋转控制30 ABLCON 自动射束电流控制31 VSS 地32 VDD 电源33 ADC0 键输入34 ADC1 自检信号输入35 NC 空脚36 SDA1 显示器接口DDCI2C总线串行数据37 SCL1 显示器接口DDCI2C总线串行时钟38 SDA1 I2C总线串行数据39 SCL1 I2C总线串行时钟40 VIN 场同步信号输入41 接存储器时钟VCLK端脚42 LIN 行线性控制re:MC68HC05B03 1 ROTA...MC68HC05B031 ROTA 光栅旋转控制输出2 H-SIZE 行幅控制输出3 MOIRE 摩尔条纹控制输出4 RESET 复位5 VDD 电源6 VSS 地7 XTAL 晶振8 EXTAL 晶振9 POWER 电源开关10 DOC 存储器电源控制11 ENTER 去面板12 WP 写存储器13 CS-OSD 字符控制14 SPENDING 去面板15 IPO16 SCL 串行时钟,接存储器17 SDA 串行数据,接存储器18 A 去面板19 B 去面板20 DEG 消磁控制21 LED 指示灯控制输出22 OFF 电源关闭控制23 SUSPEND 电源挂起控制24 SDA 串行数据25 SCL 串行时钟26 SW1 开关控制127 SW0 开关控制028 CS1 S校正电容切换129 CS2 S校正电容切换230 CS3 S校正电容切换331 CS4 S校正电容切换432 VSYNC 场同步信号输出33 CLAMP 行同步信号输出34 SWBLK 消隐控制35 HCON 行控制36 VCON 场控制37 VOL 音量控制38 PIN-CORN 左右枕校角部失真控制信号输入39 HSIN 行同步信号输入40 VSIN 场同步信号输入MC68HC0880241 VSYNC 场同步信号输入端2 VDD3 滤波端3 DPMS 挂起/响应状态控制端(H:工作;L:挂起)4 DPMF 停机状态控制端(H:工作;L:停机)5 VCC 5V电压供电端6 XTAL 时钟振荡器7 EXTAL 时钟振荡器8 GND 地9 RESET 复位信号输入端(L:复位;H:工作)10 LED-R 电源橙色指示灯控制端11 LED-G 电源绿色指示灯控制端12 EL2 空脚13 KBD1 电源开关操作键控制端14 KBD2 操作键控制端15 IRQ 空脚16 SOG 绿同步信号输入端17 PA7 空脚18 BRI 亮度控制PWM信号输出端19 PA5 空脚20 H-SIZE 行幅控制PWM信号输出端21 G2-ADJ 显像管加速极电压调节PWM信号输出端22 CS1 S校正电容切换控制端123 CS2 S校正电容切换控制端224 CS3 S校正电容切换控制端325 SCL I2C总线时钟信号输出端26 SDA I2C总线数据信号输入/输出端27 CLAMP 钳位信号输出端28 ISDA I2C总线数据信号输入/输出端(接显示卡)29 ISCL I2C总线时钟信号输出端(接显示卡)30 GND 地31 DEG 消磁控制32 ST-IN 无信号检测信号输入端33 ABLCTL 对比度控制PWM信号输出端34 HV.PWM B+电源设定值PWM控制信号输出端35 TILT 倾斜校正控制PWM信号输出端36 HOUT 行同步信号输出端37 VOUT 场同步信号输出端38 ADC 空脚39 MUTE 静噪控制端(L:正常;H:静噪)40 H.LOCK 行频失锁信号输入端41 XRAY X射线保护信号输入端(L:正常;H:保护)42 HSYNC 行同步信号输入端re:HD68HC05BD32B1 V...HD68HC05BD32B1 VSYNC 场同步信号输入2 VCC 5V电源3 USBD USB数据4 USBD USB数据5 RESET 复位6 XIN 晶振7 XOUT 晶振8 GND 地线9 CS4 模式切换(S校正电容切换)控制信号10 CS3 模式切换(S校正电容切换)控制信号11 CS2 模式切换(S校正电容切换)控制信号12 CS1 模式切换(S校正电容切换)控制信号13 CS0 模式切换(S校正电容切换)控制信号14 u-Hf 场同步信号15 u-W/CLAMP 消隐/钳位脉冲16 SOG 绿信号上的同步信号输入17 STBY 待机控制18 DPMOFF 显示器电源管理OFF控制信号19 SUB-BRT 副亮度控制20 u-ABL ABL控制21 CS5 模式切换(S校正电容切换)控制信号22 DEG 消磁控制23 ST-IN 接USB接口电路24 PURITY 色纯控制25 DDC-SDA DDCI2C总线串行数据26 DDC-SCL DDCI2C总线串行时钟27 MUTE 静噪28 SCL I2C总线串行时钟29 SDA I2C总线串行数据30 GND 地线31 TILT 倾斜控制32 VSTC 垂直会聚控制33 HSTC 水平会聚控制34 HSIZE-MAX 最大行幅控制35 H-SIZE 行幅控制36 SOG-OFF SOG关断37 NC 空脚38 NC 空脚39 NC 空脚40 KBDI 键输入41 LED 指示发光二极管控制42 HSYNC 行同步信号输入LGM912-2401 VSYNC 场同步信号输入端2 RESET 复位信号输入端3 NC 空脚4 NC 空脚5 VCC 5V电源6 XTAL 时钟振荡器7 XTAL 时钟振荡器8 GND 地线9 DPMS 挂起/响应控制端(H:工作;L:挂起)10 BUZZ 蜂鸣器电路信号输出端11 XRAY X射线保护信号输入端(H:工作;L:保护)12 DPMF 停机状态控制端(H:工作;L:停机)14 LED-G 电源绿色指示灯控制端15 KBDI 电源开关操作键控制端16 PCT 视频电路供电控制端17 CS3 S校正电容切换控制端18 CS2 S校正电容切换控制端19 CS1 S校正电容切换控制端20 CS0 S校正电容切换控制端21 CS4 S校正电容切换控制端22 DEGAUSS 消磁控制端23 MUTE 静噪控制端(L:正常;H:静噪)24 ST-IN 无信号检测信号输入端25 SDA I2C总线数据信号输入/输出端(接显示卡)26 SCL I2C总线时钟信号输出端(接显示卡)27 HUNLOCK 行频失锁信号输入端28 ISCL I2C总线时钟信号输出端29 ISDA I2C总线数据信号输入/输出端30 GND 地线31 PURITY 色纯校正控制PWM信号输出端32 ABL ABL控制PWM信号输出端33 SUB-CON 对比度控制PWM信号输出端34 SUB-BRI 亮度控制PWM信号输出端35 TILT 倾斜校正控制PWM信号输出端36 HOUT 行同步信号输出端37 VOUT 场同步信号输出端38 KBD1 模拟操作信号输入端39 KBD2 模拟操作键时钟信号输出端40 NC 空脚41 NC 空脚42 HSYNC 行同步信号输入端re:D16F78B1 CS0 S校正电容...D16F78B1 CS0 S校正电容切换控制端02 CS2 S校正电容切换控制端24 LED-R 电源橙色指示灯控制端5 STANDBY 挂起/响应状态控制端(H:工作;L:挂起)6 VSYNCOUT 场同步信号输出端7 HSYNCOUT 行同步信号输出端8 HSYNCIN 行同步信号输入端9 VSYNCIN 场同步信号输入端10 RESET 复位信号输入端(L:复位;H:工作)11 VDD 5V电压供电端12 VSS 未用13 OSC-OUT 时钟振荡器14 OSC-IN 时钟振荡器15 HUNLOCK 行频失锁信号输入端16 DDC-SCL I2C总线时钟信号输出端(接显示卡)17 DDC-SDA I2C总线数据信号输入/输出端(接显示卡)18 GND 接地端19 USB 停机状态控制端(H:工作;L:停机)20 DEGAUSS 消磁控制端21 MUTE 静噪控制端(L:正常;H:静噪)22 NC 空脚23 CS1 S校正电容切换控制端124 XRAY X射线保护信号输入端(H:正常;L:保护)25 ST-IN 无信号检测信号输入端26 KEY 操作键信号输入端27 ENBL 模拟操作键时钟信号输出端28 BZZ 蜂鸣器电路信号输出端29 ABL 对比度控制PWM信号输出端30 W B+电压控制端31 NC 空脚32 BRIGHT 亮度控制PWM信号输出端33 SCL I2C总线时钟信号输出端34 SDA I2C总线数据信号输入/输出端35 F/V 频率/电压变换信号输出端36 PURITY 色纯校正控制PWM信号输出端37 TILT 倾斜校正控制PWM信号输出端38 NC 空脚39 CS4 S校正电容切换控制端440 CS3 S校正电容切换控制端3HD6433214W1 WINK 视频静噪2 NC 空脚3 VSYNCO 场同步信号输出4 VSYNCI 场同步信号输入5 VSYNCI 场同步信号输入6 P-SCL 串行时钟7 P-SCL 串行时钟8 RESET 复位9 XTAL 晶振10 EXTAL 晶振11 MD1 接+5V电源12 MD0 接+5V电源13 NRI 接+5V电源14 VCC 接+5V电源15 STBY 接+5V电源16 VSS 地线17 COLOR ID 彩色识别18 LED 电源指示发光二极管控制19 NC 空脚20 HYNCI 行同步信号输入21 HYNCO 行同步信号输出(未使用)22 CSYNCI 复合同步信号输入23 NC 空脚24 CLAMPO 钳位脉冲输出25 GND 接地26 MODE-ID1 模式识别127 MODE-ID2 模式识别2(接地)28 MODE-ID3 模式识别3(接地)29 RMSSUS 电源管理挂起控制信号输出30 PMS-OFF 电源管理关断控制信号输出31 SCL0 I2C总线串行时钟(接显示卡)32 SDA0 I2C总线串行数据(接显示卡)33 SCL1 I2C总线串行时钟34 SDA1 I2C总线串行数据35 ADJ-1 接32脚SDA036 NC 空脚37 NC 空脚38 M-DEGID 通过上拉电阻接+5V电源39 VCC 接+5V电源40 NC 空脚41 NC 空脚42 NC 空脚43 FH4 行频频段切换控制信号444 FH3 行频频段切换控制信号345 FH2 行频频段切换控制信号246 FH1 行频频段切换控制信号147 S-START 慢启动控制48 GND 地线49 NC 空脚50 通过电阻接地51 通过电阻接地52 通过电阻接地53 通过电阻接地54 通过电阻接地55 DF-SIZE 动态聚焦幅度控制56 HSIZE-MAX 最大行幅控制57 DEGAUSS 消磁控制58 EXIT 键输入(退出键)59 - 键输入(“-”键)60 LEFT 键输入(“左”键)61 RIGHT 键输入(“右”键)62 + 键输入(“+”键)63 PROCEED 键输入(“前进”键)64 RESET 键输入(“复位”键)[分享]CPU 各脚功能CPU 各脚功能56A1125-411 OFF 省电模式控制2 SUSPEND 省电模式控制3 DEG 消磁4 RESET 复位5 VCC 电源6 GND 地7 OSCO 晶振8 OSCI 晶振9 ISCL I2C通信接口10 ISDA I2C通信接口11 LED LED控制12 MODEL 高低频机种切换脚13 SIZECOMP 空脚14 FUNC 键控信号输入15 KEYA 键控信号输入16 KEYB 键控信号输入17 MUTE 保护信号输出18 CS0 S校正电容切换功能脚19 CS1 S校正电容切换功能脚20 CS2 S校正电容切换功能脚21 CS3 S校正电容切换功能脚22 CS4 S校正电容切换功能脚23 CS5 S校正电容切换功能脚24 SDA I2C通信接口25 SCL I2C通信接口26 VOLUME 音量控制27 ROTATE 旋转控制28 SIZEF/V 幅度大小补偿29 BRIGHT 亮度控制30 CONT 对比度控制31 B/B 蓝色字符信号32 VOUT 场同步信号输出33 HOUT 行同步信号输出34 G/B 绿字符信号35 R/B 红字符信号36 B/D 蓝色增益控制37 G/D 绿色增益控制38 R/D 红色增益控制39 H.S 行同步信号输入40 V.S 场同步信号输入。

89代cpu针脚定义

89代cpu针脚定义

89代CPU的针脚定义是指第89代中央处理器的引脚配置和功

能定义。

由于没有具体指明是哪一款CPU,我将以Intel第89代CPU为例进行说明。

在Intel处理器中,89代CPU通常是指第八代

酷睿处理器,如i7-8700K等。

这些处理器的针脚定义包括多个方面,主要涉及电源供应、数据传输、控制信号等功能。

具体来说,这些

针脚包括但不限于地线、电源引脚、时钟信号、输入输出引脚、控

制信号引脚等。

这些针脚的定义和功能是根据处理器的架构和规格

而定的。

从功能角度来看,这些针脚定义了处理器与主板及其他组件之

间的通信和数据传输方式,同时也包括了处理器对外部设备的控制

和管理功能。

另外,针脚定义也涉及到处理器的供电和散热等方面,保证处理器能够正常工作并且在规定的温度范围内运行。

从技术角度来看,这些针脚的定义需要严格遵循处理器设计的

规范,以确保处理器能够在各种工作负载下稳定可靠地运行。

此外,针脚定义还需要考虑到处理器的制造工艺和封装方式,以便在生产

过程中能够准确地焊接和封装处理器。

总的来说,89代CPU的针脚定义涉及到处理器的功能、技术和制造等多个方面,是处理器设计和生产中至关重要的一部分。

希望这个回答能够全面地解答你的问题。

cpu供电引脚定义 -回复

cpu供电引脚定义-回复“CPU供电引脚定义”是一个关于计算机中央处理器(CPU)供电引脚的定义和解释。

在本篇文章中,我们将一步一步回答这个问题,并深入了解CPU 供电引脚的作用和不同引脚的功能。

我们将从基本概念开始,逐渐深入,帮助读者了解这个主题的方方面面。

第一部分:基本概念和背景知识计算机中央处理器(CPU)是计算机的核心部件,负责执行各种指令和进行数据处理。

为了正常工作,CPU需要稳定的电源供应。

这就涉及到CPU 供电引脚的作用。

供电引脚是连接计算机硬件和电源的接口。

对于CPU而言,供电引脚充当了电源信号和电流流动的通路。

不同的供电引脚承担不同的功能,确保CPU能够正常工作并实现高性能计算。

第二部分:CPU供电引脚一个CPU可能有数十个供电引脚,下面列举了其中几个重要的引脚,并对它们的功能进行解释。

1. VCC/VCCIN引脚:这是一个重要的引脚,它提供了CPU所需的电源电压。

通常情况下,这个引脚与电源模块连接,确保CPU能够正常工作。

2. GND引脚:这是接地引脚,用于提供电流回路的接地。

它对于稳定的电流流动非常重要,确保CPU的正常运行。

3. VID/P微引脚:这些引脚是电压标识引脚,与VCC引脚密切相关。

它们用于指定CPU所需的工作电压,以满足不同的工作负载需求。

4. VSS引脚:这是供电引脚之一,用于连接CPU的内部电压分压网络。

它起到了维持CPU内部稳定电压的作用。

5. VRM引脚:这是供电引脚之一,连接到电压调节模块(VRM)。

VRM是用于调节CPU电压的设备,确保CPU工作在正确的电压范围内。

6. AVGATE引脚:这是供电引脚之一,也连接到VRM。

它负责控制VRM 的开关,以提供不同级别的电压,以适应CPU在不同工作状态下的需求。

第三部分:CPU供电的重要性CPU供电引脚的正确使用和连接对于计算机的性能和稳定性至关重要。

一个不稳定的供电系统可能导致CPU工作不正常,甚至造成计算机崩溃。

89代cpu针脚定义 -回复

89代cpu针脚定义-回复89代CPU针脚定义89代CPU针脚定义是指第89代中央处理器(CPU)的引脚定义。

在计算机领域,CPU是整个系统的核心部件,负责执行计算机指令并控制其他硬件设备。

每一代CPU都有特定的针脚定义,以确保与其他组件的兼容性和正确连接。

本文将一步一步回答有关89代CPU针脚定义的问题。

1. 什么是CPU的针脚定义?CPU的针脚定义是指CPU上的金属引脚的排列和编号方式。

这些金属引脚通过插座或焊接连接到主板上,用于与其他硬件设备进行数据和信号传输。

2. 89代CPU具体指的是哪一代CPU?在计算机技术的发展历程中,每一代CPU代表了一种新的技术和性能提升。

89代CPU是指Intel于1989年发布的第89代处理器系列。

该系列CPU包括了Intel 80486(i486)等型号。

3. 89代CPU针脚定义有多少个?常见的89代CPU针脚定义有168个。

4. 89代CPU针脚定义的布局是怎样的?89代CPU的针脚定义布局采用了PGA(Pin Grid Array)封装技术,意味着CPU上的引脚被排列成一个方形的网格状。

每一边有14个引脚,在四个角上各有一个额外的引脚。

5. 89代CPU针脚定义的编号方式是怎样的?89代CPU的针脚定义采用了二进制编码方式进行编号。

每个金属引脚上都有一个唯一的二进制编码,以表示其在系统中的功能和连接。

6. 89代CPU针脚定义中的主要引脚有哪些?在89代CPU针脚定义中,有一些是具有特殊功能的主要引脚,例如电源引脚、时钟引脚、地址引脚、数据引脚和控制引脚。

这些引脚扮演着传输和控制数据的重要角色。

7. 89代CPU针脚定义中的特殊功能引脚有哪些?除了主要功能引脚外,89代CPU针脚定义中还包含了一些特殊功能引脚,如测试引脚、重置引脚和调试引脚等。

这些引脚用于调试和测试处理器的电路和功能。

8. 89代CPU针脚定义与其他代CPU的区别是什么?每一代CPU的针脚定义都会有所不同,以适应当时计算机技术的发展需求。

032n06n针脚定义

032n06n针脚定义

CPU针脚常指的是硬件芯片向外提供的接口方式,由于采用的是针式接口,所以称为针脚。

CPU针脚即一种接口类型,CPU需要通过某个接口与主板连接的才能进行工作,经过这么多年的发展,采用的接口方式有引脚式、卡式、触点式、针脚式等。

而使用最普遍的CPU的接口是针脚式接口,对应到主板上就有相应的插槽类型。

CPU大都采用针脚式接口与主板相连,而不同的接口的CPU在针脚数上各不相同。

CPU接口类型的命名,习惯用针脚数来表示,比如酷睿2系列处理器所采用的775针脚接口,其CPU针脚数就为775针;而AMD 最新的AM3系列处理器所采用的Socket938针脚接口,其CPU针脚数就为938针。

针脚只是处理器接口的一种形式,随着处理器频率的上升和功能的增加,处理器的针脚也随之增加。

但当处理器频率增加到一定程度,针脚增加到一定数量时,处理器运行在高频时会产生大量信噪,造成信号干扰,而这些干扰会影响到处理器的正常工作。

为了有效克服针脚接触造成的信号干扰,Intel就发布了Socket775接口的处理器。

Socket775接口处理器的底部没有传统的针脚,而代之以775个触点,通过与对应的主板上的

Socket775插槽内的775根触针接触来传输信号,这样一来干扰少了,CPU可以设计得更强劲,频率也更高了。

cpu供电引脚定义 -回复

cpu供电引脚定义-回复CPU供电引脚定义详解引言:在计算机硬件中,CPU(中央处理器)被认为是“大脑”,它负责执行所有计算机系统的指令和操作。

为了使CPU正常工作,它需要得到适当的供电。

供电引脚是CPU连接到电源的接口,负责提供所需的电压和电流以供CPU运行。

在本文中,我们将详细介绍CPU供电引脚的定义及其功能,以及它们在计算机系统中的作用。

第一部分:引脚功能及作用1. VCC(电源电压)VCC是CPU供电引脚中最重要的一个。

这个引脚为CPU提供工作所需的电压。

通常,现代CPU的工作电压为1.2V至1.5V。

正确的电压水平对于CPU的稳定工作至关重要。

2. VSS(接地电压)VSS是另一个重要的供电引脚,被用作CPU的接地引脚。

它提供了一个电压的参考值,用于确保CPU工作的稳定性。

正常情况下,VSS引脚通过与地电和系统地电相连接来实现接地。

3. VID(电压识别)VID引脚用于提供CPU的电压识别和识别功能。

这可以通过与电源管理芯片或主板上的电源控制器进行通信来实现。

通过识别电压,系统可以调整电源的输出以满足CPU的需求,并确保CPU正常工作。

4. VDD(电源引脚)VDD是供电引脚中的另一个关键引脚。

它提供了CPU的电源,即所需电压和电流,以确保CPU能够正常工作。

VDD引脚与VCC引脚紧密相关,实际上它们在某些情况下可以交替使用。

第二部分:供电引脚的工作原理CPU供电引脚的工作原理涉及到供电电源、供电管理芯片以及主板与CPU 之间的实际连接。

以下是CPU供电引脚的一般工作原理:1.主板供电系统:主板供电系统通常是通过电源单元完成。

这个系统将电源的直流电(DC)转换为CPU所需的工作电压。

供电系统还包括供电管理芯片,用于管理和控制CPU的供电。

2. 引脚-电源管理芯片连接:通过电源管理芯片,供电系统可以实现与CPU供电引脚的连接。

引脚和芯片之间的连接通常是通过引脚的针脚和芯片上的连接器完成的。

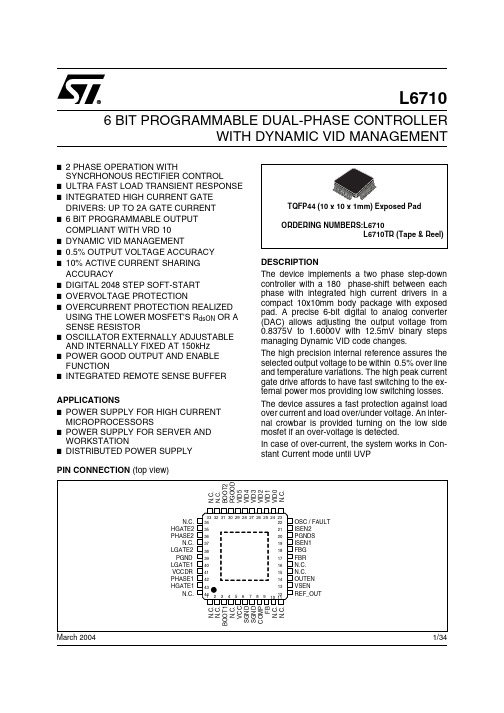

CPU常用供电芯片 L6710 针脚定义

CURRENT CORRECTION

PGNDS ISEN2

CH2 OCP CH1 OCP

32k

CH2 OCP

FBG FBR

32k 32k

I FB

LOGIC PWM ADAPTIVE ANTI CROSS CONDUCTION

LS

LGATE2

PHASE2 HS UGATE2 BOOT2

DESCRIPTION The device implements a two phase step-down controller with a 180 phase-shift between each phase with integrated high current drivers in a compact 10x10mm body package with exposed pad. A precise 6-bit digital to analog converter (DAC) allows adjusting the output voltage from 0.8375V to 1.6000V with 12.5mV binary steps managing Dynamic VID code changes. The high precision internal reference assures the selected output voltage to be within 0.5% over line and temperature variations. The high peak current gate drive affords to have fast switching to the external power mos providing low switching losses. The device assures a fast protection against load over current and load over/under voltage. An internal crowbar is provided turning on the low side mosfet if an over-voltage is detected. In case of over-current, the system works in Constant Current mode until UVP

1200cpu引脚定义

1200cpu引脚定义1200,CPU 1214C,紧凑型 CPU,AC/DC/继电器,机载I/O: 14 个 24V DC 数字输入;10 DO 继电器 2A; 2 AI 0-10V DC,电源:交流 47-63Hz 时 85-264V AC,程序/数据存储器100 KB一般息产品类型标志 CPU 1214C AC/DC / 继电器固件版本 V附带程序包的● 工程系统 STEP 7 V17 及以上版本电源电压额定值 (AC)● AC 120 V 是● AC 230 V 是允许范围,下限 (AC) 85 V允许范围,上限 (AC) 264 V电源频率● 允许范围,下限 47Hz● 允许范围,上限 63 Hz输入电流耗用电流(额定值)在AC 120 V 时 100 mA;在 AC 240 V 时 50 mA耗用电流,***大值在 AC 120 V 时 300 mA;在 AC 240 V 时 150 mA接通电流,***大值 20 A; 264 V 时I²t0.8 A²·s输出电流用于背板总线 (DC 5 V),***大值 1 600 mA; ***大 5 V DC,用于 SM 和 CM传感器供电24 V 传感器供电● 24 V20.4 至28.8V功率损失功率损失,典型值 14 W存储器工作存储器● 集成100 kbyte● 可扩展否装载存储器● 集成4 Mbyte● 插拔式(SIMATIC 存储卡),***大值带有 SIMATIC 存储卡缓冲● 存在是● 免维护是● 不带电池是CPU-处理时间对于位运算,典型值0.08 µs; / 说明对于字运算,典型值1.7 µs; / 说明对于浮点运算,典型值2.3 µs; / 说明CPU-组件组件数量(总计) DBs、FCs、FBs、计数器和定时器。

可设定地址的模块数量可从1到。

可不受限制用于整个工作存储器OB● 数量,***大值只通过代码工作存储器进行限制数据范围及其剩磁保留的数据范围(包括时间、计数器、标记),***大值 14 kbyte标记●容量,***大值 8 kbyte; 标记范围的大小本地数据● 每个优先等级,***大值16 kbyte; 优先级等级1(程序周期):16 KB,优先级等级 2 至 26:6 KB地址范围过程映像● 输入端,可调整1 kbyte● 输出端,可调整 1 kbyte硬件扩展每个系统的组件数量,***大值 3 个通讯模块、1 个号板、8 个号模块时间时钟● 硬件时钟(实时时钟)是● 缓冲持续时间 480 h; 典型值● 每日偏差,***大值 25 °C 时 ±60 秒/月数字输入数字输入端数量14; 集成● 可用来实现技术功能的输入端 6; HSC(高速运算)源型输入/漏性输入是可同时控制的输入端数量所有安装位置— ***高可达 40 ℃,***大值 14输入电压● 额定值(DC) 24 V● 对于号“0” 1 mA 时 DC 5V● 对于号“1” 15 V DC,当为2.5 mA 时输入延迟(输入电压为额定值时)对于标准输入端—可参数化0.2 ms、0.4 ms、0.8 ms、1.6 ms、3.2 ms、6.4 ms 和12.8 ms,可在 4 个组别中选择—从“0”到“1”时,***小值0.2 ms—从“0”到“1”时,***大值12.8 ms对于报警输入端—可参数化是用于技术功能—可参数化单个相位: 3 @ 100 KHz & 3 @ 30 kHz,差分: 3 @ 80 kHz & 3 @ 30 kHz导线长度● 屏蔽,***大值 500 m; 50 m 用于技术功能● 未屏蔽,***大值 300 m; 用于技术功能:否数字输出数字输出端数量 10; 继电器输出端的通断能力● 电阻负载时的***大值2 A● 照明负载时的***大值 DC 时 30 W,AC 时 200 W电阻负载时的输出延迟● 从“0” 到“1”,***大值10 ms; ***大值● 从”1” 到“0”,***大值 10 ms; ***大值继电器输出端● 继电器输出端数量 10● ***大操作循环数在负载额定电压为时,机械电流为 1 千万导线长度● 屏蔽,***大值500 m● 未屏蔽,***大值 150 m模拟输入模拟输入端数量 2输入范围● 电压是输入范围(额定值),电压● 0 至 +10 V 是—输入电阻(0 至 10 V)≥100 千欧姆导线长度● 屏蔽,***大值 100 m; 扭线和屏蔽模拟输出模拟输出端数量 0输入端的模拟值构成集成和转换时间/每通道分辨率● 带有过调制的分辨率(包括符号在内的位数),***大值10 bit● 可参数化的集成时间是● 转换时间(每个通道) 625 µs传感器可连接传感器● 双线传感器是1. 接口接口类型 PROFINET电位隔离是传输速率的自动计算是自动协商是自动交叉是物理接口● RJ 45(以太网)是● 端口数量 1● 集成开关否协议● PROFINET IO 控制器是● PROFINET IO 设备是● SIMATIC 通讯是● 开放式 IE 通讯是; 选件也可加密● 网络服务器是● 气液冗余否PROFINET IO 控制器● 传输速率,***大值 100 Mbit/s服务— PG/OP 通讯是; 使用 TLS V1.3 预设进行加密—等时模式否— IRT 否— PROFIenergy 否—按优先级启动是—带优先启动权限的 IO 设备数量,***大值 16—可连接的 IO 设备数量,***大值 16—用于 RT 的可连接 IO 设备数量,***大值 16—线路上的,***大值 16—激活/取消 IO 设备是—可同时激活/取消的 IO 设备数量,***大值 8—更新时间更新时间***小值还取决于为 PROFINET IO设置的通组件、IO 设备数目以及所组态的用户数据量。

cpu供电引脚定义

cpu供电引脚定义CPU(中央处理器)的供电引脚定义是一种用于向CPU提供电力的接口。

这些引脚与CPU供电有关,负责传输电源电压、电流以及其他与电力相关的信号。

在本文中,我将详细介绍CPU供电引脚的定义以及它们的功能。

CPU供电引脚通常分为两类:电源引脚和地面引脚。

电源引脚用于通过主板与电源相连,提供所需的电压和电流。

地面引脚用于将CPU与主板的地面连接起来,以确保电路的稳定性和可靠性。

以下是一些常见的CPU供电引脚及其定义:1. VCC(电源电压):这是供应给CPU芯片的主电源电压引脚。

它通常由主板上的电源模块提供,其电压通常为3.3V或5V,具体取决于CPU的要求。

2. VID(电压识别):这是一组引脚,它们用于与主板进行通信,以便调整VCC电压。

主板可以根据CPU的要求动态调整电压,以提供最佳的供电性能。

3. VSS(地面引脚):这些引脚与主板上的地面连接起来,以确保电路的稳定性。

它们提供低电平和电流路径,以确保电路中的信号传输正常。

4. VRM(电压调节模块)引脚:这些引脚用于与主板上的电压调节模块通信。

VRM是通过调整VCC电压来提供所需的供电能力,以保持CPU稳定的关键组件。

5. Power Good(PG):这是一个输出信号,用于表示电源是否正常工作。

PG引脚通常与主板的其他电源引脚一起使用,以确保CPU得到正确的供电。

6. Thermal Sense(温度传感器)引脚:这些引脚用于连接CPU的温度传感器。

它们被用于监测CPU的温度,以便主板或其他系统组件可以做出相应的调整。

7. Clock(时钟)引脚:这些引脚用于接收主板提供的时钟信号,用于同步CPU的操作。

时钟引脚的频率和稳定性对CPU的性能和稳定性至关重要。

8. Reset(复位)引脚:这些引脚用于进行硬件复位操作,以将CPU恢复到初始状态。

复位引脚通常由主板的重置电路触发,当CPU出现错误或不响应时,可以使用此信号。

9. Overclock(超频)引脚:这些引脚用于接收来自主板的超频信号,以增加CPU的工作频率。

主板4针CPU风扇针脚定义是怎样的

主板4针CPU风扇针脚定义是怎样的

主板中的CPU风扇是散热的重要部件,很多用户可能对风扇只是功能上的认知,结构方面可能不太了解,本文详细介绍主板4针CPU 风扇针脚定义,希望能帮到您!

主板4针CPU风扇针脚定义如下:

说明:

GROUND:地

PEOWER:电源,一般是12V.

SENSE:传感器信号针

CONTROL:风扇转速控制针,通过该针的电压控制风扇转速。

主板上还有一种系统风扇针脚,一般是3针的,其定义如下:

补充:主板选购注意事项

1、工作稳定,兼容性好。

2、功能完善,扩充力强。

3、使用方便,可以在BIOS中对尽量多参数进行调整。

4、厂商有更新及时、内容丰富的网站,维修方便快捷。

5、价格相对便宜,即性价比高。

相关阅读:主板常用保养技巧

1. 除尘

拔下所有插卡、内存及电源插头,拆除固定主板的螺丝,取下主板,用羊毛刷轻轻除去各部分,的积尘。

一定注意不要用力过大或动作过猛,以免碰掉主板表面的贴片元件或造成元件的松动以致虚焊。

2. 翻新

其作用同除尘,比除尘的效果要好,只不过麻烦一点。

取下主板,拔下所有插卡,CPU,内存,CMOS电池后,把主板浸入纯净水中,再用毛刷轻轻刷洗。

待干净后,放在阴凉处至表面没有水份后,再用报纸包好放在阳光下爆晒至全干。

一定完全干燥,否则会在以后的使用中造成主板积尘腐蚀损坏。

特别是一些主板上的电容出现漏液,在更换新的电容后,一定要

把主板认真清洗一遍,防止酸性介质腐蚀主板,造成更大的故障。

cpu供电引脚定义

cpu供电引脚定义现代计算机的核心处理器(Central Processing Unit,CPU)是整个系统的重要组成部分。

作为一个复杂的电子设备,CPU需要稳定和可靠的电源供应。

而为了满足CPU工作的需求,供电引脚在CPU中发挥着至关重要的作用。

本文将介绍CPU供电引脚的定义和功能。

一、供电引脚的基本概念供电引脚是指连接CPU与电源的引脚。

在现代CPU中,供电引脚的数量和布局都是经过精心设计的,以确保CPU能够正常工作。

不同型号和品牌的CPU供电引脚数量和定义可能会有所不同,但它们的基本功能是相似的。

二、主要的供电引脚1. VCC(电源电压)VCC是CPU的主要供电引脚,提供CPU核心电源电压。

在典型的供电引脚定义中,VCC引脚需要稳定地提供电压,以满足CPU的工作需求。

通常情况下,VCC引脚与CPU的地面引脚相连,以形成供电回路。

2. VSS(地面引脚)VSS引脚是CPU的地面引脚,为电流的回路提供一个低电位点。

它与VCC引脚通过供电回路连接起来,共同为CPU提供稳定的电源供应。

3. VDD(内存电压)VDD引脚是用于供电给CPU内部的存储器单元的引脚。

CPU内部的存储器单元包括高速缓存和寄存器等部件,需要稳定的供电以确保其正常工作。

4. VSS(内存地电压)与VDD引脚对应的是VSS引脚,它为CPU内部的存储器单元提供一个地电位点。

通过连接VDD引脚和VSS引脚,CPU内部存储器单元可以得到合适的电源供应。

5. AVDD(模拟电源电压)对于一些带有模拟电路的CPU来说,AVDD引脚用于提供模拟电路的电源电压。

模拟电路在一些特定的应用场景下起重要作用,它们的正常工作需要稳定的供电。

6. AVSS(模拟地电压)与AVDD引脚对应的是AVSS引脚,它为CPU中的模拟电路提供地电位点。

通过连接AVDD引脚和AVSS引脚,CPU内部的模拟电路可以得到稳定的电源和地电位供应。

三、其他的供电引脚除了上述提到的主要供电引脚,一些CPU还可能具有其他的供电引脚。

Cpu风扇供电针脚的定义

Cpu风扇供电针脚的定义

红线是十二V,黑线为底线,黄线为探测转数线.!电脑里几乎所有的风扇都采用12V供电,遇到对应插座损坏,都可以从Atx电源的12V直接取电.

旧的3针接口:

1针、接地脚

2针、正12V电压

3针、转速侦测脚

新的4针接口:

1针、接地脚

2针、正12V电压

3针、转速侦测脚

4针、调速

目前在Intel芯片组的主板上已经普遍采用了4pin接口的风扇,两针供电(接地与12V),一针温度监控,一针调速。

这种新型的接口对旧有风扇的3针接口兼容性十分好,3pin风扇接上去之后防呆口依然起作用。

看到没有,有防呆口,要不然插不进去,你插的还是123,而不是234,因为1针的位置是,仔细看图:

1 / 1

(注:本资料素材和资料部分来自网络,仅供参考。

请预览后才下载,期待您的好评与关注!)。

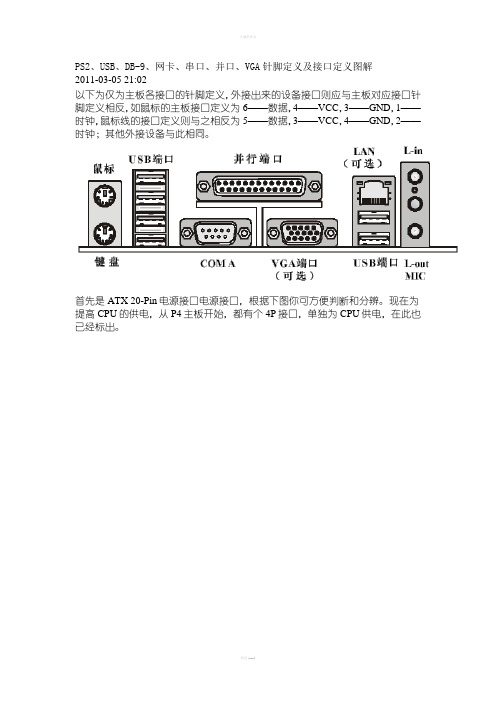

针脚定义及接口定义图解

PS2、USB、DB-9、网卡、串口、并口、VGA针脚定义及接口定义图解2011-03-05 21:02以下为仅为主板各接口的针脚定义,外接出来的设备接口则应与主板对应接口针脚定义相反,如鼠标的主板接口定义为6——数据,4——VCC,3——GND,1——时钟,鼠标线的接口定义则与之相反为5——数据,3——VCC,4——GND,2——时钟;其他外接设备与此相同。

首先是ATX 20-Pin电源接口电源接口,根据下图你可方便判断和分辨。

现在为提高CPU的供电,从P4主板开始,都有个4P接口,单独为CPU供电,在此也已经标出。

鼠标和键盘绝大多数采用PS/2接口,鼠标和键盘的PS/2接口的物理外观完全相同,初学者往往容易插错,以至于业界不得不在PC'99规范中用两种不同的颜色来将其区别开,而事实上它们在工作原理上是完全相同的,从下面的PS/2接口针脚定义我们就可以看出来。

上图的分别为AT键盘(既常说的大口键盘),和PS2键盘(即小口键盘),如今市场上PS2键盘的数量越来越多了,而AT键盘已经要沦为昨日黄花了。

因为键盘的定义相似,所以两者有共同的地方,各针脚定义如下:1、DATA 数据信号2、空3、GND 地端4、+5V5、CLOCK 时钟6 空(仅限PS2键盘)USB(Universal Serial Bus,通用串行总线)接口是由Compaq、IBM、Microsoft等多家公司于1994年底联合提出的接口标准,其目的是用于取代逐渐不适应外设需求的传统串、并口。

1996年业界正式通过了USB1.0标准,但由于未获当时主流的Win95支持(直到Win95 OSR2才通过外挂模块提供对USB1.0的支持)而未得到普及,直到1998年USB1.1标准确立和Win98内核正式提供对USB接口的直接支持之后,USB才真正开始普及,到今天已经发展到USB2.0标准。

USB接口的连接线有两种形式,通常我们将其与电脑接口连接的一端称为“A”连接头,而将连接外设的接头称为“B”连接头(通常的外设都是内建USB数据线而仅仅包含与电脑相连的“A”连接----USB接口提供5V和200ma电流Imax=500 mApc=500ma,笔记本100ma头)。

cpu引脚的基本功能 -回复

cpu引脚的基本功能-回复CPU引脚的基本功能[CPU引脚的基本功能]是计算机架构中非常重要的组成部分。

CPU引脚,也称为管脚,是计算机处理器上的小金属触点。

每个引脚都有其特定的功能,它们通过连接到其他组件(例如主板和内存)来实现信息的传递和处理。

在本文中,我们将一步一步地回答有关CPU引脚的基本功能的问题。

第一步:介绍CPU引脚的基本概念CPU引脚是计算机处理器的一部分,通常位于处理器芯片的边缘。

它们通过某种方式与外部世界(例如主板和其他组件)通信,以便能够用于数据的输入和输出。

CPU引脚的功能取决于其特定的设计和配置,因此不同的处理器会具有不同类型和数量的引脚。

第二步:了解CPU引脚的类别和类型CPU引脚可以被分类为不同的类型,这取决于它们的功能和用途。

以下是一些常见的CPU引脚类型:1. 电源引脚:这些引脚用于提供处理器所需的电源。

它们通常连接到主板上的电源插槽,以确保处理器能够正常运行。

2. 数据引脚:这些引脚用于在处理器和其他设备之间传输数据。

它们通常用于连接内存、输入输出设备和其他外部设备。

3. 控制引脚:这些引脚用于控制处理器内部的操作和功能。

例如,某些引脚可能用于启动和停止处理器的时钟信号。

4. 地址引脚:这些引脚用于指示处理器要访问的内存地址。

它们通常用于连接内存和其他存储设备。

5. 时钟引脚:这些引脚用于提供处理器时钟的定时信号。

时钟信号确定了处理器内部操作的速度和协调。

这只是CPU引脚类型的一些例子,不同的处理器可能有其他类型的引脚,因此具体情况可能会有所不同。

第三步:深入了解一些常见的CPU引脚在了解CPU引脚的一般分类后,我们来讨论一些常见的CPU引脚及其功能。

1. 地址总线引脚:这些引脚用于在处理器和内存之间传输地址信息。

处理器可以将地址发送到这些引脚上,以请求特定内存位置上的数据或指令。

2. 数据总线引脚:这些引脚用于在处理器和其他设备之间传输数据。

它们可以用于读取和写入数据。

cpu引脚针定义

cpu引脚针定义摘要:cpu引脚定义如下图对应的AthlonXPdatasheet如下图下面是socketA的针脚定义。

SocketA针脚如图。

我们把它分为A、B、C、D四个部分。

下面对应的阵脚定义:A和B,C和D。

我们先就针脚做一些解释。

其中SYSCLK、SYSCLK#负责clock频率部分;SDATA[63:0]#、SDATAINCLK[3:0]#、SDATAOUTCLK[3:0]#、SDATAINVALID#、SDATAOUTVALID#、SFILLVALID#负责Data数据输入输出部分;SADDIN[14:2]#、SADDINCLK#负责probe/sysCMD部分;SDADDOUT[14:2]#、目录cpu引脚定义如下图对应的Athlon XP data sheet如下图下面是socketA的针脚定义。

SocketA针脚如图。

我们把它分为A、B、C、D四个部分。

下面对应的阵脚定义:A和B,C和D。

我们先就针脚做一些解释。

其中SYSCLK、SYSCLK#负责clock频率部分;SDATA[63:0]#、SDATAINCLK[3:0]#、SDATAOUTCLK[3:0]#、SDATAINVALID#、SDATAOUTVALID#、SFILLVALID#负责Data数据输入输出部分;SADDIN[14:2]#、SADDINCLK#负责probe/sysCMD部分;SDADDOUT[14:2]#、SADDOUTCLK#为Request部分;PROCRDY、CLKPWDRST、CONNECT、STPCLK#、RESET为电源管理和初始化部分;VID[4:0]、COREFB、COREFB#、PWROK为电压控制部分;FID[3:0]为频率控制部分;FSB_SENSE[1:0]为前端总线控制部分;THERMDA、THERMDC为热敏二极管;PICCLK、PICD[1:0]为APIC部分;FREE、IGNNE#、INIT#、INTR、NMI、A20M#、SMI#、FLUSH#这里定义为legacy,功能不详。

格力变频空调外机电路板CPU引脚定义(80引脚)

格力变频空调外机电路板CPU引脚定义(80引脚)首先祝:大家新年快乐!万事如意!格力板常见80脚cpu格力常见80引脚cpu引脚定义(仅供参考、电路板不一样有可能不同)1.NC 空2.数据、到存储器第5脚3.时钟、到存储器第6脚4.NC空5.NC空6.压缩机热过载保护7.芯片内电源外接滤波电容8.GND地9.经过电阻R67到3.3V供电10.经过2.2K、R4电阻到地11.NC空12.模块相电流检测信号输入13.模块相电流检测信号输入14.模块相电流检测信号输入15.压缩机排气感温信号输入16.室外环境感温信号输入17.IPM功率模块温度检测信号输入18.室外热交换器感温检测信号输入19.芯片供电3.3V20.芯片供电3.3V21.GND地22.GND地23.NC空24.GND地25.GND地26.GND地27.GND地28.GND地29.直流电压检测信号输入30.交流电流检测信号输入32.NC空33.四通阀控制到2003反相器第7脚34.通信电路信号发送输出35.GND地36. 3.3V供电输入37.主供电继电器控制到2003反相器第5脚38.NC空39.NC空40.通信电路信号接收41.外风机控制到2003反相器第3脚42.电流保护信号输入43.NC空44.NC空45.到绿色LED指示灯46.NC空47.到红色LED指示灯48.经2.2K、R2电阻到地49.NC空50.NC空51.NC空52.GND地53.GND地54.芯片内电源外接滤波电容C755.reset复位56.到黄色LED指示灯57.到JTAG插座第5脚、第6脚58.到JTAG插座第4脚59.到JTAG插座第2脚60.到JTAG插座第1脚62.模块驱动输出63.模块驱动输出64.PFC驱动输出65.NC空66.模块驱动输出67.模块驱动输出68.模块驱动输出69.模块驱动输出70. 3.3V供电输入71.GND地72.芯片内电源外接滤波电容73.外接5.1K、R68电阻到地74.NC空75.模块保护检测信号输入76.通过10K电阻到3.3V供电77.通过10K电阻到3.3V供电78.通过10K电阻到3.3V供电79.NC空80.NC空。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5.) DRDY 位置在 H2 腳位,連接至北橋 資料備妥致能時指示系統已備妥CPU的資料屬於輸入/輸出裝置 資料備妥致能 實驗機種 : 8PE800P DRDY 空焊時會不開機,與地短路時會也不開機,與附近腳位短路( 如 ADS#,REQ#[4],REQ#[3],REQ#[0] ) 則均不開機,如果與BNR#短路則會當C3.

12. DP[3:0]# •

這四個訊號主要用於對數據總線上的數據進行奇偶校驗。 I/O Data Ready(數據准備)

13. DRDY# •

當DRDY#為Low時,指示當前數據總線上的數據是有效的, 若為High時,則總線上的數據為無效。

14. DSTBN[3:0]# I/O Data Strobe • Data strobe used to latch in D[63:0]# :

17. GTLREF •

這個訊號用於設定GTL Bus的參考電壓,這個訊號一般被設為Vcc電壓 的三分之二。 I Ignore Numeric Error(忽略數值錯誤) (忽略數值錯誤)

18. IGNNE# •

這個訊號為一ICH輸出至CPU的訊號。當CPU出現浮點運算錯誤時需要 此訊號回應CPU。IGNNE#為Low時,CPU會忽略任何已發生但尚未處 理的不可遮蔽的浮點運算錯誤。但若IGNNE#為High時,又有錯誤存在 時,若下一個浮點指令是FINIT、FCLEX、FSAVE等浮點指令中之一時, CPU會繼續執行這個浮點指令但若指令不是上述指令時CPU會停止執行 而等待外部中斷來處理這個錯誤。

7.) FERR# (浮點運算錯誤): 此PIN為一輸出訊號,當CPU內部浮點運算器發生一個Non-Masked Floating Point Error (不遮蔽的浮點運算錯誤) 時,FERR#會被CPU驅 動為LOW。 FERR#的功能與Intel387 Math Coprocessor ( 術學輔助處理器 ) 的 ERROR#訊號相同,為與DOS應用程式相容且提供DOS系統報告浮點 運算錯誤相同的模式。 動作說明 : 一 . Type : output 二 . Normal Voltage Status : High (1.5 V ) 三 . High Min Level : 0.8 V 四 . High Man Level : 1.2 V

4.) BPRI# (Bus Priority Request) 匯流排優先請求 TYPE:輸入訊號 ACTIVE LEVEL:LOW BPRI#訊號是使用於仲裁微處理機系統匯流排的所有權,它必須連接特有的腳位在所有 微處理機系統匯流排代理者之中.觀察敏銳的BPRI#在所有其他代理者中活動的原因是 為了停止匯流排得到新的請求,除此之外這樣的請求是為切斷進行中上鎖動作.直到代 理者優先請求完成,然後放棄匯流排. 簡單的說,BPRI#會造成微處理機停止匯流排請求

19. INIT# •

I

Initialization(初始化)

這個訊號為一由ICH輸出至CPU的訊號,與Reset功能上非常 類似,但與Reset不同的是CPU內部L1 Cache和浮點運算操 作狀態並沒被無效化。但TLB(位址轉換參考暫存器)與BTB (分歧位址暫存器)內資料則被無效化了。INIT#另一點與 Reset不同的是CPU必須等到在指令與指令之間的空檔才會被 確認,而使CPU進入啟始狀態。 I Processor Interrupt(可遮蔽式中斷)

CPU信号定义:

一、CPU接口訊號說明 接口訊號說明

1. • A[31:3]# I/O Address(地址總線)

這組地址信號定義了CPU的最大內存尋址空間為4GB。在地址 周期的第一個子周期中,這些Pin傳輸的是交易的地址,在地址 周期的第二個子周期中,這些Pin傳輸的是這個交易的信息類型。 A20M# I Adress-20 Mask(地址位元20屏蔽)

27. STPCLK# •

I

Stop Clock(停止時鍾)

當CPU進入省電模式時,ICH(南橋)將發出這個訊號給CPU, 讓它把它的Clock停止。 I/O Target Ready(目標准備)

28. TRDY# •

當TRDY#為Low時,表示目標已經准備好,可以接收數據。當 為High時,Target沒有准備好。 O Voltage ID(電壓識別)

24. RS[2:0]# •

這些信號由回應方來驅動,具體含義請看下表:

25. STKOCC# •

O

Socket Occupied(CPU插入)

這個訊號一般由CPU拉到地,在主機板上的作用主要是來告訴 主機板CPU是不是第一次插入。若是第一次插入它會讓你進 CMOS對CPU進行重新設定。 I System Management Interrupt(系統管理

5. • 6. •

AP[1:0]#

I/O

Address Parity(地址奇偶校驗)

這兩個信號主要用對地址總線上的數據進行奇偶校驗。 BCLK[1:0] I Bus Clock(總線時鍾)

這兩個Clock主要用於供應在Host Bus上進行交易所需的 Clock。 BNR# I/O Block Next Request(下一塊請求)

實驗 機種:8PE800

實驗項目 BPRI# open BPRI# 接地 BPRI# 與 TDI short BPRI# 與 PROCHOT# short BPRI# 與 HITM# short BPRI# 與 DEFFER# short BPRI# 與 LINT0 short 實驗結果 不開機(當88) 不開機(當88) 可開機 可開機 不開機(當88) 不開機(當88) 不開機(當27)

9. •

這兩組訊號主要用於選擇CPU所需的頻率,下表定義了所選 的頻率:

10. D[63:0]# •

I/O

Data(數據總線)

這些訊號線是數據總線主要負責傳輸數據。它們提供了CPU 與NB(北橋)之間64 Bit的通道。衹有當DRDY#為Low時, 總線上的數據才為有效,否則視為無效數據。 I/O Data Bus Inversion(數據總線倒

當這個信號被宣稱時說明在地址信號上的數據是有效的。在 一個新的交易中,所有Bus上的信號都在監控ADS#是否有效, 一但ADS#有效,它們將會作一些相應的動作,如:奇偶檢查、 協義檢查、地址解碼等操作。 ADSTB[1:0]# I/O Address Strobes

4. •

這兩個信號主要用於鎖定A[31:3]#和REQ[4:0]#在它們的上昇 沿和下降沿。相應的ADSTB0#負責REQ[4:0]#和A[16:3]#, ADSTB1#負責A[31:17]#。

23. REQ[4:0]# •

這些訊號由CPU接到NB(北橋),當總線擁有者開始一個新 的交易時,由它來定義交易的命令。

23. RESET# •

I

Reset(重置訊號)

當Reset為High時CPU內部被重置到一個已知的狀態並且開 始從位址0FFFFFFF0H讀取重置後的第一個指令。CPU內部 的TLB(位址轉換參考暫存器)、BTB(分歧位址暫存器) 以及SDC(區段位址轉換快取記憶體)當重置發生時內部資 料全部都變成無效。 I Response Status(響應狀態)

當CPU的溫度傳感器偵測到CPU的溫度超過它設定的最高度 溫度時,這個訊號將會變Low,相應的CPU的溫度控制電路 就會動作。 I Power Good(電源OK)

22. PWRGOOD •

這個訊號通常由ICH(南橋)發給CPU,來告訴CPU電源已 OK,若這個訊號沒有供到CPU,CPU將不能動作。 I/O Command Request(命令請求)

7. •

這個信號主要用於宣稱一個總線的延遲通過任一個總線代理, 在這個期間,當前總線的擁有者不能做任何一個新的交易。

8.

BPRI# 請求)

I

Bus Priority Request(總線優先權

•

這個訊號主要用於對系統總線使用權的仲裁,它必須被連接 到系統總線的适當Pin 。當BPRI#有效時,所有其它的設備都 要停止發出新的請求,除非這個請求正在被鎖定。總線所有 者要始終保持BPRI#為有效,直到所有的請求都完成才釋放 總線的控制權。 BSEL[1:0] I/O Bus Select(總線選擇)

1 . T H E R M D A (T h e rm a l D io d e A n o d e )熱 二 極 體 正 極 位 置 :B 3 2 . T H E R M D C (T h e rm a l D io d e C a th o d e )熱 二 極 體 負 極 位 置 :C 4 功 用 :監 控 C P U 溫 度 以 8 IP E 1 0 0 0 為 範 例 說 明 : TH ER M D A 這 支 腳 是 連 接 至 TH ER M D C 這 支 腳 是 接 地

26. SMI# 中斷) •

此訊號為一由ICH輸出至CPU的訊號,當CPU偵測到SMI#為 Low時,即進入SMM模式(系統管理模式)並到SMRAM (System Management RAM)中讀取SMI#處理程序,當 CPU在SMM模式時NMI、INTR及SMI#中斷訊號都被遮蔽掉, 必需等到CPU執行RSM(Resume)指令後SMI#、NMI及 INTR中斷訊號才會被CPU認可。

29. VID[4:0] •

這些訊號主要用於設定CPU的工作電壓,在主機板中這些訊號 必須被提昇到最高3V。

CPU 重點控制腳位說明

1.) TDI-檢測資料( test data ) 輸.HIGH電位動作 1.5v被用來檢測伴著TCK(測試力 時脈 testability clock ) 信號鎖入 Pentium 的資料 2.) TDO-檢測資料( test data )輸出.HIGH電位動作 1.5v 被用來將檢測資料和指令聚 集再在一起.其中指令是和TCK信號一起從 Pentium 移出 3.) Thermo 腳位