用SystemVerilog验证赛灵思 FPGA

FPGA_验证流程综述

FPGA验证流程综述张勇 陈逸韬深圳市国微电子有限公司 广东深圳 518000摘要:现场可编程门阵列(Field-Programmable Gate Array,FPGA),也被称为FPGA芯片,在通信、安防、工业等领域有着举足轻重的作用。

随着FPGA芯片的规模不断扩大、性能不断提升,其模块数量、电路网表规模、连接复杂度也随之增加。

在此趋势下,如何有效地提升大规模FPGA电路的验证效率与验证完备性变得更为重要。

一个完整的、有针对性的、结构性的验证流程方法,能更全面地对电路设计情况进行覆盖性检查,确保FPGA芯片功能的正确性。

详细叙述从底层到顶层(模块级、子系统级、全芯片级)的FPGA芯片验证方式,包括它们各自的验证方法、流程与侧重等细节,探讨了这种方式是如何帮助FPGA验证工作进行的。

关键词:FPGA芯片 验证效率 验证流程方法 全芯片级验证中图分类号:TN40;TN791文献标识码:A 文章编号:1672-3791(2024)04-0020-03 An Overview of the FPGA Verification ProcessZHANG Yong CHEN YitaoShenzhen State Microelectronics Co., Ltd., Shenzhen, Guangdong Province, 518000 China Abstract:The field-programmable gate array (FPGA) is also known as the FPGA chip, and it plays a crucial role in fields such as communications, security and industry. As the scale of FPGA chips continues to expand and their performance continues to improve, their number of modules, size of circuit netlists and connection complexity also increase. In this trend, how to effectively improve the verification efficiency and completeness of large-scale FPGA circuits has become more important. A complete, targeted and structured verification process method can compre⁃hensively check the coverage of circuit design and ensure the correctness of the function of FPGA chips. This paper detailedly describes the verification method of FPGA chips from the bottom layer to the top layer (module-level, subsystem-level, full chip-level), including details such as their respective verification methods, processes and em⁃phases, and explores how this method helps FPGA verification work.Key Words: FPGA chip; Validation efficiency; Validation process method; Full chip-level validation1 FPGA分层级验证1.1 验证层级分类根据验证侧重点,验证分为3个层级:模块级、子系统级与全芯片级。

FPGA仿真验证

第一编验证的重要性验证,顾名思义就是通过仿真、时序分析、上板调试等手段检验设计正确性的过程,在FPGA/IC开发流程中,验证主要包括功能验证和时序验证两个部分。

为了了解验证的重要性,我们先来回顾一下FPGA开发的整个流程。

FPGA开发流程和IC的开发流程相似,主要分为以下几个部分:1)设计输入,利用HDL输入工具、原理图输入工具或状态机输入工具等把所要设计的电路描述出来;2)功能验证,也就是前仿真,利用Modelsim、VCS等仿真工具对设计进行仿真,检验设计的功能是否正确;常用的仿真工具有Model Tech公司的ModelSim,Synopsys公司的VCS,Cadence公司的NC-Verilog和NC-VHDL,Aldec公司的Active HDL VHDL/Verilog HDL等。

仿真过程能及时发现设计中的错误,加快了设计进度,提高了设计的可靠性。

3)综合,综合优化是把HDL语言翻译成最基本的与或非门的连接关系(网表),并根据要求(约束条件)优化所生成的门级逻辑连接,输出edf和edn等文件,导给CPLD/FPGA厂家的软件进行实现和布局布线。

常用的专业综合优化工具有Synplicity公司的synplify/Synplify Pro、Amplify等综合工具,Synopsys公司的FPGA Compiler II综合工具(Synopsys 公司将停止发展FPGA Express软件,而转到FPGA Compiler II平台),Exemplar Logic公司出品的LeonardoSpectrum等综合工具。

另外FPGA/CPLD厂商的集成开发环境也带有一些综合工具,如Xilinx ISE中的XST等。

4)布局布线,综合的结果只是通用的门级网表,只是一些门与或非的逻辑关系,与芯片实际的配置情况还有差距。

此时应该使用FPGA/CPLD厂商提供的实现与布局布线工具,根据所选芯片的型号,进行芯片内部功能单元的实际连接与映射。

systemverilog的force语句

在SystemVerilog中,force语句是一种非常有用的调试和验证工具。

它可以用于强制修改模拟器中的信号值,以便验证设计在各种情况下的行为。

在本文中,我们将深入探讨force语句的用法、优缺点以及在设计验证中的实际应用。

在深入研究force语句之前,让我们先简要介绍一下SystemVerilog的基本概念。

1. SystemVerilog简介SystemVerilog是一种硬件描述语言(HDL),它扩展了Verilog HDL并添加了一些新的特性,包括面向对象编程、事务级建模、随机化测试等。

SystemVerilog不仅可以用于设计硬件,还可以用于验证硬件设计的正确性。

它为硬件工程师提供了丰富的工具和语言特性,使他们能够更轻松、高效地完成设计和验证工作。

2. force语句的基本概念force语句是SystemVerilog中用于强制修改信号值的一种语句。

它可以在仿真过程中动态地修改信号的值,而不需要对设计进行任何真正的更改。

force语句通常用于调试和验证阶段,以验证设计在不同情况下的行为是否符合预期。

3. force语句的基本语法在SystemVerilog中,force语句的语法如下:```verilogforce signal_name = value;```其中,signal_name是要修改的信号名,value是要强制设置的值。

在仿真过程中,一旦执行了force语句,被force的信号就会立即被强制设置为指定的值。

4. force语句的优点和缺点force语句作为调试和验证工具,具有以下优点:- 可以动态地修改信号值,方便验证设计在不同情况下的行为。

- 不需要对设计进行修改,减少了修改设计的风险。

- 可以快速定位和修复设计中的问题,加速验证过程。

然而,force语句也存在一些缺点:- 过度使用force语句可能会掩盖设计中的真实问题,导致验证不够彻底。

- force语句只能在仿真过程中起作用,不能对实际硬件进行修改。

systemverilog验证方法

systemverilog验证方法SystemVerilog验证方法引言在现代芯片设计中,验证是一个非常重要的环节。

SystemVerilog 是一种常用的硬件描述语言,有许多验证方法可以帮助设计人员有效验证设计的正确性。

本文将详细介绍一些常用的SystemVerilog验证方法。

1.仿真验证方法•使用仿真工具进行功能验证–利用Simulator工具来模拟设计行为以进行功能验证。

验证工程师可以编写testbench来生成输入数据,驱动设计的输出,并进行断言验证。

–通过创建各种激励来测试设计中的不同情况,包括边界情况、异常情况和极端情况等。

•波形分析验证–利用仿真工具生成波形,并分析波形来验证设计的正确性。

可以检查信号的时序关系、逻辑等,并比较期望结果和实际结果。

波形分析验证可以在不同抽象级别进行,包括电平验证、逻辑状态验证和功能验证等。

2.形式验证方法形式验证是一种使用形式工具来验证设计是否满足规范的方法。

形式工具基于设计的数学模型进行验证,可以全面而快速地验证设计的正确性。

•模型检查方法–使用形式工具对设计进行形式化建模,并使用模型检查器来验证设计是否满足特定的属性。

设计人员需要编写属性规范来描述设计的期望行为,并利用模型检查器来自动验证属性是否满足。

•定理证明方法–使用形式工具来进行数学定理的证明来验证设计的正确性。

设计人员需要将设计抽象为一个形式化的数学模型,并利用定理证明器来验证设计是否满足特定的性质。

3.边界扫描方法边界扫描方法是一种将设计周围的接口边界进行扫描以验证设计的方法。

•验证接口协议–针对设计中使用的接口协议,可以编写验证环境来验证接口协议是否正确地被设计所遵循。

验证环境可以利用随机算法生成各种接口交互情况,并验证设计的响应是否满足接口协议规定的规范。

•验证接口互连–针对设计中的各个接口之间的互连,可以编写验证环境来验证互连是否满足设计的要求。

验证环境可以生成接口交互的各种情况,并验证互连的正确性和稳定性。

芯片fpga验证流程

芯片fpga验证流程1. 原理图设计FPGA验证的第一步是进行原理图设计,即将设计的电路拆分成逻辑门、时钟、控制器等基本部件,并将这些部件根据需要布局和布线。

由于FPGA具有可编程性,因此一般使用HDL(Hardware Description Language)语言进行设计和模拟。

2. 仿真验证在进行FPGA设计之前,需要进行仿真验证,以保证设计的正确性。

使用仿真工具对设计的电路进行模拟,可以快速检测出设计中的错误和不足之处。

仿真验证需要注意时钟同步、数据传输、芯片会场布局等问题。

3. 物理验证在完成电路的设计后,需要进行物理验证。

其中包括板级布局、芯片级布局、测试访问机制等物理设计。

在这一阶段中,需要考虑布局对时序、信号完整性和电磁干扰等方面的影响。

4. 静态时序分析静态时序分析是验证在各种情况下FPGA系统的信号传输时间是否能满足硬性时序要求的一项关键任务。

这一过程通常包括设置时钟时延、根据门级网络实现和约束文件添加关键路径等。

5. 时钟分析时钟是FPGA设计中非常重要的元素,“时钟域过渡捕捉”是指当信号从一个时钟域转到另一个时钟域时,捕捉到信号的过程。

在FPGA设计过程中,出现时钟域过渡捕捉错误会导致系统不可预测的行为,因此时钟分析是不可或缺的一步。

6. 功耗分析FPGA芯片设计中,功耗一般分为静态功耗和动态功耗。

在FPGA设计的过程中,需要对功耗进行有效控制,以确保芯片设计能够满足功耗规格和限制。

这一步骤的目标是将功耗保持在可行范围内,同时确保电路的性能和功能稳定。

7. 芯片测试和验证芯片测试和验证是FPGA设计流程中的最后一步,用于确定芯片设计的正确性、性能和可靠性。

在芯片测试和验证过程中,需要进行硬件测量和软件测试,依据测试结果对设计进行修改和纠正,直到达到设计要求。

以上就是FPGA验证流程的主要步骤。

在实际工作中,还需要根据实际情况进行调整和修改,以达到最佳的验证效果。

uvm system verilog总结

uvm system verilog总结### UVM System Verilog 总结#### 导语UVM(Universal Verification Methodology)与System Verilog的结合,为芯片设计验证领域带来了革新。

这种方法论不仅提高了验证效率,还增强了验证的可重用性和覆盖率。

本文将全面总结UVM与System Verilog的相关概念、特点以及应用。

---#### 一、UVM与System Verilog概述**1.1 UVM简介**UVM是建立在System Verilog基础上的一个标准化验证方法论,旨在提供一种通用的、模块化的验证平台。

它通过将验证环境分层,实现了环境的可重用性和易于维护性。

**1.2 System Verilog简介**System Verilog是一种硬件描述和验证语言,结合了Verilog和VHDL的优点,并增加了面向对象编程的特性。

它在芯片设计和验证中广泛应用。

---#### 二、UVM的核心特点**2.1 面向对象**UVM采用面向对象的设计思想,将验证环境分为不同的类和层次,便于管理和重用。

**2.2 模块化**UVM的模块化设计使得验证环境可以根据不同的测试需求灵活组合和配置。

**2.3 自动化**UVM支持自动化测试,包括自动生成测试序列、自动检查和报告错误等。

---#### 三、System Verilog在UVM中的应用**3.1 非阻塞赋值**System Verilog的非阻塞赋值在UVM中用于描述硬件行为。

**3.2 面向对象编程**System Verilog的面向对象编程特性使得UVM可以定义基类和派生类,实现代码的复用。

**3.3 功能覆盖**利用System Verilog的功能覆盖(Functional Coverage)特性,UVM 可以全面检查设计功能的覆盖率。

---#### 四、UVM与System Verilog的结合优势**4.1 提高验证效率**UVM与System Verilog的结合使得验证人员可以快速搭建验证环境,提高验证效率。

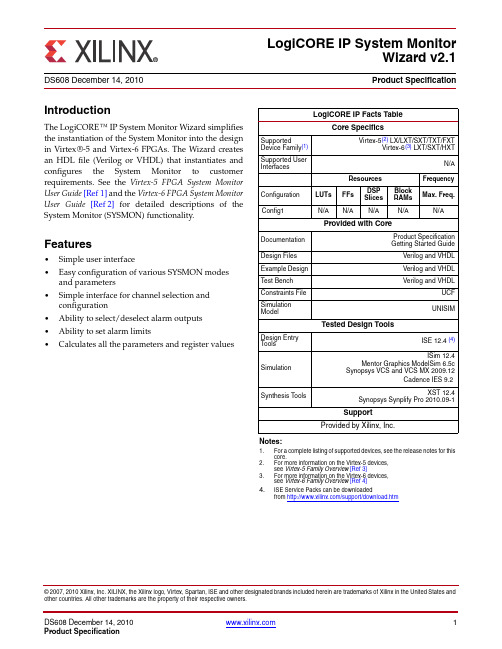

赛灵思(Xilinx)Virtex-5和Virtex-6 FPGA系统监控器向导(LogiCORE

© 2007, 2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.IntroductionThe LogiCORE™ IP System Monitor Wizard simplifies the instantiation of the System Monitor into the design in Virtex®-5 and Virtex-6 FPGAs. The Wizard creates an HDL file (Verilog or VHDL) that instantiates and configures the System Monitor to customer requirements. See the Virtex-5 FPGA System Monitor User Guide [Ref 1] and the Virtex-6 FPGA System Monitor User Gu ide [Ref 2] for detailed descriptions of the System Monitor (SYSMON) functionality.Features•Simple user interface•Easy configuration of various SYSMON modes and parameters•Simple interface for channel selection and configuration•Ability to select/deselect alarm outputs •Ability to set alarm limits•Calculates all the parameters and register valuesLogiCORE IP System MonitorWizard v2.1DS608 December 14, 2010Product SpecificationLogiCORE IP Facts TableCore SpecificsSupportedDevice Family (1)Virtex-5(2) LX/LXT/SXT/TXT/FXTVirtex-6(3) LXT/SXT/HXTSupported User InterfacesN/AResourcesFrequency Configuration LUTs FFs DSP Slices Block RAMs Max. Freq.Config1N/AN/AN/AN/AN/AProvided with CoreDocumentation Product Specification Getting Started GuideDesign Files Verilog and VHDL Example Design Verilog and VHDL Test Bench Verilog and VHDLConstraints File UCF Simulation ModelUNISIMTested Design ToolsDesign Entry ToolsISE 12.4 (4)SimulationISim 12.4Mentor Graphics ModelSim 6.5c Synopsys VCS and VCS MX 2009.12Cadence IES 9.2Synthesis T oolsXST 12.4Synopsys Synplify Pro 2010.09-1SupportProvided by Xilinx, Inc.Notes:1.For a complete listing of supported devices, see the release notes for this core.2.For more information on the Virtex-5 devices, see Virtex-5 Family Overview [Ref 3]3.For more information on the Virtex-6 devices, see Virtex-6 Family Overview [Ref 4]4.ISE Service Packs can be downloadedfrom /support/download.htmLogiCORE IP System Monitor Wizard v2.1Functional DescriptionThe System Monitor Wizard is an interactive graphical user interface (GUI) that instantiates a SYSMONbased design on specific needs. Using the wizard, users can explicitly configure the SYSMON tooperate in the desired mode. The GUI allows the user to select the channels, enable alarms, and set thealarm limits.SYSMON Functional FeaturesMajor functional SYSMON features can be used to determine an appropriate mode of operation. Thesefeatures include:•Analog to digital conversion•FPGA temperature and voltage monitoring•Generate alarms based on user set parametersI/O SignalsTable1 describes the input and output ports provided from the System Monitor Wizard. Availability ofports is controlled by user-selected parameters. For example, when Dynamic Reconfiguration isselected, these ports are exposed to the user. Any port that is not exposed is appropriately tied off orconnected to a signal labeled unused in the delivered source code.Table 1:System Monitor I/O SignalsPort Direction DescriptionDI_IN[15:0]Input Input data bus for the dynamic reconfiguration port (DRP).DO_OUT[15:0]Output Output data bus for the dynamic reconfiguration port.DADDR_IN[6:0]Input Address bus for the dynamic reconfiguration port.DEN_IN Input Enable signal for the dynamic reconfiguration port.DWE_IN Input Write enable for the dynamic reconfiguration port.DCLK_IN Input Clock input for the dynamic reconfiguration port.DRDY_OUT Output Data ready signal for the dynamic reconfiguration port.RESET_IN Input Reset signal for the System Monitor control logic and max / min registers.CONVST_IN Input Convert start input. This input is used to control the sampling instant on the ADC input and is only used in Event Mode Timing (see Event-Driven Sampling in the Virtex-5 and Virtex-6 FPGA System Monitor user guides, [Ref1] and [Ref2]).CONVSTCLK_IN Input Convert start input. This input is connected to a global clock input on the interconnect. Like CONVST, this input is used to control the sampling instant on the ADC inputs and is only used in Event Mode Timing.VP_IN VN_IN InputOne dedicated analog-input pair. The System Monitor has onepair of dedicated analog-input pins that provide a differentialanalog input.LogiCORE IP System Monitor Wizard v2.1VAUXP15[15:0]VAUXN15[15:0]Inputs16 auxiliary analog-input pairs. In addition to the dedicated differential analog-input, the System Monitor uses 16 differential digital-input pairs as low-bandwidth differential analog inputs. These inputs are configured as analog during FPGA configuration.USER_TEMP_ALARM_OUT Output System Monitor temperature-sensor alarm output.VCCINT_ALARM_OUT Output System Monitor V CCINT -sensor alarm output.VCCAUX_ALARM_OUT Output System Monitor V CCAUX -sensor alarm output.OT_OUTOutput Over-T emperature alarm output.CHANNEL_OUT[4:0]OutputsChannel selection outputs. The ADC input MUX channel selection for the current ADC conversion is placed on these outputs at the end of an ADC conversion.EOC_OUT OutputEnd of Conversion signal. This signal transitions to an active-High at the end of an ADC conversion when the measurement result is written to the status registers. For detailed information, see the System Monitor Timing section in the Virtex-5 and Virtex-6 FPGA System Monitor user guides ([Ref 1] and [Ref 2].)EOS_OUT OutputEnd of Sequence. This signal transitions to an active-High when the measurement data from the last channel in the Channel Sequencer is written to the status registers. For detailed information, see the System Monitor Timing section in the Virtex-5 and Virtex-6 FPGA System Monitor user guides ([Ref 1] and [Ref 2]).BUSY_OUT Output ADC busy signal. This signal transitions High during an ADC conversion. This signal transitions High for an extended period during calibration.JTAGLOCKED_OUT Output Used to indicated that DRP port has been locked by the JTAG interface.JTAGMODIFIED_OUT Output Used to indicate that a JTAG write to the DRP has occurred.JTAGBUSY_OUTOutputUsed to indicate that a JTAG DRP transaction is in progress.Table 1:System Monitor I/O Signals (Cont’d)PortDirection DescriptionLogiCORE IP System Monitor Wizard v2.1User AttributesThe System Monitor functionality is configured through the control registers (See the Register File Interface sections in the Virtex-5 and Virtex-6 FPGA System Monitor user guides: [Ref 1] and [Ref 2]).Table 2 lists the attributes associated with these control registers. These control registers can be initialized when the SYSMON primitive is instantiated in the HDL using the attributes listed in Table 2.The control registers can also be initialized through the DRP at run time. The System Monitor Wizard simplifies the initialization of these control registers in the HDL instantiation. The Wizard will generate the correct bit patterns based on user functionality selected through the Wizard GUI.SupportXilinx provides technical support for this LogiCORE product when used as described in the product documentation. Xilinx cannot guarantee timing, functionality, or support of product if implemented in devices that are not defined in the documentation, if customized beyond that allowed in the product documentation, or if changes are made to any section of the design labeled DO NOT MODIFY .Ordering InformationThe System Monitor™ Wizard LogiCORE IP core is provided free of charge under the terms of the Xilinx End User License Agreement . The core can be generated by the Xilinx ISE CORE Generator software, which is a standard component of the Xilinx ISE Design Suite. This version of the core can be generated using the ISE CORE Generator system v12.4. For more information, please visit the Architecture Wizards web page .Table 2:System Monitor AttributesAttribute Name Control Reg Address DescriptionINIT_40Configuration register 040h System Monitor configuration registers. For detailed information, see the Virtex-5 and Virtex-6 FPGA System Monitor user guides ([Ref 1] and [Ref 2])INIT_41Configuration register 141h INIT_42Configuration register 242hINIT_48 to INIT_4FSequence registers48h to 4Fh Sequence registers used to program the Channel Sequencer function in the System Monitor. Fordetailed information, see the Virtex-5 and Virtex-6FPGA System Monitor user guides ([Ref 1] and [Ref 2]).INIT_50 to INIT_57Alarm Limits registers50h to 57hAlarm threshold registers for the System Monitor alarm function. For detailed information, see theVirtex-5 and Virtex-6 FPGA System Monitor user guides ([Ref 1] and [Ref 2]).SIM_MON ITOR_FILE Simulation Analog Entry File -This is the text file that contains the analog input stimulus. This is used for simulation.SIM_DEVICEDevice family-This is used to identify the device family. This is used for simulation.LogiCORE IP System Monitor Wizard v2.1Information about additional Xilinx LogiCORE modules is available at the Xilinx IP Center . For pricing and availability of other Xilinx LogiCORE modules and software, please contact your local Xilinx sales representative .References1.UG192, Virtex-5 FPGA System Monitor User Guide2.UG370, Virtex-6 FPGA System Monitor User Guide3.DS100, Virtex-5 Family Overview4.DS150, Virtex-6 Family Overview5.UG741, System Monitor Wizard Getting Started GuideRevision HistoryThe following table shows the revision history for this document:Notice of DisclaimerXilinx is providing this product documentation, hereinafter “Information,” to you “AS IS” with no warranty of any kind, express or implied. Xilinx makes no representation that the Information, or any particular implementation thereof, is free from any claims of infringement. You are responsible for obtaining any rights you may require for any implementation based on the Information. All specifications are subject to change without notice. XILINX EXPRESSLY DISCLAIMS ANY WARRANTY WHATSOEVER WITH RESPECT TO THE ADEQUACY OF THE INFORMATION OR ANY IMPLEMENTATION BASED THEREON, INCLUDING BUT NOT LIMITED TO ANY WARRANTIES OR REPRESENTATIONS THAT THIS IMPLEMENTATION IS FREE FROM CLAIMS OF INFRINGEMENT AND ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. Except as stated herein, none of the Information may be copied, reproduced,distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including,but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx.Date Version Description of Revisions02/15/071.0Initial Xilinx release.04/19/10 2.0LogiCORE IP System Monitor Wizard v2.0 release. Updated tools and version numbers. Expanded supported Virtex-5 devices. Added support for Virtex-5 TXT and FXT sub-families. Added Virtex-6 FPGA support. Added Functional Description , SYSMON Functional Features , I/O Signals , Support , Ordering Information , and References .12/14/10 2.1Updates to the Wizard and tools versions.。

211171337_轻量级序列密码算法lizard_的FPGA_设计与优化

258 时:

B tj + 1 : = B tj + 1 ,for j ∈ {0,…,88}

(9)

第 89 位更新函数如等式(10)

t+1

t

t

t

t

B 89

: = S 0t B 0t B 24

B 49

B 79

B 84

t

t

t

t

t

t

t

t

t

B 3t B 59

B 10

B 12

B 15

最高工作 频 率 达 到 221MHz; 在 并 行 版 本 中, Lizard 序 列 密 码 算 法 实 现 最 大 的 吞 吐 量 可 达

1254Mbps,提高了数据加密运算的速率。

关键词:轻量级;流密码;现场可编程门阵列;并行优化

文章编号:1672 - 464X(2023)1 - 09 - 18

并行优化,进一步提高算法吞吐率,与文献[ 15]

第 89 位更新函数如等式(4)

的对比性能有一定的提升。

(3)

t+1

t

t

t

t

B 89

: = z t S 0t B 0t B 24

B 49

B 79

B 84

1 密码算法 Lizard 原理

Hamann M 等人设计的 Lizard 轻量级密码算

B 22

B 23

B 62

B 68

B 72

移位寄存器 S 从 1 - 30 位左移至 0 - 29 位

S ti + 1 : = S ti + 1 ,for i ∈ {0,…,29}

vivado中systemverilog混合编译

vivado中systemverilog混合编译在Vivado中,SystemVerilog混合编译是指将SystemVerilog代码与Verilog代码一起编译和仿真。

Vivado支持这种混合编译,以便您可以在同一个项目中使用两种语言。

以下是混合编译的一般步骤:1. 创建项目:首先,创建一个新的Vivado项目。

这可以通过打开Vivado软件并创建一个新的项目文件来实现。

2. 添加文件:在项目中添加所需的Verilog和SystemVerilog文件。

您可以将文件直接拖放到项目浏览器中,或者通过菜单栏中的“File”>“Add”>“File”来添加。

3. 编写代码:在Verilog和SystemVerilog文件中编写代码。

请注意,混合编译的代码应该遵循一定的规范,以便Vivado可以正确地识别和处理两种语言。

4. 编译和仿真:在Vivado中编译项目。

可以通过菜单栏中的“Run”>“Compile”来执行编译操作。

编译完成后,您可以使用Vivado提供的仿真工具进行仿真。

5. 分析结果:在仿真过程中,您可以查看波形、报告和其它输出文件,以分析设计的性能和正确性。

以下是一些建议,以确保混合编译的顺利进行:-避免在同一个模块中混合使用Verilog和SystemVerilog代码。

尽量将Verilog代码和SystemVerilog代码分别放在不同的模块中。

-使用Vivado提供的预处理器指令来区分Verilog和SystemVerilog代码。

例如,使用``来声明一个模块为SystemVerilog模块。

-确保SystemVerilog模块中的异常处理和监控功能正确实现,以避免编译错误。

-熟悉Vivado的编译器和仿真器,以便在混合编译环境中正确地使用它们。

总之,在Vivado中进行SystemVerilog混合编译需要遵循一定的规范和技巧。

通过遵循这些规范和技巧,您可以充分利用Verilog和SystemVerilog的优势,提高设计开发效率。

vivado block design vcs方针

Vivado是赛灵思公司(Xilinx)开发的一款集成电路设计软件,其Block Design功能是一种用于图形化设计和综合可编程逻辑的工具。

而VCS(Verification Computing System)则是Cadence公司推出的一款高级综合(HLS)工具,用于对硬件描述语言(HDL)代码进行验证和仿真。

1. Vivado Block Design框图Vivado Block Design允许用户在图形化界面中组合各种IP核和逻辑模块,以及自定义的硬件设计。

通过简单的拖拽和连接操作,用户可以快速构建复杂的数字电路。

Vivado还提供了一系列的分析工具,可以对设计进行时序分析、资源利用率分析等,帮助用户优化设计。

2. VCS的功能与特点VCS作为一款综合性的HLS工具,具有强大的仿真、验证和综合能力。

它支持Verilog、SystemVerilog和VHDL等多种硬件描述语言,可以对设计进行准确的仿真,帮助用户发现和修复潜在的逻辑错误。

VCS还提供了丰富的调试和优化工具,帮助用户提高设计的性能和可靠性。

3. Vivado Block Design与VCS的集成Vivado和VCS可以通过一些桥接工具实现集成,实现从图形化设计到验证和综合的一体化流程。

用户可以在Vivado中设计好硬件逻辑,并将设计导出到VCS进行仿真和验证。

通过集成,用户可以更加高效地完成硬件设计和验证的整个流程,提高工作效率。

4. Vivado Block Design和VCS的优势Vivado Block Design和VCS的集成可以带来诸多优势,首先可以提高设计的可靠性和稳定性,通过图形化设计和准确的仿真,可以减少设计中的潜在错误。

集成也可以提高工作效率,减少反复导入导出的操作,简化设计流程。

Vivado和VCS作为两大主流工具的集成,也可以带来更多的技术和资源支持,帮助用户解决各种设计和验证中的问题。

5. Vivado Block Design和VCS的应用领域Vivado Block Design和VCS集成的方案,可以广泛应用于各种数字电路设计和验证领域。

赛灵思回读

"赛灵思回读"(Xilinx Readback)通常指的是在FPGA(现场可编程门阵列)设计流程中的一个步骤,特别是在使用Xilinx公司的FPGA芯片时。

FPGA是一种可编程的集成电路,可以被重新配置以实现各种数字电路系统。

在设计FPGA时,工程师会使用硬件描述语言(如VHDL或Verilog)来描述电路的功能,然后将这个设计编译并加载到FPGA 芯片上。

在这个过程中,"回读"(Readback)是指从FPGA芯片中读取当前配置的数据,并与原始的设计数据进行比较,以验证FPGA是否已正确配置。

这通常用于调试和验证目的,帮助工程师确保FPGA的配置没有错误或损坏。

赛灵思(Xilinx)公司提供了一系列的工具和技术来支持FPGA设计的回读操作。

这些工具通常包含在Xilinx的开发套件(如Vivado)中,并允许用户通过JTAG接口或其他方式从FPGA中读取配置数据。

需要注意的是,"回读"操作可能受到FPGA芯片型号、配置方式以及设计复杂度等因素的影响,并且不是所有FPGA都支持完整的回读功能。

在某些情况下,可能只能读取部分配置数据或进行有限的验证。

总的来说,"赛灵思回读"是FPGA设计流程中的一个重要步骤,用于验证FPGA的配置正确性和完整性。

它有助于确保设计的可靠性和稳定性,特别是在对FPGA配置有严格要求的应用场景中。

IC验证工程师招聘笔试题与参考答案(某大型集团公司)2024年

2024年招聘IC验证工程师笔试题与参考答案(某大型集团公司)(答案在后面)一、单项选择题(本大题有10小题,每小题2分,共20分)1、在集成电路(IC)验证过程中,以下哪个阶段通常不会直接涉及硬件描述语言(HDL)的编写?A、功能验证B、时序验证C、代码覆盖率分析D、功耗验证2、在Verilog HDL中,以下哪个关键字用于定义一个无符号整数类型?A、integerB、unsignedC、realD、bit3、以下关于IC(集成电路)验证的描述,正确的是:A. IC验证主要是通过仿真来验证设计的功能正确性。

B. IC验证过程不需要考虑时序问题。

C. IC验证只需要关注设计的顶层模块。

D. IC验证的结果完全取决于验证环境的设置。

4、在IC验证中,以下哪种验证方法主要用于检查设计中的时序问题?A. 动态仿真验证B. 状态机验证C. 功能仿真验证D. 代码覆盖率分析5、在集成电路(IC)验证过程中,以下哪种技术主要用于验证芯片的行为是否与设计规格相符?A. DFT(Design For Test)B. ATPG(Automatic Test Pattern Generation)C. Formal VerificationD. FPGA Prototyping6、以下哪种验证方法可以检测到设计中的时序错误?A. 动态仿真B. 功能仿真C. 硬件加速仿真D. 性能仿真7、在数字电路中,以下哪种触发器是同步时序逻辑电路中最常用的基本触发器?A、D触发器B、JK触发器C、RS触发器D、T触发器8、以下关于Verilog硬件描述语言中模块定义的说法,正确的是?A、模块名称必须以字母开头B、模块名称可以包含下划线、数字等特殊字符C、模块名称可以与标准库中的模块名称相同D、模块名称在定义时可以不指定返回值类型9、以下哪个不是IC验证常用的验证方法?()A. 仿真验证B. 模拟验证C. 代码覆盖率分析D. 逻辑仿真 10、在UVM(Universal Verification Methodology)中,以下哪个组件不是用于创建测试序列的?()A. sequenceB. driverC. monitorD. scoreboard二、多项选择题(本大题有10小题,每小题4分,共40分)1、以下哪些是IC(集成电路)验证中常用的验证方法?A. 功能仿真B. 逻辑综合C. 信号完整性分析D. 动态功耗分析2、在IC验证流程中,以下哪些步骤属于验证环境的搭建?A. 设计测试用例B. 创建测试平台C. 编写验证脚本D. 实施验证计划3、以下哪些技术是IC验证工程师在芯片设计过程中常用的验证方法?()A. 仿真验证B. 硬件加速验证C. 现场可编程逻辑阵列(FPGA)验证D. 模拟验证E. 系统级验证4、在IC验证过程中,以下哪些工具是常用的?()A. Verilog/VHDLB. SystemVerilogC. UVM(Universal Verification Methodology)D. ModelSimE. VCS5、以下哪些技术是IC(集成电路)验证工程师在设计中常用的验证方法?()A. 仿真验证B. 仿真加速C. 硬件加速D. 实物测试E. 模拟验证6、在IC验证过程中,以下哪些工具是常用的验证语言和描述工具?()A. VerilogB. VHDLC. SystemVerilogD. C/C++E. Python7、关于集成电路(IC)验证,以下哪些是验证工程师常用的验证方法?()A. 仿真验证B. 代码覆盖率分析C. 动态功耗分析D. 硬件在环(HIL)测试8、以下关于Verilog和SystemVerilog的区别,哪些描述是正确的?()A. Verilog是SystemVerilog的超集B. SystemVerilog增加了对系统级设计的支持C. Verilog不支持面向对象编程,而SystemVerilog支持D. Verilog主要用于数字电路设计,而SystemVerilog适用于系统级和硬件描述9、以下哪些是IC验证工程师在验证过程中常用的验证方法?A. 仿真验证B. 系统测试C. 代码覆盖率分析D. 动态功耗分析E. 断言检查 10、以下关于Verilog HDL的描述,正确的是?A. Verilog HDL支持行为建模和结构建模B. Verilog HDL不支持模拟仿真C. Verilog HDL主要用于硬件描述和仿真D. Verilog HDL不支持时序约束三、判断题(本大题有10小题,每小题2分,共20分)1、在数字电路设计中,同步复位比异步复位更易于时序分析和综合,因此在所有情况下都应当使用同步复位而不是异步复位。

systemverilog断言例子

systemverilog断言例子SystemVerilog中的断言(assertion)是用于验证设计和验证环境的正确性的一种强大的工具。

它可以在仿真过程中实时监控设计和验证环境的状态,并根据预定义的条件判断来暂停仿真或生成错误报告。

断言通常被用于验证设计的前提假设和防止意外的行为发生。

下面是一些SystemVerilog断言的例子和相关参考内容。

1. 简单断言的例子:以下是一个简单的SystemVerilog断言示例,它验证了一个信号seq_in是否按照预期的顺序发送。

```systemverilogassert property (@posedge clk)seq_in[0] |=> seq_in[1] |=> seq_in[2];```这个断言会在时钟上升沿检查`seq_in[0]`是否在`seq_in[1]`之前发送,以及`seq_in[1]`是否在`seq_in[2]`之前发送。

2. 断言触发时的操作:当断言触发时,可以指定一些操作,比如生成错误报告、记录波形、忽略断言失败等。

以下是一个断言触发时生成错误报告的例子:```systemverilogassert property (@posedge clk)fell_edge_trigger |-> (sig_a == 1);```这个断言将在时钟上升沿检查前一个时钟周期是否发生了下降沿,并且在sig_a为1时触发。

触发后,将生成一个错误报告。

3. 断言的重要性等级:在SystemVerilog中,可以为每个断言定义重要性等级,以指示其相对重要性。

以下是一个设置了重要性等级的断言例子:```systemverilogproperty p1;@(posedge clk) ($rose(req) |-> $stable(resp));endpropertyproperty p2;@(posedge clk) (req && !resp);endpropertyassert property (@(posedge clk) p1)else $error("p1 assertion failed!");assert property (@(posedge clk) p2)else $warning("p2 assertion failed!");```这个例子中有两个断言`p1`和`p2`,它们都在时钟上升沿检查。

【SoCVista】Xilinx FPGA仿真与验证实例

Digital IC Lab文件名稱:Simulation and Verification with Xilinx FPGA撰寫人員:林宜民(依姓氏筆劃)硬體要求:PC、Xilinx FPGA Spartan3 XC3S1500軟體要求:ModelSim SE 5.6、Synplify Pro 7.2、Xilinx ISE 6.3i文件版本:Version 1.2 (1/24/2006)工作內容:1.設計一個組合電路(解碼器)。

2.設計一個循序電路(移位暫存器)。

3.利用Xilinx ISE的CoreGenerator(以下簡稱CoreGen)產生RAM,ROM跟一個乘法器的IP,並藉以完成一個新的電路設計。

補充事項:1.一般硬體描述語言(Hardware Description Language,HDL)可分為VHDL與Verilog兩種,而Verilog是以類似C的語法來描述硬體電路,並擁有各種不同層次的表示方式。

2.模擬器(Simulator)是用來模擬電路的波形。

3.合成工具(Synthesizer)的功用是將HDL轉換成由電路所組成的Netlist。

4.一般而言,在電路設計的模擬上可分為Pre-Sim跟Post-Sim。

Pre-Sim是針對電路的function做模擬,此時只在意由HDL所撰寫的程式之function 是否正確,而Post-Sim則是針對合成過且做完APR(Auto Place and Route)的電路做模擬,以確保所設計的電路實現在FPGA上時,與Pre-Sim的function一樣。

組合電路二對四解碼器※名詞解釋:解碼器(Decoder)的功能是將編碼過的資料做解碼,以得到原始的資料。

※真值表:※示意圖:in0out0enablein1out1out2out3Pre-Sim步驟一:開啟ModelSim ,然後建立一個Project 。

※建立Project 的方式為點選File → New → Project …。

vivado 差分信号类型 -回复

vivado 差分信号类型-回复Vivado 差分信号类型差分信号是现代电子系统设计中常见的一种信号传输方式。

它在抗干扰性、传输速率和静态功耗等方面相对于单端信号有着明显的优势。

Vivado是赛灵思(Xilinx)公司的FPGA设计工具,提供了丰富的差分信号支持,使得设计人员能够更方便地进行差分信号的设计和验证。

本文将深入介绍Vivado中的差分信号类型及其使用方法。

我们将从差分信号的基本概念开始,逐步介绍差分信号在Vivado中的相关设置和操作。

第一部分:差分信号的基本概念差分信号是由一对相互对称的信号组成,分别称为差分信号对的正向和反向信号。

正向信号和反向信号在时间上完全相反,幅度一致,但极性相反。

差分信号通过正向信号和反向信号之间的差异来传递信息,从而提高了信号传输的可靠性和抗干扰能力。

第二部分:Vivado中的差分信号类型Vivado提供了多种差分信号类型,常用的差分信号类型包括LVDS、LVPECL、DIFF_SSTL、TMDS等。

这些差分信号类型在电平、电平摆幅和电流等方面有所不同,适用于不同的应用场景。

其中,LVDS(低压差分信号传输)是一种常用的差分信号类型,适用于高速数据传输和串行通信。

LVDS信号在传输速率、电源噪声抑制和散射数据抑制等方面表现出色,广泛应用于LCD显示器、高速AD/DA转换器和通信接口等领域。

LVPECL(低压峰峰差分输出逻辑)是另一种常见的差分信号类型,适用于要求更高速率和更低功耗的应用。

LVPECL信号具有较大的电平摆幅和更高的传输速率,常见于高性能计算和通信设备。

DIFF_SSTL(差分同步转发时序逻辑)则是一种专为系统芯片内部通信设计的差分信号类型,其电平摆幅和输入阻抗等都得到了优化。

TMDS(差分信号最小转换传输)则主要用于音视频传输,如HDMI和DVI接口。

第三部分:Vivado中的差分信号设置方法在Vivado中,设置差分信号类型主要涉及到FPGA设计的约束文件和代码编写。

SystemVerilog 芯片验证8-功能覆盖

4 module adder #(parameter WIDTH = 4) (

5 input clk,

6 input rst_n,

7 input [WIDTH-1:0] a,

8 input [WIDTH-1:0] b,

9 output reg [WIDTH:0] sum);

10

11 always @(posedge clk, negedge rst_n) begin

10 / 50

覆盖组的触发

覆盖组的触发

功能覆盖的主要内容包括采样数据和采样触发条件。当新数据准备好时(例如 发送完一个事务),测试平台便会触发覆盖组。触发覆盖组的主要方式如下。

1 如果代码中不存在标识何时采样的信号或事件,或者一个覆盖组中有多个 实例需要独立触发,这时应该使用 sample 方法显式触发覆盖。

3 状态机覆盖(FSM coverage):即状态机里所有可能发生的状态跳转都要被 遍历到。

4 分支覆盖(branch coverage):即 DUT 的所有模块的每个条件分支是否有 被执行过(包括 if、else 和 case 语句等)。

5 翻转覆盖(toggle coverage):即 DUT 的每个模块的信号(包括端口信号和 内部信号)是否有被翻转过(即每个信号都从 0 到 1 或从 1 到 0 变化过)。 例如异步复位信号 rst_n 只从 0 到 1 翻转过,但没有从 1 到 0 翻转过,那 么这个信号没有被翻转覆盖。

->>done; // 触发事件

23

end

24 endtask

25 endclass

SystemVerilog 芯片验证

2023 年 11 月 21 日

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

但通常并不会提供特别具有挑战性的向 量对其进行有针对性的测试。这里需要 的是有用的测试激励。我们建议先从最 简单的测试开始,即先检查设计的基本 功能。具体来说,我们的最初测试实例 就是在每个方向仅发送一个封包。发送 单个封包可以验证逻辑和物理层之间的 通信是正确的,并且测试平台本身也能 够正常运行。

SystemVerilog接口对内核信号进 行抽象,从而可以在测试平台和待测器 件(DUT)之间提供简单的连接。唯 一与内核接口通信的类是将事务转换为 向量的驱动器和将向量转换回事务监视 器。图1中用黑色实线表示基于向量的 接口。所有其它单元之间的连接都用灰 色虚线,代表基于事务的通信。在处理 向量流时,驱动器和监视器利用内建在 事务中的函数实现域和数据流之间的转 换,并且还使用比较(comparison)等 成员函数。

coverpoint din1_s; coverpoint din2_s; combos: cross din1_s, din2_s; endgroup

// overflow not allowed // on dout wire [WIDTH:0] tmp = din1 + din2; property p_dout_over;

4

赛灵思中国通讯 31 期

信号增加对应的输入端口。

最后一步是编写封装(wrapper) 模块,用来将验证模块绑定到现有 RTL模块。 SystemVerilog的关键字绑 定和固有的按名字连接(connect-byname)能力使得创建封装模块非常简 单。请注意,SystemVerilog并不支持 参数的隐含连接,因此在这一级必须 明确地将其作为端口调用。分层引用 (Hierarchical references)允许访问子 模块中的信号和参数。

clk,

input

rst,

input [WIDT[WIDTH-1:0] din1,

input [WIDTH-1:0] din2)

// ensure all combinations // of din1/din2 "signs" wire din1_s = din1[WIDTH-1]; wire din2_s = din2[WIDTH-1]; covergroup sign_bits @(posedge clk)

@(posedge clk) tmp[WIDTH] == 1; endproperty ap_dout_over: assert property

(p_dout_over) else $error("dout overflowed!");

endmodule

图 2. 针对一个简单加法器的绑定(Binding )嵌入式断言和覆盖实例。 在高层仿真时,还包括 “top_bind”做为仿真目标。

为了快速测试感兴趣的功能,我们 建立的测试实例仅包括部分受约束的随 机向量空间。例如,为测试逻辑内核发 送侧路的接口仲裁,我们利用fork/join 构造并行向发生器发出指令。在仿真过 程中,每个发生器同时或几乎同时在每 个逻辑发送接口生成事务。因为可以直 接仿真某一功能,而不需要约束求解器 通过随机仿真过程来覆盖,所以这在一 定程度上缩短了测试时间。

2008 年冬季刊

3

专家园地

我们采用随机引擎自动创建包含不 同内容的合法封包,并以正确的时序将 其发送到内核。这样就可以保证无论是 任意次序的任意封包,还是活跃的内核 是哪种封包类型,我们对内核的测试都 是全面的。这种方法可以快速验证:内 核数据通道能够处理所有可能的封包组 合,而且内核控制能够应对任何可能发 生的情况。

随机生成和覆盖

强大的测试平台基础架构非常重 要,但如何没有实际应用于具体设计的 事务,其好处也体现不出来。传统的方 法是创建一个测试方案,编写覆盖所关 注功能的受控测试。不幸的是,高级验 证也需要测试方案。利用SystemVerilog 内建的随机约束功能可自动覆盖许多待 测功能。随机测试的一个好处是能够发 现设计人员没有注意到的隐藏测试点。 一旦发现这些新的测试点,就可以将其 添加到测试方案中,保证仿真环境测试 到这些点。

如图1所示,在事务序列的末端, 驱动器或监视器发送事务到记分板。记 分板包含DUT的参考模型,可以验证 DUT行为是否正如预期。参考模型还特 别检查内核是否能够正确完成接口间的 仲裁、构造恰当的封包并在需要时正确 地重新传输封包。

SRIO内核不仅在外部通信,而且

在所有顶级模块之间都采用逻辑链路接 口。一个通用监视器类的实例是检查一 个逻辑链路接口,目的是当问题在内核 中发生时就能够捕获它们,而不是等待 问题出现在外部接口。在设计中采用标 准接口可以尽早检测到电路中的潜在问 题,从而更快完成调试。立即纠正一个 错误可以避免从事件序列中进行反向追 溯。

GGeGenneeernareatrotaortror

LocalLink Monitor

LocalLink Monitor

LoDcDraiDvrlLievriirenvrker

Transmit to Core

Receive from Core

Logical Core

Transmit Receive

Buffer

当你自己要开发可便携并且强大的 新测试平台时,可以很容易地使用我们 在这个验证项目中用到的一些方法。本 文还会描述我们用于提高设计质量的一 些甚至不必对测试平台进行改动的方法 和功能覆盖技巧。

抽象测试平台开发 事务(transaction)帮助我们在

仿真过程中跟踪数据移动并控制事件。 SRIO验证基础架构中的一个事务类代 表RapidIO封包并且在每个域都包含成 员元素。我们还使用事务类来表示内核 中的其它事件和状态。例如,我们采用 一个调度类型来指出封包是否需要在链 路接口重新传输,使用另一个配置类来 表示主端口上的读写事务。

2

赛灵思中国通讯 31 期

仅运行简单的“通过型测试”(is it alive?)然后将FPGA设计下载到板 上已经不能满足系统开发的需要了。由 于现代FPGA器件的复杂度不断提高, FPGA设计现在也需要与之前ASSP和 ASIC同样的全面功能验证。好消息是现 有的先进验证技术已经可以用于FPGA 开发,并帮助提高设计质量。

对每一RTL模块,我们都创建了包 含断言(assertion)和功能覆盖的嵌入 式验证模块。首先我们拷贝每一RTL模 块的端口说明,只不过要将输出端口修 改为输入端口。然后,我们为验证模块 增加所有需要访问的任何参数或本地参 数。最后,我们为希望检测的任何内部

RTL source code

module my_rtl

立即执行:断言和覆盖 SystemVerilog语言分为组件验证

和开发。绑定(binding)是用来将一 个模块连接到另一个模块的验证构造。

在不对RTL源文件进行任何修改的情况 下,它允许验证代码直接监视寄存器传 输级(RTL)可综合代码。

在不对测试平台进行大幅修改的情 况下,Binding构造支持增加更为先进的 验证特性。唯一需要做的就是创建一个 新的验证模块并将其“绑定”到您的代 码。这种白盒测试方法可立即识别缺陷 事件,并且决定应当发生的测试事件响 应。

一旦基本测试可以工作,我们再转 向随机测试。随机测试改变所有接口上 封包的内容和大小以及时序,这简单的 一个步骤可帮助我们进行更为彻底的测 试。然后,我们逐渐提高测试的复杂度 并内核进行全面的验证。因为更为高级 的测试已经覆盖了基本功能,随着测试 的深入,这种台阶式的方法还让我们逐 步关闭一些较为简单的测试项目并缩短 仿真周期。

专家园地

重新传输封包时,采用一个新智能缓冲 器实现事务自动重新排序和事务优先级 管理。对于这个特定的验证项目,工程 师采用了Mentor Graphics公司标准AVM 基础类别之上的SystemVerilog(利用 Mentor Graphics Questa工具仿真)来 验证新设计的Buffer LogiCORE与现有 Logical LogiCORE之间的交互作用,同 时保证符合RapidIO标准应用层。

#(.WIDTH (WIDTH)) my_rtl_bound

(.clk, .rst, .dout, .din1, .din2);

endmodule

Embedded assertions and coverage

module my_rtl_bind

#(parameter WIDTH = 8)

(input

if (rst) begin

dout <= #`TCQ 0;

end else begin

dout <= #`TCQ din1 + din2;

end

end

Bind verification to source

module top_bind #(parameter WIDTH = 8) ();

bind <your hierpath to inst name for my_rtl> my_rtl_bind

一旦回归测试开始运行,我们就 可以检查功能和代码覆盖数据。正如所 预期的一样,肯定还有一些覆盖空隙。 我们通过编写受控随机测试来覆盖随机 测试没有充分覆盖的区域。例如,我们 通过改变用户和链路接口上的数据限速 来仿真缓冲器全满和全空时的情况来增 加一个测试实例。当封闭覆盖间隙时, 采用受控随机测试激励的混合方法效率 是最高的。通过将随机向量集中在感 兴趣的地方,生成的测试激励向量会更 有用,并且可以维持随机测试带来的好 处。

#(parameter WIDTH = 8)

(input

clk,

input

rst,

output [WIDTH-1:0] dout,

input [WIDTH-1:0] din1,

input [WIDTH-1:0] din2)