AC耦合电容

dc耦合的ac电压

DC耦合的AC电压一、什么是DC耦合的AC电压在电路中,直流(Direct Current,简称DC)和交流(Alternating Current,简称AC)是两种常见的电流形式。

直流电压是恒定的,而交流电压则是周期性变化的。

DC耦合的AC电压是指通过一种特殊的电路连接方式,将直流电压和交流电压进行耦合,使得交流电压可以在直流电压的基础上进行叠加。

二、DC耦合的AC电压的原理DC耦合的AC电压的实现依赖于电容和耦合电路。

通过将一个电容连接在直流电压和交流电压之间,可以实现直流电压的隔离,并使交流信号通过。

当交流信号通过电容时,它会在电容两端产生一个交流电压,这个交流电压可以与直流电压相叠加,从而得到DC耦合的AC电压。

三、DC耦合的AC电压的应用DC耦合的AC电压在电子电路中有着广泛的应用。

以下是一些常见的应用场景:1. 音频放大器音频放大器是将微弱的音频信号放大到足够大的电压和功率输出的设备。

在音频放大器中,经常使用DC耦合的AC电压来传输音频信号。

通过将音频信号和直流电压耦合,可以实现音频信号的放大和输出。

2. 射频放大器射频放大器是将射频信号放大到足够大的电压和功率输出的设备。

在射频放大器中,也常常使用DC耦合的AC电压来传输射频信号。

通过将射频信号和直流电压耦合,可以实现射频信号的放大和输出。

3. 信号传输在信号传输中,如果需要同时传输直流和交流信号,可以使用DC耦合的AC电压。

通过将直流信号和交流信号耦合,可以实现信号的有效传输。

四、DC耦合的AC电压的设计与实现要实现DC耦合的AC电压,需要进行相应的电路设计和实现。

以下是一些常见的设计和实现要点:1. 选择合适的电容选择合适的电容是实现DC耦合的AC电压的关键。

电容的容值需要根据具体的应用场景和要求进行选择。

一般来说,电容的容值越大,对交流信号的传输越好,但也会增加成本和体积。

2. 设计合适的耦合电路耦合电路是实现DC耦合的AC电压的另一个关键。

耦合电容的作用是什么以及滤波、旁路电容的作用

电容耦合的作用是将交流信号从前一级传到下一级。当然,耦合的方法还有直接耦合和变压器耦合的方法。直接耦合效率最高,信号又不失真,但是,前后两级的工作点的调整复杂,相互牵连。为了不使后一级的工作点不受前一级的影响,就必须在直流方面把前一级和后一级分开。同时,又能使交流信号顺利的从前一级传给后一级,同时能完成这一任务的方法就是采用电容传输或变压器传输来实现。它们都能传递交流信号和隔断直流,使前后级的工作点互不牵连。但不同的是,用电容传输时,信号的相位要延迟一些,用变压器传输时,信号的高频成份要损失一些。一般情况下,小信号传输时,常用电容作为耦合元件,大信号或强信号的传输,常用变压器作耦合元件。

如果微观来看,高频器件在工作的时候,其电流是不连续的,而且频率很高,

而器件VCC到总电源有一段距离,即便距离不长,在频率很高的情况下,

阻抗Z=i*wL+R,线路的电感影响也会非常大,

会导致器件在需要电流的时候,不能被及时供给。

而去耦电容可以弥补此不足。

滤波电容、去耦电容、旁路电容作用

滤波电容用在电源整流电路中,用来滤除交流成分。使输出的直流更平滑。

去耦电容用在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。

旁路电容用在有电阻连接时,接在电阻两端使交流信号顺利通过。

1.关于去耦电容蓄能作用的理解

1)去耦电容主要是去除高频如RF信号的干扰,干扰的进入方式是通过电磁辐射。

2.旁路电容和去耦电容的区别

去耦:去除在器件切换时从高频器件进入到配电网络中的RF能量。去耦电容还可以为器件 供局部化的DC电压源,它在减少跨板浪涌电流方面特别有用。

旁路:从元件或电缆中转移出不想要的共模RF能量。这主要是通过产生AC旁路消除无意的能量进入敏感部分,另外还可以提供基带滤波功能(带宽受限)。

PCIe基础知识

PCIe基础知识PCIe总线概述随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。

与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI 总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

PCIe总线的基础知识与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe 链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。

PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe 总线使用的层次结构与网络协议栈较为类似。

1.1 端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图41所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC耦合电容。

电容耦合效应

电容耦合效应

摘要:

1.电容耦合效应的概念

2.电容耦合效应的原理

3.电容耦合效应的应用

4.电容耦合效应的优缺点

正文:

一、电容耦合效应的概念

电容耦合效应是指在电路中,由于电容器的存在,使得电路中的某一部分与另一部分产生相互影响的现象。

电容器能够储存电荷,并在需要时释放电荷,从而对电路中的电压产生影响。

二、电容耦合效应的原理

电容耦合效应的原理是由于电容器内部的电荷会发生变化,从而改变电容器两端的电压。

当电容器充电时,电容器内部的电荷会增加,导致电容器两端的电压上升;当电容器放电时,电容器内部的电荷会减少,导致电容器两端的电压下降。

这种电压变化会传递到电路中的其他部分,从而产生电容耦合效应。

三、电容耦合效应的应用

电容耦合效应在电路设计中有着广泛的应用,例如:

1.滤波器:滤波器能够通过电容耦合效应去除电路中的噪声和干扰信号,从而提高信号的质量。

2.振荡器:振荡器能够通过电容耦合效应产生稳定的振荡信号,从而为电路提供时钟信号。

3.耦合器:耦合器能够通过电容耦合效应将两个电路的信号进行耦合,从而实现信号的传输和放大。

四、电容耦合效应的优缺点

电容耦合效应的优点:

1.能够实现信号的传输和放大;

2.能够去除电路中的噪声和干扰信号;

3.能够为电路提供稳定的时钟信号。

电容 ac voltage characteristic

电容ac voltage characteristic标题:电容的AC电压特性深度解析一、引言电容是电子电路中不可或缺的基础元件,其主要功能是储存电能并在电路中起到滤波、耦合、谐振等作用。

在交流(AC)电压环境下,电容的性能表现与直流(DC)电压环境有所不同,这就涉及到电容的AC电压特性。

本文将详细探讨电容的AC电压特性,包括其基本概念、工作原理、影响因素以及实际应用。

二、电容的基本概念电容,简单来说,是衡量两个导体之间存储电荷能力的物理量。

其单位为法拉(F),但在实际应用中,通常使用微法(μF)、纳法(nF)或皮法(pF)等较小的单位。

电容由两个相互靠近但不接触的导体构成,中间隔着绝缘介质。

当这两个导体分别带有一定的电荷时,就会在它们之间产生电场,电容就是这个电场储能的度量。

三、电容的AC电压工作原理在AC电压环境下,电容的电压和电流的关系并非线性,而是呈现出一种称为阻抗的复数特性。

这是因为电容对交流电压的响应取决于电压的频率。

在低频下,电容可以看作是一个开路,阻止电流通过;而在高频下,电容则可以看作是一个短路,允许电流自由通过。

电容的这种频率依赖性源于其充电和放电的过程。

当交流电压施加到电容上时,电容会在每个半周期内进行充电和放电。

电压的变化速率(即频率)决定了电容充电和放电的速度。

频率越高,电容充电和放电的速度越快,因此通过电容的电流也就越大。

四、电容的AC电压特性影响因素1. 电容值:电容值越大,其对交流电流的阻碍作用越小,也就是说,电容的阻抗越低。

2. 电压频率:如前所述,电压频率越高,电容的阻抗越小,通过电容的电流越大。

3. 绝缘介质:不同的绝缘介质具有不同的介电常数,这会影响电容的电容值和阻抗。

4. 温度:温度变化会影响绝缘介质的介电常数和电阻率,从而影响电容的AC电压特性。

五、电容的AC电压特性在实际应用中的体现电容的AC电压特性在许多电子设备和系统中都有重要应用,以下是一些典型例子:1. 滤波:在电源电路中,电容常常被用作滤波元件,以去除电压中的交流成分。

9_耦合_交流耦合和直流耦合的区别

关于交流耦合和直流恢复的区别耦合耦合是指两个或两个以上的电路元件或电网络等的输入与输出之间存在紧密配合与相互影响,并通过相互作用从一侧向另一侧传输能量的现象。

∙交流耦合(AC Coupling)就是通过隔直电容耦合,去掉了直流分量∙直流耦合(DC Coupling)就是直流、交流一起过,并不是去掉了交流分量。

∙比如在3V的直流电平上叠加一个1Vpp的弦波,如果用直流耦合,看到的是以3V为基准,+/-0.5V的正弦波;如果用交流耦合,看到的是以0V为基准,+/-0.5V的正弦波∙∙电容具有隔直通交的特性,所以电容只能用来耦合交流信号,而对于直流,电容用来滤波,就是把直流中的交流滤去。

1、交流耦合和直流恢复的区别:直流耦合时,屏幕上显示的才是真正的被测信号。

交流耦合时,输入信号通过一个电容器进行耦合,之后才进入示波器的放大电路,由于电容器的隔直作用,被测信号中的直流分量会被滤除,示波器显示的只是交流分量。

交流耦合和直流耦合在匹配电路上的区别:直流耦合就是直接的导线连接,包括通过像电阻之类的线性元件的连接。

它适用于对包括直流分量的信号的放大电路中。

在直流耦合电路中,各级电路的静态工作点是互相影响的。

一级的工作点改变了相邻的二级也会受到影响。

因此不能单独地调整工作点电流和电压。

而在交流耦合直流不耦合的电路中各级电路是用电容或者是电感隔离开的。

因此静态工作点是独立的,调整静态工作点比较容易。

直流耦合中因为各级的输入和输出阻抗是一定的,不好作阻抗变换,直接耦合时高效率匹配就很难做到。

而在交流耦合电路中用线间变压器就很好地进行阻抗变换实现高效率的匹配。

特别是选频放大电路中普遍采用的LC谐振电路更是极大地提高了电路的效率。

2、交流耦合(AC COUPLED)是通过电容串联在线路中来完成的耦合,电容种类不限,交流耦合的作用是去除信号里面的直流分量。

它对纯交流信号(没有任何直流成分)没有特别的影响,对于直流信号来说则是去除了直流分量,这是电容充电稳定后的特性。

10-100M以太网板级电容耦合应用浅谈

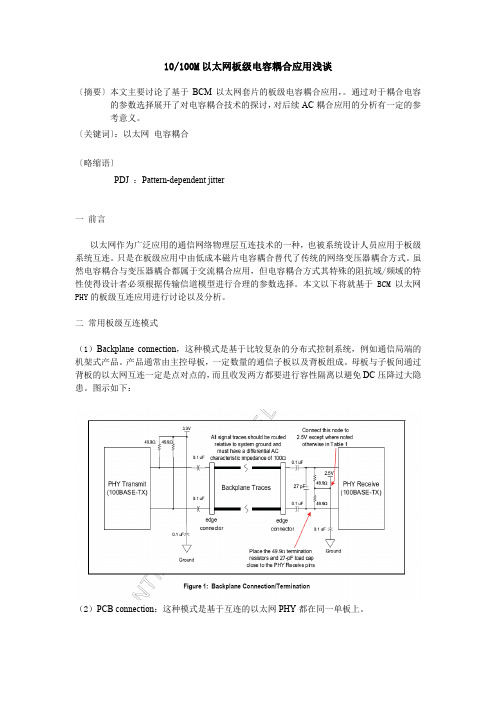

10/100M以太网板级电容耦合应用浅谈〔摘要〕本文主要讨论了基于BCM以太网套片的板级电容耦合应用,。

通过对于耦合电容的参数选择展开了对电容耦合技术的探讨,对后续AC耦合应用的分析有一定的参考意义。

〔关键词〕:以太网电容耦合〔略缩语〕PDJ :Pattern-dependent jitter一前言以太网作为广泛应用的通信网络物理层互连技术的一种,也被系统设计人员应用于板级系统互连。

只是在板级应用中由低成本磁片电容耦合替代了传统的网络变压器耦合方式。

虽然电容耦合与变压器耦合都属于交流耦合应用,但电容耦合方式其特殊的阻抗域/频域的特性使得设计者必须根据传输信道模型进行合理的参数选择。

本文以下将就基于BCM以太网PHY的板级互连应用进行讨论以及分析。

二常用板级互连模式(1)Backplane connection,这种模式是基于比较复杂的分布式控制系统,例如通信局端的机架式产品。

产品通常由主控母板,一定数量的通信子板以及背板组成。

母板与子板间通过背板的以太网互连一定是点对点的,而且收发两方都要进行容性隔离以避免DC压降过大隐患。

图示如下:(2)PCB connection:这种模式是基于互连的以太网PHY都在同一单板上。

三 AC耦合电容的参数选择为了方便进行分析,我们可以将板级以太网交流耦合应用回路归一化等效为RC一阶高通电路如下:Figure 3: RC耦合电路我们可以发现,在这样的信道模型中,一段时间内,如果驱动器驱动到线路上为同一码型,则在这段时间内,高速互连通道的特性与RC高通特性的完全一致,图3的C相当于图2中的AC耦合电容,R相当于接收器的100ohm终端匹配电阻。

同一码型持续的时间段中,接收器上接收到的电压呈指数级别降低,时间越长,电压降低越多。

假设驱动器发送连“1”码比特流到线路上,随着时间的延续,接收器接收到的电压会逐渐降低,即图4中的LF Droop(低频衰减,因为RC电路具有高通滤波特性,所以电路的低频分量衰减较大),时间越长,LF Droop越大,一旦码型发生变化后,比如图4中改变为“0”码,接收器上的电压会迅速降低并反相,因为LF Droop的影响,电压降低的起点会比理想位置低,导致从“1”码到“0”码的变化边沿时刻会比理想位置有所提前,这个与理想位置的偏移量就是由AC耦合所带来的PDJ(Pattern-dependent jitter)。

dc耦合的ac电压

dc耦合的ac电压【实用版】目录1.概述2.dc 耦合的 ac 电压的概念3.dc 耦合的 ac 电压的工作原理4.dc 耦合的 ac 电压的应用5.结论正文1.概述在电子电路中,我们常常会遇到一种名为 dc 耦合的 ac 电压的现象。

这种现象对于电子电路的设计和运行都有着重要的影响。

因此,了解 dc 耦合的 ac 电压的工作原理和应用,对于电子工程师来说,是必不可少的。

2.dc 耦合的 ac 电压的概念dc 耦合的 ac 电压,指的是在直流电路中,由于电容器的存在,使得交流电压得以通过电容器,形成一种既有直流分量,又有交流分量的电压。

这种电压既具有直流电压的稳定性,又具有交流电压的变化性,因此在电子电路中得到了广泛的应用。

3.dc 耦合的 ac 电压的工作原理dc 耦合的 ac 电压的工作原理主要依赖于电容器的特性。

电容器可以储存电荷,当交流电压通过电容器时,电容器会储存交流电压的电荷,形成一个稳定的直流电压。

同时,电容器也会放出储存的电荷,使得交流电压得以通过。

这样,就形成了一种既有直流分量,又有交流分量的电压。

4.dc 耦合的 ac 电压的应用dc 耦合的 ac 电压在电子电路中有着广泛的应用。

例如,在放大器电路中,通过使用 dc 耦合的 ac 电压,可以有效地抑制交流噪声,提高信号的纯度。

在振荡电路中,通过使用 dc 耦合的 ac 电压,可以得到更加稳定的振荡信号。

此外,dc 耦合的 ac 电压还被广泛应用于滤波器、信号处理器等电子电路中。

5.结论总的来说,dc 耦合的 ac 电压是一种既有直流分量,又有交流分量的电压,它的工作原理主要依赖于电容器的特性。

ac耦合电容(ACcouplingcapacitor)

ac耦合电容(AC coupling capacitor)Step response of 1 RC series circuitFigure 1 RC first order circuitAs shown in Figure 1, is composed of RC high order filter circuit, t = 0 + time switch, namely to a RC circuit step excitation, 0 + voltage time capacitor C is up to 0, there is no charge for the response voltage on R.For the sake of simplification, the complex frequency domain analysis method is applied to this circuit, and the results of voltage sharing on the R are R and C. The complex frequency domain image function UR of the resistance R voltage (s) is shown as follows:The inverse Laplasse transform of s domain to time domain is used to obtain the time-domain solution UR (T) of the voltage on the resistor:The result shows that at t = 0 + time time on switch capacitor C, the equivalent circuit, the voltage on R VDC, and then with the charging capacitor C, voltage R exponentially on the lower level, when time tends to infinity when, C VDC is fully charged, the voltage on the approach VDC, R voltage on reaching 0.Characteristic analysis of 2 AC coupled transmission channelThrough the analysis, in Section 1 can be found in thehigh-speed interconnection transmission system, in a period of time, if you drive on the line for the same type of code, inthis period of time, the characteristics of high speed interconnect channels and in Section 1 identical figure 1 C is equivalent to AC coupling capacitor in figure 2, the 50ohm terminal R is equivalent to the receiver, the resistance, the figure does not draw the same code continuous period of time, the receiver receives the voltage level decreased exponentially, longer, more voltage drop.In Figure 2, shown in Figure 3, assuming the drive to send even the "1" code bit stream on the line, as time went on, the receiver receives the voltage will be gradually reduced, namely LF in 2 Droop (low frequency attenuation, because the RC circuit has characteristics of high pass filter circuit, so low frequency components attenuation) LF Droop, the longer, more, once the code changes, such as Figure 2, 3 changed to "0" code, the voltage on the receiver will decrease quickly and reverse the effects of LF Droop because of the reduced voltage starting point than the ideal position is low, leads to a change from "1" edges. Code "0" code will be earlier than the ideal position, and the ideal position offset is caused by the coupling of AC PDJ. Obviously, 3dB corner frequency of high pass filter circuit RC is low, RC constant is, the more low frequency components by LF Droop PDJ, smaller, smaller, because the fixed value of R, so C is larger, the smaller the PDJ, higher C is beneficial to the inhibition of PDJ.Figure 2 PDJ caused by AC couplingFigure 3 Correlation jitter caused by AC couplingFigure 4 PDJ estimation of similar trianglesThe mathematical deduction of PDJ is given in combination with figures 3 and 4, and an analytic formula is given and the values are estimated. The difference of the two signals, the common mode voltage as a common center, equal and opposite phase, can be seen from Figure 5, the PDJ and the difference of common mode voltage size on the line Never mind and signal, and the magnitude of the change in VPP (i.e., differential mode voltage), and because of difference the positive and negative phase is completely symmetrical, so only on one of the signal analysis of difference.As shown in Figure 2, the differential is output to the single end of the drive with a signal swing of VPP,The signal period is TUI, the signal rise time is TR for 20% to 80%, and the continuous code length is N Bits. The voltage caused by the continuous invariant code is reduced to V, and the signal edge offset (that is PDJ) is TJ. Set the initial voltage on the receiving end (i.e. the initial voltage on the R) as the "middle 1" code and "0" code level value 0.5VPP, according to the analysis in Section 2 of the results, after continuous invariant code transfer time N Bits, voltage R:The voltage drop on the R is V:We need to solve the value of TJ, and now we know the value of delta V. Obviously, if we can find the relationship between them, the value of TJ can be easily solved. The signal edge shift in Fig. 5 local amplification of the study, as shown in Figure 3, we can see that from 20% to 80% Tr, and the 0.6VPP signal ofthe rising edge and triangle TJ, composed of delta V and signal drop along the right triangle composed of similar shape, so:According to the formula, you can calculate the value of TJ, TR value can be found from the drive's data book, must pay attention to 20% to 80% of the rise time, if you do not find the value of TR, you can use the next type of estimation:BW is the bandwidth of the transmitted signal, and in the first-order system, the typical rate of BW is 60% to 100% data rates. In practical applications, if only the TJ is estimated, it is recommended that the BW take an intermediate value, that is, the data rate of 80%, so that:N is the largest number of continuous invariant codes, related to the channel bearer type; TUI is the unit cycle of the signal; the R is generally 50ohm; the value of C can be flexibly chosen; the size of the C determines the size of the TJ.The formula for TJ can eventually be reduced to:(*)The ratio of TJ to unit cycle TUI is:(* *)Selection of 3 AC coupling capacitorFrom the analysis in the 2 section, we can know that as the length of the continuous NRZ code increases, or the C value ofthe AC coupling capacitor decreases, the correlation jitter PDJ of the system will become larger than that of the N code. For example, for continuous NRZ code, the data signal of 3.125GBPS whose length is 20, the period TUI is 320pS, the rise time of 20% to 80% is 150pS, and R is 50ohm, then the formula of PDJ becomes TR:For different C, the pattern correlation jitter is:Capacitance jitter jitter and unit cycle ratio performance100pF 90pS 28% is unacceptable1nF 15pS 5% okay10nF 1.6pS <1% is great100nF 0.2pS is an excellent 0From the vibration point of view, the greater the AC coupling capacitor C, transmission channel PDJ is smaller, the better the performance of the system, but the wobble is not the only need to consider the issue, but there is another aspect to consider, on the contrary, the rules against the use of large capacitance, following a detailed description of the issue.A real capacitor also includes a parasitic resistance (ESR, equivalent series resistance) and a parasitic inductance (ESL, equivalent series inductance), as shown in Figure 7, the actual capacitor is connected in series of the three elements, there will be a series resonant frequency. At the resonant frequencypoint, the C plays a dominant role. The capacitor behaves as a capacitor, and as the frequency rises, the impedance becomes larger; at the resonant frequency point,The role of C and ESL completely offset the capacitor performance for the resistance characteristic impedance reaches the minimum value, the value is ESR; on the resonant frequency, ESL plays a leading role for the performance of the inductor capacitor, with the rising frequency of impedance change. That is to say, two parasitic components, minimum impedance ESR decided the capacitor can be achieved, the ESL capacitor on the resonant frequency performance of inductors, capacitors and lost, with increasing frequency, impedance becomes larger, and the impedance of an ideal capacitor in high frequency tends to zero.Figure 4 impedance frequency characteristics of a Murata multilayer ceramic capacitorThe analysis in Section 2, we believe that the capacitor is ideal, if taking into account the actual effect of the capacitor will be in the high impedance, leading to high frequency components of the signal attenuation change, will also make the receiver receives the voltage drop, will cause the signal Bian Yuanfa phase offset caused by the extra jitter. The greater the capacitance, the higher the frequency impedance, the more the voltage drop, the greater the jitter. From this point of view, the smaller the AC coupling capacitor, the better.As shown in Figure 5, the impedance frequency curves of the multilayer ceramic capacitors of 4 different Murata packagesof the 0603 are shown:The smaller the capacitance, the greater the ESR and the higher the resonant frequency point, the better the high frequency characteristics of the capacitor. The capacitance of the resonant frequency is lower than 1GHz, for high speed interconnect transmission system over GHz, the whole system in the high frequency bandwidth, resonant frequency over the inevitable capacitor, electrically sensitive; in the four capacitor, the capacitor 10nF in the whole frequency keep the lowest impedance performance the best, the capacitor impedance at low frequency is better than that of 1nF and 100pF, high frequency capacitor impedance is less than 100nF. Therefore, in combination, for example of the above 3.125G data transmission system, it is best to select the AC coupling capacitor of 10nF.Although multilayer ceramic capacitors generally work in high data rate systems when foreign showed up to 5 ~ 10ohm impedance, but for the realization of AC coupling function, can still work well enough, the high impedance voltage drop is a result of the increase of (usually <2%), leading to the phase shift is also small (less than 10o), so there is no need to use special standard RF capacitors, multilayer ceramic capacitors (general ceramic dielectric, optional NPO or X7R) will be able to meet the requirements.Therefore, we choose the AC coupled capacitors, which not only from the high pass filter capacitor is selected considering the characteristics of large capacity, can not consider the single capacitor of small capacity from the perspective of ESL, shouldbe considered high pass filter characteristics and high frequency capacitance under the influence of ESL, selection of middle value capacitor the basic principles are as follows:The jitter associated with the 1 capacitor shall not exceed 5% of the unit cycle;2, as far as possible the use of small packaging capacitor, small package of high frequency characteristics better than the large package, it is recommended to use 0603 or 0402 package;3, the impedance of the capacitor in the entire low frequency and high frequency can be taken into account, with the lowest overall performance impedance, it is recommended to choose between 1nF ~ 100nF capacitor.Today, I'm interested in the two AC coupled capacitors when I look at the content of SATA,Find some information, and over the book, look for related content: the empirical formulas: definition of Tc for each bit of data for the NUM period, the maximum allowable continuous 0 or 1 bit number, the impedance of the load is R (typically 50 ohms), C AC coupled electric capacity value. ForCmin=7.8*NUM*Tc/R SATA we number NUM the largest I temporarily did not find information, but "high speed digital design practice" mentioned in the example can give you a calculation method of the initial 800Mbit/S connection when the Tc=1.25ns NUM is the largest in the product in 0 consecutive or 1, R is 50 ohm, calculated minimum Cmin 0.0167uF, so he proposed800Mbit/S selected when the 0.01uF capacitor is not appropriate.Please refer to the second chapter of high-speed digital design practice for more details. QQ 450911824 can be discussed in detailCalculation formula of charge discharge time of capacitor:Let V0 be the initial voltage value on the capacitor;Vu is the capacitor full termination voltage value;Vt is the voltage value of the capacitor at any time t.Then,Vt=V0+ (Vu-V0) * [1-exp (-t/RC)]If the voltage is E, the battery charges the capacitor C to the initial value of 0 through the resistor RV0=0, charge limit Vu=E,Therefore, at any time, t, the voltage on the capacitor is:Vt=E*[1-exp (-t/RC)]T=RCLn[E/ (E-Vt)]If the voltage Vt on a capacitor is known at a certain time, the time t can be calculated based on the constant.Formula meaning:Fully filled, Vt approaches E, time is infinite;When t= RC, the capacitor voltage is =0.63E;When t= 2RC, the capacitor voltage is =0.86E;When t= 3RC, the capacitor voltage is =0.95E;When t= 4RC, the capacitor voltage is =0.98E;When t= 5RC, the capacitor voltage is =0.99E;It can be seen that after 3~5 RC, the charging process is basically over.Discharge time calculation:The initial voltage is E, and the capacitor C is discharged through the RV0=E, Vu=0, so the capacitor discharges at any time t, and the voltage on the capacitor is:Vt=E*exp (-t/RC)T=RCLn[E/Vt]The above exp () indicates the exponent based on E; Ln () is the logarithm of the e base.。

ac-dc 层间电容 -回复

ac-dc 层间电容-回复什么是ACDC层间电容?ACDC层间电容指的是在电路中不同层之间存在的电容现象。

在现代电子设备中,为了提高电路的集成度和性能,使用了层间互连技术。

层间互连技术是将不同层(通常是金属层)之间通过一层厚度非常薄的介电层隔离开来,形成层间互连电容。

这个电容称为ACDC层间电容。

为什么存在ACDC层间电容?层间电容是电路中不可避免的现象,存在的原因主要有以下几点:1. 信号传输:在电路中,信号需要在各个元件之间进行传输。

而层间电容直接影响信号的传输质量。

通过层间互连技术,可以将信号通过层间电容进行传输,实现高速、高密度的互连。

层间电容的存在使得信号传输更加稳定,降低信号损耗。

2. 降噪和屏蔽:在电子设备中,各个电路之间的信号往往会相互干扰。

通过层间互连技术,可以利用层间电容来屏蔽干扰信号,减少噪音的影响。

层间电容能够将干扰信号与被干扰信号进行隔离,从而提高电路的抗干扰能力和抗噪声性能。

3. 电气隔离:在复杂电子系统中,不同电路之间往往需要进行电气隔离。

通过层间电容,可以实现电气隔离,并防止发生电路间的短路现象。

层间电容在电路设计中起到了隔离和保护的作用,保证了电路的安全性和可靠性。

如何计算ACDC层间电容值?计算ACDC层间电容值需要考虑多个因素,其中主要包括介电层的参数和电路的几何结构等。

下面介绍一种常用的计算方法:1. 确定介电层的参数:首先需要知道介电层的相对介电常数(εr)和层间厚度(d)。

相对介电常数表示介电层对电场的阻抗程度,层间厚度表示介电层的厚度。

2. 计算电容值:ACDC层间电容的计算公式为:C = ε0 * εr * A / d,其中ε0为真空中的介电常数,A为层间电容的接触面积。

根据实际情况,可以通过层间电容的计算公式得到层间电容的数值。

需要注意的是,由于ACDC层间电容的计算涉及到电路的几何结构等复杂因素,所以通常会借助电磁场仿真软件进行模拟计算,以准确得到层间电容的数值。

耦合电容、滤波电容、去耦电容、旁路电容

耦合电容器主要的作用是隔离直流信号。

电容的阻抗和信号的频率成反比,信号的频率越高,衰减越小。

理论上,对于直流信号的阻抗是无穷大。

很多场合需要放大的是交流信号,所以,会用耦合电容去掉信号中的直流部分。

滤波电容用在电源整流电路中,用来滤除交流成分。

使输出的直流更平滑。

去耦电容用在放大电路中不需要交流的地方,用来消除自激,使放大器稳定工作。

旁路电容用在有电阻连接时,接在电阻两端使交流信号顺利通过。

1.关于去耦电容蓄能作用的理解1)去耦电容主要是去除高频如RF信号的干扰,干扰的进入方式是通过电磁辐射。

而实际上,芯片附近的电容还有蓄能的作用,这是第二位的。

你可以把总电源看作密云水库,我们大楼内的家家户户都需要供水,这时候,水不是直接来自于水库,那样距离太远了,等水过来,我们已经渴的不行了。

实际水是来自于大楼顶上的水塔,水塔其实是一个buffer的作用。

如果微观来看,高频器件在工作的时候,其电流是不连续的,而且频率很高,而器件VCC到总电源有一段距离,即便距离不长,在频率很高的情况下,阻抗Z=i*wL+R,线路的电感影响也会非常大,会导致器件在需要电流的时候,不能被及时供给。

而去耦电容可以弥补此不足。

这也是为什么很多电路板在高频器件VCC管脚处放置小电容的原因之一(在vcc引脚上通常并联一个去藕电容,这样交流分量就从这个电容接地。

)2)有源器件在开关时产生的高频开关噪声将沿着电源线传播。

去耦电容的主要功能就是提供一个局部的直流电源给有源器件,以减少开关噪声在板上的传播和将噪声引导到地2.旁路电容和去耦电容的区别去耦:去除在器件切换时从高频器件进入到配电网络中的RF能量。

去耦电容还可以为器件提供局部化的DC电压源,它在减少跨板浪涌电流方面特别有用。

旁路:从元件或电缆中转移出不想要的共模RF能量。

这主要是通过产生AC旁路消除无意的能量进入敏感的部分,另外还可以提供基带滤波功能(带宽受限)。

我们经常可以看到,在电源和地之间连接着去耦电容,它有三个方面的作用:一是作为本集成电路的蓄能电容;二是滤除该器件产生的高频噪声,切断其通过供电回路进行传播的通路;三是防止电源携带的噪声对电路构成干扰。

AC耦合连接器的信号完整性分析.doc

AC耦合连接器的信号完整性分析高速互连系统受许多因素的影响,例如互连密度、带宽、信号完整性和功率需求等。

随着电子系统向高速度、高密度、低功耗、低电压和大电流的趋势发展,系统中的数据传输速率迅速提高,对互连的带宽要求越来越大。

如何获得可传输多Gbps信号的高带宽互连系统是目前许多团队正在研究的课题。

AC耦合互连可用于芯片间传输高速数字信号,AC耦合包括电感耦合和电容耦合,由于AC耦合互连的信号传输界面是非接触的,所以能提供比机械匹配连接更加密集、简单的互连。

本论文站在前人研究成果的基础上,讨论了使用电容耦合互连实现板级高速数字信号传输的可行性,提出AC耦合互连的有效均衡方案,增加了AC耦合互连的适用范围;此外文中还分析和研究了同时开关噪声抑制中的电容位置对噪声抑制的影响。

本论文的主要研究成果归纳如下:1.根据AC耦合原理,设计了一种板级电容耦合连接器,将发射端信号通过两条紧耦合传输线构成的电容耦合到接收端。

由于信号传输界面是非接触的,插入力为零,因此消除了磨损和氧化对引脚造成的影响,使信号得到更好的传输。

仿真结果表明,文中所设计的电容耦合连接器能在信号数据传输率达到4Gbps时保证信号的高质量传输。

2.根据高速互连线间的串扰耦合机理,分析了电容耦合连接器物理结构对接收端脉冲波形的影响,提出了连接器尺寸的选择策略,为电容耦合连接器的设计提供了经验法则。

3. AC耦合连接器可以用于板级互连的多Gbps信号传输,当信号的传输速率增加或使用较大的电感(电容)值时,接收端脉冲将遭受过多的符号间干扰,不能有效的恢复信号。

针对这个问题,通过分析接收端脉冲产生符号间干扰的原因,提出了驱动端均衡的方案,并给出均衡比例的计算方法。

仿真结果显示,采用驱动端均衡方案,能够有效的消除符号间干扰,可以使电感值(电容值)的选择和信号传输速率相互独立,增加了AC耦合连接器的适用范围。

4.基于微波网络理论,分析和研究了同时开关噪声的传播与抑制,提出了一种新的抑制噪声传播的多级电容法,该方法采用多列分布电容和增大噪声路径传输损耗,能够有效地抑制噪声的传播,提高电容噪声抑制的效率。

0.33uf耦合电容

材料选择与制备

电容器芯体材料的选择应考虑介 电常数、介质损耗、耐压性能等 因素。常用的芯体材料包括聚酯

薄膜、聚丙烯薄膜等。

技术发展及未来挑战预测

材料技术不断进步

新材料不断涌现,为耦合 电容的制造提供了更多的 可能性。

制造工艺持续优化

制造工艺持续优化,提高 了耦合电容的品质和性能 。

未来技术挑战预测

未来,耦合电容将面临更 严格的技术要求和更高的 性能标准。

产品升级及新产品研发方向建议

产品升级方向建议

建议向高容量、高耐压、高可靠性、 绿色环保等方向升级。

新产品研发方向建议

建议研发新型耦合电容,如微型化、 集成化、智能化等,以满足不断变化 的市场需求。

THANK YOU

外壳材料的选择应考虑机械强度 、绝缘性能、耐环境因素等因素 。常用的外壳材料包括塑料、陶

瓷、玻璃等。

环氧树脂等密封和绝缘材料的选 择应考虑粘度、固化速度、耐温 性能等因素,以确保耦合电容器

的密封性和绝缘性能。

04

0.33uf耦合电容的测试 与评估

测试方法

静电容量测试

通过使用LCR表或电桥等设备,对耦 合电容进行静电容量测试,以获得准 确的容量值。

将卷绕好的芯体浸入绝 缘液体中,以实现对外 壳的绝缘处理。

采用环氧树脂等材料将 电容器外壳密封,以防 止内部元件与外部环境 接触,同时保证电容器 具有良好的绝缘性能。

完成制造过程后,需要 进行性能检测和老化处 理,以确保耦合电容器 的稳定性和可靠性。

ac 耦合电容的容值对dc漂移-概述说明以及解释

ac 耦合电容的容值对dc漂移-概述说明以及解释1.引言1.1 概述在本文中,我们将讨论AC耦合电容的容值对DC漂移的影响。

AC耦合电容是电子电路中常见的元件,它的作用是将交流信号传入不同直流(DC)偏置点的电路中。

然而,容值的选择却可能会对系统的性能产生一定的影响。

在电子电路中,DC漂移是指电路在长时间稳定运行中的偏移现象。

这种偏移可能是由于温度变化、电路元件老化、供电不稳定等原因引起的。

DC漂移会对电路的工作稳定性和准确性产生不利影响,因此对其进行控制和补偿是非常重要的。

AC耦合电容被广泛应用于电子系统中,特别是在信号传输和放大电路中。

它起到了隔离和削弱DC偏置信号的作用,只传递交流信号。

然而,AC耦合电容的容值对于DC漂移的影响却不容忽视。

首先,大容值的AC耦合电容可以有效削弱DC漂移的影响。

它可以过滤掉大部分DC偏置信号,保持输入交流信号的准确性。

因此,在对DC 漂移要求较高的电子系统中,选择较大容值的AC耦合电容是一个明智的选择。

另一方面,小容值的AC耦合电容则会对DC漂移产生一定程度的影响。

它可能无法完全滤除DC偏置信号,从而使得系统的准确性下降。

因此,在需要较高准确性的应用中,应该谨慎选择AC耦合电容的容值。

综上所述,AC耦合电容的容值对于DC漂移具有一定的影响。

选择适当的容值可以有效削弱或降低DC漂移的影响,从而提高系统的性能和准确性。

然而,在实际应用中还需要考虑其他因素,如成本、尺寸和功耗等。

本文将进一步讨论这些因素对AC耦合电容容值选择的影响。

文章结构是指文章整体的组织和篇章的布局。

一个良好的文章结构可以帮助读者更好地理解文章的内容,并能清晰地展现文章的逻辑思路。

本文将围绕AC 耦合电容的容值对DC 漂移这一主题展开论述,文章结构如下:1. 引言1.1 概述- 在这一部分,将简要介绍AC 耦合电容和DC 漂移的概念,以及它们在电路中的重要性。

1.2 文章结构- 此处将对整篇文章的结构进行说明,包括主要部分和各个部分的涵义和连接关系。

在阻容耦合放大器中耦合电容的作用

在阻容耦合放大器中耦合电容的作用在咱们讨论阻容耦合放大器的时候,耦合电容这个小家伙可是个大明星。

想象一下,你在厨房里做饭,家里的小音响响起你最爱的歌曲,感觉倍儿爽。

但是,要是音响没电了,那可就没法享受美妙的旋律了,对吧?耦合电容就像是给音响提供电力的那条电缆,虽然它在电路中体型小,但作用可大着呢!它的主要任务就是把信号从一个地方“搬运”到另一个地方,而不让直流电影响到交流信号。

这耦合电容嘛,其实可以把它想象成一个超级过滤器。

它过滤掉那些不需要的直流成分,让交流信号轻松通过,就像把一杯茶里的杂质过滤掉,只留下清香扑鼻的茶水。

要知道,直流信号在这里可不是个好客,直接就把交流信号挤得没地方可去了。

电容在这里扮演的角色真是妙不可言。

它帮助放大器接收到的信号干净又整洁,简直就是个小小的“清道夫”。

说到这里,咱们得提到一点,耦合电容还可以调整放大器的频率响应。

听起来有点复杂,其实就是让音质更佳。

就好比你听歌的时候,有些频段的声音听起来就是更动人,耦合电容就像是调音师,帮你把那些“音痴”的部分过滤掉,让好听的旋律更显眼。

这样一来,音质自然就上升一个档次,耳朵也跟着乐开了花。

耦合电容的选择也至关重要。

别小看这小家伙,不同类型的电容会影响到整个电路的表现。

好比在选菜的时候,你总不能随便拿几根菜来炒吧,得挑新鲜的、合适的。

选择合适的电容,就能让放大器更有效地工作,信号的质量更上一层楼。

这时候,感觉就像是找到了“金钥匙”,打开了音响的新世界。

当然了,耦合电容也不是万能的,有时候它可能会影响信号的相位。

想象一下你和朋友一起合唱,结果一个人唱得早,一个人唱得晚,那可就乱套了。

耦合电容在传递信号的时候,如果没掌握好时机,可能会让信号的相位出现偏差,这样一来,音效就会大打折扣。

不过,调试得当的话,这种情况就能避免,信号的相位就会和谐得像一首动人的合唱曲。

在很多时候,耦合电容的设计也是个艺术活。

好比一个画家,得根据不同的场合调配颜色,选用合适的材料。

耦合电容的计算

耦合电容的计算耐压要看实际工作中,电容两端承受的实际直流电压是多少,如果真的要计算,还要看通过电容的交流信号的数值是多少。

那样比较麻烦,一般留实际承受直流电压的2倍的余量就够用了。

容量有这样一个公式(计算过程一律使用国际单位):F=1/(2*π*R*C)其中,F是最低截止频率,R是电容后面的负载(对于输入电容就是放大器的输入电阻,对于输出电容就是放大器的负载电阻),C就是耦合电容的数值。

关于电路的耦合问题,通常应该选取多大的电容呢,我在网上查到有这样一种计算公式: F=1/(2*π*R*C)其中,F是最低截止频率,R是电容后面的负载(对于输入电容就是放大器的输入电阻,对于输出电容就是放大器的负载电阻),C就是耦合电容的数值。

但是用这个计算出来和实际电路图上的电容值又相差很大,而且串一电容、并一电阻的组成的应该是一个高通滤波器,所以我还有一点搞不明白的时这个公式里面的频率应该是高通截止频率还是低通截止频率。

所以请大虾指教一下,这个估算方式到底对不对呢,具体应该怎么考虑呢,谢谢大家了低频情况下,选取电容的方法就跟楼主所述的差不多,原则上是越大越好,当然,计算时一般选择下限频率、补偿低频频响,音响电路里面很多时候就是这么干的。

如果还要照顾高频,那就采用两个一大一小电容并联的办法试试看。

一般估算时候采用的低端截止频率要比你需要的最低频率低5,10倍,高频则要选高5,10倍。

还要注意电容的材料和工艺,音频频段常用电解、聚丙烯和涤纶电容,几百K 用独石(低频瓷介)的足够了,上兆的就用高频瓷介,30兆以上的最好不用涤纶、低频瓷介和有长引线的铝电解,它们很有可能已经变成电感了。

射频的情况下就复杂一些,最好用半波长谐振腔法,通过做一个陷波器、观察陷波深度来测试电容的等效射频串联电阻ESR,越小越好。

本人试过用微带腔体来做,但是Q值低,测得的数值偏大,一般S波段上,只能测到陷波-30dB的水平、也就是只能测得略小于1欧姆的等效串联电阻。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

当t= 4RC时,电容电压=0.98E;

当t= 5RC时,电容电压=0.99E;

可见,经过3~5个RC后,充电过程基本结束。

放电时间计算:

初始电压为E的电容C通过R放电

V0=E,Vu=0,故电容器放电,任意时刻t,电容上的电压为:

Vt=E*exp(-t/RC)

3 电容器的阻抗在整个低频段和高频段都能兼顾,有最低的整体表现阻抗,推荐选用1nF~100nF间的电容。

今天在看SATA的内容的时候也对这个两个AC耦合电容感兴趣,查找了一些资料,又翻了一下书,找找了相关内容: 其计算经验公式为:定义Tc为每比特的数据周期,NUM为最大容许连续0或者1的比特位的数目,负载的阻抗为R(一般为50欧姆),C为交流耦合电容容值。 Cmin=7.8*NUM*Tc/R 对于SATA中我们最大的NUM数目我暂时没有查找到资料,不过《高速数字设计实践》中提及的例子可以给大家一个最初的计算方法 800Mbit/S的连接的时候 Tc=1.25ns NUM在该产品中最大的连续的0或者1,R为50欧姆的时候,计算出来Cmin最小0.0167uF,所以他提出来800Mbit/S的时候选择0.01uF的电容是不合适的。 详细请参考高速数字设计实践里面的第二章。 详细讨论可以QQ我 450911824

图4 Murata的多层陶瓷电容器的阻抗-频率特性曲线

在2节的分析中,我们认为电容器是理想的,如果考虑实际的电容器在高频段阻抗会变大的效应,导致信号的高频分量衰减变大,同样会使接收器上接收到的电压幅值跌落,也会引起信号边缘发生相位偏移,引起额外的抖动。电容值越大,高频阻抗越大,电压跌落越多,引起的抖动越大,从这一点上来说,希望交流耦合电容越小越好。

如图2所示,设差分对驱动器的单端输出信号摆幅为VPP,信号周期为TUI,20%~80%的信号上升时间为TR,连续不变码长度为N Bits,由连续不变码引起的电压跌落为ΔV,引起的信号边缘偏移(也就是PDJ)为TJ。设接收端上的初始电压(也就是加在R上的初始电压)为“1”码和“0”码电平的中间值0.5VPP,根据2节中分析的结果,经过N Bits的连续不变码的传送时间后,R上电压为:

一个真正的电容器还包括一个寄生电阻(ESR,串联等效电阻)和一个寄生电感(ESL,串联等效电感),如图7所示,实际的电容器是这三个元件的串联,会存在一个串联谐振频率。在谐振频率点之下,C起主导作用,电容器表现为电容的特性,随着频率上升,阻抗变大;在谐振频率点上,C和ESL的作用完全抵消,电容器表现为电阻的特性,阻抗达到最小值,其值大小为ESR;在谐振频率点之上,ESL起主导作用,电容器表现为电感的特性,随着频率上升,阻抗变大。也就是说,两个寄生元件,ESR决定电容器所能达到的最低阻抗,ESL使得电容器在谐振频率点之上表现为电感器的特性,失去电容器的作用,且随着频率增加,阻抗变大,而理想电容器在高频时的阻抗趋于零。

尽管一般的多层陶瓷电容器在高数据速率的系统中工作时,对外表现出高达5~10ohm的阻抗,但是对于实现交流耦合的功能而言,仍然能工作得足够好,高频下阻抗增大导致的电压跌落不大(一般<2%),导致的相移也小(一般小于10o),所以完全没有必要选用特殊的射频电容器,一般的标准多层陶瓷电容器(陶瓷介质可选NPO或X7R)就能满足要求。

进行s域到时域的拉普拉斯反变换,得到电阻上电压的时域解UR(t)为:

从结果可以看出:在t=0+时刻开关合上的时刻,电容C相当于短路,R上的电压为VDC,然后随着电容C的充电,R上的电压呈指数级别降低,当时间趋于无穷大的时候,C被VDC完全充电,其上的电压趋近VDC,R上的电压趋近0。

电容充电放电时间计算公式:

设,V0 为电容上的初始电压值;

Vu 为电容充满终止电压值;

Vt 为任意时刻t,电容上的电压值。

则,

Vt=V0+(Vu-V0)* [1-exp(-t/RC)]

如果,电压为E的电池通过电阻R向初值为0的电容C充电

V0=0,充电极限Vu=E,

如图2、图3所示,假设驱动器发送连“1”码比特流到线路上,随着时间的延续,接收器接收到的电压会逐渐降低,即图2中的LF Droop(低频衰减,因为RC电路具有高通滤波特性,所以电路的低频分量衰减较大),时间越长,LF Droop越大,一旦码型发生变化后,比如图2、3中改变为“0”码,接收器上的电压会迅速降低并反相,因为LF Droop的影响,电压降低的起点会比理想位置低,导致从“1”码到“0”码的变化边沿时刻会比理想位置有所提前,这个与理想位置的偏移量就是由AC耦合所带来的PDJ。显然,高通滤波RC电路的3dB转折频率点越低,即RC常数越大,低频分量通过得越多,LF Droop越小,PDJ就越小,因为R的值固定,所以C越大,PDJ越小,选择较大的C对抑制PDJ有利。

则对于不同的C,码型相关抖动为:

电容值 抖动 抖动与单位周期比 性能

100pF 90pS 28% 不能接受

1nF 15pS 5% 好

10nF 1.6pS <1% 很好

100nF 0.2pS ≈0 极好

从抑制抖动的观点来Байду номын сангаас,交流耦合电容C越大,传输通道的PDJ越小,系统的性能越好,但是抖动不是唯一需要考虑的问题,而是存在另一个需要考虑的方面,恰恰相反,这个规则反对使用大的电容,下面详细说明这个问题。

R上的电压跌落ΔV为:

我们需要求解的是TJ的值,现在已经知道ΔV的值,显然,如果能找到两者间的关系,TJ的值就迎刃而解了。将图5中的信号边缘偏移图示进行局部放大研究,如图3所示,可以看出,由20%~80%的Tr、0.6VPP和信号上升沿组成的直角三角形与TJ、ΔV和信号下降沿组成的直角三角形为相似形,于是有:

因此,我们在选择交流耦合电容器的时候,即不能单方面从高通滤波特性考虑选大容量的电容器,也不能单方面从ESL的角度考虑选小容量的电容器,应综合考虑电容的高通滤波特性和高频下ESL影响,选择中间值的电容器,基本原则如下:

1 电容器带来的码型相关抖动不超过单位周期的5%;

2 尽量选用小封装的电容器,小封装的高频特性优于大封装的,推荐选用0603或0402封装;

1 RC串联电路的阶跃响应

图1 RC一阶电路

如图1所示,是由RC组成的高通一阶滤波电路,在t=0+时刻开关合上,即给RC电路一个阶跃激励,0+时刻电容C上的电压为0,即没有积累电荷,求R上的响应电压。

为简化起见,对本电路运用复频域分析法,R上的电压为R和C共同分压的结果,得到电阻R电压复频域象函数UR(s)如下所示:

2 交流耦合传输通道特性分析

经过1节中的分析,可以发现,在高速互连传输系统中,在一段时间内,如果驱动器驱动到线路上为同一码型,则在这段时间内,高速互连通道的特性与1节中的完全一致,图1的C相当于图2中的AC耦合电容,R相当于接收器的50ohm终端匹配电阻,图中没有画出,同一码型持续的时间段中,接收器上接收到的电压呈指数级别降低,时间越长,电压降低越多。

根据上式就可以计算出TJ的值,TR值可以从驱动器的数据手册中查到,一定要注意是20%~80%的上升时间,如果没有找到TR的值,可以用下式进行估算:

BW为所传输信号的带宽,在一阶系统中,BW的典型值为60%~100%的数据速率。在实际应用中,如果仅仅是对TJ进行预估,建议BW取中间值,即80%的数据速率,于是:

图2 AC耦合引起的PDJ

图3 AC耦合引起的码型相关抖动

图4 PDJ估算相似三角形

下面结合图3、图4,对PDJ进行数学推导,给出解析公式,并对其值进行估计。对于差分对中的两个信号,以共同的共模电压为中心,大小相等,相位相反,从图5中可以看出,PDJ与差分对线上的共模电压大小没有关系,而与信号变化的幅度VPP(即差模电压)有关,又因为差分对的正、负相是完全对称的,所以只需对差分对的其中一个信号进行分析即可。

故,任意时刻t,电容上的电压为:

Vt=E*[1-exp(-t/RC)]

t=RCLn[E/(E-Vt)]

如果已知某时刻电容上的电压Vt,根据常数可以计算出时间t。

公式涵义:

完全充满,Vt接近E,时间无穷大;

当t= RC时,电容电压=0.63E;

当t= 2RC时,电容电压=0.86E;

图5中给出了Murata的4种不同0603封装的多层陶瓷电容器的阻抗-频率曲线,可以看出:

电容值越小, ESR越大,谐振频率点越高,电容器的高频特性越好。电容的谐振频率点都低于1GHz,对于GHz以上的高速互连传输系统而言,在系统整个带宽的高频段,电容器的工作频率不可避免的跃过谐振点,呈电感性;在四个电容器中,10nF的电容器在整个频端的保持最低的阻抗,性能最好,低频端的阻抗优于1nF和100pF的电容器,高频段的阻抗优于100nF的电容器。因此,综合考虑,对于上面的3.125G数据传输系统的举例,选择10nF的交流耦合电容最好。

t=RCLn[E/Vt]

以上exp()表示以e为底的指数;Ln()是e为底的对数。

N为最多的连续不变码的个数,与通道承载的信号类型有关;TUI是信号的单位周期;R一般为50ohm;C的值可以灵活选取,C的大小就决定了TJ的大小。

TJ的计算式可以最终简化为:

(﹡)

TJ对单位周期TUI的比值为:

(﹡﹡)

3 交流耦合电容的选取

从2节中的分析我们可以知道:随着连续不变NRZ码的长度N增加或交流耦合电容C值减小,系统的码型相关抖动PDJ会变大。如对于连续不变NRZ码的长度为20的3.125GBPS的数据信号,周期TUI为320pS,20%~80%的上升时间TR为150pS,R为50ohm,则PDJ的计算公式变为: