芯片引脚对照表

74系列芯片引脚图及逻辑功能表

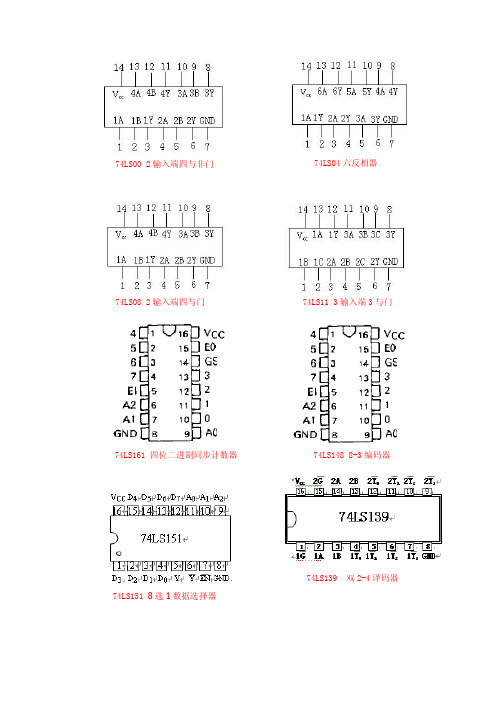

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS54——4-2-3与或非门

74LS08——2输入4与门

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门

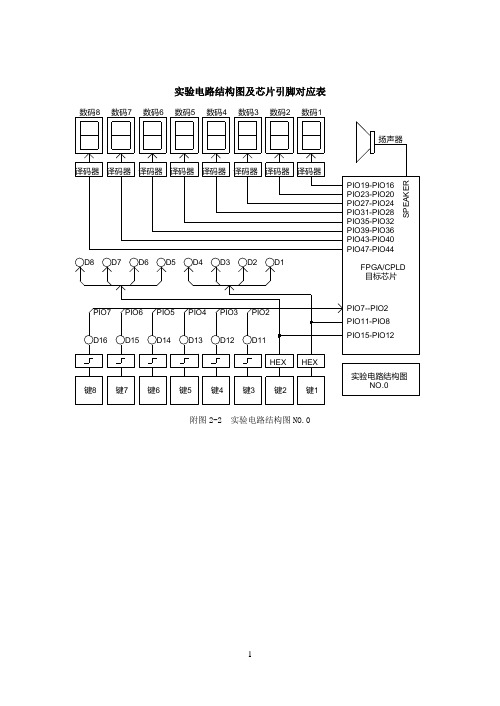

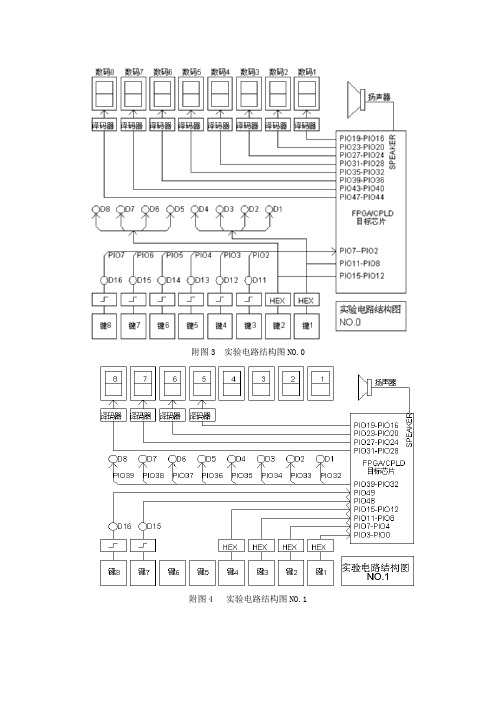

实验电路结构图及芯片引脚对应表

实验电路结构图及芯片引脚对应表NO.0实验电路结构图HEXPIO2PIO3PIO4PIO5PIO7PIO6D1D2D3D4D5D6D7D8D16D15D14D13D12D11数码1数码2数码3数码4数码5数码6数码7数码8S P E A K E R扬声器译码器译码器译码器译码器译码器译码器译码器译码器FPGA/CPLD PIO15-PIO12PIO11-PIO8PIO7--PIO2HEX 键1键2键3键4键5键6键7键8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16目标芯片附图2-2 实验电路结构图NO.0附图2-3 实验电路结构图NO.1附图2-4 实验电路结构图NO.2ʵÑéµç·½á¹¹Í¼NO.3ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷ÒëÂëÆ÷D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E RÑïÉùÆ÷12345678Ä¿±êоƬFPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7¼ü1¼ü2¼ü3¼ü4¼ü5¼ü6¼ü7¼ü8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图2-5 实验电路结构图NO.3附图2-6 实验电路结构图NO.4GNDPIO45PIO46513PS/2接口VCCJ74接PC 机串行通讯接口接口电路单片机接口电路235RS-232B412MHZA键复位P34P33P32X1X2P31P30P35RST GND12345678910VCCPIO11PIO12PIO13PIO14AT89C2051EU3P37P10P11P12P13P14P15P16P17VCC 11121314151617181920PIO15PIO24PIO25PIO26PIO27PIO28PIO29PIO30PIO317.2K P29->A14)27512(PIN30->VCC,PIN3->A15,PIN29->WE)628128(PIN30->VCC,PIN3->A14,RAM/ROMP29->WE)62256(PIN30->VCC,PIN3->A14,6264(PIN30->VCC,PIN29->WR)PIN30->A17,PIN3->A15,PIN29->A14)29C040(PIN31->WE,PIN1->A18,PIN3->A15,PIN29->A14)27040(PIN31->A18,PIN30->A17,PIN29->A14)27020(PIN30->A17,PIN3->A15,P29->A14)27010(PIN30->VCC,PIN3->A15,PIO40PIO41PIO42PIO43PIO44R78 200R77 200R76 20010548761413321 视频接口VGA J6A18/A19A18/A15/WE PIO49VCC SLA17RAM_ENVCC GND SLRAMPIO26PIO25PIO24PIO32PIO33PIO34PIO35PIO36PIO37PIO38PIO39PIO14PIO47PIO10PIO48PIO9PIO46PIO45PIO11PIO12PIO13PIO8PIO15PIO31PIO30PIO29PIO28PIO273231302928272625242322212019181716151413121110987654321VCC GND2708027040270202701027512272562764628128622566264VCC A17/VCC WR/A14A13A8A9A11OE A10CS1D7D6D5D4D3GND D2D1D0A0A1A2A3A4A5A6A7A12A14(A15)A1610K VCCVR1PIO31PIO29PIO30PIO28PIO27PIO26PIO25PIO24131415164D7D6D5D4D35D26D1D07PIO37+5JP251pFC27JP2(COMP)COMP LM311VCC10K -12+124823TL082/1AIN0AOUT1021035.1KR72765TL082/2841+12-12滤波0滤波1FITCOMMEU2DAC0832118171032WR1FB93211IOUT1IOUT212/CS WR2XFER A GND D GNDVREF8VCC 20VCCJP2(1/2,3/4)D1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实验电路结构图NO.5S P E A K E R扬声器FPGA/CPLD 目标芯片12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器译码器译码器PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7键1键2键3键4键5键6键7键8P I O 8J P 2(5/6)P I O 8(23)(24)1216272610C L O C K 750K H Z A F I T102C 30103C 29P I O 37P I O 35C O M MC O M PA D E O C A D E NJ P 22018161412108642191715131197531021+5V A I N 0A I N 1r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T附图2-7 实验电路结构图NO.5附图2-8 实验电路结构图NO.6D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器附图2-9 实验电路结构图NO.7附图2-10 实验电路结构图NO.8附图2-11 实验电路结构图NO.9附图2-12 实验电路结构图NO.BD22D21D20D19D18D17VCC87654321SDA (PIO79)SCL (PIO78)24C01GNDVCCPIO77PIO766PS/254321GNDVCCD-(PIO76)D+(PIO77)SLAVEUSB GND键12键11键9键1010K X 4PIO75PIO74PIO72PIO73VCCP I O 71P I O 76P I O 77P I O 70P I O 69P I O 68数码14数码13数码12数码11数码10数码9PIO67PIO66PIO65PIO64PIO63PIO62PIO61PIO60hg f e d c b a 888888附图2-13 实验电路结构图COM万能接插口与结构图信号/与芯片引脚对照表附录二:《EDA技术》部分实验参考源程序一、8位硬件加法器设计程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ADDER8 ISPORT ( CIN : IN STD_LOGIC;A, B : IN STD_LOGIC_VECTOR(7 DOWNTO 0);S : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);COUT : OUT STD_LOGIC );END ADDER8;ARCHITECTURE behav OF ADDER8 ISSIGNAL SINT : STD_LOGIC_VECTOR(8 DOWNTO 0);BEGINSINT <= ('0'& A) + B + CIN ;S <= SINT(7 DOWNTO 0); COUT <= SINT(8);END behav;选择实验电路NO.1验证此加法器的功能。

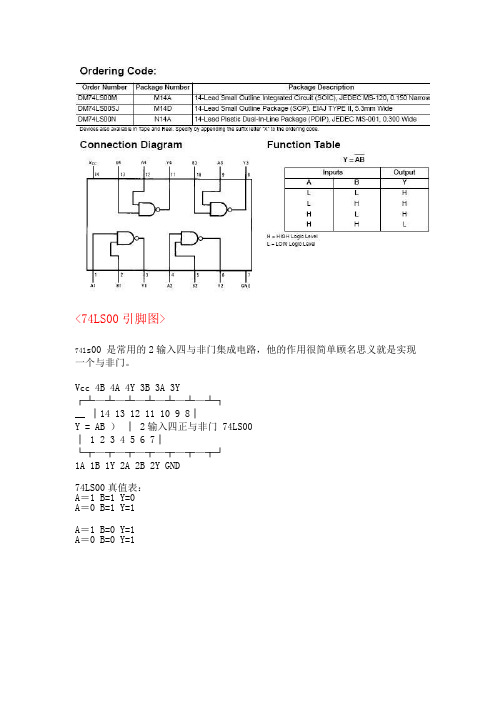

74LS系列主要芯片引脚及参数

<74LS00引脚图>74l s00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输入四正与非门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

74LS138的作用:利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这里的输入端的三个A0~1有的原理图中也用A B C表示(如74H138.pdf中所示,试用于普中科技的HC-6800 V2.2单片机开发板)。

<74ls138功能表>74LS138逻辑图无论从逻辑图还是功能表我们都可以看到74LS138的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同一个时间又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

74系列芯片引脚图

类别 电路简称 四位比较器 74LS85

A3 B3

数据输入 A2 B2 A1 B1

真值表 A0 B0

级联输入

输出

A>B A<B A=B A>B A<B A=B

A3>B3 A3<B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3 A3=B3

GND 8

7744LLSS17124

16 Vcc 15 1CLR 14 2CLR 13 2CK 12 2K 11 2J 10 2PR 9 2Q

(a) JK 触发器 74112 引脚图

Y0 1

Y1 2

Y2 3 Y3 4 Y4 5 Y5 6 Y6 7 GND 8

7474LLSS7442

16 Vcc

15 A0 14 A1

13 A2 12 A3 11 Y9 10 Y8 9 Y7

图 3.2 74LS42 引脚图

74LS04

B1

C2

LT 3 BI/RBO 4

RBI 5 D6 A7

GND 8

747L4LSS7448

16 Vcc 15 f 14 g

13 a 12 b 11 c 10 d 9e

图 3.3 74LS48 引脚图

常用 74 系列 TTL 集成电路

真值表

时钟 CP J K

X

XX

X

XX

↓

00

↓

10

↓

01

↓

11

输出 清零(Q=0) 置 1(Q=1) 保持(Q=Qn)

Q=1 Q=0 翻转(Q=/Q)

电路引脚图

类别

电路简 称

GW48结构图信号名与芯片引脚对照表

附图3 实验电路结构图NO.0附图4 实验电路结构图NO.1附图5 实验电路结构图NO.2实实实实实实实NO.3实实实实实实实实实实实实实实实实实实实实实实实实D9D16D15D14D13D12D11D10D8D7D6D5D4D3D2D1PIO8PIO9PIO10PIO11PIO12PIO13PIO14PIO15S P E A K E R实实实12345678实实实实FPGA/CPLD PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8PIO15-PIO8PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16附图6 实验电路结构图NO.3附图7 实验电路结构图NO.4D1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实实实实实实实NO.5S P E A K E R实实实FPGA/CPLD 实实实实12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16实实实实实实实实实实实实实实实实实实实实实实实实PIO15-PIO8PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8附图8 实验电路结构图NO.5附图9 实验电路结构图NO.6D16D15D14D13D12D11D9D8PIO47D7PIO46D6PIO45D5PIO44D4PIO43D3PIO42D2PIO41PIO40D1NO.7实验电路结构图S P E A K E R扬声器FPGA/CPLD 目标芯片12345678PIO0PIO2PIO3PIO4PIO5PIO6PIO7单脉冲单脉冲单脉冲键1键2键3键4键5键6键7键8PIO47-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16译码器译码器译码器译码器译码器译码器附图10 实验电路结构图NO.7附图11 实验电路结构图NO.8附图12 实验电路结构图NO.9附图13 实验电路结构图NO.B实验电路结构图 N O .5AD 16D 15D 14D 13D 12D 11D 10D 9D 8D 7D 6D 5D 4D 3D 2D 1P I O 8J P 2(1/2,3/4)J P 2(5/6)P I O 8SPEAKER目标芯片F P G A /C P L D(23)(24)1216272610C L O C K 750K H Z A 750K H Z A F I T102C 30103C 29D A -5--+5D A 0--+5P I O 38P I O 37P I O 35C O M MD A W RC O M P ADE O C A D E N J P 22018161412108642191715131197531021V R 110K V C C +5V A I N 0A I N 1r e f (-)r e f (+)I N -1I N -06922257171415818192021E U 1A D C 0809P I O 16P I O 17P I O 18P I O 19P I O 20P I O 21P I O 22P I O 23P I O 32P I O 33P I O 35P I O 34m s b 2-12-22-32-42-52-62-7l s b 2-8E O C A D D -A A D D -B A D D -C A L E E N A B L E S T A R T扬声器P I O 39-P I O 36P I O 43-P I O 40P I O 47-P I O 4412345678数码数码数码数码数码数码数码数码译码器译码器译码器单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7P I O 15P I O 14P I O 13P I O 12P I O 11P I O 10P I O 9P I O 8键1键2键3键4键5键6键7键8附图14 实验电路结构图NO.5AD 8D 7D 6D 5D 4D 3D 2D 1译码器译码器译码器D 16D 15D 14D 13D 12D 11D 10D 9实验电路结构图 N O .5BV C C目标芯片F PG A /C P L D串行通讯接口接口电路J 75413P I O 45P I O 46P S /2接口单片机接口电路235接P C 机R S -232B 412M H Z A键复位P I O 11P I O 12P I O 13P I O 14SPEAKERA T 89C 2051E U 3P 34P 33P 32X 1X 2P 31P 30P 35R S TG N D P 37P 10P 11P 12P 13P 14P 15P 16P 17V C C 1234567891011121314151617181920P I O 15P I O 24P I O 25P I O 26P I O 27P I O 28P I O 29P I O 30P I O 31扬声器P I O 39-P I O 36P I O 43-P I O 40P I O 47-P I O 4412345678数码数码数码数码数码数码数码数码单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7P I O 15P I O 14P I O 13P I O 12P I O 11P I O 10P I O 9P I O 8键1键2键3键4键5键6键7键8附图15 实验电路结构图NO.5BD 16D 15D 14D 13D 12D 11D 10D 9D 1P I O 8D 2P I O 9D 3P I O 10D 4P I O 11D 5P I O 12D 6P I O 13D 7P I O 14D 8P I O 15译码器译码器译码器实验电路结构图 N O .5CF PG A /C P L DJ P 251p F C 27J P 2(C O M P )C O M PP I O 37L M 311V C C 10K-12+124823T L 082/1A I N 0A O U T5.1K102103+510K5.1K5.1KR 72765T L 082/2841+12-12D A 0--+5D A -5--+5滤波0滤波1F I TC O M M E U 2D A C 0832********J P 2(9,10)P I O 38D A W R 2W R 1F B93211I O U T 1I O U T 212/C S W R 2X F E R A G N D D G N D V R E F 8V C C20+5V C CD 0D 1D 2D 3D 4D 5D 6D 7765416151413P I O 24P I O 25P I O 26P I O 27P I O 28P I O 29P I O 30P I O 31P I O 43-P I O 40P I O 35-P I O 32P I O 23-P I O 20P I O 19-P I O 16目标芯片P I O 47-P I O 44译码器译码器P I O 15-P I O 812345678数码数码数码数码数码数码数码数码单脉冲单脉冲单脉冲P I O 0P I O 1P I O 2P I O 3P I O 4P I O 5P I O 6P I O 7键1键2键3键4键5键6键7键8附图16 实验电路结构图NO.5CD A C C1K REFS 1KREFSNO.5DPIO34PIO27SDASCL TEST NC NC NC PIO19PIO17PIO34PIO27GNDNC NC DOUTDIN SK CS 24CXX93CXXVCC87654321VCC GNDVCC 87654321VCC TLC549VCC PIO30PIO2987654321PIO28CSDOUT I/OCK VCC GNDREF-AIN REF+JSL141312111098765PIO26PIO24PIO25PIO31VCCLOADDACD DACC DACB DACA LDAC CLKDATA REFD REFC REFB REFA TLC5620GND VCCREFSS VCC REFSJTLJAVPIO19PIO18TLV1572PIO17SCLKVCC FS DO AINGND VREF PIO34CS 87654321VCC 4321REFSSREFINCLK VCC PIO17PIO34PIO198031VIN-VIN+CS 87654321DOUT GNDADC08031VCC ADCCD1PIO8D2D3D4D5D6D7D8PIO9PIO10PIO11PIO12PIO15PIO14PIO13实实实实实实实S P E A K E R实实实FPGA/CPLD 实实实实12345678D16D15D14D13D12D11D10D9PIO47-PIO44PIO43-PIO40PIO39-PIO36PIO35-PIO32PIO31-PIO28PIO27-PIO24PIO23-PIO20PIO19-PIO16实实实实实实实实实实实实实实实实实实实实实实实实PIO15-PIO8实实实实实实实实实PIO0PIO1PIO2PIO3PIO4PIO5PIO6PIO7实1实2实3实4实5实6实7实8附图17 实验电路结构图NO.5D附录2 GW48结构图信号名与芯片引脚对照表。

74系列芯片引脚图及逻辑功能表

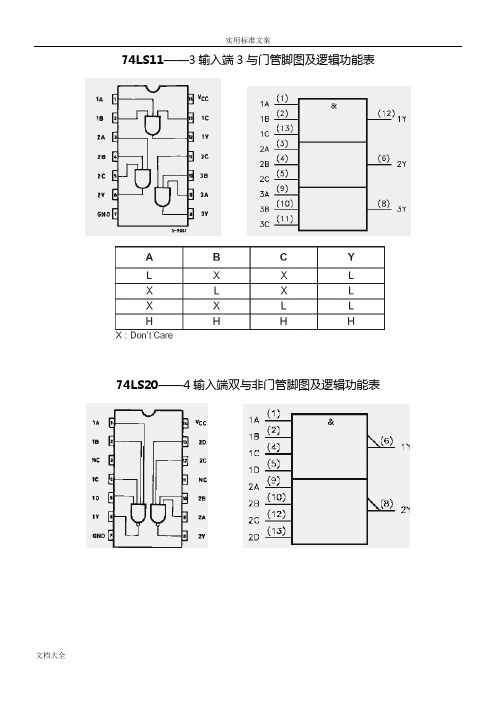

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门

74LS54——4-2-3与或非门

74LS08——2

输入4与门。

系列芯片引脚图及逻辑功能表

系列芯片引脚图及逻辑

功能表

Document serial number【NL89WT-NY98YT-NC8CB-NNUUT-NUT108】

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门

74LS54——4-2-3与或非门

74LS08——2输入4与门。

芯片引脚定义翻译

芯片引脚定义翻译引脚名称引脚定义CSH高端电流检测正向输入CSL低端电流检测反向输入FB电压反馈输入端VDD电压回馈输入端SYNC同步电压频率选择/频率设置/同步信号TIME/ON5延时电容/开关控制端SKIP低噪音模式控制器/跳频冲输入RST基准电压输出端SEQ电压转换模式控制DH高端场管驱动方波信号输出端LX电感连接反馈输入/电感检测输入端BST自举端/高低端激放电路输入端DL低端场管驱动方波信号输出端VL线性基准电压V+供电SHDN总关闭模式/总控制信号RUN/ON3开关控制SUS挂起输入/待机电压OFS偏移控制分压器输入ILIM电流限制调节CCV电压积分电容CCI电流均衡补偿OAIN-运算放大器反相输入OAIN+运算放大器同相输入VROK电源好信号BSTM自举电容LXM主电感连接端CMP主电感电流正输入CMN主电感电流负输入CSN副电感电流正输入CSP副电感电流负输入ON3电压开关控制脚ADD地址线AFC自动频率控制AGC自动增益控制AVCC音频供电BACKLIGHT背光灯开启BAT_VOLT电压检测Boost-En升压启动BUZZER振铃CS FLASH字库片选CS ROM版本片选CSRAM暂存片选DATA数据线LCD_CS显示屏片选LCD-EN显示屏启动MIC-本机话筒负极MIC+本机话筒正极ON_OFF开机触发POWER ON开机启动Reset复位VBATT电池电压TIME频率设置TON导通时间选择S0挂起模式DLM低端管驱动EC嵌入式控制器THRMTRIP温度控制VRON开机电源电压控制信号VSB待机VCCP总线供电EMI电磁抗干扰电路MOSFET方波切割组件PWM脉宽调制定义说明同步信号用于逻辑控制电路。

ISL6251(笔记本)电池充放电管理芯片引脚定义(图)(精)

ISL6251AHRZ (笔记本电池充放电管理芯片引脚定义7DDM SET ENCELLSICO HP VCOMP KM VREF CHUMAC UMVADJGND 21, 22脚CSOP/CSON:是电池的充电电流感应正/负输入。

在CSOP 的差动电压 和CSON 是用于检测电池的充电电流,并与充电电流限制门限调节充电电流。

该 CSON 管脚也可以用作电池的反馈电压来执行电压调节。

19, 20脚CSIP/CSIN:是AC 适配器电流传感正/负输入。

CSIP 的两端的差分电压 和CSIN 是用于检测AC 适配器电流,并与AC 适配器电流限制相比,调节 AC 适 配器电流。

24脚DCIN:是内部5V LDO 输入。

它连接到AC 适配器的输出。

连接 DCIN —个 0.1卩的陶瓷电容。

heftDC INACPRNCSONC4OPCSIN PHASE UGATEBOOTVbDPLGATEPGMDISL6251I, ISL6251A 124 LD aSQP) TOP VIEW2脚ACSET:是一个AC适配器检测输入。

连接到从适配器输入电阻分压器。

23脚CACPRN:是AC适配器开漏输出。

ACPRN是低电平时ACSET比通常1.26V 较高,高电平时ACSET比一般1.26V低。

3脚EN:是充电使输入。

连接中文高使充电控制功能,连接中文的充电功能低禁用。

使用的热敏电阻来检测并暂停热电池充电。

7脚ICM:是适配器的电流输出。

该引脚输出产生的电压成正比适配器的电流。

13脚PGND:是电源地。

连接PGND到的低侧MOSFET栅极驱动器低电压端MOSFET 源。

1脚VDD:是一个内部LDO输出电源IC的模拟电路。

连接一个1 X陶瓷电容接地。

15脚VDDP:是低端MOSFET栅极驱动器电源电压。

4.7 Q电阻连接到VDD和1 ^F 陶瓷电容,电源地。

5脚ICOMP:是一个电流环误差放大器输出。

6脚VCOMP:是一个循环放大器的输出电压。

常用模拟开关芯片引脚,功能及应用电路

常用模拟开关芯片引脚,功能及应用电路CMOS模拟开关是一种可控开关,它不象继电器那样可以用在大电流、高电压场合,只适于处理幅度不超过其工作电压、电流较小的模拟或数字信号。

一、常用CMOS模拟开关功能及引脚介绍1.四双向模拟开关CD4066CD4066的引脚功能如图1所示。

每个封装内部有4个独立的模拟开关,每个模拟开关有输入、输出、控制三个端子,其中输入端和输出端可互换。

当控制端加高电平时,开关导通;当控制端加低电平时开关截止。

模拟开关导通时,导通电阻为几十欧姆;模拟开关截止时,呈现很高的阻抗,可以看成为开路。

模拟开关可传输数字信号和模拟信号,可传输的模拟信号的上限频率为40MHz。

各开关间的串扰很小,典型值为-50dB。

2.单八路模拟开关CD4051CD4051引脚功能见图2。

CD4051相当于一个单刀八掷开关,开关接通哪一通道,由输入的3位地址码ABC来决定。

其真值表见表1。

“INH”是禁止端,当“INH”=1时,各通道均不接通。

此外,CD4051还设有另外一个电源端VEE,以作为电平位移时使用,从而使得通常在单组电源供电条件下工作的CMOS电路所提供的数字信号能直接控制这种多路开关,并使这种多路开关可传输峰-峰值达15V的交流信号。

例如,若模拟开关的供电电源VDD=+5V,VSS=0V,当VEE=-5V时,只要对此模拟开关施加0~5V的数字控制信号,就可控制幅度范围为-5V~+5V的模拟信号。

表1附件: 您所在的用户组无法下载或查看附件, 保暖拖鞋,就算打一天电脑也不冷收藏分享评分新洁家园致力于电气电子、软件编程、佛教、中医中药、产品开发、情感交流,是您我梦寐以求的温馨家园!回复引用订阅TOP《新洁家园论坛总版规》《论坛新增大附件上传功能》《新洁家园论坛积分等级说明》新洁电子管理员UID1帖子2557积分31797 阅读权限200在线时间979 小时2#发表于 2010-6-12 14:27 | 只看该作者3.双四路模拟开关CD4052CD4052的引脚功能见图3。

芯片引脚图

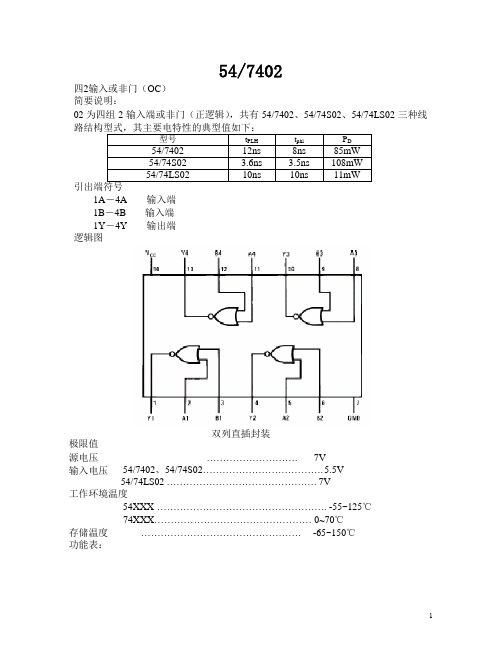

54/7402四2输入或非门(OC)简要说明:02 为四组2 输入端或非门(正逻辑),共有54/7402、54/74S02、54/74LS02 三种线1A-4A 输入端1B-4B 输入端1Y-4Y 输出端逻辑图双列直插封装极限值源电压 (7V)输入电压54/7402、54/74S02……………………………….5.5V54/74LS02 (7V)工作环境温度54XXX ……………………………………………. -55~125℃74XXX………………………………………… 0~70℃存储温度………………………………………….-65~150℃功能表:74LS00四2输入与非门简要说明00 为四组2 输入端与非门(正逻辑),共有 54/7400、54/74H00、54/74S00、54/74LS001A-4A,1B-4B 输入端1Y-4Y 输出端逻辑图双列直插封装极限值电源电压 (7V)输入电压 54/7400、54/74H00、54/74S00…………….5.5V54/74LS00 (7V)A-B 间电压除 54/74LS00 外………………………………5.5V工作环境温度 54XXX …………………. -55~125℃74XXX …………………. 0~70℃存储温度………………………………………….-65~150℃功能表:54/7408四2输入与门简要说明08 为四组2 输入端与门(正逻辑),共有54/7408、54/74S08、54/74LS08 三种线路1A-4A 输入端1B-4B 输入端1Y-4Y 输出端双列直插封装极限值电源电压 (7V)输入电压 54/7408、54/74S08……………………………… 5.5V54/74LS08 (7V)A-B 间电压 54/7408、54/74S08………………………………5.5V输出截止态电压 (7V)工作环境温度 54XXX ……………………………………………. -55~125℃ 74XXX………………………………………… 0~70℃存储温度…………………………………………. -65~150℃功能表:54/7420双4输入与非门简要说明20 为两组4 输入端与非门(正逻辑),共有54/7420、54/74H20、54/74S20、54/74LS20引出端符号1A,2A 输入端1B,2B 输入端1C,2C 输入端1D,2D 输入端1Y,2Y 输出端逻辑图双列直插封装极限值电源电压 (7V)输入电压54/7420、54/74H20、54/74S20…………….5.5V54/74LS20 (7V)A-B-C-D 间电压除54/74LS20 外………………………………5.5V工作环境温度54XXX ………………………………….-55~125℃74XXX ……………………….0~70℃存储温度………………………………65~150℃功能表:54/7454四路输入与或非门 简要说明54 为与或非门(正逻辑),其中 54/7454 是 2-2-2-2 输入端,54/74H54 是 2-2 -3-引出端符号A -H (‘H54 为 I ,’LS 为 J ) 输入端Y 输出端逻辑图54/7454 双列直插封装 ‘LS54 双列直插封装 ‘LS54PLCC 封装极限值电源电压 (7V)输入电压54/7454…………………………………………. 5.5V54/74LS54 (7V)A-B,C-D,E-F,G-H 间电压54/7454…………………………………………. 5.5V工作环境温度54XXX ……………………………………………. -55~545℃74XXX………………………………………… 0~70℃存储温度………………………………………….-65~150℃原理图:74ls13874HC138管脚图:74LS138 为3 线-8 线译码器,共有 54/74S138和54/74LS138 两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

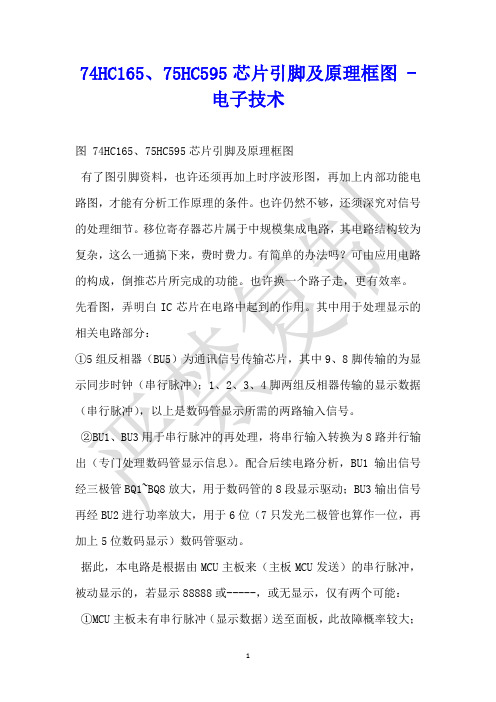

74HC165、75HC595芯片引脚及原理框图 - 电子技术

74HC165、75HC595芯片引脚及原理框图 -电子技术图 74HC165、75HC595芯片引脚及原理框图有了图引脚资料,也许还须再加上时序波形图,再加上内部功能电路图,才能有分析工作原理的条件。

也许仍然不够,还须深究对信号的处理细节。

移位寄存器芯片属于中规模集成电路,其电路结构较为复杂,这么一通搞下来,费时费力。

有简单的办法吗?可由应用电路的构成,倒推芯片所完成的功能。

也许换一个路子走,更有效率。

先看图,弄明白IC芯片在电路中起到的作用。

其中用于处理显示的相关电路部分:①5组反相器(BU5)为通讯信号传输芯片,其中9、8脚传输的为显示同步时钟(串行脉冲);1、2、3、4脚两组反相器传输的显示数据(串行脉冲),以上是数码管显示所需的两路输入信号。

②BU1、BU3用于串行脉冲的再处理,将串行输入转换为8路并行输出(专门处理数码管显示信息)。

配合后续电路分析,BU1输出信号经三极管BQ1~BQ8放大,用于数码管的8段显示驱动;BU3输出信号再经BU2进行功率放大,用于6位(7只发光二极管也算作一位,再加上5位数码显示)数码管驱动。

据此,本电路是根据由MCU主板来(主板MCU发送)的串行脉冲,被动显示的,若显示88888或-----,或无显示,仅有两个可能:①MCU主板未有串行脉冲(显示数据)送至面板,此故障概率较大;②BU5、BU1、BU2、BU3等电路异常,此故障概率较小。

先不管芯片好坏,测量BU5相关输入、输出引脚的串行脉冲信号,此处推荐采用示波器测量较为准确,若有一路是存在的,则说明主板MCU已经工作(该两路脉冲是主板MCU已经正常工作的标志)。

若两路俱无,则故障检修方向已经明确指向排线端子及主板MCU基本工作条件电路。

若脉冲正常,而显示异常,检修方向即指向面板电路。

例如针对74HC595芯片,①只要测知输入11脚串行脉冲(显示时钟)和输入14脚串行脉冲(显示数据)正常,②则其余8个“段驱动”信号输出脚,至少有数个脚应有脉冲电压(如2.5V左右)输出。

74161引脚功能表

74161引脚功能表74161 是一种常见的四位同步二进制计数器芯片,在数字电路中有着广泛的应用。

为了更好地理解和使用 74161 芯片,了解其引脚功能是至关重要的。

下面将详细介绍 74161 的引脚功能。

74161 一共有 16 个引脚,分别具有不同的功能。

引脚 1 是清零端(CLR),低电平有效。

当该引脚输入低电平时,计数器会被立即清零,输出为 0000 状态。

引脚 2 是时钟输入端(CLK),上升沿有效。

也就是说,在时钟信号的上升沿时,计数器会进行计数操作。

引脚 3 和引脚 4 分别是预置数数据输入端(A 和 B),用于输入预置的二进制数值。

引脚 5 和引脚 6 同样是预置数数据输入端(C 和 D),与引脚 3 和引脚 4 一起构成四位预置数。

引脚 7 是使能端(ENP),高电平有效。

引脚 8 是使能端(ENT),高电平有效。

只有当 ENP 和 ENT 都为高电平时,计数器才能在时钟信号的作用下进行计数。

引脚9 是进位输出端(RCO),当计数器计数达到最大值1111 后,在下一个时钟上升沿,该引脚会输出一个高电平脉冲,表示进位。

引脚 10 到引脚 13 分别是计数器的输出端(QA、QB、QC 和 QD),用于输出当前的计数值。

引脚 14 是预置数控制端(LOAD),低电平有效。

当该引脚为低电平时,将预置数数据加载到计数器中。

引脚 15 和引脚 16 分别接电源(VCC)和地(GND),为芯片提供工作所需的电源。

在实际应用中,我们可以根据具体的需求灵活配置 74161 的引脚。

例如,如果需要实现特定的计数序列,可以通过预置数功能来设置初始值;如果需要多个计数器级联,就可以利用进位输出端来连接下一级计数器。

通过对 74161 引脚功能的深入理解,我们能够更加有效地设计和实现各种数字逻辑电路。

比如,在计数器的扩展中,我们可以将多个74161 芯片连接起来,以实现更多位数的计数。

假设我们要设计一个从 0 计数到 9 的十进制计数器,就可以利用74161 的清零端和预置数功能。

芯片cd4511引脚图与管脚功能资料

芯片cd4511引脚图与管脚功能资料

CD4511是BCD锁存/7段译码器/驱动器,常用的显示译码器件,MAX7219和他功能差不多。

cd4511引脚图资料

CD4511引脚功能:

BI:4脚是消隐输入控制端,当BI=0 时,不管其它输入端状态是怎么样的,七段数码管都会处于消隐也就是不显示的状态。

LE:锁定控制端,当LE=0时,允许译码输出。

LE=1时译码器是锁定保持状态,译码器输出被保持在LE=0时的数值。

LT:3脚是测试信号的输入端,当BI=1,LT=0 时,译码输出全为1,不管输入DCBA 状态如何,七段均发亮全部显示。

它主要用来检测数7段码管是否有物理损坏。

A1、A2、A3、A4、为8421BCD码输入端。

a、b、c、d、e、f、g:为译码输出端,输出为高电平1有效。

CD4511的里面有上拉电阻,可直接或者接一个电阻与七段数码管接口。

74ls系列主要芯片引脚及参数.doc

74ls系列主要芯⽚引脚及参数.doc<74LS00引脚图>74l s00 是常⽤的2输⼊四与⾮门集成电路,他的作⽤很简单顾名思义就是实现⼀个与⾮门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│ 2输⼊四正与⾮门 74LS00│ 1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=174HC138基本功能74LS138 为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138⼯作原理如下:当⼀个选通端(G1)为⾼电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的⼆进制编码在⼀个对应的输出端以低电平译出。

74LS138的作⽤:利⽤G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接⼀个反相器还可级联扩展成32 线译码器。

若将选通端中的⼀个作为数据输⼊端时,74LS138还可作数据分配器⽤与⾮门组成的3线-8线译码器74LS138图74ls138译码器内部电路3线-8线译码器74LS138的功能表备注:这⾥的输⼊端的三个A0~1有的原理图中也⽤A B C表⽰(如74H138.pdf中所⽰,试⽤于普中科技的HC-6800 V2.2单⽚机开发板)。

<74ls138功能表>74LS138逻辑图⽆论从逻辑图还是功能表我们都可以看到74LS138的⼋个输出管脚,任何时刻要么全为⾼电平1—芯⽚处于不⼯作状态,要么只有⼀个为低电平0,其余7个输出管脚全为⾼电平1。

如果出现两个输出管脚在同⼀个时间为0的情况,说明该芯⽚已经损坏。

当附加控制门的输出为⾼电平(S=1)时,可由逻辑图写出74ls138逻辑图由上式可以看出,在同⼀个时间⼜是这三个变量的全部最⼩项的译码输出,所以也把这种译码器叫做最⼩项译码器。

74系列芯片引脚图及逻辑功能表

74LS11——3输入端3与门管脚图及逻辑功能表

74LS20——4输入端双与非门管脚图及逻辑功能表

74LS21——4输入端双与门管脚图及逻辑功能表

74LS27——3输入端三或非门管脚图及逻辑功能表

74LS42——BCD/十进制译码器管脚图及逻辑功能表

74LS138——3-8线译码器管脚图及逻辑功能表

74LS139——双2-4线译码器管脚图及逻辑功能表

74LS148——8-3线优先编码器管脚图及逻辑功能表

74LS151——八选一数据选择器管脚图及逻辑功能表

74LS153——双4选1数据选择器管脚图及逻辑功能表

74LS47——4线7段显示译码器,低电平有效,驱动共阳数码管

74LS55——双4输入与或非门74LS54——4-2-3与或非门

74LS08——2输入4与门

如有侵权请联系告知删除,感谢你们的配合!。