第6章DSP片内外设资料

第6章 'C54x片内外设6

第6章 TMS320C54x片内外设 TMS320C54x片内外设

(2) 软件配置的PLL 软件配置的PLL ② 软件PLL的工作方式 软件PLL PLL的 通过软件编程,可以使软件PLL PLL实现两种工作 通过软件编程,可以使软件PLL实现两种工作 方式: 方式: PLL方式,即倍频方式。 PLL方式,即倍频方式。 方式 芯片的工作频率等于输入时钟CLKIN乘以PLL 芯片的工作频率等于输入时钟CLKIN乘以PLL的 CLKIN乘以PLL的 乘系数,共有31个乘系数,取值范围为0 25~15。 31个乘系数 乘系数,共有31个乘系数,取值范围为0.25~15。 DIV方式,即分频方式。 DIV方式,即分频方式。 方式 对输入时钟CLKIN进行2分频或4分频。 对输入时钟CLKIN进行2分频或4分频。 CLKIN进行

时钟方式 方案一

工作频率=外部时钟源× 工作频率=外部时钟源×3 工作频率=外部时钟源× 工作频率=外部时钟源×2 工作频率=内部时钟器× 工作频率=内部时钟器×3 工作频率=外部时钟源÷ 工作频率=外部时钟源÷2 工作频率=内部时钟器÷ 工作频率=内部时钟器÷2 工作频率=外部时钟源× 工作频率=外部时钟源×1 停止工作

2012年 13日 2012年1月13日

时钟频率 = (PLL×N) PLL×

DSP原理及应用 DSP原理及应用 8

第6章 TMS320C54x片内外设 TMS320C54x片内外设

2.锁相环 2.锁相环PLL 锁相环PLL (2) 软件配置的PLL 软件配置的PLL 软件配置的PLL具有高度的灵活性。 软件配置的PLL具有高度的灵活性。它是利用 PLL具有高度的灵活性 编程对时钟方式寄存器CLKMD的设定,来定义PLL CLKMD的设定 PLL时 编程对时钟方式寄存器CLKMD的设定,来定义PLL时 钟模块中的时钟配置。 钟模块中的时钟配置。 软件PLL 软件PLL的时钟定标器提供各种时钟乘法器系 PLL的时钟定标器提供各种时钟乘法器系 并能直接接通和关断PLL PLL。 数,并能直接接通和关断PLL。 软件PLL的锁定定时器可以用于延迟转换PLL 软件PLL的锁定定时器可以用于延迟转换PLL的 PLL的锁定定时器可以用于延迟转换PLL的 时钟方式,直到锁定为止。 时钟方式,直到锁定为止。

dsp片内外设

第六章:片内外设 ——可编程定时器 初始化定时器:

(1) 将TCR中的TSS位置1,停止定时器。

(2。

(4) 重新启动定时器。TSS位为0,TRB位为l, 以重载定时器周期值, 使能定时器。

使能定时器中断(假定INTM=1): (1) 将IFR中的TINT位置1,清除尚未处理完(挂起)的定时器中断。 (2) 将IMR中的TINT位置l,使能定时器中断。 (3) 可以将ST1中的INTM位清0,使能全局中断。

控制扩展寄存器(BSPCE)控制,其各位的定义如表6-5所示。

第六章:片内外设 ——串行口 缓冲工作模式的操作过程

其功能主要由自动缓冲单元ABU来完成

• 自动缓冲单元(ABU)可独立于CPU自动完成控制串行口与固定 缓冲内存区中的数据交换。它包括

地址发送寄存器(AXR)

块长度发送寄存器(BKX) 地址接收寄存器(ARR) 块长度接收寄存器(BKR) 串行口控制寄存器(BSPCE) • 当发送或接收缓冲区的一半或全部满或空时,ABU才产生CPU 的中断,避免了CPU直接介入每一次传输带来的资源消耗。

• ABU利用独立于CPU的专用总线,让串行口直接读/写C54x内 部存储器。这样可以使串行口处理事务的开销最省,并能达到 较快的数据率。 • BSP有两种工作方式:非缓冲方式和自动缓冲方式。

• ABU具有自身的循环寻址寄存器组,每个都与地址产生单元 相关。发送和接收缓冲存储器位于一个指定的C54x DSP内部存 储器的2K字块中。该块可作为通用的存储器,但却是唯一的自 动缓冲能使用的存储块。

第六章:片内外设 ——可编程定时器 CounterSet .set 100 PERIOD .set 49999 .asg AR1,Counter ;定义计数次数 ;定义计数周期 ;AR1做计数指针,重 新命名以便识别 STM #CounterSet,Counter ;设计数器初值 STM #0000000000010000B,TCR ;停止计数器 STM #PERIOD,TIM ;给TIM设定初值49999 STM #PERIOD,PRD ;PRD与TIM一样 STM #0000011001101001B,TCR;开始定时器 STM #0008H,IMR ;开TIME0的中断 RSBX INTM ;开总中断 NOP B End

DSP课件乔瑞萍第6章TMS320C54x片内外设

第6章 TMS320C54x片内外设

No No No No No

IDLE2 Yes Yes Yes No No No No

IDLE3 Yes Yes Yes Yes No No No

HOLD

Yes No No No Yes Yes Yes

操作特性 CPU暂停 CPU时钟停止 外围电路时钟停止 锁相环(PLL)停止 外部地址线处高阻状态 外部数据线处高阻状态 外部控制信号处高阻状态

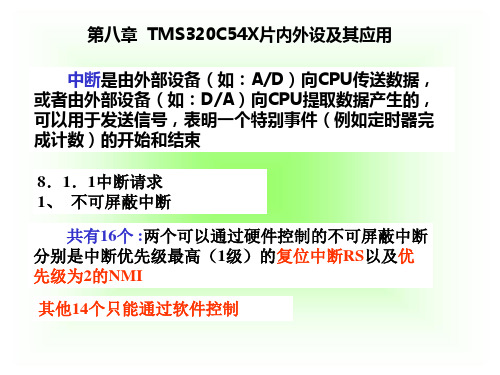

1) 可屏蔽中断 可屏蔽中断是可用软件来屏蔽或开放的中断,即 通过对中断屏蔽寄存器(IMR)中的相应位和状态寄存器 (ST1)中的中断允许控制位INTM编程来屏蔽或开放该 中断。TMS320C54x最多可以支持16个用户可屏蔽中断 (SINT15~SINT0),但有的处理器只用了其中的一部分。 有些中断有两个名称,如TMS320C541。

第6章 TMS320C54x片内外设

IPTR=000000001

IN T=48H (IN T2)

向量0 0 0 0

位15141312

地址

0

0000 1110 9 8

0

1100 7654

C

1000 3210

8

图6-5 中断向量地址的形成

第6章 TMS320C54x片内外设

6.2.2 中断流程 1.接受中断请求 当发生硬件和软件指令请求中断时,IFR中相应的

第6章 TMS320C54x片内外设

6.1.2 时钟模块编程 软件可编程PLL可以对时钟方式寄存器(CLKMD)

编程加载,以配置成所要求的时钟方式。CLKMD寄存 器是16位存储器映像寄存器,地址为0058H。它是用来 定义PLL时钟模块中的时钟配置。CLKMD的结构如图 6-2所示。

第6章片内外设d

第六章:片内外设 ——可编程定时器

6.2 可编程定时器

6.2.1 定时器的结构及特点

• C5402内部有定时器0和定时器1两个定时器。结构一样. • 每个定时器有3个控制寄存器,都是存储器映像寄存器,表6-1 TIM定时器寄存器:是减1计数器,可加载周期寄存器PRD的值, 并随计数减少。

PRD定时器周期寄存器:PRD中存放定时器的周期计数值,提供

第六章:片内外设 ——主机接口HPI

6.4.1 标准8位主机接口HPI8

1. HPI8的特点

• • • 是一个8位并行口 用于主机(其他控制器)与C54x DSP的通信,实现主机访问 DSP的内部2K的双口RAM(HPI存储器)。 HPI具有两种工作模式: 主机具有访问优先权,C54x DSP等待一个周期。 (2) 仅仅主机访问模式(HOM) • HPI支持主机与C54x DSP之间高速传输数据。

问题: 54x系列DSP其内部存储器有限,在应用时有时需要扩展外 部存储器. 但可能产生流水线冲突; 同时由于DSP工作频率高,与外 部存储器和外设接口时有时序问题。

HINT : C54x DSP向主机发出中断位。

第六章:片内外设 ——主机接口HPI

主机与HPI8的连接

第六章:片内外设 ——主机接口HPI 4. 主机接口的操作

• 8位数据总线(HD0~HD7)与主机之间交换信息。 16位字 ,HBIL

引脚 和HPIC的BOB位决定; • 两个控制输入(HCNTL0和HCNTL1)表示哪个HPI寄存器被访问 • 主机可以中断C54x DSP。C54x DSP也可用HPIC中的HINT来中 断主机。

第六章:片内外设

——概述

片内外设:串行接口、定时器、通用I/O引脚和标准主机接口

《DSP片内外设》课件

DSP片内外设功能

时钟与定时器

功能:提供精确的时钟信号和定时功能 应用:用于控制DSP片内外设的运行和操作 特点:高精度、低功耗、可编程 工作模式:单次触发、循环触发、连续触发等

中断控制器

功能:处理来自片内外设的中断请求

结构:包括中断源、中断控制器、中断服务程序 工作原理:中断源产生中断请求,中断控制器接收并处理,最后由中断 服务程序执行 应用:广泛应用于实时控制系统、通信系统等领域

存储器类型:随机存取存储器(RAM)和只读存储器(ROM) 存储器大小:根据DSP芯片的型号和规格而定 存储器访问速度:直接影响DSP芯片的处理速度 存储器映射:将物理地址空间映射到逻辑地址空间,便于访问和操作

输入输出接口

输入接口:用于接收外部信号,是DSP与外部设备进行数据传输的通道 输出接口:用于将DSP处理后的信号输出到外部设备,实现控制或数据传 输功能 接口类型:并行接口、串行接口、GPIO接口等

DSP片内外设应用实例

数字音频处理应用实例

数字音频处理:将 模拟音频信号转换 为数字信号进行处 理

应用实例:音乐播 放器、语音识别系 统、音频处理软件 等

特点:高保真、低 延迟、高稳定性

技术实现:DSP片 内外设、音频编解 码算法、音频处理 算法等

图像处理应用实例

图像增强:提高图像质量,如对比度、亮度、色彩饱和度等 图像去噪:去除图像中的噪声,如高斯噪声、椒盐噪声等 图像分割:将图像中的不同区域分割开来,如边缘检测、阈值分割等 图像识别:识别图像中的物体或特征,如人脸识别、车牌识别等

接口特点:高速、稳定、灵活,可满足多种应用需求

总线结构

总线类型:数据总线、地址总 线、控制总线

数据总线:用于传输数据,如 指令、数据等

第6章 C54x系列DSP的外设及应用 《DSP原理及实践应用》电子课件

第六章 C54X系列DSP的外设及应用

#include "cpu_reg.h" int j; int ms; ioport unsigned portf000; int motor; void main() { asm(" STM #0000h,CLKMD "); while(*CLKMD & 0x01 ); asm(" STM #97FFh,CLKMD "); //设置CPU运行频

PSC:定时器预定标计数器。这是一个减1 计数器, 当PSC减到0后,TDDR寄存器的值装载到PSC寄存器, TIM减1。PSC可被TCR读取,PSC的作用相当于预分 频器。

第六章 C54X系列DSP的外设及应用

TRB : 定时器重新加载位,用来复位片内定时器。当 TRB=1时,TIM寄存器装入PRD寄存器中的数,并且预定标 计数器PSC装入TDDR寄存器中的值。TRB总是读成0。

率=100M /* 40C7h:5*clkin =100M 30c7h:4*clkin =80M 20c7h:3*clkin =60M 10C7h:2*clkin =40M */

第六章 C54X系列DSP的外设及应用

asm(" stm #4240h, SWWSR "); //等待片上的程序1

asm(" stm #00a0h, PMST "); //MP/MC = 0, IPTR = 001,ovly=0

if(motor == 0x0) motor=0x8; /* 只有低4 位有效 */ }

第六章 C54X系列DSP的外设及应用

while(ms<100); ms=0; asm(" SSBX XF "); //位置位 motor=0x8; for(j=0;j<6;j++) { portf000=motor; /* send drive pluse to motor */ motor=motor >> 1; if(motor == 0x0) motor=0x8; /* 只有低4 位有效 */

第6章 DSP系统初始化及中断..

第六章DSP片内外设

特点: (1) 发送与接收的帧同步和时钟同步信号完全独立。 (2) 发送和接收部分可独立复位。 (3) 串口的工作时钟可来源于片外或片内。 (4) 独立的发送和接收数据线。 (5) 具有数据返回方式,便于测试。 (6) 在程序调试时,工作方式可选。 (7) 可以以查询和中断两种方式工作。

2.串行口控制寄存器(SPC) • 串行口的操作是由串行口控制寄存器(SPC)决定的。 • SPC寄存器的控制位及功能如表6-4所示—P170-171。

XF=0 *AR2=0

XF=1 *AR2=1

end

POPM ST0 RETE

6.3 串 行 口 串口分为4种: • 标准同步串口(SP) • 带缓冲的串行接口(BSP) • 时分复用(TDM)串行口 • 多通道缓冲串口(McBSP) 配置: 芯片不同串口配置也不尽相同, C5402具有两个多通 道缓冲串口(McBSP) 访问: 串行接口一般通过中断来实现与核心CPU的同步。 功能: 串行接口可以用来与串行外部器件相连,如编码解码器、 串行A/D或D/A以及其他串行设备。

定时器的中断周期 TCLK (TDDR 1) (PRD 1)

定时器的工作过程

or 3

0025H

周期寄存器 PRD

0024H

定时寄存器 TIM(16位)

借位

or 2

预定标分频系数 TDDR

预定标计数器 PSC(4位) 借位

or

SRESET

1

TRB

0026H

&

CLKOUT TSS

TINT 1

6.2.2 定时器的控制寄存器TCR

TCR 0026h

15 ~ 12

保留

11

Soft

10

DSP(知识点+思考题)

DSP复习要点第一章绪论1、数的定标:Qn表示。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示2、‟C54x小数的表示方法:采用2的补码小数;.word 32768 *707/10003、定点算术运算:乘法:解决冗余符号位的办法是在程序中设定状态寄存器STl中的FRCT位为1,让相乘的结果自动左移1位。

第二章CPU结构和存储器设置一、思考题:1、C54x DSP的总线结构有哪些特点?答:TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB):传送从程序存储器的指令代码和立即数。

(2)、三组数据总线(CB,DB和EB):连接各种元器件,(3)、四组地址总线(PAB,CAB,DAB和EAB)传送执行指令所需要的地址。

2、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

1)、累加器A和B分为三部分:保护位、高位字、地位字。

保护位保存多余高位,防止溢出。

2)、桶形移位寄存器:将输入数据进行0~31bits的左移(正值)和0~15bits的右移(负值)3)、乘法器/加法器单元:能够在一个周期内完成一次17*17bit的乘法和一次40位的加法4)、比较选择和存储单元:用维比特算法设计的进行加法/比较/选择运算。

5)、CPU状态和控制寄存器:状态寄存器ST0和ST1,由置位指令SSBX和复位指令RSBX控制、处理器模式状态寄存器PMST2-3、简述’C54x DSP的ST1,ST0,PMST的主要功能。

答:’C54x DSP的ST1,ST0,PMST的主要功能是用于设置和查看CPU的工作状态。

•ST0主要反映处理器的寻址要求和计算机的运行状态。

DSP片内外设及应用

中断标志寄存器IFR

当CPU接收到可屏蔽中断请求时,IFR相应的位置1,直 到中断得到处理为止.

图7-2

中断标志寄存器(IFR)结构图

接收中断请求

IFR的相应位置位 否 可屏蔽 中断 不可屏 蔽中断

否

中断可屏蔽? 是

图 、 中 断 操 作 流 程

INTM=0? 关闭所有可屏 是 开放所有可屏 IMR屏蔽位为1? 中断是否被屏蔽 否 是 中断被响应 IACK中断信号产生 是

5.链接命令文件 times.cmd如下:

MEMORY {PAGE 0: RAM1: origin =1000h ,length =500h PAGE 1: SPRAM1: origin=0060h,length=20h SPRAM2: origin=0100h,length=200h } SECTIONS { .text :>RAM1 PAGE 0 .data :>RAM1 PAGE 0 vars :>SPRAM1 PAGE 1 STACK :>SPRAM2 PAGE 1 }

将定时器设置为1ms,中断服务程序中计数期设置为1000, 则在计数1ms X 1000=1s 输出取反一次,得到一个周期为2S的方波

为将定时器设置为1ms,设定TDDR=9 ,则:

设置周期寄存器PRD:

t 1103 PRD 1 1639 9 T (1 TDDR ) 6110 (1 9)

(3)设置定时控制寄存器TCR: 15~12位设置为0000 11 位(soft)=0和10位(free)=1 9~6位预定标计数器PSC=TDDR=1001 5位定时器重新加载控制位,TRB=1 4位定时器停止控制位:TSS=0,定时器启动开始工作 3~0预标定分频系数:TDDR=1001H

DSP技术及其应用_第6讲_TMS320C54x DSP的片内外设

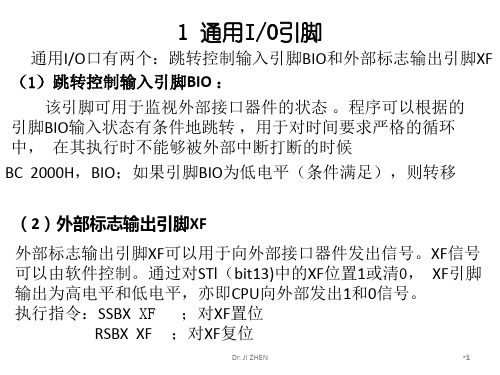

• XF(外部标志输出引脚):

– 软件控制,可以用来给外部器件发信号。通过对ST1中 的XF字段置位或清零来对XF引脚的输出电位进行控制。 – SSBX(状态寄存器置位)和RSBX (状态寄存器复位) 指令可以分别对XF进行置位和清零。

C54x系列DSP的片内外设

• • • • • • • • 通用IO引脚(BIO和XF) 时钟产生器 定时器 JTAG(IEEE1149.1) 外部总线接口 串口 主机接口HPI 直接存储器访问(DMA)控制器

C54x系列DSP的片内外设

• • • • • • • • 通用IO引脚(BIO和XF) 时钟产生器 定时器 JTAG(IEEE1149.1) 外部总线接口 主机接口(HPI) 串口 直接存储器访问(DMA)控制器

HPI

引 脚 图

HPI(Host Port Interface)

• 并行口,用来与一个主器件或主处理器连接。 • 通过C54x DSP片内既能被主机访问也能被 C54x访问的存储器,在主机和C54x DSP之间 交换信息。 • 主机接口的类型

– 共享访问 – 主机独享

• 主机独享模式下允许非同步主机访问

标准型主机接口

• 主机是接口的控制者。 • 主机通过标准型HPI可访问C54x DSP片内固定的2K RAM • 主机通过专用的地址、数据寄存器和HPI控制寄存器与 HPI通信,直接使用外部数据和控制信号进行控制, C54x DSP不能直接访问这些专用地址和数据寄存器,但 主机和C54x都能直接访问HPI控制寄存器。 • HPI将16位数据分成两个8位数据进行传递。 • 操作模式

时钟产生器

• 设计者可以通过时钟产生器选择时钟源。可驱 动时钟产生器的时钟源有:

– 一个带有内部振荡器电路的晶振。晶振电路跨接在 C54x DSP 的X1和X2/CLKIN 引脚之间。CLKMD 引脚 必须设置以启动内部振荡器。 – 一个外部时钟。外部时钟源直接连接到X2/CLKIN 引 脚, X1引脚悬空。

DSP原理与应用2011-第六章 TMS320F28335片内外设_CAN,SPI

DSP原理与应用The Technology & Applications of DSPs 第六讲TMS320F28335片内外设---CAN,SPI北京交通大学电气工程学院夏明超郝瑞祥万庆祝mchxia@haorx@qzhwan@TMS320F28335---CAN,SPI 第六讲片内外设,教学目标:掌握TMS320F28335芯片现场总线CAN通信接口,SPI串行外设接口通信相关知识;教学重点:掌握TMS320F28335芯片常用串行通信接口的特点和应用.教学难点:现场总线CAN通信编程及应用.教学内容:第一节:TMS320F28335系列SPI通信接口第二节: TMS320F28335系列CAN总线通信接口6.1.1 TMS320F2833x SPI§6S30833系列S通信SPI模块的主要特点:◆四个外部引脚SPISOMI: SPI slave-output/master-input pinSPISIMO: SPI slave-input/master-output pinSPISTE: SPI slave transmit-enable pinSPISTE:SPI slave transmit enable pinSPICLK: SPI serial-clock pin◆两个可编程模式: 主(master)和从(slave)◆125种可编程波特率设置.◆数据长度1至16位.◆四种时钟模式◆接收和发送可同时操作◆12个SPI模块控制寄存器◆增强特性16级发送/接收FIFO;延时传输控制.SPI 模块C PU 接口SPI 模块内部结构框图§6.1.2 典型SPI主/从通信连接模式一) (MASTER)()主模式()在该模式下(MASTER/SLAVE = 1), SPI模块通过SPICLK引脚提供整个串行通信网络的时钟. 数据通过SPISOMI引脚接收. SPIBRR寄存器决定网络上发送和接收的波特率。

DSP在片外围电路PPT演示文稿

• HPI数据锁存器(HPID,只能由主机访问)

– 主机读写数据的缓存

• HPI控制寄存器(地址:002Ch) • HPI控制逻辑(HPIC)

– 处理HPI与主机之间的接口信号

•3

5 TRB - 定 时 器 重 新 加 载 位 ,用 来 复 位 片 内 定 时 器 。当 TRB 置 1 时 ,

以 PRD 中 的 数 加 载 TIM , 以 及 以 TD D R 中 的 值 加 载 PSC。

TRB 总 是 读 成 0

4 TSS

0 定 时 器 停 止 状 态 位 , 用 于 停 止 或 启 动 定 时 器 。复 位 时 , TSS

0 到断点时定时器的工作状态。

Free soft

定时器状态

0

0 定时器立即停止工作

0

1 当计数器减到 0时停止工作

1 × 定时器继续运行

9~6 PSC - 定 时 器 预 先 定 标 计 数 器 。 这 是 一 个 减 1 计 数 器 , 当 PSC 减

到 0 后 。 TD D R 位 域 中 的 数 加 载 到 PSC, TIM 减 1

(2)TRC定时器控制寄存器各位含义

15-12

11

保留

soft

10

9-6

5

4

3-0

free

PSC

TRB

TSS TDDR

预定标 定时器重 定时器停 定时器分 新加载1 止状态1 频系数

•9

定时器控制寄存器(TCR)的功能

位 15~12

11 soft 10 Free

第6章 DSP片内外设

定时器初始化步骤如下: 定时器初始化步骤如下: ① TCR的TSS位置1,关闭定时器,停止定时; TCR的TSS位置 位置1 关闭定时器,停止定时; ② 装载PRD值; 装载PRD PRD值 ③ 重新装入TCR,初始化TDDR,设置TSS=0和TRB=1,重 重新装入TCR 初始化TDDR 设置TSS= TCR, TDDR, TSS=0 TRB=1 装载定时器周期。启动定时器。 装载定时器周期。启动定时器。 设置定时器中断方法(INTM=1)如下: 设置定时器中断方法(INTM=1)如下: 如下 ● 将IFR中的TINT置1,以清除尚未处理完的定时器中断; IFR中的TINT置 以清除尚未处理完的定时器中断; 中的TINT ● 将IMR中的TINT置1,启动定时器中断。 IMR中的TINT置 启动定时器中断。 中的TINT ● 将INTM置0,启动全部中断。 INTM置0,启动全部中断 启动全部中断。

结构和特点( 结构和特点(P169)

收发模块相互独立 时钟信号可以选择内部或者外部 回环模式(用于测试 用于测试) 回环模式 用于测试) 2种工作方式:查询和中断 种工作方式: 种工作方式

DSP技术讲义,2007,陈军波电子信息工程学院

工作过程(教材 工作过程(教材P169) )

缓冲寄存器 移位寄存器 串并转换 CPU的读写 的读写 工作方式: 种 工作方式:2种

DSP技术讲义,2007,陈军波电子信息工程学院

预定标模块包括TCR中的TDDR PSC位 预定标模块包括TCR中的TDDR和PSC位,由CPU时 TCR中的TDDR和 CPU时 钟定时,每来一个CPU时钟,PSC值减 CPU时钟 值减1 钟定时,每来一个CPU时钟,PSC值减1。 当PSC减至0、设备复位或定时器复位时,TDDR PSC减至 减至0 设备复位或定时器复位时, 的内容复制到PSC PSC中 的内容复制到PSC中。 4位预定标计数器PSC和16位定时计数器TIM组成 位预定标计数器PSC 16位定时计数器TIM组成 PSC和 位定时计数器TIM 一个20位计数器,定时器每接收一个CPU时钟减1, 20位计数器 CPU时钟减1,当 一个20位计数器,定时器每接收一个CPU时钟减1,当 计数器减到0 产生定时中断(TINT),同时PSC和 同时PSC 计数器减到0时,产生定时中断(TINT),同时PSC和 TIM重新装入预设的值 重新装入预设的值。 TIM重新装入预设的值。

第六章DSP片内外设

6.2.2 定时器的控制寄存器TCR

15 ~ 12 11 10 9~6 5 4 3~0

TCR 0026h

保留

Soft

Free

PSC

TRB

TSS

TDDR

保留位

软件调试控制位

预定标 计数器

重新 加载位

停止 状态位

分频 系数

① 保留位:总是读为0; ② 软件调试控制位:控制 调试断点时定时器的工作;

Soft 0 1

6.2 可编程定时器

6.2.1 定时器的结构及特点

• C5402内部有定时器0和定时器1两个定时器。结构一样. • 每个定时器有3个控制寄存器,都是存储器映像寄存器 TIM定时器寄存器:是减1计数器,可加载周期寄存器PRD的 值,并随计数减少。

PRD定时器周期寄存器:PRD中存放定时器的周期计数值,

定时器的中断周期

TCLK (TDDR 1) ( PRD 1)

定时器的工作过程

or 3 or 2

(3) 提供一些必须的特殊功能。如JTAG口、等待状态发生 器等。

片内外设分为两大类: 片内外设:串行接口、定时器、通用I/O引脚和标准主机接 口(HPI8)等。

增强型外设:多通道缓冲串口(McBSP)、主机接口(8位增强

HPI-8、16位增强HPI-16)、直接存储器访问(DMA)控 制器等。 控制寄存器:被映射到数据存储空间的第0页(地址20h~

1、复位PLLNDIV,选择DIV方式。 2、检测PLL状态,即读PLLSTATUS位,若该位为0,表明已经 切换到DIV方式。 3、根据要切换的倍频,选择PLLNDIV,PLLDIV,PLLMUL 的组合。 4、根据所需要的牵引时间,设置PLLCOUNT的当前值。 5、设定CLKMD寄存器。

DSP第6讲

22

第3章 C54x的硬件结构

3.8 流水线

DSP广泛采用能够减少指令执行时间的流水线操作,进一步 增强了处理器的处理能力 流水线操作是指各条指令以机器周期为单位,相差一个机器 周期而连续并行工作的情况 流水线操作的原理:将指令分成几个子操作,各子操作由不 同的操作阶段完成。这样每隔一个机器周期,每个操作阶段 就可以进入一条新指令。因此在同一个机器周期内,在不同 的操作阶段可以并行处理多条指令

9

第3章 C54x的硬件结构

第3章 C54x的硬件结构

3.7 中断

中断是由硬件驱动或软件驱动的信号

中断信号可以使 C54x 暂停正在执行的程序而转去执行中断服 务程序(ISP)

中断一般是由一些硬件设备产生的。当硬件设备需要送数据给 C54x 或者从 C54x 中取走数据 ( 如模 / 数转换器,数 / 模转换器或 其他处理器)时,这些硬件设备就向C54x发出中断请求信号

比较、选择和存储单元(CSSU)

COMP将A或B的高位 字与低位字进行比 较,并将结果分别送 入TRN的第0位和TC 中,并将其记录下来 以便程序调试 将比较结果输出到写 选择(MSW/LSW)选 择A或B中较大的16 位数,并将其通过总 线EB存入指定的数据 存储单元

比较、选择和存储单元

复习

中断向量地址由PMST中的中断向量指针IPTR(9位)和左移2 位后的中断向量序号(中断向量序号为0~31,左移2位后变成 7位)所组成

20

第3章 C54x的硬件结构

3.7 中断

3.7.4 重新映射中断向量地址

INT 0 的中断序号是16(10h),左移2位后为40h,若IPTR 例如,

=0001h(即中断向量表的起始地址为0080h),则

DSP知识点复习

22

TMS320C54x的指令系统符号和意义见P51-53

表3-1

DSP技术及应用

23

寻址方式

C54共有7种基本寻址方式

立即寻址

绝对寻址 累加器寻址

直接寻址

间接寻址 存储器映像寄存器寻址

堆栈寻址

DSP技术及应用

24

寻址方式

• 循环寻址的算法: If 0≤index+step〈BK; Index =index+step; Else if index+step ≥BK; Index =index+step-BK; Else if index+step〈0; Index =index+step+BK;

DSP技术及应用

25

寻址方式

循环寻址

使用循环寻址时,必须遵循以下三个原则:

① 循环缓冲区的长度 R<2N,且地址从一个低N位为0的地址开始; ② 步长小于或等于循环缓冲区的长度; ③ 所使用的辅助寄存器必须指向缓冲区单元。

DSP技术及应用

26

指令系统

TMS320C54X共有129条指令 按功能分为4大类(每大类又分为若干小类) :

DSP技术及应用

5

TMS320C54x硬件结构框图

TMS320C54x内部结构(3大块) (1)CPU:包括算术逻辑运算单元(ALU)、乘法器、 累加器、移位寄存器、各种专门用途的寄存器、地址生 成器及内部总线。 (2)存储器系统:包括片内程序ROM、片内单访问的 数据RAM和双访问的数据RAM、外接存储器接口。 (3)片内外设与专用硬件电路:包括片内定时器、 各种类型的串口、主机接口、片内锁相环(PLL)、时钟 发生器及各种控制电路。

DSP技术及其应用_第7讲_TMS320C54x DSP的片内外设(2)

BSP 框 图

BSP工作方式

• BSP可分别设置发送和接收部分的自动缓冲 功能。 • 当自动缓冲功能被禁止时(标准模式), 串口的数据传送由软件控制,与标准串口 一致。每当发送或接收一个字后,即产生 中断并作为发送中断(BXINT)和接收中断 (BRINT)被传送给CPU。 • 当自动缓冲功能被设置时,只有在缓冲区 的一半被传送时,才产生BXINT和BRINT并向 CPU传送

• 数据发送移位寄存器(XSR):

– 16位,不能被程序访问,控制从DXR向外的数据发送,并保 存向数据发送引脚(DX)发送的数据。

DRR和DXR的读写问题

• 对标准串口和缓冲串口,数据接收时串口 逻辑会自动写DRR。因此如果在DRR的数据 被读出来之前发生了串口接收操作,则前 面的内容会被覆盖。 • 如果DXR中的内容还没有被发送出去之前又 有数据写入,则前面的内容也会被覆盖, 造成数据丢失。

– 16位,存储器映射,存放从RSR来的串行数据,该数据要被 送上数据总线。

• 数据发送寄存器(DXR)

– 16位,存储器映射,存放来自数据总线的数据,该数据要发 往XSR。

• 串口控制寄存器(SPC):

– 16位,存储器映射,存放串口的模式控制位和状态位。

• 数据接收移位寄存器(RSR):

– 16位,不能被程序访问,存放从数据接收引脚(DR)来的数 据,并控制向DRR的数据传送。

McBSP寄存器

• 串口控制寄存器(SPCR)和引脚控制寄存器 (PCR)包含McBSP的状态信息位和配置位。 • 接收和发送控制寄存器(RCR和XCR)配置接收 和发送操作的各种参数。 • 多通道寄存器(MCR)、接收通道和发送通道 使能寄存器(RCER和XCER)用来进行多通道选 择。 • 采样率产生器寄存器(SRGR)控制帧和时钟信 号。

DSP控制器原理与应用张小鸣第六章片内外设1

位8:写1为CAP5/QEP4 ;写0为IOPF0 。 位7:写1为CAP4/QEP3 ;写0为IOPE7 。 位6:写1为PWM12 ;写0为IOPE6 。 位5:写1为PWM11;写0为IOPE5 。 位4:写1为PWM10 ; 写0为IOPE4 。 位3:写1为PWM9 ;写0为IOPE3 。 位2:写1为PWM8 ;写0为IOPE2 。 位1:写1为PWM7 ;写0为IOPE1。 位0:写1为CLKOUT ;写0为IOPE0 。

事件管理模块eva模块gp定时器timer1timer2t1pwmt1cmpt2pwmt2cmptimer3timer4t3pwmt3cmpt4pwmt4cmp比较单元compare1compare2compare3pwm12pwm34pwm56compare4compare5compare6pwm78pwm910pwm1112退出第四章tms320lf240x的片内外设事件管理模块eva模块捕获单元capture1capture2capture3cap1cap2cap3capture4capture5capture6cap4cap5cap6正交编码脉冲电路qepqep1qep2qep1qep2qep3qep4qep3qep4外部输入计数方向外部时钟tdiratclkina计数方向外部时钟tdirbtclkinb退出eva和evb的结构图见教材p261262引脚说明第四章tms320lf240x的片内外设1eva模块中的寄存器起始地址是7400h7400hgptcona定时器控制寄存器7401ht1cnt定时器1的计数寄存器定时器17402ht1cmpr定时器1的比较寄存器7403ht1pr定时器1的周期寄存器7404ht1con定时器1的控制寄存器7405ht2cnt定时器2的计数寄存器定时器27406ht2cmpr定时器2的比较寄存器7407ht2pr定时器2的周期寄存器7408ht2con定时器2的控制寄存器eva定时寄存器地址退出第四章tms320lf240x的片内外设eva比较控制寄存器地址7411hcomcona比较控制寄存器7413hactra比较方式控制寄存器7415hdbtcona死区时间控制寄存器7417hcmpr1比较寄存器17418hcmpr2比较寄存器27419hcmpr3比较寄存器3退出第四章tms320lf240x的片内外设eva捕获控制寄存器地址7420hcapcona捕获控制寄存器7422hcapfifoa捕获fifo状态寄存器a7423hcap1fifo两级深度的捕获fifo栈17424hcap2fifo两级深度的捕获fifo栈27425hcap3fifo两级深度的捕获fifo栈37427hcap1fbotfifo栈的栈底寄存器允许读最近捕获的值7428hcap2fbot7429hcap3fbot退出第四章tms320lf240x的片内外设eva中断寄存器地址742chevai

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

预定标模块包括TCR中的TDDR和PSC位,由 CPU时钟定时,每来一个CPU时钟,PSC值减1。

当PSC减至0、设备复位或定时器复位时, TDDR的内容复制到PSC中。

4位预定标计数器PSC和16位定时计数器TIM组 成一个20位计数器,定时器每接收一个CPU时钟减 1,当计数器减到0时,产生定时中断(TINT),同时 PSC和TIM重新装入预设的值。

加载初值:TDDR和PRD

DSP技术讲义,2007,陈军波©电子信息工程学院

例:设工作频率为40MHz的TMS320C5402,要求产 生40kHz的定时控制,则计数器的初始化程序如下: STM #10h,TCR ;停止计数器(TSS=1) STM #999, PRD ;设置PRD寄存器值为999

保留位 软件调试控制位

预定标 计数器

复位

停止/ 启动

初值

DSP技术讲义,2007,陈军波©电子信息工程学院

4. 定时器的初始化 定时器的基准工作脉冲由CLKOUT提供,每来

一个脉冲预定标计数器PSC减1,当PSC减至0时, 下一个脉冲到来,PSC产生借位。

借位信号分别控制定时计数器TIM减1和或门2 的输出,重新将TDDR的内容加载预定标计数器PSC ,从而完成定时工作的一个基本周期。 定时器的定时时间为:

设置定时器中断方法(假定INTM=1,关闭)如下: ● 将IFR中的TINT置1,以清除尚未处理完的定时器中断

; ● 将IMR中的TINT置1,启动定时器中断。 ● 将INTM置0,启动全部中断。

DSP技术讲义,2007,陈军波©电子信息工程学院

例子:

教材P167 中断程序中设置一个计数器(减法) 执行中断程序时定时器仍然在工作(同时) TSS:控制定时器的开始(TSS=0)和停止(TSS=1) TRB: 定时器复位信号 当计数器的值为0时,产生的借位脉冲自动给计数器

C54x的片内有2个定时器,是可编程的定时 器,主要用于产生周期性的中断。

定时器的最高分辨率为处理器的CPU时钟速 度。通过带4位预定标器的16位计数器,可以获 得较大范围的定时频率。

DSP片内计数器利用系统时钟CLKOUT作为计 数时钟,使用三个存储器映射寄存器(TIM, PRD, TCR)来控制计数。

DSP技术讲义,2007,陈军波©电子信息工程学院

6.3 串行口

4种串口

SP串口(标准同步串口) BSP串口(带缓冲的串口) TDM串口(时分复用串口) MCBSP串口(多通道带缓冲串口) TMS320C54x都提供了串行通信接口(SP),芯片型号 不同,配置的串口类型和数目都有所不同

DSP技术讲义,2007,陈军波©电子信息工程学院

▼SP串口(标准同步串口)

串口信号

1)时钟:CLKR,CLKX 2)帧同步信号:FSR,FSX 3)数据(发送和接受): DR,DX 4)中断信号(跟CPU接口):RINT,XINT

结构和特点(P169)

收发模块相互独立 由DRR、DSR、RSR、XSR以及控制电路组成 时钟信号可以选择内部或者外部 回返模式(用于测试) 2种工作方式:查询和中断

TINT中断频率为 Foutclk/(999+1)=40MHz/1000=40kHz

STM #20h,TCR ;重新装入TIM和PSC,然后

启动计数器(TSS=0,TRB=1)

DSP计数器的定时控制,不仅产生TOUT信 号,用来控制外围电路,同时也产生中断TINT 给CPU。CPU利用该中断,可以控制程序进程, 进行中断服务程序的处理。

,预定标模块每输出一个时钟,TIM减1。当TIM 减到0后,TIM装入PRD的值。

当设备复位(SRESET=0)或者定时器复位 (TRB=1)时,PRD的内容将装入TIM中。

主定时模块的定时中断(TINT)信号输出至CPU 以及定时器的输出引脚TOUT。

DSP技术讲义,2007,陈军波©电子信息工程学院

片内外设

定时器、串口、主机接口、通用IO等

访问方式

通过访问片内外设寄存器来实现控制

片内外设寄存器

寄存器种类及地址

CPU寄存器(教材P41),地址:0~1F(第0页) 片内外设寄存器(教材P163),地址:20~5F(第0页)

DSP技术讲义,2007,陈军波©电子信息工程学院

6.2 可编程定时器

第6章 DSP片内外设

DSP硬件系统设计

☆DSP片内外设 ☆DSP中断系统控制 ☆ DSP系统设计

DSP技术讲义,2007,陈军波©电子信息工程学院

第一部分 DSP片内外设 ➢可编程定时器 ➢串行通信接口 ➢ 主机接口 ➢ 通用I/O

DSP技术讲义,2007,陈军波©电子信息工程学院

6.1 DSP片内外设概述

DSP技术讲义,2007,陈军波©电子信息工程学院

1. 定时器的组成

1

初值 PRD

计数器 TIM 借位

1

初值 TDDR

预定标计数器 PSC 借位

1

SRESET

TRB

&

CLKOUT

TSS

主定时模块

预定标模块

1

DSP技术讲义,2007,陈军波©电子信息工程学院

TINT TOUT

2. 定时器工作原理 主定时模块包括PRD和TIM,由预定标模块定时

DSP技术讲义,2007,陈军波©电子信息工程学院

定时器的工作过程:

① 定时分频系数和周期数分别装入TCR和PRD寄存器中;

② 每来一个定时脉冲CLKOUT,计数器PSC减1; ③ 当PSC减至0时,PSC产生借位信号; ④ 在PSC的借位信号作用下,TIM减1计数,同时将分频

系数装入PSC,重新计数; ⑤ 当TIM减到0时,定时时间到,由借位产生定时中断

定时周期 = TCLK×(TTDDR+1)×(TPRD+1)

DSP技术讲义,2TCR的TSS位置1,关闭定时器,停止定时; ② 装载PRD值; ③ 重新装入TCR,初始化TDDR,设置TSS=0和TRB=1

,重装载定时器周期。启动定时器。

TINT和定时输出TOUT,并将PRD中的时间常数重 新装入TIM。

DSP技术讲义,2007,陈军波©电子信息工程学院

3. 定时控制寄存器TCR

16位存储器映像寄存器,包含定时器的控制位和状 态位。

TCR 0026h

15 ~ 12

保留

11

Soft

10

Free

9~6

PSC

5

TRB

4

TSS

3~0

TDDR