第6章DSP片内外设

dsp片内外设

第六章:片内外设 ——可编程定时器 初始化定时器:

(1) 将TCR中的TSS位置1,停止定时器。

(2。

(4) 重新启动定时器。TSS位为0,TRB位为l, 以重载定时器周期值, 使能定时器。

使能定时器中断(假定INTM=1): (1) 将IFR中的TINT位置1,清除尚未处理完(挂起)的定时器中断。 (2) 将IMR中的TINT位置l,使能定时器中断。 (3) 可以将ST1中的INTM位清0,使能全局中断。

控制扩展寄存器(BSPCE)控制,其各位的定义如表6-5所示。

第六章:片内外设 ——串行口 缓冲工作模式的操作过程

其功能主要由自动缓冲单元ABU来完成

• 自动缓冲单元(ABU)可独立于CPU自动完成控制串行口与固定 缓冲内存区中的数据交换。它包括

地址发送寄存器(AXR)

块长度发送寄存器(BKX) 地址接收寄存器(ARR) 块长度接收寄存器(BKR) 串行口控制寄存器(BSPCE) • 当发送或接收缓冲区的一半或全部满或空时,ABU才产生CPU 的中断,避免了CPU直接介入每一次传输带来的资源消耗。

• ABU利用独立于CPU的专用总线,让串行口直接读/写C54x内 部存储器。这样可以使串行口处理事务的开销最省,并能达到 较快的数据率。 • BSP有两种工作方式:非缓冲方式和自动缓冲方式。

• ABU具有自身的循环寻址寄存器组,每个都与地址产生单元 相关。发送和接收缓冲存储器位于一个指定的C54x DSP内部存 储器的2K字块中。该块可作为通用的存储器,但却是唯一的自 动缓冲能使用的存储块。

第六章:片内外设 ——可编程定时器 CounterSet .set 100 PERIOD .set 49999 .asg AR1,Counter ;定义计数次数 ;定义计数周期 ;AR1做计数指针,重 新命名以便识别 STM #CounterSet,Counter ;设计数器初值 STM #0000000000010000B,TCR ;停止计数器 STM #PERIOD,TIM ;给TIM设定初值49999 STM #PERIOD,PRD ;PRD与TIM一样 STM #0000011001101001B,TCR;开始定时器 STM #0008H,IMR ;开TIME0的中断 RSBX INTM ;开总中断 NOP B End

第5章DSP片内外设

模/数转换模块方框图

模/数转换模块方框图

为讲解方便,规定排序器的状态如下: 排序器SEQ1:CONV00-CON07 排序器SEQ2:CONV08-CON15 排序器SEQ: CONV00-CON15 转换触发特性: SEQ1:软件、EVA、外部引脚,仲裁优先级高于SEQ2 SEQ2:软件、EVB,仲裁优先级低于SEQ1 SEQ: 软件、EVA、EVB、外部引脚,无仲裁优先级 为每个排序所选的模拟输入通道排序控制寄存器 (CHSELSEQn)的CONVnn位所定义。 CONVnn位为4位长,可指定16通道中的任何一个。

5.2事件管理器模块EVA/EVB 5.2事件管理器模块 事件管理器模块EVA/EVB

• 通用定时器 GPT (General Purpose Timer) • 比较单元与PWM发生器 (Pulse Width Modulation) • 捕获单元Capture • 正交脉冲编码电路QEP (Quadrature Encoder Pulse ) 240x DSP 提供两个完全相同的事件管理器模块 EVA/EVB。而24x(240,243等)DSP有一个。事件管 理器中断分为三组(INT2, INT3, INT4),每组分配一 个中断。每组中断皆有多个中断源。

5.3.2.ADC模块的寄存器 表5-1 (ADC)模块的寄存器 地址 寄存器 70A0h ADCCTRL1 70A1h ADCCTRL2 70A2h MAXCONV 70A3h CHSELSEQ1 70A4h CHSELSEQ2 70A5h CHSELSEQ3 70A6h CHSELSEQ4 70A7h AUTO_SEQ_SR

事件管理器结构图

事件管理器: 事件管理器:通用定时器 GPT

通用定时器 GPT

DSP原理与应用 第三版

运算速度 以上。TMS320C6201执行1024点复数FFT运算时间只有66uS。

高度集成化

集滤波、A/D、D/A、ROM、RAM和DSP内核于一体的

运算精度和动态范围

模拟混合式DSP芯片已有较大的发展和应用。 DSP字长从8位已增到64位,累加器长度也增到40位,

开发工具

提高了运算精度。同时,采用超长字指令字(VLIW)结构和

2. TMS320C55x概况

目前C55x系列芯片主要有:

C5501/2(主频300MHz, McBSP,HPI接口), C5503/6/7/9A (主频200MHz, McBSP, HPI,

优点:成本低廉 缺点:性能差、

速度慢

DSP处理器

优点:速度高、大规模生产成本低; 缺点:开发成本高、通用性差。

针对数字信号处理的要求而设计,是数 字信号处理系统设计中采用的主流芯片。 优点:灵活、高速、便于嵌入式应用

7

1.2 DSP芯片简介

1.2.1 DSP芯片的发展历史、现状和趋势 1.2.2 DSP芯片的特点 1.2.3 DSP芯片的分类 1.2.4 DSP芯片的应用领域 1.2.5 选择DSP芯片考虑的因素

可同时进行取指令和多个数据存取操作,使CPU

在一个机器周期内可多次对程序空间和数据空

采用哈佛结构 间进行访问, 大大地提高了DSP的运行速度。

采用多总线结构

T1

T2

T3

T4

时钟

采用流水线结构

取指令

N

N+1

N+2

N+3

指令译码

N-1

N

N+1

N+2

配有专用的硬件乘法-累加器 取操作数 N-2

C54x DSP片内外设

Copyright © 2003 Texas Instruments. All rights reserved.

HPI接口框图

Copyright © 2003 Texas Instruments. All rights reserved.

主机接口(HPI)

HPI的外部接口为8位的总线,通过两个连续的8位字节组 合在一起形成一个16位字,HPI就可以为C54x DSP提供16位 的数。当主机使用HPI寄存器执行一个数据传输时, HPI控制 逻辑自动执行对一个专用2K字的HPI内部的双访问RAM的访 问,以完成数据处理。 C54x DSP然后可以在它的存储器空 间访问读写数据。HPI RAM也可以用作通用目标双访问数据 或程序RAM。 HPI具有两种工作模式: ☆ 共用访问模式(SAM)——此模式,主机和C54x DSP 都 能访问HPI存储器。异步的主机访问可以在HPI内部重新得到 同步。 ☆ 仅仅主机访问模式(HOM)——此模式,只有主机可以访 问HPI, C54x DSP 处于复位状态或者处于IDLE2空闲状态。

CLKMD各位 定义续

Copyright © 2003 Texas Instruments. All rights reserved.

PLL乘法系数

Copyright © 2003 Texas Instruments. All rights reserved.

主机接口(HPI)

C54x DSP 片内都有一个标准主机接口( HPI )。HPI 是一个8位并行口,用来与主设备或主处理器与C54x DSP 的 接口。信息在C54x DSP 和主机间通过C54x DSP 存储器进 行交换,主机和C54x DSP 均可以访问存储器。 主机是HPI的主控者, HPI作为一个外设与主机相连接, 使主机的访问操作很容易。主机通过以下单元与HPI通信: 专用地址和数据寄存器、 HPI控制寄存器以及使用外部数据 和接口控制信号。主机和C54x DSP 都可以访问HPI控制寄 存器。 下面给出HPI的接口框图:

《DSP片内外设》课件

DSP片内外设功能

时钟与定时器

功能:提供精确的时钟信号和定时功能 应用:用于控制DSP片内外设的运行和操作 特点:高精度、低功耗、可编程 工作模式:单次触发、循环触发、连续触发等

中断控制器

功能:处理来自片内外设的中断请求

结构:包括中断源、中断控制器、中断服务程序 工作原理:中断源产生中断请求,中断控制器接收并处理,最后由中断 服务程序执行 应用:广泛应用于实时控制系统、通信系统等领域

存储器类型:随机存取存储器(RAM)和只读存储器(ROM) 存储器大小:根据DSP芯片的型号和规格而定 存储器访问速度:直接影响DSP芯片的处理速度 存储器映射:将物理地址空间映射到逻辑地址空间,便于访问和操作

输入输出接口

输入接口:用于接收外部信号,是DSP与外部设备进行数据传输的通道 输出接口:用于将DSP处理后的信号输出到外部设备,实现控制或数据传 输功能 接口类型:并行接口、串行接口、GPIO接口等

DSP片内外设应用实例

数字音频处理应用实例

数字音频处理:将 模拟音频信号转换 为数字信号进行处 理

应用实例:音乐播 放器、语音识别系 统、音频处理软件 等

特点:高保真、低 延迟、高稳定性

技术实现:DSP片 内外设、音频编解 码算法、音频处理 算法等

图像处理应用实例

图像增强:提高图像质量,如对比度、亮度、色彩饱和度等 图像去噪:去除图像中的噪声,如高斯噪声、椒盐噪声等 图像分割:将图像中的不同区域分割开来,如边缘检测、阈值分割等 图像识别:识别图像中的物体或特征,如人脸识别、车牌识别等

接口特点:高速、稳定、灵活,可满足多种应用需求

总线结构

总线类型:数据总线、地址总 线、控制总线

数据总线:用于传输数据,如 指令、数据等

第6章 DSP系统初始化及中断..

DSP原理及应用-(修订版)--课后习题答案

第一章:1、数字信号处理的实现方法一般有哪几种?答:数字信号处理的实现是用硬件软件或软硬结合的方法来实现各种算法。

(1) 在通用的计算机上用软件实现;(2) 在通用计算机系统中加上专用的加速处理机实现;(3) 用通用的单片机实现,这种方法可用于一些不太复杂的数字信号处理,如数字控制;(4)用通用的可编程 DSP 芯片实现。

与单片机相比,DSP 芯片具有更加适合于数字信号处理的软件和硬件资源,可用于复杂的数字信号处理算法;(5) 用专用的 DSP 芯片实现。

在一些特殊的场合,要求的信号处理速度极高,用通用 DSP 芯片很难实现( 6)用基于通用 dsp 核的asic 芯片实现。

2、简单的叙述一下 dsp 芯片的发展概况?答:第一阶段, DSP 的雏形阶段( 1980 年前后)。

代表产品: S2811。

主要用途:军事或航空航天部门。

第二阶段, DSP 的成熟阶段( 1990 年前后)。

代表产品: TI 公司的 TMS320C20主要用途:通信、计算机领域。

第三阶段, DSP 的完善阶段( 2000 年以后)。

代表产品:TI 公司的 TMS320C54 主要用途:各个行业领域。

3、可编程 dsp 芯片有哪些特点?答: 1、采用哈佛结构( 1)冯。

诺依曼结构,( 2)哈佛结构( 3)改进型哈佛结构2、采用多总线结构 3.采用流水线技术4、配有专用的硬件乘法-累加器5、具有特殊的 dsp 指令6、快速的指令周期7、硬件配置强8、支持多处理器结构9、省电管理和低功耗4、什么是哈佛结构和冯。

诺依曼结构?它们有什么区别?答:哈佛结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯。

诺依曼结构:该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

DSP(知识点+思考题)

DSP复习要点第一章绪论1、数的定标:Qn表示。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示2、‟C54x小数的表示方法:采用2的补码小数;.word 32768 *707/10003、定点算术运算:乘法:解决冗余符号位的办法是在程序中设定状态寄存器STl中的FRCT位为1,让相乘的结果自动左移1位。

第二章CPU结构和存储器设置一、思考题:1、C54x DSP的总线结构有哪些特点?答:TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB):传送从程序存储器的指令代码和立即数。

(2)、三组数据总线(CB,DB和EB):连接各种元器件,(3)、四组地址总线(PAB,CAB,DAB和EAB)传送执行指令所需要的地址。

2、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

1)、累加器A和B分为三部分:保护位、高位字、地位字。

保护位保存多余高位,防止溢出。

2)、桶形移位寄存器:将输入数据进行0~31bits的左移(正值)和0~15bits的右移(负值)3)、乘法器/加法器单元:能够在一个周期内完成一次17*17bit的乘法和一次40位的加法4)、比较选择和存储单元:用维比特算法设计的进行加法/比较/选择运算。

5)、CPU状态和控制寄存器:状态寄存器ST0和ST1,由置位指令SSBX和复位指令RSBX控制、处理器模式状态寄存器PMST2-3、简述’C54x DSP的ST1,ST0,PMST的主要功能。

答:’C54x DSP的ST1,ST0,PMST的主要功能是用于设置和查看CPU的工作状态。

•ST0主要反映处理器的寻址要求和计算机的运行状态。

DSP片内外设及应用

中断标志寄存器IFR

当CPU接收到可屏蔽中断请求时,IFR相应的位置1,直 到中断得到处理为止.

图7-2

中断标志寄存器(IFR)结构图

接收中断请求

IFR的相应位置位 否 可屏蔽 中断 不可屏 蔽中断

否

中断可屏蔽? 是

图 、 中 断 操 作 流 程

INTM=0? 关闭所有可屏 是 开放所有可屏 IMR屏蔽位为1? 中断是否被屏蔽 否 是 中断被响应 IACK中断信号产生 是

5.链接命令文件 times.cmd如下:

MEMORY {PAGE 0: RAM1: origin =1000h ,length =500h PAGE 1: SPRAM1: origin=0060h,length=20h SPRAM2: origin=0100h,length=200h } SECTIONS { .text :>RAM1 PAGE 0 .data :>RAM1 PAGE 0 vars :>SPRAM1 PAGE 1 STACK :>SPRAM2 PAGE 1 }

将定时器设置为1ms,中断服务程序中计数期设置为1000, 则在计数1ms X 1000=1s 输出取反一次,得到一个周期为2S的方波

为将定时器设置为1ms,设定TDDR=9 ,则:

设置周期寄存器PRD:

t 1103 PRD 1 1639 9 T (1 TDDR ) 6110 (1 9)

(3)设置定时控制寄存器TCR: 15~12位设置为0000 11 位(soft)=0和10位(free)=1 9~6位预定标计数器PSC=TDDR=1001 5位定时器重新加载控制位,TRB=1 4位定时器停止控制位:TSS=0,定时器启动开始工作 3~0预标定分频系数:TDDR=1001H

DSP技术及其应用_第6讲_TMS320C54x DSP的片内外设

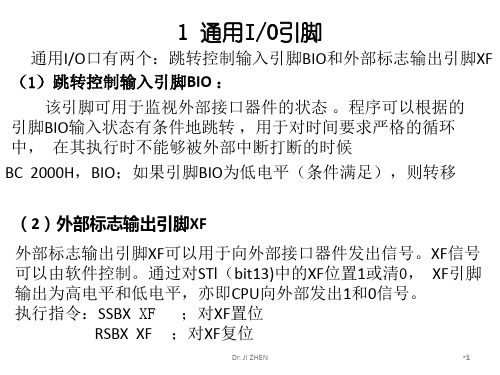

• XF(外部标志输出引脚):

– 软件控制,可以用来给外部器件发信号。通过对ST1中 的XF字段置位或清零来对XF引脚的输出电位进行控制。 – SSBX(状态寄存器置位)和RSBX (状态寄存器复位) 指令可以分别对XF进行置位和清零。

C54x系列DSP的片内外设

• • • • • • • • 通用IO引脚(BIO和XF) 时钟产生器 定时器 JTAG(IEEE1149.1) 外部总线接口 串口 主机接口HPI 直接存储器访问(DMA)控制器

C54x系列DSP的片内外设

• • • • • • • • 通用IO引脚(BIO和XF) 时钟产生器 定时器 JTAG(IEEE1149.1) 外部总线接口 主机接口(HPI) 串口 直接存储器访问(DMA)控制器

HPI

引 脚 图

HPI(Host Port Interface)

• 并行口,用来与一个主器件或主处理器连接。 • 通过C54x DSP片内既能被主机访问也能被 C54x访问的存储器,在主机和C54x DSP之间 交换信息。 • 主机接口的类型

– 共享访问 – 主机独享

• 主机独享模式下允许非同步主机访问

标准型主机接口

• 主机是接口的控制者。 • 主机通过标准型HPI可访问C54x DSP片内固定的2K RAM • 主机通过专用的地址、数据寄存器和HPI控制寄存器与 HPI通信,直接使用外部数据和控制信号进行控制, C54x DSP不能直接访问这些专用地址和数据寄存器,但 主机和C54x都能直接访问HPI控制寄存器。 • HPI将16位数据分成两个8位数据进行传递。 • 操作模式

时钟产生器

• 设计者可以通过时钟产生器选择时钟源。可驱 动时钟产生器的时钟源有:

– 一个带有内部振荡器电路的晶振。晶振电路跨接在 C54x DSP 的X1和X2/CLKIN 引脚之间。CLKMD 引脚 必须设置以启动内部振荡器。 – 一个外部时钟。外部时钟源直接连接到X2/CLKIN 引 脚, X1引脚悬空。

CH06 - DSP片内外设

第6章 DSP片内外设教学提示:TMS320C54x DSP的片内外设是集成在芯片内部的外部设备。

本章将以C5402 DSP为主详细介绍其可编程定时器、串行口、主机接口、通用I/O以及软件等待状态发生器和分区转换逻辑。

教学要求:掌握可编程定时器、标准同步串行口、标准8位主机接口、通用I/O的特点和操作过程,能够应用。

了解多通道缓冲串口(McBSP)、8位增强主机接口HPI-8、软件等待状态发生器和分区转换逻辑。

6.1 DSP片内外设概述TMS320C54x DSP的片内外设是集成在芯片内部的外部设备。

CPU核对片内外设的访问是通过对相应的控制寄存器的访问来完成的。

外部设备集成在芯片内部主要有以下优点:(1) 片内外设访问速度快。

因为片外外设必须通过与程序、数据总线共用的外部总线来访问,访问速度慢,而片内外设的访问或操作速度大大快于外部I/O空间中的片外外设。

(2) 可以简化电路板的设计。

如将A/D转换、D/A转换、定时器集成在片内。

(3) 提供一些必须的特殊功能。

这些特殊功能必须以片内外设的方式来实现,如JTAG 口、等待状态发生器等。

TI公司将相关的片内外设分为两大类:片内外设和增强型片内外设。

其中片内外设主要包括串行接口、定时器、通用I/O引脚和标准主机接口(HPI8)。

增强型外设主要包括多通道缓冲串口(McBSP)、主机接口(8位增强HPI-8、16位增强HPI-16)、DMA控制器。

所有的C54x DSP的CPU结构及功能完全相同,但是片内的外设配置多少不同。

任何一款C54x DSP拥有的片内外设都只是以上列举的片内外设的一部分。

片内外设的操作是通过相关的控制寄存器来实现的,寄存器被映射到数据存储空间的第0页(地址20h~5Fh)。

具体的映射关系如表6-1所示。

表6-1 C5402外设存储器映像寄存器地址(十六进制) 名称描述McBSP0数据接收寄存器220 DRR20McBSP0数据接收寄存器121 DRR10McBSP0数据发送寄存器222 DXR20McBSP0数据发送寄存器123 DXR10定时器0寄存器24 TIM定时器0周期计数器25 PRDDSP技术及应用·164·续表地址(十六进制) 名称描述定时器0控制寄存器26 TCR27 ―保留软件等待状态寄存器28 SWWSR块切换控制寄存器29 BSCR2A ―保留软件等待状态控制寄存器2B SWCRHPI控制寄存器2C HPIC2D~2F ―保留定时器1寄存器30 TIM1定时器1周期计数器31 PRD1定时器1控制寄存器32 TCR133~37 ―保留McBSP0 串口子块地址寄存器38 SPSA0McBSP0 串口子块数据寄存器39 SPSD03A~3B ―保留通用I/O引脚控制寄存器3C GPIOCR通用I/O引脚状态寄存器3D GPIOSR3E~3F ―保留McBSP1数据接收寄存器240 DRR21McBSP1数据接收寄存器141 DRR11McBSP1数据发送寄存器242 DXR21McBSP1数据发送寄存器143 DXR1144~47 ―保留McBSP1串口子地址寄存器48 SPSA1McBSP1串口子数据寄存器49 SPSD14A~53 ―保留DMA通道容许与优先控制寄存器54 DMPRECDMA子块地址寄存器55 DMSA带子块地址递增的DMA数据寄存器56 DMSDIDMA子地址寄存器57 DMSDN时钟模式寄存器58 CLKMD59~5F ―保留·164·第6章 DSP片内外设·165·6.2 可编程定时器C5402有两个片内定时器,主要用来产生周期性的中断。

DSP原理及应用TMS320C54x片内外设及应用实例

应用领域拓展

随着数字信号处理技术的不断发展,DSP的应用领 域也在不断拓展,需要不断探索新的应用场景和市 场需求。

人才培养和生态系统建设

为了推动DSP技术的发展和应用,需要加强 人才培养和生态系统建设,建立完善的开发 环境和工具链。

06

参考文献

参考文献

1

[1] 张雄伟, 杨吉斌. 数字信号处理——原理、算 法与实现[M]. 北京: 清华大学出版社, 2011.

应用场景

在音频处理、信号测量、控制系统 等领域广泛应用。

存储器和I/O引脚

存储器和I/O引脚功能

01

TMS320C54x芯片具有外部存储器和多个I/O引脚,用于扩展外

部存储空间和连接外设。

工作原理

02

通过读写外部存储器实现数据存储,I/O引脚用于输入输出电平

信号。

应用场景

03

在数据存储、外设控制、信号采集等方面具有广泛应用。

FFT在TMS320C54x上的实现

TMS320C54x的硬件结构支持FFT运算,其乘法器和累加器运算单元可以高效地完成 FFT计算。在实现FFT时,需要注意数据的位序和存储方式。

FFT应用实例

通过FFT算法,可以分析语音、图像、雷达等信号的频谱成分,从而实现信号的频域分 析、滤波、调制解调等功能。

TMS320C54x的优势与局限性

• 丰富的外设接口:TMS320C54x系列DSP具有多种外设接口, 如串行通信接口、并行输入输出接口等,方便与外部设备进行 数据交换。

TMS320C54x的优势与局限性

价格较高

由于TMS320C54x系列DSP采用高性能的制程技术和复杂的内 部结构,导致其价格较高,增加了应用成本。

DSP在片外围电路PPT演示文稿

• HPI数据锁存器(HPID,只能由主机访问)

– 主机读写数据的缓存

• HPI控制寄存器(地址:002Ch) • HPI控制逻辑(HPIC)

– 处理HPI与主机之间的接口信号

•3

5 TRB - 定 时 器 重 新 加 载 位 ,用 来 复 位 片 内 定 时 器 。当 TRB 置 1 时 ,

以 PRD 中 的 数 加 载 TIM , 以 及 以 TD D R 中 的 值 加 载 PSC。

TRB 总 是 读 成 0

4 TSS

0 定 时 器 停 止 状 态 位 , 用 于 停 止 或 启 动 定 时 器 。复 位 时 , TSS

0 到断点时定时器的工作状态。

Free soft

定时器状态

0

0 定时器立即停止工作

0

1 当计数器减到 0时停止工作

1 × 定时器继续运行

9~6 PSC - 定 时 器 预 先 定 标 计 数 器 。 这 是 一 个 减 1 计 数 器 , 当 PSC 减

到 0 后 。 TD D R 位 域 中 的 数 加 载 到 PSC, TIM 减 1

(2)TRC定时器控制寄存器各位含义

15-12

11

保留

soft

10

9-6

5

4

3-0

free

PSC

TRB

TSS TDDR

预定标 定时器重 定时器停 定时器分 新加载1 止状态1 频系数

•9

定时器控制寄存器(TCR)的功能

位 15~12

11 soft 10 Free

DSP课设PWM

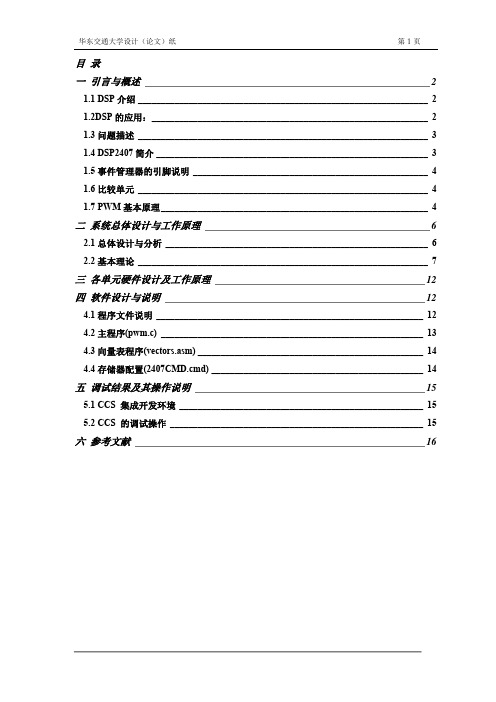

目录一引言与概述_________________________________________________________ 2 1.1 DSP介绍 _______________________________________________________________ 2 1.2DSP的应用:____________________________________________________________ 2 1.3问题描述_______________________________________________________________ 3 1.4 DSP2407简介 ___________________________________________________________ 3 1.5事件管理器的引脚说明___________________________________________________ 4 1.6比较单元_______________________________________________________________ 4 1.7 PWM基本原理__________________________________________________________ 4二系统总体设计与工作原理_____________________________________________ 6 2.1总体设计与分析_________________________________________________________ 6 2.2基本理论_______________________________________________________________ 7三各单元硬件设计及工作原理__________________________________________ 12四软件设计与说明____________________________________________________ 12 4.1程序文件说明__________________________________________________________ 12 4.2主程序(pwm.c) _________________________________________________________ 13 4.3向量表程序(vectors.asm) _________________________________________________ 14 4.4存储器配置(2407CMD.cmd) ______________________________________________ 14五调试结果及其操作说明______________________________________________ 15 5.1 CCS 集成开发环境_____________________________________________________ 15 5.2 CCS 的调试操作_______________________________________________________ 15六参考文献__________________________________________________________ 16一引言与概述1.1 DSP介绍数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

第六章DSP片内外设

6.2.2 定时器的控制寄存器TCR

15 ~ 12 11 10 9~6 5 4 3~0

TCR 0026h

保留

Soft

Free

PSC

TRB

TSS

TDDR

保留位

软件调试控制位

预定标 计数器

重新 加载位

停止 状态位

分频 系数

① 保留位:总是读为0; ② 软件调试控制位:控制 调试断点时定时器的工作;

Soft 0 1

6.2 可编程定时器

6.2.1 定时器的结构及特点

• C5402内部有定时器0和定时器1两个定时器。结构一样. • 每个定时器有3个控制寄存器,都是存储器映像寄存器 TIM定时器寄存器:是减1计数器,可加载周期寄存器PRD的 值,并随计数减少。

PRD定时器周期寄存器:PRD中存放定时器的周期计数值,

定时器的中断周期

TCLK (TDDR 1) ( PRD 1)

定时器的工作过程

or 3 or 2

(3) 提供一些必须的特殊功能。如JTAG口、等待状态发生 器等。

片内外设分为两大类: 片内外设:串行接口、定时器、通用I/O引脚和标准主机接 口(HPI8)等。

增强型外设:多通道缓冲串口(McBSP)、主机接口(8位增强

HPI-8、16位增强HPI-16)、直接存储器访问(DMA)控 制器等。 控制寄存器:被映射到数据存储空间的第0页(地址20h~

1、复位PLLNDIV,选择DIV方式。 2、检测PLL状态,即读PLLSTATUS位,若该位为0,表明已经 切换到DIV方式。 3、根据要切换的倍频,选择PLLNDIV,PLLDIV,PLLMUL 的组合。 4、根据所需要的牵引时间,设置PLLCOUNT的当前值。 5、设定CLKMD寄存器。

第六章DSP片内外设

6.2 可编程定时器

6.2.1 定时器的结构及特点 • C5402内部有定时器0和定时器1两个定时器。结构一样. • 每个定时器有3个控制寄存器,都是存储器映像寄存器 TIM定时器寄存器:是减1计数器,可加载周期寄存器PRD的 值,并随计数减少。 PRD定时器周期寄存器:PRD中存放定时器的周期计数值, 提供TIM重载用。 TCR定时器控制寄存器:TCR包含定时器的控制和状态位, 控制定时器的工作过程。

CounterSet .set 100-1

;定义计数次数

PERIOD

.set 49999

;定义计数周期

.asg AR1,Counter

;AR1做计数指针,重新命名以便识别

STM #CounterSet,Counter ;设计数器初值

STM #0000000000010000B,TCR ;停止计数器

TOUT

④ 借位信号使得TIM减1,同时TDDR再次装载PSC,重新计数;

定时器的工作过程

or 3

0025H

周期寄存器 PRD

0024H

定时寄存器 TIM(16位)

借位

or 2

预定标分频系数 TDDR

预定标计数器 PSC(4位) 借位

or

SRESET

1

TRB

0026H

&

CLKOUT TSS

TINT 1

控制寄存器:被映射到数据存储空间的第0页(地址20h~ 5Fh)。表6-1-p163,164。

6.1 时钟发生器

C5402内部有一个时钟发生器,可为C5402提供时钟,包 括内部振荡器和锁相环电路PLL两部分。

•时钟信号的产生的两种方式:

一是使用外部时钟源的时钟信号,将外部时钟信号 直接加到DSP芯片的X2/CLKIN引脚,而X1引脚悬空。

DSP知识点复习

22

TMS320C54x的指令系统符号和意义见P51-53

表3-1

DSP技术及应用

23

寻址方式

C54共有7种基本寻址方式

立即寻址

绝对寻址 累加器寻址

直接寻址

间接寻址 存储器映像寄存器寻址

堆栈寻址

DSP技术及应用

24

寻址方式

• 循环寻址的算法: If 0≤index+step〈BK; Index =index+step; Else if index+step ≥BK; Index =index+step-BK; Else if index+step〈0; Index =index+step+BK;

DSP技术及应用

25

寻址方式

循环寻址

使用循环寻址时,必须遵循以下三个原则:

① 循环缓冲区的长度 R<2N,且地址从一个低N位为0的地址开始; ② 步长小于或等于循环缓冲区的长度; ③ 所使用的辅助寄存器必须指向缓冲区单元。

DSP技术及应用

26

指令系统

TMS320C54X共有129条指令 按功能分为4大类(每大类又分为若干小类) :

DSP技术及应用

5

TMS320C54x硬件结构框图

TMS320C54x内部结构(3大块) (1)CPU:包括算术逻辑运算单元(ALU)、乘法器、 累加器、移位寄存器、各种专门用途的寄存器、地址生 成器及内部总线。 (2)存储器系统:包括片内程序ROM、片内单访问的 数据RAM和双访问的数据RAM、外接存储器接口。 (3)片内外设与专用硬件电路:包括片内定时器、 各种类型的串口、主机接口、片内锁相环(PLL)、时钟 发生器及各种控制电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

结构和特点(P169)

DSP技术讲义,2007,陈军波©电子信息工程学院

工作过程(教材P171)

缓冲寄存器 移位寄存器 串并转换 CPU的读写 工作方式:2种

DSP技术讲义,2007,陈军波©电子信息工程学院

例:设工作频率为40MHz的TMS320C5402,要求 产生40kHz的定时控制,则计数器的初始化程序如 下: STM #10h,TCR ;停止计数器(TSS=1) STM #999, PRD ;设置PRD寄存器值为999

TINT中断频率为 Foutclk/(999+1)=40MHz/1000=40kHz ;重新装入TIM和PSC,然后 启动计数器(TSS=0,TRB=1)

DSP技术讲义,2007,陈军波©电子信息工程学院

1. BSP结构

TMS320C54x内存界面 16 11 自动缓冲单元ABU 控制 XRDY RRDY BXINT BMINT BRINT

BCLKX BFSX

BDXR

BSPCE BXINT TMS320C54x CPU界面

BDX BDR

BXSR BRSR

2) 地址寄存器自动增加,直至缓冲区的底部,然后 地址寄存器内容恢复到缓冲存储区顶部。

3)

DSP技术讲义,2007,陈军波©电子信息工程学院

▼TDM串口

时分复用串口

将时间分为相等的间隔,每个间隔表示一个通道 也可配置为标准工作模式 了解(P176)

教学要求:

DSP技术讲义,2007,陈军波©电子信息工程学院

DSP技术讲义,2007,陈军波©电子信息工程学院

3. 定时控制寄存器TCR

16位存储器映像寄存器,包含定时器的控制位和状 态位。

15 ~ 12 11 10 9~6 5 4 3~0

TCR 0026h

保留

Soft

Free

PSC

TRB

TSS

TDDR

保留位

软件调试控制位

预定标 计数器

复位

停止/ 启动

初值

中断到 CPU DMA DSP技术讲义, 2007,陈军波©同步事件到 电子信息工程学院

(1) 外部引脚 DX: 串行数据发送引脚; DR: 串行数据接收引脚; CLKX: 发送时钟引脚; CLKR: 接收时钟引脚; FSX: 发送帧同步引脚; FSR: 接收帧同步引脚; CLKS: 外部提供的采样时钟引脚。 McBSP通过DX和DR引脚与外部设备进行数据 通信,时钟和帧同步等控制信息的传输通过CLKX 、CLKR、FSX和FSR引脚来实现。

DSP技术讲义,2007,陈军波©电子信息工程学院

预定标模块包括TCR中的TDDR和PSC位,由 CPU时钟定时,每来一个CPU时钟,PSC值减1。 当PSC减至0、设备复位或定时器复位时, TDDR的内容复制到PSC中。

4位预定标计数器PSC和16位定时计数器TIM组 成一个20位计数器,定时器每接收一个CPU时钟减 1,当计数器减到0时,产生定时中断(TINT),同时 PSC和TIM重新装入预设的值。

DSP技术讲义,2007,陈军波©电子信息工程学院

定时器初始化步骤如下:

① TCR的TSS位置1,关闭定时器,停止定时;

② 装载PRD值; ③ 重新装入TCR,初始化TDDR,设置TSS=0和TRB=1

,重装载定时器周期。启动定时器。

设置定时器中断方法(假定INTM=1,关闭)如下: ● 将IFR中的TINT置1,以清除尚未处理完的定时器中 断; ● 将IMR中的TINT置1,启动定时器中断。 ● 将INTM置0,启动全部中断。

1)非缓冲方式 2)自动缓冲方式

DSP技术讲义,2007,陈军波©电子信息工程学院

非缓冲方式:

串口工作和标准SP相同,不使用缓冲区;

自动缓冲方式:

不需每传送一个字就发一次中断,而是每通过一次缓冲器的 半边界,才产生中断至CPU,从而减少频繁中断对CPU的影响。 发送和接受缓冲最大的长度为2K,对C542而言,这2K的缓冲 区在0800h~0FFFh之间。缓冲区的长度和起始地址是用户可 编程的,但必须遵守一定的规范。

TMS320C54x都提供了串行通信接口(SP),芯片型号 不同,配置的串口类型和数目都有所不同

DSP技术讲义,2007,陈军波©电子信息工程学院

▼SP串口(标准同步串口)

串口信号

1)时钟:CLKR,CLKX 2)帧同步信号:FSR,FSX 3)数据(发送和接受): DR,DX 4)中断信号(跟CPU接口):RINT,XINT

第6章 DSP片内外设

DSP硬件系统设计

☆DSP片内外设 ☆DSP中断系统控制 ☆ DSP系统设计

DSP技术讲义,2007,陈军波©电子信息工程学院

第一部分 DSP片内外设

可编程定时器

串行通信接口

主机接口

通用I/O

DSP技术讲义,2007,陈军波©电子信息工程学院

6.1 DSP片内外设概述

DSP技术讲义,2007,陈军波©电子信息工程学院

定时器的工作过程:

① 定时分频系数和周期数分别装入TCR和PRD寄存器中; ② 每来一个定时脉冲CLKOUT,计数器PSC减1;

③ 当PSC减至0时,PSC产生借位信号;

④ 在PSC的借位信号作用下,TIM减1计数,同时将分频 系数装入PSC,重新计数; ⑤ 当 TIM 减到 0 时,定时时间到,由借位产生定时中断 TINT和定时输出TOUT,并将PRD中的时间常数重 新装入TIM。

片内外设

定时器、串口、主机接口、通用IO等 通过访问片内外设寄存器来实现控制

访问方式

片内外设寄存器

寄存器种类及地址

CPU寄存器(教材P41),地址:0~1F(第0页) 片内外设寄存器(教材P163),地址:20~5F(第0页)

DSP技术讲义,2007,陈军波©电子信息工程学院

6.2 可编程定时器

缓冲区使用方式: 循环寻址

DSP技术讲义,2007,陈军波©电子信息工程学院

以VC542为例,与BSP串口有关的存储器映射寄存器共有6个。

地址 0x22 0x23 0x38 0x39 0x3A 0x3B

寄存器符号 BSPC BSPCE AXR BKX ARR BKR

功能 16位串口控制寄存器 16位串口扩展控制寄存器 11位发送缓冲区地址寄存器 11位发送缓冲区大小寄存器 11位接收缓冲区地址寄存器 11位接收缓冲区大小寄存器

BNMINT 串口控 制逻辑 中断 控制 BRINT 中断 逻辑

BCLKR BFSR

BDRR

BSPC

DSP技术讲义,2007,陈军波©电子信息工程学院

2. 控制寄存器BSPC(P170)

BSPC用于控制串行口的操作。

15 BSPCH Free 仿真 控制 13 12 11 10 9 RSRFUL XSREMPT Soft XRDY RRDY IN1 L Y 仿真 接收移位 发送移位 发送 接收 发送 控制 寄存器 寄存器 准备 准备 时钟 满 空 好 好 状态 14 8 IN0 接收 时钟 状态

15~10 BSPCE ABU控制 9 8 7 6 5 4~0

PCM

FIG

FE

CLKP

FSP

CLKDV

ABU 控制位

脉冲编码 帧同步信 扩展 时钟极性 帧同步极 发送时钟 模式位 号选择位 格式位 设置位 性设置位 分频因数

DSP技术讲义,2007,陈军波©电子信息工程学院

BSP自动缓冲过程

1) ABU完成对缓冲存储器的存取;

7

BSPCL RRST 接收 复位

6

XRST 发送 复位

5

TXM 发送 模式

4

MCM 时钟 选择模式

3

FSM 帧 同步 模式

2

FO 数据 格式

1

DLB 数据 回送 模式

0

Res 保留

DSP技术讲义,2007,陈军波©电子信息工程学院

2. BSP的控制寄存器BSPCE

BSPCE寄存器包含控制位和状态位,用于控制 BSP和ABU的增强功能。寄存器的低10位用于增强 特性控制,高6位用于ABU控制。

STM #20h,TCR

DSP计数器的定时控制,不仅产生TOUT信 号,用来控制外围电路,同时也产生中断TINT 给CPU。CPU利用该中断,可以控制程序进程, 进行中断服务程序的处理。 DSP技术讲义,2007,陈军波©电子信息工程学院

6.3 串行口

4种串口

SP串口(标准同步串口) BSP串口(带缓冲的串口) TDM串口(时分复用串口) MCBSP串口(多通道带缓冲串口)

DSP技术讲义,2007,陈军波©电子信息工程学院

4. 定时器的初始化

定时器的基准工作脉冲由CLKOUT提供,每来 一个脉冲预定标计数器PSC减1,当PSC减至0时, 下一个脉冲到来,PSC产生借位。

借位信号分别控制定时计数器TIM减1和或门2 的输出,重新将TDDR的内容加载预定标计数器PSC ,从而完成定时工作的一个基本周期。 定时器的定时时间为: 定时周期 = TCLK×(TTDDR+1)×(TPRD+1)

送,同时允许程控串口通信的时钟频率。

DSP技术讲义,2007,陈军波©电子信息工程学院

何为缓冲串口? 所谓缓冲串口,实际上是在标准串口的基础上增加了

一个2K的自动缓冲单元,叫ABU。每次串口发送数据时,硬 件自动将发送缓冲中的数据送出;在接收数据时,硬件自 动将收到的数据写入接收缓存。 缓冲串口的工作方式: