数字逻辑4-4 显示译码器

数字逻辑复习题

一、填空题:1、由二值变量所构成的因果关系称为逻辑关系。

能够反映和处理逻辑关系的数学工具称为逻辑代数。

2、在正逻辑的约定下,“1”表示高电平,“0”表示低电平。

3、数字电路中,输入信号和输出信号之间的关系是逻辑关系,所以数字电路也称为逻辑电路。

在逻辑关系中,最基本的关系是与逻辑、或逻辑和非逻辑。

4、用来表示各种计数制数码个数的数称为基数,同一数码在不同数位所代表的权不同。

十进制计数各位的基数是10,位权是10的幂。

5、8421 BCD码和2421码是有权码;余3码和格雷码是无权码。

6、进位计数制是表示数值大小的各种方法的统称。

一般都是按照进位方式来实现计数的,简称为数制。

任意进制数转换为十进制数时,均采用按位权展开求和的方法。

7、十进制整数转换成二进制时采用除2取余法;十进制小数转换成二进制时采用乘2取整法。

8、十进制数转换为八进制和十六进制时,应先转换成二进制,然后再根据转换的二进数,按照三个数码一组转换成八进制;按四个数码一组转换成十六进制。

9、逻辑代数的基本定律有交换律、结合律、分配律、反演律和非非律。

10、最简与或表达式是指在表达式中与项中的变量最少,且或项也最少。

13、卡诺图是将代表最小项的小方格按相邻原则排列而构成的方块图。

卡诺图的画图规则:任意两个几何位置相邻的最小项之间,只允许一位变量的取值不同。

14、在化简的过程中,约束项可以根据需要看作1或0。

15、数字逻辑中的有与, 或, 非基本逻辑运算。

16、逻辑函数有四种表示方法,它们分别是真值表、逻辑图、逻辑表达式和卡诺图。

二、判断正误题2、异或函数与同或函数在逻辑上互为反函数。

(对)3、8421BCD码、2421BCD码和余3码都属于有权码。

(错)4、二进制计数中各位的基是2,不同数位的权是2的幂。

(对)3、每个最小项都是各变量相“与”构成的,即n个变量的最小项含有n个因子。

(对)4、因为逻辑表达式A+B+AB=A+B成立,所以AB=0成立。

练习4-四位BCD译码器

1.4 4位BCD译码器的设计4位BCD译码器可将BCD码转换成数字显示码,有4个输入引脚和7个输出引脚。

4位BCD译码器可分为共阴与共阳两种,下面以设计共阳4位BCD译码器为例来说明其设计方法。

1.实验原理共阳4位BCD译码器有4个输入端用来输入BCD码,7个输出端分别对应到七段显示4位BCD译码器应具备的脚位:输入端:D3、D2、D1、D0:输出端:S6、S5、S4、S3、S2、Sl、S0。

2.原理图输入由于原理图输入法较复杂,所以在这里不再详述。

3.文本输入(1)建立新文件:选取窗口菜单File—New,出现对话框,选Text Editor file选项,单击OK按钮,进入文本编辑画面。

(2)保存:选取窗口菜单File—save,出现对话框,键入文件名sevenBcD.vhd,单击OK按钮。

(3)指定项目名称,要求与文件名相同:选取窗口菜单File—Project—Name,键入文件名sevenBCD,单击OK按钮。

或也可以通过如下操作把当前设计项目设置成工程文件:选择菜单File|Project|Set Project to Current File命令,即将当前设计文件设置成Project。

选择此项后可以看到标题栏显示出所设文件的路径。

(4)选择实际编程器件型号:选取窗口菜单Assign—Device,出现对话框,选择ACEXlK 系列的EPlK30TCl44一3。

(5)输入VHDL源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sevenBCD ISPORT(D:IN STD_LOGIC_VECTOR(3 DOWNTO 0);S :OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END sevenBCD;ARCHITECTURE a OF sevenBCD ISBEGINPROCESS (D)BEGINCASE D ISWHEN 0000=>S<=“0000001”;一0WHEN 0001l=>S<=“1001111”;一1WHEN 0010=>S<=“0010010”;一2WHEN 0011=>S<=“0000110”;—3WHEN 0100=>S<:“1001100”;一4WHEN 0101=>S<=“0100lOO”;—5WHEN 0110=>S<=“0100000”;—6WHEN 0111=>S<=“0001111”;一7WHEN 1000=>S<=“0000000”;一8WHEN 1001=>S<=“0000100”;一9WHEN OTHERS=>S<=“111111l”;END CASE;END PROCESS;END a;(6)保存并查错:选取窗口菜单File—Project—Save&Check,即可针对电路文件进行检查。

2020—2021学年非毕业班集成电路设计与集成系统专业《数字逻辑电路》期末考试题及答案(试卷A)

院系: 专业班级: 学号: 姓名: 座位号:XXX 大学2020—2021学年非毕业班集成电路设计与集成系统专业《数字逻辑电路》期末考试题及答案(试卷A )题 号 一 二 三 四 五 总分 评卷人 分 值 20 20 10 20 30 100得 分得 分一、 选择题;(每小题2分,共20分)。

1、将幅值上、时间上离散的阶梯电平统一归并到最邻近的指定电平的过程称为( )。

A 、采样;B 、量化;C 、保持;D 、编码;2、8个输入端的编码器按二进制数编码时,输出端的个数是教研室主任审核(签名): 教学主任(签名):课程代码: 适用班级:命题教师:任课教师:院系: 专业班级: 学号: 姓名: 座位号:( )。

A 、2个;B 、3个;C 、4个;D 、8个;3、下列电路中,不属于组合逻辑电路的是( )。

A 、译码器;B 、全加器;C 、寄存器;D 、编码器;4、CMOS 数字集成电路与TTL 数字集成电路相比突出的优点是( )。

A 、微功耗;B 、高速度;C 、高抗干扰能力;D 、电源范围宽;5、指出下列各式中哪个是四变量A 、B 、C 、D 的最大项( )。

A 、ABC ;B 、A+B+C+D ;C 、D ABC ; D 、B AC ;6、同步时序电路和异步时序电路比较,其差异在于后者( )。

院系: 专业班级: 学号: 姓名: 座位号:A 、没有触发器;B 、没有统一的时钟脉冲控制;C 、没有稳定状态;D 、输出只与内部状态有关;7、两片74LS290芯片扩展而成的计数器,最大模数是( )。

A 、80;B 、20;C 、54;D 、100;8、由与非门组成的基本RS 触发器不允许输入的变量组合S 、R 为( )。

A 、1==S R ; B 、10==S R 、; C 、01==S R 、;D 、==S R ;9、逻辑函数的表示方法中具有唯一性的是( )。

A 、真值表;B 、表达式;C 、表达式;D 、卡诺图;10、将TTL 与非门作非门使用,则多余输入端应做的处理是( )。

ch4组合逻辑电路(4.4-4.5)详解

功能表

E

Y0 输 入

输出

E A1 A0 Y0 Y1 Y2 Y3 Y1 H × × H H H H

A0

L L LLHHH

Y2L H L H H L H

L HHHHH L

Y 0 EA1 A0

Y 1 EA1 A0

Y 2 EA1 A0

Y 3 EA1 A0

19

2、 典型译码器电路及应用

EI2

1

I7 I6 I5 I4 I3 I2 I1 I0

EO2

EI CD4532(II) EO

GS

Y2 Y1 Y0 0

I7 I6 I5 I4 I3 I2 I1 I0 EI1 EI CD4532(I) EO

GS

Y2 Y1 Y0

EO1

0

GS2

GS1

≥1 G3

1

GS

L3 1

≥1 G2

0 L2 1

≥1 G1

0 L1 1

3

4)编码器的分类:普通编码器和优先编码器。

普通编码器:任何时候只允许输入一个有效编码信号,否则 输出就会发生混乱。

优先编码器:允许同时输入两个以上的有效编码信号。当同 时输入几个有效编码信号时,优先编码器能按预先设定的优 先级别,只对其中优先权最高的一个进行编码。

4

1、编码器的工作原理 普通二进制编码器

EI2

I7 I6 I5 I4 I3 I2 I1 I0 EO2

EI CD4532(II) EO

I7 I6 I5 I4 I3 I2 I1 I0 EI1 EI CD4532(I) EO

EO1

0 GS

Y2 Y1 Y0

0

GS

Y2 Y1 Y0 0

GS2

数字逻辑实验二

数字逻辑实验⼆实验⼆数据选择器、译码器、全加器实验⼀、实验⽬的1.熟悉数据选择器的逻辑功能。

2.熟悉译码器的⼯作原理和使⽤⽅法。

3.设计应⽤译码器的电路,进⼀步加深对它的理解。

4.掌握全加器的实现⽅法。

5.学习⽤中规模集成电路的设计⽅法。

⼆、实验所⽤器件和仪表1.双4选1数据选择器74LS153 1⽚2.双2-4线译码器74LS139 2⽚3.⼆输⼊四与⾮门74LS00 1⽚4.⼆输⼊四异或门74LS86 1⽚5.万⽤表6.⽰波器7.实验箱三、实验内容1.测试74LS153中⼀个4选1数据选择器的逻辑功能。

2.测试74LS139中⼀个2-4译码器的逻辑功能。

3.⽤2-4线译码器74LS139和与⾮门74LS00实现逻辑函数。

4.⽤两⽚2-4线译码器74LS139设计⼀个8通道的数据分配器。

5.⽤数据选择器74LS153设计⼀个全加器。

四、实验接线图1.74LS153实验接线图和74LS153真值表(每个芯⽚的电源和地端要连接)4个数据输⼊引脚C0─C3分别接实验台上的10MHz、1MHz、500KHz、100KHz脉冲源。

变化地址选择引脚A、B和使能引脚G的电平,产⽣不同的组合。

观测并记录每种组合下数据选择器的输出波形。

Output输出送到⽰波器上的红⾊线端,⽰波器上的⿊⾊线端接地。

观察⽰波器上输出波形和右下⽅频率的数值。

K1、K2和K3是实验箱上3个不同的开关。

图4.1 74LS153实验接线图表4.1 74LS153真值表2.74LS139实验接线图和74LS139真值表图4.2 74LS139实验接线图表4.2 74LS139真值表4个译码输出引脚Y0─Y3接电平指⽰灯。

改变引脚G、B、A的电平,产⽣8种组合。

观测并记录指⽰灯的显⽰状态。

=+。

输⼊来源于开关,输出送到LED 3.⽤74LS139和74LS00实现逻辑函数F AB AB灯上,观察在不同的输⼊时,灯的亮灭情况)4.⽤两⽚74LS139设计⼀个8通道的数据分配器(输⼊来源于开关,输出送到LED灯A图4.4 74LS139实现数据分配器的接线图5.⽤数据选择器74LS153设计⼀个全加器(输⼊来源于开关,输出送到LED灯上,观察在不同的输⼊时LED 灯的亮灭情况)。

习题册答案-《数字逻辑电路(第四版)》-A05-3096

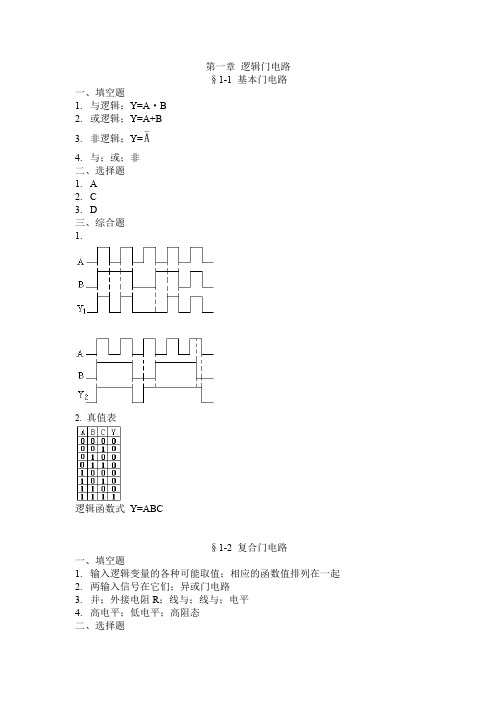

第一章逻辑门电路§1-1 基本门电路一、填空题1.与逻辑;Y=A·B2.或逻辑;Y=A+B3.非逻辑;Y=4.与;或;非二、选择题1. A2. C3. D三、综合题1.2.真值表逻辑函数式Y=ABC§1-2 复合门电路一、填空题1.输入逻辑变量的各种可能取值;相应的函数值排列在一起2.两输入信号在它们;异或门电路3.并;外接电阻R;线与;线与;电平4.高电平;低电平;高阻态二、选择题1. C2. B3. C4. D5. B三、综合题1.2.真值表逻辑表达式Y1=ABY2=Y3==A+B 逻辑符号3.第二章组合逻辑电路§2-1 组合逻辑电路的分析和设计一、填空题1.代数;卡诺图2.n;n;原变量;反变量;一;一3.与或式;1;04.组合逻辑电路;组合电路;时序逻辑电路;时序电路5.该时刻的输入信号;先前的状态二、选择题1. D2. C3. C4. A5. A三、判断题1. ×2. √3. √4. √5. ×6. √四、综合题1.略2.(1)Y=A+B(2)Y=A B+A B(3) Y=ABC+A+B+C+D=A+B+C+D3. (1) Y=A B C+A B C+ A B C + ABC=A C+AC(2) Y=A CD+A B D+AB D+AC D(3) Y=C+A B+ A B4. (a)逻辑函数式Y= Y=AB+A B真值表逻辑功能:相同出1,不同出0 (b)逻辑函数式Y=AB+BC+AC真值表逻辑功能:三人表决器5.状态表逻辑功能:相同出1,不同出0逻辑图1. 6.Y=A ABC+B ABC+C ABC判不一致电路,输入不同,输出为1,;输入相同,输出为0。

§2-2 加法器一、填空题1.加数与被加数;低位产生的进位2.加数与被加数;低位产生的进位3.加法运算二、选择题1. A2. C三、综合题1.略2.略3.§2-3 编码器与比较器一、填空题1. 编码2. 101011;010000113. 十;二;八;十六4. 0;1;逢二进一;10;逢十进一5. 二进制编码器;二—十进制编码器6. 两个数大小或相等7. 高位二、选择题1. A2. B3. C4. B三、综合题1.略2.(1)10111;00100011(2)00011001;19(3)583. (1)三位二进制(2)1,1,0(3)1,1,14.§2-4 译码器与显示器一、填空题1. 编码器;特定含意的二进制代码按其原意;输出信号;电位;解码器2. 二进制译码器;二—十进制译码器;显示译码器3. LED数字显示器;液晶显示器;荧光数码管显示器4. 1.5~3;10mA/段左右5. 共阴极显示译码器;共阳极显示译码器;液晶显示译码器二、选择题1. A;D2. A三、判断题1.√2.×3.×4.√5.√四、综合题七段显示译码器真值表f=D C B A +D C B A +D C B A+D CB A +D C B A +D C B A =D+B A +C A +C B =DB AC AC B§2-5 数据选择器与分配器一、填空题1.多路调制器;一只单刀多掷选择开关;地址输入;数字信息;输出端2.从四路数据中,选择一路进行传输的数据选择器3.地址选择;输出端二、选择题1. D2. A;C三、判断题1. √2. ×四、综合题1.略2. Y=A B D0+A BD1+A B D2+ABD3第三章触发器§3-1 基本RS触发器与同步RS触发器一、填空题1.两个;已转换的稳定状态2.R S+RSQ n;R+S=13. R S Q n+ R S;RS=04.置0;置15.相同;低电平;高电平6.时钟信号CP7.D触发器8.空翻二、选择题1.D2.B3.A4.B5.B6.D三、判断题1. ×2. ×3. √4. ×5. ×6. ×四、综合题1.略2.3.4.5.略§3-2主从触发器与边沿触发器一、填空题1.空翻2.置0、置1、保持、翻转3.D、J Q n+K Q n4.保持、置1、清0、翻转5.电平、主从6.一次变化7.边沿触发器8.不同、做成9.置0、置1、时钟脉冲二、选择题1.A2.A3.D4.B5.A6.C7.D8.B9.A10.D三、判断题1. √2. ×3. ×4. ×5. √6. ×7. √8. √四、综合题1.2.3.4.略5.略6.§3-3触发器的分类与转换一、填空题1.T、T'2. T Q n+ T Q n、Q n3.1、04. Q n、Q n5. 16. T'7. T8. T'二、选择题1.D2.D3.D4.B5.B三、判断题1. ×2. ×3. ×4. ×四、分析解答题1.2.3.略4.略5.略第四章时序逻辑电路§4-1 寄存器一、填空题1.输入信号;锁存信号2.接收;暂存;传递;数码;移位二、选择题1. C2. B;A三、判断题1. √2. ×3. √四、综合题1.JK触发器构成D触发器,即Q n+1= D。

电工电子技术:44 显示译码器

共阳极:

ab c d e f g

“0”亮,“1”不亮

各段加反向电压导通,发光; 各段加正向电压截止,不发光

七段显示译码表

(共阴极接法)

A3 A2 A1 A0 a b c d e f g 0000 111111 0 0 0001 0110000 1 0010 1101101 2 0 0 1 1 1 1 1 1 0 01 3 0100 0110011 4 0 1 0 1 0 1 1 1 0 11 5 0110 1011111 6 0111 1110010 7 1000 1111111 8 1 0 0 1 1 1 11 0 1 1 9

a

f gb

e

c

d

显示译码器: CT7449的管脚图

14 Ucc f g a b c d 七段输出

CT7449

编码信号输入

1 A1 A2 BI A3 A0

消隐控制端

e GND

功能表(简表)

输入

输出

A0A3 8421码

XXXX

BI

ag

显示

1

译码 显示字型

0 0000000

消隐

完整的功能表请参考相应的参考书

电工电子技术

显示译码器

显示译码器

在数字系统中,常常需要将运算结果用人们习惯的十 进制显示出来,这就要用到显示译码器。

二-十进 制编码

显示的是七段显示器件

f

a gb

e

c

d

接法:

共阴极:

“1”亮,“0”不亮

ab c d e f g

各段加正向电压导通,发光; 各段加反向电压截止,不发光

CT7449与七段显示

A3 A2

数字电路——4译码器设计

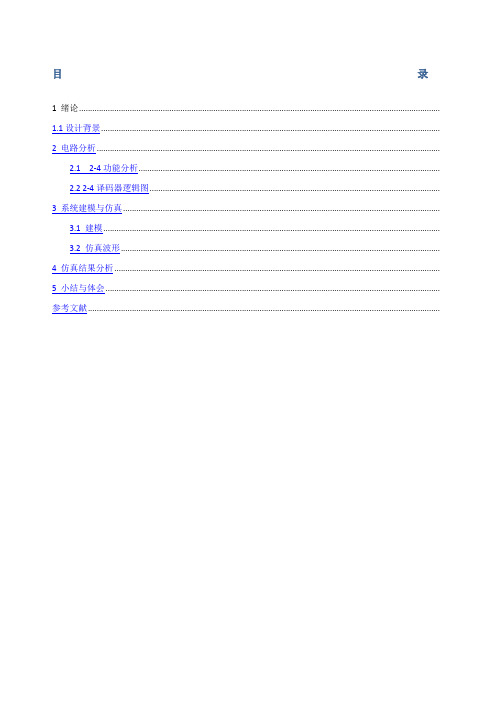

目录1 绪论....................................................................................................................................................................1.1设计背景..........................................................................................................................................................2 电路分析 ............................................................................................................................................................2.1 2-4功能分析.........................................................................................................................................2.2 2-4译码器逻辑图....................................................................................................................................3 系统建模与仿真 ................................................................................................................................................3.1 建模.........................................................................................................................................................3.2 仿真波形 .................................................................................................................................................4 仿真结果分析 ....................................................................................................................................................5 小结与体会 ........................................................................................................................................................ 参考文献 ................................................................................................................................................................1 绪论1.1设计背景在数字系统中,经常需要将一中代码转换为另一种代码,以满足特定的需求,完成这种功能的电路称为码转化电路。

李国龙-数字逻辑-编码器译码器

HUNAN UNIVERSITY 数字逻辑学生姓名李国龙学生学号201408010211专业班级计算机科学与技术2015年12月 12日实验二 编码器、译码器电路仿真实验一、实验内容:(1)利用两块8—3线优先编码器74LS148D 设计16—4线优先编码电路,然后仿真验证16—4线优先编码的逻辑功能。

(2)利用两块3—8线译码器74LS138D 设计4—16线优先编码电路,然后仿真验证4—16线译码的逻辑功能。

二、实验目的:(1) 掌握编码器、译码器的工作原理; (2) 常见编码器、译码器的应用; (3) 掌握优先编码电路的设计方法。

三、实验原理:所谓编码是指在选定的一系列二进制数数码中,赋予每个二进制数码以某一固定含义。

例如,用二进制数码表示十六进制数叫做二—十六进制编码。

能完成编码功能的电路统称为编码器。

74LS148D 是常用额8线—3线优先编码器。

在8个输入线上可以同时出现几个有效输入信号,但只对其中优先权最高的一个有效输入信号进行编码。

其中7端优先权最高,0端优先权最低,其他端的优先权按端脚号的递减顺序排列。

~E1为选通输入端,低电平有效,只有~E1=0时,编码器正常工作,而在~E1=1时,所以的输出端均被封锁。

E0为选通输出端,GS 为优先标志端。

该编码器输入、输出均为低电平有效。

译码器是编码的逆过程,将输入的每个二进制代码赋予的含义“翻译”过来,给出相应的输出信号。

能够完成译码功能的电路焦作译码器。

74LS138D 属于3线—8线译码器。

该译码器输入高电平有效,输出低电平有效。

U174LS148DA 09A 17A 26G S14D 313D 41D 52D 212D 111D 010D 74D 63E I 5E O 15U274LS138DY 015Y 114Y 213Y 312Y 411Y 510Y 69Y 77A1B 2C 3G 16~G 2A 4~G 2B 5图2-1编码器74LS148D 图2-2译码器74LS138D 8位信号输入端7端优先权最高 三个使能端 三路输入端 0端优先权最低8—3线优先编码器:切换9个单刀双掷开关(J0—J8)进行仿真实验,将结果填入表2.1中。

《数字逻辑设计》第7章 数据选择器及译码器

P1

P2

P9

P3

P8

Gnd P4

P7 P6

P5

扩展

W=(P8•P9)’ Y=(P2•P3•P6•P7)’

X=(P4•P5•P6•P7)’ Z=(P1•P3•P5•P7•P9)’

X

Y

Z

&

&

&

&

1. 二进制编码器——例:4线-2线编码器

Example

4:2编码器

计算机配有四个外部设备:声卡(A0),硬盘驱动器 (A1),鼠标(A2),网卡(A3),B0、B1为编码输出。

g

CD

AB 00 01 11 10 00 1 1 0 0 01 0 0 1 0 11 × × × × 10 0 0 × ×

g=A+CD+BC+BC

编码器(Encoders)

编码器——

♦ 特点:多输入、多输出的组合逻辑电路 ♦ 功能:将二进制码按照一定规律编排,使其具有特定含义

(如:8421BCD码用1000 代表数字8),与译码器互逆。

0 1 0 0 0 1 1 001 1 4

0 1 0 1 1 0 1 101 1 5

0 1 1 0 1 0 1 111 1 6

0 1 1 1 1 1 1 000 0 7

1 0 0 0 1 1 1 111 1 8

1 0 0 1 1 1 1 101 1 9

七段数码管

f g COM a b

a

f

b

g

e

c

d

e d COM c

A1

A0

典型应用——实现常规逻辑函数

A

D0

D1

D2

数字逻辑课件——译码器

图3-3-10 4线-7线译码器/驱动 器7448逻辑符号

28

用7448驱动BS201A的基本接法如图3-3-11(a)所 示。当B3B2B1B0 输入0000~1111这16种不同信 号时,相应的显示字形如图3-3-11(b)所示。

图3-3-11 7448驱动BS201A

29

接线时务必防止将+5V直接与a~g段输入短接,否则 会烧毁PN结,用7448的输出Ya~Yg驱动BS201A的段输 入则没有这种危险,这是因为Ya~Yg为集电极开路输

19

常用的半导体数码管、液晶显示器及其BCD – 七段显示 译码器。 4. 半导体数码管 半导体数码管是分段式半导体显示器件,其基本结构为 PN结,一些特殊半导体材料作成的PN结具有这样的性质: 当外加正向偏压时,P区的多数载流子空穴流向N区,N区 的多数载流子电子流向P区,而少数载流子注入PN结与多 数载流子复合,在这个过程中会发出一定波长的光束。

e

c

d

27

配合半导体数码管BS201A工作的4线 — 7线译码 器/驱动器7448 (1)7448的逻辑功能

7448的逻辑符号如图3-3-10所示,其功能如表3-3-7,

它的基本输入信号是 四位二进制数(也可 以是8421BCD码)A3, A2,A1,A0,

基本输出端有7个: Ya,Yb,Yc,Yd,Ye, Yf,Yg。

出结构,并已有上拉电阻2kΩ。

在7448中,除了上述基本输入端和基本输出端 外,还有几个辅助输入、输出端:

(1)灯测试输入(LT ); (2)灭零输入(RBI ); (3)灭灯输入/灭零输出 (BI / RBO) : 这个端钮 比较特殊,它既可作输入用,也可作输出用。

30

4线-7线译码器/驱动器7448功能表

数字逻辑实验报告

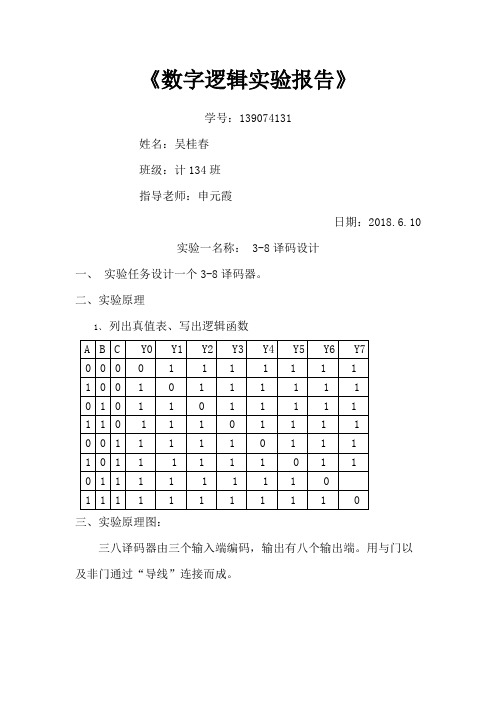

《数字逻辑实验报告》学号:139074131姓名:吴桂春班级:计134班指导老师:申元霞日期:2018.6.10实验一名称: 3-8译码设计一、实验任务设计一个3-8译码器。

二、实验原理1、列出真值表、写出逻辑函数三、实验原理图:三八译码器由三个输入端编码,输出有八个输出端。

用与门以及非门通过“导线”连接而成。

四、实验步骤:1)打开软件max+plus2,建立新目标文件开始画图。

并保存原图,设置工程指向。

2)选择芯片类型本实验选择EPF10K10LC84-3芯片3)编译配置4)时序仿真:由仿真结果可以看出,本实验仿真成功。

五、实验结果六、实验分析1、结合本次实验,简述原理图输入法设计组合电路的步骤。

设计输入原理图→电路的编译与适配→电路仿真与时序分析→管脚的重新分配与定位→器件的下载编程与硬件实现2、时序仿真波形中,输出波形与输入波形是否同步变化?如何解释输出波形中存在的毛刺?不完全同步变化,存在延迟。

3、连线时,线条不能连接到器件内部,否则会出现编译错误。

同时,添加激励脉冲时a,b,c分别为2倍的关系。

加错激励信号结果也将不正确。

b5E2RGbCAP实验二名称:全加全减器设计一、实验任务设计并实现一个一位全加全减器。

二、实验原理图1.列出真值表、写出逻辑函数。

a,b,c为三个输入端,分别输入0或者1,m为控制端当m=1是全减器,m=0时是全加器,输出端s表示结果,y代表进位或借位。

p1EanqFDPw三、实验步骤:1)打开软件max+plus2,建立新目标文件开始画图。

并保存原图,设置工程指向。

2)选择芯片类型本实验选择EPF10K10LC84-3芯片3)编译配置4)时序仿真:由仿真结果可以看出,全加全减器仿真成功。

实验三名称:七段显示译码器一、实验任务设计并实现一个七段显示译码器。

二、实验原理图1. 列出真值表、写出逻辑函数8421BCD输入代码数字A3A2A1A0a b c d e f g 000000000010 000110011111 001000100102 001100001103 010********* 010*********011011000006011100011117 100000000008 1001000010092、数字显示是由0—9共有十个数字所以有四个输入端,输出端分别编码为a—g,每一个字母代表一个笔画。

数字逻辑实验报告(2-4地址译码器)

成绩:实验报告课程名称:数字逻辑实验实验项目:2-4地址译码器的原理及实现姓名:专业:计算机科学与技术班级:计算机14-8班学号:计算机科学与技术学院实验教学中心2015年12月15日实验项目名称: 2-4地址译码器的原理及实现一、实验要求设计实现一个2-4地址译码器,掌握使用方法。

二、实验目的掌握2-4地址译码器的设计方法和原理。

三、实验内容2-4地址译码器功能分析:2-4地址译码器有2个输入端,4个输出端和一个使能端。

在使能端为高电平时,对应输入,其中只有一个输出为有效电平,其余为相反电平,输出电平可以是低电平有效,也可以是高电平有效。

具体来说,2输入变量 X1,X2共有4种不同的状态组合,所以2-4地址译码器有四个输出信号Y0-Y3。

此处2-4地址译码器输出为低电平有效,其真值表如下:由真值表可写出各输出端逻辑表达式:由以上4式可以画出逻辑电路图,如下:四、实验步骤建立一个新的文件夹打开Quartus Ⅱ后,新建工程,输入工程名。

选择仿真器件,器件选择FLEX10K ,芯片选择EPF10K10TC144-4 。

新建“Block Diagram/Schematic File ”文件画逻辑图并编译。

2132********X X E Y X X E Y X X E Y X X E Y ++=++=++=++=新建“Vector Waveform File”波形文件,设置好输入的波形,保存文件并分析仿真波形。

选择“Assignments”->“Pins”,绑定管脚并编译。

选择“Tools”->“Programmer”点击“Start”下载到芯片并进行逻辑验证。

五、实验设备LP-2900逻辑设计实验平台,计算机,QuartusⅡ六、实验结果E端输入波形周期为100微秒X1端输入波形周期为50微秒X2端输入波形周期为25微秒仿真波形如下:经过验证,仿真波形符合设计要求。

数字电子技术04译码器ppt课件

74HC42

Y7 Y8

Y3 Y4

Y5

D

Y9

Y6

Y7 Y8

Y9

;.

15

(2)功能分析

功能表

输入为无效码时,输出均为高电平, 无有效码输出

BCD输入

输出

A3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9 00000111111111

00011011111111

00101101111111

EN

I2 I3

EN

2线—4线译码器组 成4线--16线译码器

;.

5

2、集成电路译码器 (1)二进制译码器 常用的有CMOS(74HC138)和TTL(74LS138),可用74X138表示。

①74X139介绍: 74X139是双2线-4线译码器

E

E

Y0

Y0

Y1

Y1

A0

A0

Y2

Y2

A1

A1

Y3

Y3

1/2 74X139逻辑符号

例4.4.3 四片74HC138和一片74HC139构成5线32线译码器。

解:

首先列出5线-32线译码器的真值表,如表4.4.7所示。

;.

10

B4B3从00~11 共4种组合

对B4B3的一种组合 B2B1B0从000~111

;.

11

例4.4.3的逻辑图

对输入的任一组5位 码,只有一个输出端 为有效低电平。

由于译码器是低电平有效输出,所 以将最小项变换(双非)为反函数 的形式,得到:

CBA

L= m0 ·m2 ·m6 ·m7

= Y0 ·Y2 ·Y6 ·Y7

Y0

4 2-4译码器

时序逻辑电路类型

• 输出状态不光与当时的输入状态有关, 还与之前的输出状态有关。 • 有组合逻辑部分和记忆部分组成。

设计2-4译码器

• • • •

A0 A1 Q3 Q2 1 、根据设计要求写出真值表 A1 q2 0 0 0 0 2、写出逻辑关系式 0 1 0 0 q1 2-4 A0 1 0 0 1 3、化简 q0 1 1 1 0 4、画出逻辑图

设计24译码器q0q1q2q3a1a0a1a0q2q1q0q324原理图vhdl文本编辑综合fpgacpld适配fpgacpld编程下载fpgacpld器件和电路系统时序与功能门级仿真1功能仿真2时序仿真逻辑综合器结构综合器1isp方式下载2jtag方式下载3针对sram结构的配置4otp器件编程功能仿真22eda应用fpgacpld的eda开发流程

第二课

• 1、数字电路的设计方法 • 2、EDA设计流程介绍

• 3、MAX+plus的图形编辑方法

2.1数字电路的设计方法

• 组合逻辑电路的认识 • 时序逻辑电路的认识

以下电路中,哪个是组合逻辑,哪个是时序逻辑 1、2-4译码器 5、10进制计数器 2、8-3编码器 6、存储A1 A0 q2 A1 A0 q1 A1 A0 q3 A1 A0

q3

Q1 Q0 0 1 0 0 1 0 0 0

2.2 EDA设计流程

应用FPGA/CPLD的EDA开发流程: 原理图/VHDL文本编辑

综合

FPGA/CPLD

器件和电路系统

1、isp方式下载 2、JTAG方式下载 3、针对SRAM结构的配置 4、OTP器件编程

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4.3.3

译码器

显示译码器

2015-1-10

1

复习

如何用74LS138译码器实现如下逻辑函数?

F ( A, B, C) m(1,2,7)

2015-1-10

2ห้องสมุดไป่ตู้

4.3.3 显示译码器

在数字测量仪表和各种数字系统中,都需

要将数字量直观地显示出来,一方面供人们直接

读取测量和运算的结果,另一方面用于监视数字

系统的工作情况。

数字显示电路是数字设备不可缺少的部分。

数字显示电路通常由显示译码器、驱动器和显示

器等部分组成,如图4-12所示。

2015-1-10 3

图4-12 数字显示电路的组成方框图

1. 数字显示器件

数字显示器件是用来显示数字、文字或者符

号的器件,常见的有辉光数码管、荧光数码管、

液晶显示器、发光二极管数码管、场致发光数字

共阴型LED数码管的实用电路。

2015-1-10

图4-17 74LS49驱动LED数码管电路

12

作业题

4.16

2015-1-10

13

图4-16 74LS49的逻辑符号

2015-1-10

灭灯 控制端

9

表4-8 74LS49的功能表

8421BCD码

禁止码

灭灯状态

2015-1-10 10

译码输入端:D、C、B、A,为8421BCD码; 七段代码输出端:abcdefg,某段输出为高电

平时该段点亮,用以驱动高电平有效的七段显示 LED数码管;

灭灯控制端:IB , 当IB = 1时,译码器处于正常译码工作状态; 若IB = 0,不管D、C、B、A输入什么信号,译 码器各输出端均为低电平,处于灭灯状态。 利用IB信号,可以控制数码管按照要求处于显 示或者灭灯状态,如闪烁、熄灭首尾部多余的0等。

2015-1-10 11

图4-17是一个用七段显示译码器74LS49驱动

板、等离子体显示板等等。本书主要讨论发光二

极管数码管。

2015-1-10 4

(1)发光二极管(LED)及其驱动方式 LED具有许多优点,它不仅有工作电压低

(1.5~3V)、体积小、寿命长、可靠性高等优点,而

且响应速度快(≤100ns)、亮度比较高。

一般LED的工作电流选在5~10mA,但不允许

超过最大值(通常为50mA)。 LED可以直接由门电路驱动。

2015-1-10

5

a)是输出为低电平时,LED发光,称 R图( 为限流电阻 为低电平驱动; 图(b)是输出为高电平时, LED发光,称 5V VD 5V 2V R 为高电平驱动; 10mA I F 采用高电平驱动方式的 TTL门最好选用OC门。

2015-1-10

图4-13 门电路驱动LED (a) 低电平驱动 (b) 高电平驱动

LED数码管通常采用图4-15所示的七段字形

显示方式来表示0-9十个数字。

图4-15 七段数码管字形显示方式

2015-1-10

8

(2)七段显示译码器 七段显示器译码器把输入的BCD码,翻译成 驱动七段LED数码管各对应段所需的电平。 74LS49是一种七段显示译码器。 七段 代码

8421 BCD 码

6

(2) LED数码管

LED数码管又称为半导体数码管,它是由多 个LED按分段式封装制成的。LED数码管有两种 形式:共阴型和共阳型。

高电平驱动

低电平驱动

公共阴极

2015-1-10

公共阳极

7

图4-14 七段显示LED数码管 (a) 外形图 (b) 共阴型 (c) 共阳型

2.七段显示译码器

(1)七段字形显示方式