7段显示译码器

7段数码显示译码器设计

7段数码显示译码器设计

设计一个7段数码显示译码器,主要功能是将4位二进制编码转换为用7段LED显示的十进制数。

具体设计过程如下:

1.确定电路的输入和输出:输入为4位二进制编码,输出为7段LED 显示的十进制数。

2.确定译码器类型:由于需要将二进制编码转换为十进制数,可以选用BCD-7段译码器或者十进制译码器作为基本器件。

3.确定电路原理图:根据所选的译码器类型,画出电路原理图。

在原理图中,需要连接一个4位二进制编码器到译码器的输入端,同时将译码器的输出连接到7段LED显示器的相应段。

4.电路连接和布线:将译码器和7段LED显示器连接到电源和接地线上,并将4位二进制编码器的输出连接到译码器的输入端。

5.电源和接地线:将电源和接地线正确连接到电路中,确保电路能够正确工作。

6.电路调试和测试:通过输入不同的4位二进制编码来测试电路的译码功能,确保译码器能够正确地将二进制编码转换为十进制数,并且在7段LED显示器上显示。

7.电路性能优化和改进:根据测试结果,对电路进行进一步的优化和改进。

可以考虑是否需要增加输入的保护电路,或者改进电源和接地线的布线方式来提高电路的性能。

总结:

以上是设计一个7段数码显示译码器的基本步骤,通过选择合适的译码器类型,正确连接电路和调试测试,可以实现4位二进制编码到十进制数的转换,并在7段LED显示器上显示。

在设计过程中,需要注意电路连接的正确性和稳定性,以及对电路的性能进行优化和改进。

实验3 七段字形显示译码器实验

实验三七段字形显示译码器实验一、 实验目的1.了解LED数码管的显示原理及其使用;2.熟悉七段字形显示译码器(74LS48)的外特性及使用;3.学会查集成电路手册。

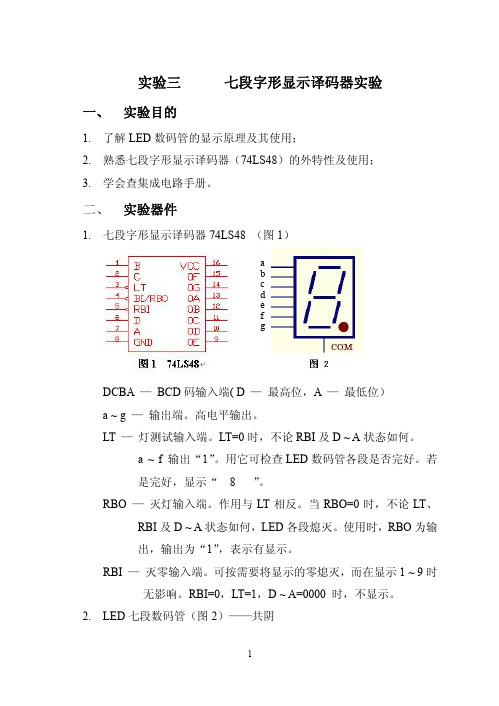

二、 实验器件1.七段字形显示译码器74LS48 (图1)abcdefgDCBA — BCD码输入端( D —最高位,A —最低位)a ~ g —输出端。

高电平输出。

LT —灯测试输入端。

LT=0时,不论RBI及D ~ A状态如何。

a ~ f 输出“1”。

用它可检查LED数码管各段是否完好。

若是完好,显示“8 ”。

RBO —灭灯输入端。

作用与LT相反。

当RBO=0时,不论LT、RBI及D ~ A状态如何,LED各段熄灭。

使用时,RBO为输出,输出为“1”,表示有显示。

RBI —灭零输入端。

可按需要将显示的零熄灭,而在显示1 ~ 9时无影响。

RBI=0,LT=1,D ~ A=0000 时,不显示。

2.LED七段数码管(图2)——共阴74LS48功能表LT RBI D C B A RBO a b c d e f g1 1 0 0 0 0 1 1 1 1 1 1 1 01 X 0 0 0 1 1 0 1 1 0 0 0 01 X 0 0 1 0 1 1 1 0 1 1 0 11 X 0 0 1 1 1 1 1 1 1 0 0 11 X 0 1 0 0 1 0 1 1 0 0 1 11 X 0 1 0 1 1 1 0 1 1 0 1 11 X 0 1 1 0 1 0 0 1 1 1 1 11 X 0 1 1 1 1 1 1 1 0 0 0 01 X 1 0 0 0 1 1 1 1 1 1 1 11 X 1 0 0 1 1 1 1 1 0 0 1 11 X 1 0 1 0 1 0 0 0 1 1 0 11 X 1 0 1 1 1 0 0 1 1 0 0 11 X 1 1 0 0 1 0 1 0 0 0 1 11 X 1 1 0 1 1 1 0 0 1 0 1 11 X 1 1 1 0 1 0 0 0 1 1 1 11 X 1 1 1 1 1 0 0 0 0 0 0 0X X X X X X 0* 0 0 0 0 0 0 01 0* 0 0 0 00 0 0 0 0 0 0 00 X X X X X 1 1 1 1 1 1 1 1三、 实验内容1.设计实验电路。

简述七段显示译码指令seg的用法

一、引言在计算机系统中,七段显示译码器是一种常用的数字显示设备,通过此设备可以实现数字的显示。

而在使用七段显示译码器时,我们通常需要使用相应的指令来进行控制和操作。

其中,seg指令就是一种常见的用于七段显示译码的指令,本文将就seg指令的用法进行简要介绍。

二、seg指令的基本概念seg指令是一种用于控制七段显示译码器的指令,通过该指令,可以将需要显示的数字发送给七段显示译码器,从而实现数字的显示。

在指令的使用过程中,我们需要了解一些基本的用法和注意事项。

三、seg指令的语法格式在使用seg指令时,需要按照其规定的语法格式进行操作,以确保指令的正确执行。

一般而言,seg指令的语法格式如下:seg [寄存器],[数字]其中,寄存器表示要操作的七段显示译码器的寄存器,数字则表示要显示的数字。

四、seg指令的使用方法在实际编程中,我们可以通过使用seg指令来控制七段显示译码器的显示。

具体的使用方法如下:1. 需要将要显示的数字存储到一个寄存器中,通常是将其存储到某个特定的内存位置区域中。

2. 接下来,使用seg指令将存储的数字发送给七段显示译码器,从而实现数字的显示。

五、seg指令的注意事项在使用seg指令时,需要注意以下一些事项,以确保指令的正确执行:1. 确保寄存器的正确选择:在使用seg指令时,需要选择正确的寄存器来操作,以确保数字能够正确地发送给七段显示译码器。

2. 确保数字的有效性:在使用seg指令发送数字时,需要确保数字的有效性,避免发送无效的数字,从而造成显示错误。

六、seg指令的实际应用seg指令在嵌入式系统开发中有着广泛的应用,在一些数字显示设备的驱动程序中,我们经常会看到seg指令的身影。

通过使用seg指令,可以方便地控制七段显示译码器的显示,从而满足不同应用场景下的显示需求。

七、结语seg指令是一种用于控制七段显示译码器的指令,通过该指令,可以实现数字的显示。

在使用seg指令时,需要按照其规定的语法格式进行操作,并注意一些使用方法和注意事项,以确保指令的正确执行。

实验五-7段数码显示译码器设计

实验五7段数码显示译码器设计实验报告一、实验要求1、GW48实验箱2、写出7段数码显示译码器程序3、总结实验步骤和实验结果二、实验内容1、说明例中各语句的含义,以及该例的整体功能。

在max+plus2或quartus2上对以下该例进行编辑、编译、综合、适配仿真,给出其所有信号的时序仿真波形。

module zdw(in,out);output [6:0]out;input [3:0]in;reg[6:0]out;always@(in)begincase(in)4'd0: out=7'b1111110;4'd1: out=7'b0110000;4'd2: out=7'b1101101;4'd3: out=7'b1111001;4'd4: out=7'b0110011;4'd5: out=7'b1011011;4'd6: out=7'b1011111;4'd7: out=7'b1110000;4'd8: out=7'b1111111;4'd9: out=7'b1111011;4'd10: out=7'b1110111;4'd11: out=7'b0011111;4'd12: out=7'b1001110;4'd13: out=7'b0111101;4'd14: out=7'b1001111;4'd15: out=7'b1000111;default: out=7'bx;endcaseendendmodule2、引脚锁定以及硬件下载测试。

建议选实验电路模式6,用数码8显示译码输出(PIO46—PIO40)。

键8,键7,键6,键5四位控制输入,硬件验证译码器的工作性能。

十六进制7段数码显示译码器设计

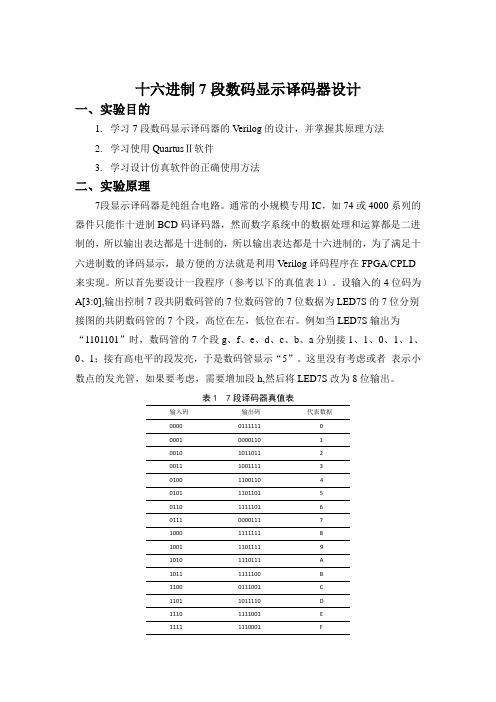

十六进制7段数码显示译码器设计一、实验目的1.学习7段数码显示译码器的Verilog的设计,并掌握其原理方法2.学习使用QuartusⅡ软件3.学习设计仿真软件的正确使用方法二、实验原理7段显示译码器是纯组合电路。

通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码器,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用Verilog译码程序在FPGA/CPLD 来实现。

所以首先要设计一段程序(参考以下的真值表1)。

设输入的4位码为A[3:0],输出控制7段共阴数码管的7位数码管的7位数据为LED7S的7位分别接图的共阴数码管的7个段,高位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

这里没有考虑或者表示小数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。

表1 7段译码器真值表输入码输出码代表数据0000 0111111 00001 0000110 10010 1011011 20011 1001111 30100 1100110 40101 1101101 50110 1111101 60111 0000111 71000 1111111 81001 1101111 91010 1110111 A1011 1111100 B1100 0111001 C1101 1011110 D1110 1111001 E1111 1110001 F三、实验任务将设计好的Verilog译码器程序在QuartusⅡ上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。

四、实验步骤1.新建一个文件夹DECL_DEMO,然后选择File,点击new,再打开Verilog HDL File文件类型。

七段显示译码器7448功能,引脚图及应用电路

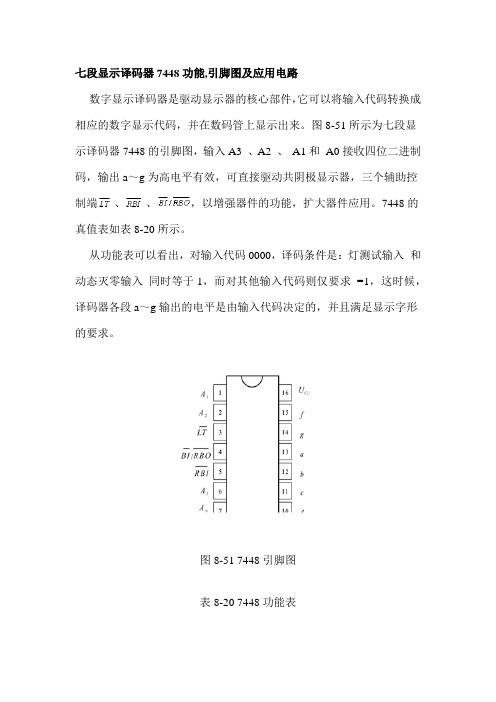

七段显示译码器7448功能,引脚图及应用电路数字显示译码器是驱动显示器的核心部件,它可以将输入代码转换成相应的数字显示代码,并在数码管上显示出来。

图8-51所示为七段显示译码器7448的引脚图,输入A3 、A2 、A1和A0接收四位二进制码,输出a~g为高电平有效,可直接驱动共阴极显示器,三个辅助控制端、、,以增强器件的功能,扩大器件应用。

7448的真值表如表8-20所示。

从功能表可以看出,对输入代码0000,译码条件是:灯测试输入和动态灭零输入同时等于1,而对其他输入代码则仅要求=1,这时候,译码器各段a~g输出的电平是由输入代码决定的,并且满足显示字形的要求。

图8-51 7448引脚图表8-20 7448功能表灯测试输入低电平有效。

当 = 0时,无论其他输入端是什么状态,所有输出a~g均为1,显示字形8。

该输入端常用于检查7448本身及显示器的好坏。

动态灭零输入低电平有效。

当=1,,且输入代码时,输出a~g均为低电平,即与0000码相应的字形0不显示,故称“灭零”。

利用=1与= 0,可以实现某一位数码的“消隐”。

灭灯输入/动态灭零输出是特殊控制端,既可作输入,又可作输出。

当作输入使用,且= 0时,无论其他输入端是什么电平,所有输出a~g均为0,字形熄灭。

作为输出使用时,受和控制,只有当,,且输入代码时,,其他情况下。

该端主要用于显示多位数字时多个译码器之间的连接。

【例8-13】七段显示器构成两位数字译码显示电路如图8-52所示。

当输入8421BCD码时,试分析两个显示器分别显示的数码范围。

图8-52 两位数字译码显示电路解:图8-52所示的电路中,两片7448的均接高电平。

由于7448(1)的,所以,当它的输入代码为0000时,满足灭零条件,显示器(1)无字形显示。

7448(2)的,所以,当它的输入代码为0000时,仍能正常显示,显示器(2)显示0。

而对其他输入代码,由于,译码器都可以输出相应的电平驱动显示器。

七段译码器

七段译码器目前用于显示电路的中规模译码器种类很多,其中用得较多的是七段显示译码器。

它的输入是8421BCD码,输出是由a,b,c,d,e,f,g构成的一种代码,我们称之为七段显示码。

LED七段显示器分为共阴极和共阳极两种,它们所需要的显示译码器各不相同,此处我们重点讨论共阴极。

共阴极数码管是一类数字形式的显示屏,通过对其不同的管教输入相对的电流,会使其发亮,从而显示出数字。

共阴极结构:各段发光二极管和阴极连在一起,将此公共点接地,某一段发光二极管的阴极为高电平时,该段发光。

引脚图逻辑原理a=∑(0,2,3,5,6,7,8,9)+d(10,11,12,13,14,15)b=∑(0,1,2,3,4,7,8,9) +d(10,11,12,13,14,15)c=∑(0,1,3,4,5,6,7,8,9) +d(10,11,12,13,14,15)d=∑(0,2,3,5,6,7,8,9)+d(10,11,12,13,14,15)e=∑(0,2,6,8,) +d(10,11,12,13,14,15)f=∑(0,4,5,6,8,9) +d(10,11,12,13,14,15)g=∑(2,3,4,5,6,8,9) +d(10,11,12,13,14,15)真值表其功能介绍如下:BI:4脚是消隐输入控制端,当BI=0 时,不管其它输入端状态如何,七段数码管均处于熄灭(消隐)状态,不显示数字。

LT:3脚是测试输入端,当BI=1,LT=0 时,译码输出全为1,不管输入DCBA 状态如何,七段均发亮,显示“8”。

它主要用来检测数码管是否损坏。

LE:锁定控制端,当LE=0时,允许译码输出。

LE=1时译码器是锁定保持状态,译码器输出被保持在LE=0时的数值。

A1、A2、A3、A4、为8421BCD码输入端。

a、b、c、d、e、f、g:为译码输出端,输出为高电平1有效。

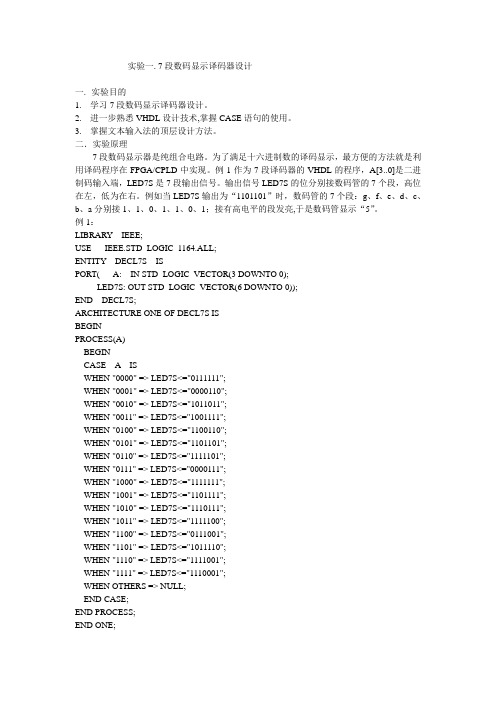

实验一7段数码显示译码器设计

实验一. 7段数码显示译码器设计一.实验目的1.学习7段数码显示译码器设计。

2.进一步熟悉VHDL设计技术,掌握CASE语句的使用。

3.掌握文本输入法的顶层设计方法。

二.实验原理7段数码显示器是纯组合电路。

为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中实现。

例1作为7段译码器的VHDL的程序,A[3..0]是二进制码输入端,LED7S是7段输出信号。

输出信号LED7S的位分别接数码管的7个段,高位在左,低为在右。

例如当LED7S输出为“1101101”时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

例1:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DECL7S ISPORT( A: IN STD_LOGIC_VECTOR(3 DOWNTO 0);LED7S: OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END DECL7S;ARCHITECTURE ONE OF DECL7S ISBEGINPROCESS(A)BEGINCASE A ISWHEN "0000" => LED7S<="0111111";WHEN "0001" => LED7S<="0000110";WHEN "0010" => LED7S<="1011011";WHEN "0011" => LED7S<="1001111";WHEN "0100" => LED7S<="1100110";WHEN "0101" => LED7S<="1101101";WHEN "0110" => LED7S<="1111101";WHEN "0111" => LED7S<="0000111";WHEN "1000" => LED7S<="1111111";WHEN "1001" => LED7S<="1101111";WHEN "1010" => LED7S<="1110111";WHEN "1011" => LED7S<="1111100";WHEN "1100" => LED7S<="0111001";WHEN "1101" => LED7S<="1011110";WHEN "1110" => LED7S<="1111001";WHEN "1111" => LED7S<="1110001";WHEN OTHERS => NULL;END CASE;END PROCESS;END ONE;三.实验内容1.说明例1各语句的含义,以及该例的整体功能。

七段显示译码器

D

数据输出

Y2 (G1 G2A G2B ) A2 A1 A0 G2A

74138译码器作为数据分配器时的功能表

输入

输出

G1 G2B G2A C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

L L X X X XHHHHHHHH

HLDL L LDHHHHHHH HLDL LHHDHHHHHH H L D L H L HHDHHHHH H L D L HHHHHDHHHH HLDHL LHHHHDHHH H L DH L HHHHHHDHH H L DHH L HHHHHHDH H L DHHHHHHHHHHD

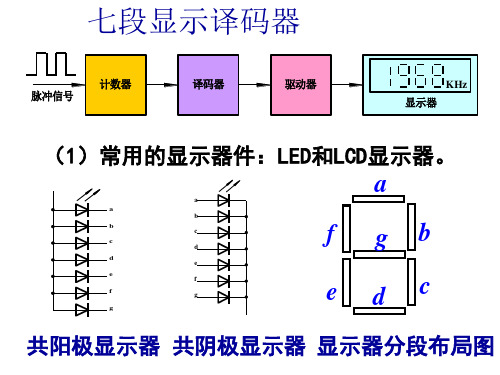

七段显示译码器

脉冲信号

计数器

译码器

驱动器

KHz 显示器

(1)常用的显示器件:LED和LCD显示器。

a a

b b

c

c d

d e

e f

f

g

g

a f gb e dc

共阳极显示器 共阴极显示器 显示器分段布局图

计数器 脉冲信号

译码器

驱动器

abcde f g

111111 0 f

0110000

1101101

e

3.4.3 数据分配器

数据分配器:相当于有多个输出的单刀多掷开关, 将从一个数据源来的数据分时送到多个不同的通 道上去的逻辑电路。

Y0 Y1 数据输入

Y7 通道选择信号

例:用译码器实现数据分配器

数据输入

D

Y

0

Y

1

74138

Y

2

Y

3

G

2A

Y

4

Y

5

Y

6

Y

7Aຫໍສະໝຸດ AAGG0

BCD七段数码管显示译码器和真值表资料教学教材

BCD七段数码管显示译码器和真值表资料BCD七段数码管显示译码器和真值表类别:网文精粹阅读:1865发光二极管(LED)由特殊的半导体材料砷化傢、磷砷化傢等制成,可以单独使用,也可以组装成分段式或点阵式LED显示器件(半导体显示器)。

分段式显示器(LED数码管)由7条线段围成8型,每一段包含一个发光二极管。

外加正向电压时二极管导通,发出清晰的光,有红、黄、绿等色。

只要按规律控制各发光段的亮、灭,就可以显示各种字形或符号。

图4 - 17(a是共阴式LED数码管的原理图,图4-17(b)是其表示符号。

使用时,公共阴极接地,7个阳极a~g由相应的BCD七段译码器来驱动(控制),如图4 - 17(c)所示BCD七段译码器的输入是一位BCD码(以D、C、B、A表示),输出是数码管各段的驱动信号(以Fa~Fg表示),也称4—7译码器。

若用它驱动共阴LED 数码管,则输出应为高有效,即输出为高(1)时,相应显示段发光。

例如,当输入8421码DCBA=0100时,应显示,即要求同时点亮b、c、f、g段,熄灭a d、e段,故译码器的输出应为Fa~Fg=0110011,这也是一组代码,常称为段码。

同理,根据组成0~9这10个字形的要求可以列出8421BCD七段译码器的真值表,见表4 - 12(未用码组省略)表4-12 BCD -段译码器真直表D 输C入F M出字晤A尺Fj00001111110一n 00Q101100a a1001a]10i I a* 匚001i111i001二010a c110011LJ010i1Q11011Ei011010i1111r Li0111111100Q01000]'1i I111100i11110i i匚MSI BCD七段译码器就是根据上述原理组成的,只是为了使用方便,增加了一些辅助控制电路。

这类集成译码器产品很多,类型各异,它们的输出结构也各不相同,因而使用时要予以注意。

图4-17(c)是BCD七段译码器驱动LED 数码管(共阴)的接法。

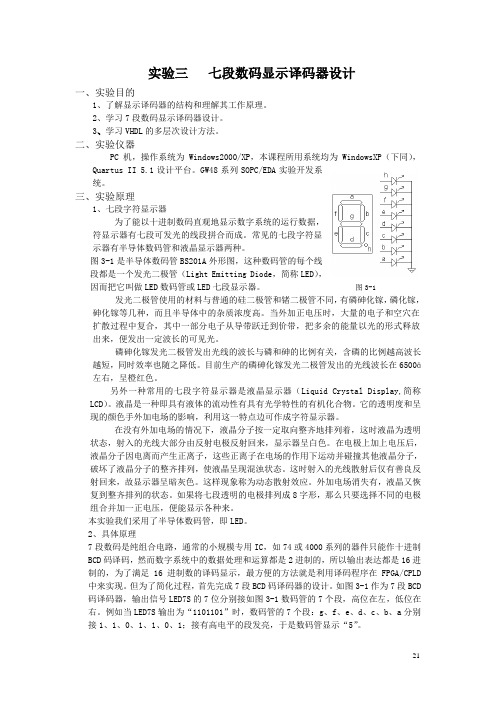

实验三七段数码显示译码器设计

实验三七段数码显示译码器设计一、实验目的1、了解显示译码器的结构和理解其工作原理。

2、学习7段数码显示译码器设计。

3、学习VHDL的多层次设计方法。

二、实验仪器PC机,操作系统为Windows2000/XP,本课程所用系统均为WindowsXP(下同),Quartus II 5.1设计平台。

GW48系列SOPC/EDA实验开发系统。

三、实验原理1、七段字符显示器为了能以十进制数码直观地显示数字系统的运行数据,符显示器有七段可发光的线段拼合而成。

常见的七段字符显示器有半导体数码管和液晶显示器两种。

图3-1是半导体数码管BS201A外形图,这种数码管的每个线段都是一个发光二极管(Light Emitting Diode,简称LED),因而把它叫做LED数码管或LED七段显示器。

图3-1 发光二极管使用的材料与普通的硅二极管和锗二极管不同,有磷砷化镓,磷化镓,砷化镓等几种,而且半导体中的杂质浓度高。

当外加正电压时,大量的电子和空穴在扩散过程中复合,其中一部分电子从导带跃迁到价带,把多余的能量以光的形式释放出来,便发出一定波长的可见光。

磷砷化镓发光二极管发出光线的波长与磷和砷的比例有关,含磷的比例越高波长越短,同时效率也随之降低。

目前生产的磷砷化镓发光二极管发出的光线波长在6500ā左右,呈橙红色。

另外一种常用的七段字符显示器是液晶显示器(Liquid Crystal Display,简称LCD)。

液晶是一种即具有液体的流动性有具有光学特性的有机化合物。

它的透明度和呈现的颜色手外加电场的影响,利用这一特点边可作成字符显示器。

在没有外加电场的情况下,液晶分子按一定取向整齐地排列着,这时液晶为透明状态,射入的光线大部分由反射电极反射回来,显示器呈白色。

在电极上加上电压后,液晶分子因电离而产生正离子,这些正离子在电场的作用下运动并碰撞其他液晶分子,破坏了液晶分子的整齐排列,使液晶呈现混浊状态。

这时射入的光线散射后仅有善良反射回来,故显示器呈暗灰色。

CD4511(BCD码七段码译码器)

CD4511是一个用于驱动共阴极LED (数码管)显示器的BCD 码—七段码译码器,特点如下:具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流。

可直接驱动LED显示器。

CD4511 是一片CMOS BCD—锁存/7 段译码/驱动器,引脚排列如图2 所示。

其中a b c d 为BCD 码输入,a为最低位。

LT为灯测试端,加高电平时,显示器正常显示,加低电平时,显示器一直显示数码“8”,各笔段都被点亮,以检查显示器是否有故障。

BI为消隐功能端,低电平时使所有笔段均消隐,正常显示时,B1端应加高电平。

另外CD4511有拒绝伪码的特点,当输入数据越过十进制数9(1001)时,显示字形也自行消隐。

LE是锁存控制端,高电平时锁存,低电平时传输数据。

a~g是7 段输出,可驱动共阴LED数码管。

另外,CD4511显示数“6”时,a段消隐;显示数“9”时,d段消隐,所以显示6、9这两个数时,字形不太美观图3是CD4511和CD4518配合而成一位计数显示电路,若要多位计数,只需将计数器级联,每级输出接一只CD4511 和LED 数码管即可。

所谓共阴LED 数码管是指7 段LED 的阴极是连在一起的,在应用中应接地。

限流电阻要根据电源电压来选取,电源电压5V时可使用300Ω的限流电阻。

用CD4511实现LED与单片机的并行接口方法如下图:(略)CD4511 引脚图其功能介绍如下:BI:4脚是消隐输入控制端,当BI=0 时,不管其它输入端状态如何,七段数码管均处于熄灭(消隐)状态,不显示数字。

LT:3脚是测试输入端,当BI=1,LT=0 时,译码输出全为1,不管输入DCBA 状态如何,七段均发亮,显示“8”。

它主要用来检测数码管是否损坏。

LE:锁定控制端,当LE=0时,允许译码输出。

LE=1时译码器是锁定保持状态,译码器输出被保持在LE=0时的数值。

A1、A2、A3、A4、为8421BCD码输入端。

七段显示译码器资料讲解

此课件下载可自行编辑修改,仅供参考! 感谢您的支持,我们努力做得更好!谢谢

3.4.3 数据分配器

数据分配器:相当于有多个输出的单刀多掷开关, 将从一个数据源来的数据分时送到多个不同的通 道上去的逻辑电路。

Y0 Y1 数据输入

Y7 通道选择信号

例:用译码器实现数据分配器

数据输入

D

Y

0

Y

1

74138

Y

2

Y

3

G

2A

Y

4

Y

5

Y

6

Y

7

A

A

AG

G

0

1

2

2B

1

010

地址 输入

1

EN

七段显示译码器

(2)集成电路显示译码器7448

3个控制端

逻辑图

4个输入端

7个输出端

C B A

LT

RBI BI/RBO

a b

7448

.

.

.ห้องสมุดไป่ตู้

g

7448功能框图

逻辑功能

十进制

输入

BI/

输出

字

或功能 LT RBI D C B A RBO a b c d e f g 形

0 H H L L L L H HHH H H H L

D

数据输出

Y 2(G 1G 2AG 2B )A 2A 1A 0G 2A

74138译码器作为数据分配器时的功能表

输入

输出

G1 G2B G2A C B A Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

L L X X X XHHHHHHHH

HLDL L LDHHHHHHH HLDL LHHDHHHHHH H L D L H L HHDHHHHH H L D L HHHHHDHHHH HLDHL LHHHHDHHH H L DH L HHHHHHDHH H L DHH L HHHHHHDH H L DHHHHHHHHHHD

实验一七段数码管显示译码器

实验⼀七段数码管显⽰译码器实验⼀七段数码显⽰译码器⼀.实验⽬的:1.设计七段显⽰译码器,并在实验板上验证;2.学习Verilog HDL⽂本⽂件进⾏逻辑设计输⼊;3.学习设计仿真⼯具的使⽤⽅法;⼆.实验内容1.实现BCD/七段显⽰译码器的“ Verilog ”语⾔设计。

说明:7段显⽰译码器的输⼊为:IN0…IN3共5根, 7段译码器的逻辑表同学⾃⾏设计,要求实现功能为:输⼊“ 0…15 ”(⼆进制),输出“ 0…9…F ”(显⽰数码),输出结果应在数码管(共阴)上显⽰出来。

2.使⽤⼯具为译码器建⽴⼀个元件符号3.设计仿真⽂件,进⾏验证。

4.编程下载并在实验箱上进⾏验证。

三.实验原理:7段数码是纯组合电路,通常的⼩规模专⽤IC,如74或4000系列的器件只能作⼗进制BCD码译码,然⽽数字系统中的数据处理和运算都是⼆进制的,所以输出表达都是⼗六进制的,为了满⾜⼗六进制数的译码显⽰,最⽅便的⽅法就是利⽤译码程序在FPGA/CPLD 中来实现。

例如6-18作为7段译码器,输出信号LED7S的7位分别接图6-17数码管的7个段,⾼位在左,低位在右。

例如当LED7S输出为“1101101”时,数码管的7个段g,f,e,d,c,b,a分别接1,1,0,1,1,0,1;接有⾼电平的段发亮,于是数码管显⽰“5”。

这⾥没有考虑表⽰⼩数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。

四.实验步骤1.编辑和输⼊设计⽂件新建⽂件夹——输⼊源程序——⽂件存盘2.创建⼯程打开并建⽴新⼯程管理窗⼝——将设计⽂件加⼊⼯程中——选择⽬标芯⽚——⼯具设置——结束设置3.全程编译前约束项⽬设置选择FPGA⽬标芯⽚——选择配置器件的⼯作⽅式——选择配置器件和编程⽅式——选择⽬标器件引脚端⼝状态——选择Verilog语⾔版本4.仿真测试五.实验参考程序module LED(A,LED7S);input [3:0]A;output [6:0]LED7S;reg [6:0]LED7S;always @ (A)begin:case(A)4'b0000: LED7S<=7'b0111111;4'b0001: LED7S<=7'b0000110;4'b0010: LED7S<=7'b1011011;4'b0011: LED7S<=7'b1001111; 4'b0100: LED7S<=7'b1100110; 4'b0101: LED7S<=7'b1101101; 4'b0110: LED7S<=7'b1111101; 4'b0111: LED7S<=7'b0000111; 4'b1000: LED7S<=7'b1111111; 4'b1001: LED7S<=7'b1101111; 4'b1010: LED7S<=7'b1110111; 4'b1011: LED7S<=7'b1111100; 4'b1100: LED7S<=7'b0111001; 4'b1101: LED7S<=7'b1011110; 4'b1110: LED7S<=7'b1111001; 4'b1111: LED7S<=7'b1110001; default: LED7S<=7'b0111111; endcaseendendmodule六.编译仿真结果1.时序仿真:2.延时分析及结果:3.⽣成RTL原理图:4.该实验的配置模式:5.适配板布局图及实验仪IO脚与芯⽚的管脚对应关系和其详细放⼤图⽚:6.⼗六进制逻辑分析:7.计数器和译码器连接电路的顶层⽂件原理图:七.体会思考:通过本次实验对EDA和QUARTER2有了初步的了解,第⼀次上机感觉挺难的,这次对Verilog也有了深⼊了解。

七段数字显示器及显示译码器

七段数字显示器及显示译码器一、七段数字显示器七段数字显示器就是将7个发光二极管(加小数点为8个)按一定的方式排列起来,a 、b 、c 、d 、e 、f 、g (小数点DP)各对应一个发光二极管,利用不同发光段的组合,显示不同的阿拉伯数字,如图7.15所示。

ab c d ef g DPe d COM c DPg f COM a b(a) 数码管外形 (b) 段组合图图7.15 七段数字显示器及发光段组合图 按内部连接方式不同,七段数字显示器分为共阴极和共阳极两种,如图7.16所示。

COM COM a b c d e f g DPa b c d e f g DP(a) 共阳极接法 (b) 共阴极接法图7.16半导体数字显示器的内部接法半导体显示器的优点是工作电压较低(1.5~3V)、体积小、寿命长、亮度高、响应速度快、工作可靠性高,缺点是工作电流大,每个字段的工作电流为10mA 左右。

二、集成七段显示译码器CD4511集成七段显示译码器CD4511为双列直插16脚封装,它将 BCD 标准代码变换成驱动七段数码管所需的信号。

CD4511的外形如图7.17所示。

B C LT BI LE D A U SSU DD Y f Y g Y a Y b Y c Y d Y e CD4511图7.17 集成七段显示译码器CD4511其中四线A~D为BCD码输入端,高电平有效。

A为低位输入端,D为高位端。

七段Y a~Y g输出高电平以驱动共阴极数码管发光并显示特定的符号,如阿拉伯数字0~9,集成七段显示译码器的输出,由表7.6可知,也是一种多位二进制代码,但该种代码除了用于显示之外,与显示字符的数值大小、特性等无任何关联,也称之为字段码。

LE为锁存控制端,高电平时能够锁存输入的BCD码。

LT为灯测试反相控制端,BI为消隐反相控制端。

其逻辑功能见表7.6。

表7.6 七段显示译码器CD4511功能表三、数码管显示电路数显电容计显示部分的显示器件采用了3位共阴极数码管,可以显示从000~999的数值。

数字电子课程设计七段LED显示译码器

数字电路设计论文七段LED显示译码器目录1.分段式2.BCD-七段显示译码器3.七段显示译码器4.动态灭零输入RBI5.动态灭零输出RBO分段式数码由散布在同一平面上假设干段发光的笔画组成,如半导体显示器。

半导体数码管——BS201A半导体数码管是分段式半导体显示器件,其大体结构是PN 结,即用发光二极管(LED)组成字型来来显示数字。

这种数码管的每一个线段都是一个发光二极管,因此也称LED数码管或LED七段显示器。

七段显示器由发光二极管(light emitting diode ; LED)组合而成,分为共阴及共阳两型,将内部所有LED的阴极接在一路的称为共阴型,内部所有LED的阳极接在一路的称为共阳型,见以下图:因为运算机输出的是BCD码,要想在数码管上显示十进制数,就必需先把BCD码转换成 7 段字型数码管所要求的代码。

咱们把能够将运算机输出的BCD码换成 7 段字型代码,并使数码管显示出十进制数的电路称为“七段字型译码器”。

1)输入:8421BCD码,用A3 A2 A1 A0表示(4位)。

2)输出:七段显示,用Ya ~ Yg 表示(7位)3)逻辑符号:七段显示译码器在数字测量仪表和各类数字系统中,都需要将数字量直观地显示出来,一方面供人们直接读取测量和运算的结果;另一方面用于监视数字系统的工作情形。

因此,数字显示电路是许多数字设备不可缺少的部份。

数字显示电路通常由译码器、驱动器和显示器等部份组成,如图5.3.5所示。

下面对显示器和译码驱动器别离进行介绍。

数码显示器是用来显示数字、文字或符号的器件,此刻已有多种不同类型的产品,普遍应用于各类数字设备中,目前数码显示器件正朝着小型、低功耗、平面化方向进展。

数码的显示方式一样有三种:第一种是字形重叠式,它是将不同字符的电极重叠起来,要显示某字符,只须使相应的电极发亮即可,如辉光放电管、边光显示管等。

第二种是分段式,数码是由散布在同一平面上假设干段发光的笔画组成,如荧光数码管等。

七段LED显示译码器

七段LED显示译码器来自EEWiki.跳转到: 导航, 搜索目录[隐藏]∙ 1 分段式∙ 2 BCD---七段显示译码器(74LS48)∙ 3 七段显示译码器∙ 4 动态灭零输入RBI∙ 5 动态灭零输出RBO[编辑]分段式数码由分布在同一平面上若干段发光的笔画组成,如半导体显示器。

半导体数码管——BS201A半导体数码管是分段式半导体显示器件,其基本结构是PN结,即用发光二极管(LED)组成字型来来显示数字。

这种数码管的每个线段都是一个发光二极管,因此也称LED数码管或LED七段显示器。

[编辑]BCD---七段显示译码器(74LS48)因为计算机输出的是BCD码,要想在数码管上显示十进制数,就必须先把BCD码转换成 7 段字型数码管所要求的代码。

我们把能够将计算机输出的BCD码换成 7 段字型代码,并使数码管显示出十进制数的电路称为“七段字型译码器”。

1)输入:8421BCD码,用A3 A2 A1 A0表示(4位)。

2)输出:七段显示,用Ya ~ Yg 表示(7位) 3)逻辑符号:[编辑]1.七段显示译码器在数字测量仪表和各种数字系统中,都需要将数字量直观地显示出来,一方面供人们直接读取测量和运算的结果;另一方面用于监视数字系统的工作情况。

因此,数字显示电路是许多数字设备不可缺少的部分。

数字显示电路通常由译码器、驱动器和显示器等部分组成,如图5.3.5所示。

下面对显示器和译码驱动器分别进行介绍。

数码显示器是用来显示数字、文字或符号的器件,现在已有多种不同类型的产品,广泛应用于各种数字设备中,目前数码显示器件正朝着小型、低功耗、平面化方向发展。

数码的显示方式一般有三种:第一种是字形重叠式,它是将不同字符的电极重叠起来,要显示某字符,只须使相应的电极发亮即可,如辉光放电管、边光显示管等。

第二种是分段式,数码是由分布在同一平面上若干段发光的笔划组成,如荧光数码管等。

第三种是点阵式,它由一些按一定规律排列的可发光的点阵所组成,利用光点的不同组合便可显示不同的数码,如场致发光记分牌。

七段显示译码器

七段显示译码器七段显示译码器是一种非常常用的电子元件,它的作用是将数字信号转换成七段显示器可显示的信号。

七段显示译码器的种类和型号较多,但是其基本工作原理都是相同的。

七段显示译码器的工作原理:该译码器的输入端接受二进制数字信号,该信号被分解为每位信号的输入端,最终输出到七段显示器的七个单元中,互不干扰,形成符合数字的图形。

七段显示器的七个单元所代表的数字分别是0-9,A-F。

同一时刻只能显示一个数字。

通常情况下,数字信号输入端的位数和七段显示器的单元数相同,比如4位二进制数字信号对应着4个输入端,同时也对应着4个七段显示器单元。

在实际电路中,七段显示译码器的输入端接受的是二进制信号,这些二进制信号实际上是数字信号的编码,而数字信号经过编码后能够更加稳定和可靠地在电路中传输。

七段显示译码器的各个输入端接受的编码数据被转换为相应的七段显示数据,并输出到相应的七段显示单元上,从而在七段显示器中显示相应的数字或字符。

例如,当输入信号为10时,该信号被转换为二进制信号1010,该信号靠近二进制译码器的输入端,四个输入端分别接受10的四个二进制编码。

最后,在七段显示器的单元中显示数字0和数字1。

七段显示译码器相关参数:七段显示器的显示分辨率是指能显示的位数,其中一位数字或字母所占的像素数称为显示分辨率。

通常情况下,七段显示器的分辨率都是相同的。

七段显示器的色彩深度是指每个像素能够显示的颜色数量,七段显示器的色彩深度通常是固定的。

七段显示译码器的相关优点:1. 体积小,易于装配,能够在小尺寸电路中使用;2. 高度集成,节省了大量空间;3. 低功耗,可在低功率设备中使用。

并且,七段显示译码器也用于很多需要数字显示的地方,比如电子表、电子秤、温度计、智能穿戴设备等。

在自动控制系统和自动化生产线中,七段显示器和相应的译码器也被广泛使用。