AMBA+AXI4总线的研究与实现

AMBA_AXI4协议

AMBA_AXI4协议AMBA (Advanced Microcontroller Bus Architecture) AXI4 协议是由 ARM(Advanced RISC Machines)公司提出的一种高性能、低功耗的总线协议。

它主要用于片上系统(SoC)中的片上通信和互连,并且被广泛应用于各种嵌入式系统设计中。

AMBAAXI4协议是AMBA协议系列中的最新版本,相较于前几个版本,它引入了许多新的特性和功能以提高数据传输的效率和可靠性。

该协议的主要目标是支持高性能、多处理器SoC中各个主从设备之间的数据传输,并能同时支持大数据宽度和高频率操作。

AXI4协议采用了一种点对点的通信方法,可以通过AMBAAXI的互连结构连接多个主设备和从设备。

主设备可以发起读请求和写请求,从设备则负责接收和响应这些请求。

协议中定义了许多标准信号和通信规范,以确保数据传输的稳定和可靠。

AXI4 协议可以支持单片上的数据传输速率高达几 GB/s,并且具有很高的吞吐量。

这是通过采用多种技术来实现的,包括独立的地址和数据通道、乱序传输和突发传输等。

AXI4 协议还引入了一个新的数据传输机制,称为 AXI4-stream,用于处理实时的数据流传输。

协议中还引入了一种称为 AXI4-Lite 的简化版本,专门用于对接一些简单的外设,如配置寄存器和状态寄存器。

AXI4-Lite 协议只使用一条地址通道和一条数据通道,并且不支持乱序传输和突发传输,因此在数据传输效率和性能上相对较低,但在资源占用和易用性方面有一定的优势。

总的来说,AMBAAXI4协议是一种功能强大、灵活性高的总线协议,适用于各种复杂的嵌入式系统设计。

它在数据传输的性能和速度方面具有很大的优势,并提供了多种传输机制和通信规范,可以满足不同设备的需求。

通过使用AMBAAXI4协议,设计人员可以更轻松地构建高性能、高效能的嵌入式系统。

AMBA_AHB_APB_AXI协议对比分析

AMBA_AHB_APB_AXI协议对比分析引言:AMBA (Advanced Microcontroller Bus Architecture)是ARM公司提供的一种开放式的总线标准,旨在为SOC(System on Chip)设计提供一个灵活、高性能的总线框架。

AMBA协议家族中包括了AHB(Advanced High-performance Bus)、APB(Advanced Peripheral Bus)和AXI (Advanced eXtensible Interface)三种协议。

本文将对这三种协议进行对比分析,详细介绍其特点、性能和应用场景。

一、AHB协议AHB协议是AMBA协议家族中最早发布的协议之一,用于连接SOC内部的高性能主设备和多个从设备之间的通信。

AHB协议通过总线仲裁、突发传输和分片传输等技术,实现了高带宽和低延迟的数据传输。

其主要特点包括:1.性能:-支持高带宽传输:AHB协议支持高带宽的传输,能够满足高性能SOC 内部各个模块之间的数据传输需求。

- 低延迟传输:AHB协议通过引入Pipeline和Split交易等机制,实现了低延迟的数据传输。

2.特性:-总线仲裁:AHB总线采用非常灵活的总线仲裁机制,可以支持多主设备并发传输。

-突发传输:AHB协议支持突发传输,可以在一次仲裁后连续传输多个数据。

-分片传输:AHB协议支持分片传输,可以将大块数据分片传输,降低总线带宽的占用率。

-低功耗:AHB协议通过支持低功耗技术,降低了整个系统的功耗消耗。

3.应用场景:-SOC内部高性能数据传输:AHB协议主要适用于SOC内部的高性能数据传输,例如CPU和DMA控制器、外设控制器之间的数据传输。

二、APB协议APB协议是AMBA协议家族中最简单的一种协议,用于连接SOC内部的低带宽从设备,例如配置寄存器和控制逻辑等。

APB协议相对于AHB协议具有以下特点:1.性能:-低带宽传输:APB协议支持低带宽的传输,主要用于传输配置和控制信息,而不是大量的数据。

05AXI4总线axi-stream(AXI4总线实战)

05AXI4总线axi-stream(AXI4总线实战)软件版本:vitis2020.2(vivado2020.2)操作系统:WIN10 64bit硬件平台:适⽤XILINX A7/K7/Z7/ZU/KU系列FPGA(⽶联客(milianke)MZU07A-EG硬件开发平台)登录"⽶联客"FPGA社区-视频课程、答疑解惑!5.1概述AXI4-Stream去掉了地址,允许⽆限制的数据突发传输规模,AXI4-Stream接⼝在数据流传输中应⽤⾮常⽅便,本来⾸先介绍了AXI4-Stream协议的型号定义,并且给出了⼀些Stream接⼝的时序⽅案图。

之后通过VIVADO⾃带的AXI4模板,创建axi-stream-master和axi-stream-slave ip。

通过图形设计连线,添加仿真激励完成验证。

本⽂实验⽬的:1:掌握基于VIVADO⼯具产⽣AXI协议模板2:掌握通过VIVADO⼯具产⽣AXI-Stream代码3:掌握通过VIVADO封装AXI-Stream图形化IP4:通过仿真验证AXI-Stream IP的⼯作是否正常。

5.2AXI4-Stream协议介绍5.2.1信号定义信号源描述ACLK时钟源信号在ACLK信号上升沿采样ARESETn复位源复位信号,ARESETn低电平有效TVALID master TVALID代表主设备数据有效,当TVALID和TREADY同时有效完成数据收发TREADY slave TREADY表⽰从设备准备可以,主设备可以发送数据,当TVALID和TREADY同时有效完成数据收发TDATA[(8n-1):0]master TDATA axi-stream的数据TSTRB[(n-1):0]master TSTRB[n-1:0]对应的bit位为1代表对应的字节有效,否则⽆效,但是会占⽤这个数据位。

TKEEP[(n-1):0]master KEEP[n-1:0]对应的bit位为1代表对应的字节有效,否则为空,可以丢掉。

AMBA双总线的设计与实现的开题报告

AMBA双总线的设计与实现的开题报告题目:AMBA双总线的设计与实现背景和意义:ARM体系结构的IP核一直在嵌入式系统中扮演着核心的角色。

而AMBA总线则是ARM基于其体系结构设计的一种高性能、低复杂度的通信协议。

作为现代计算机系统中的基本组件之一,总线的质量往往会直接影响整个系统的性能和可靠性。

本设计将AMBA双总线作为研究对象,旨在探究其设计方法和实现原理,深入了解其核心思想及其实际应用场景。

通过对AMBA双总线的研究,可以为以后的计算机系统设计和嵌入式开发提供参考和借鉴。

研究内容及计划:1. AMBA双总线的概述和原理分析(1) AMBA总线的基础概念和组成(2) AMBA双总线的特点和优势(3) AMBA双总线的基本结构及其原理分析2. 基于VHDL的AMBA总线的设计(1) AMBA双总线的主从模式设计(2) AMBA总线仲裁器的设计(3) AMBA总线时序控制器的设计(4) AMBA总线数据传输控制器的设计3. AMBA总线的仿真和验证(1) 仿真环境的搭建(2) 仿真测试用例的编写(3) 验证测试结果的分析4. 实际应用环境下的系统设计(1) 基于AMBA总线的系统设计(2) 系统的结构设计和优化(3) 系统的性能测试和验证参考资料:1. ARM AMBA总线协议规范2. AMBA Bus Min AHB Bus Matrix AHB Bus Bridge AHB Bus Decoder AHB Bus Functional model3. Design of System Architecture of SOC based Multi-mode Audio-Chip4. AMBA Bus Overview计划安排:第一周:研究AMBA总线的基础概念和组成,了解AMBA双总线的特点和优势第二周:研究AMBA双总线的基本结构及其原理分析,初步设计总线架构第三周:设计AMBA总线仲裁器,实现主从之间的调度和分配第四周:设计AMBA总线的时序控制器,对总线时序进行控制第五周:设计AMBA总线的数据传输控制器,实现数据传输和互联第六周:进行总线的仿真和测试,分析并验证测试结果第七周:基于AMBA总线的实际应用环境下的系统设计第八周:进行系统的性能测试和优化,调整完善系统设计第九周:撰写论文,并进行论文内容的修改和完善第十周:答辩预演和答辩预期目标:本设计旨在深入研究AMBA双总线的设计方法和实现原理,从多个角度解析其技术特点、优劣势及应用场景,掌握实际开发中如何进行总线设计的方法和技巧,并能够在实际应用环境中结合ARM体系结构进行系统设计和优化。

AMBA_AXI总线详解..

AXI总线协议资料整理第一部分:1、AXI简介:AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。

它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。

AXI 是AMBA 中一个新的高性能协议。

AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

2、AXI 特点:单向通道体系结构。

信息流只以单方向传输,简化时钟域间的桥接,减少门数量。

当信号经过复杂的片上系统时,减少延时。

支持多项数据交换。

通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道。

地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

第二部分:本部分对AXI1.0协议的各章进行整理。

第一章本章主要介绍AXI协议和AXI协议定义的基础事务。

1、AXI总线共有5个通道分别是read address channel、write address channel 、read data channel 、write data channel、write response channel。

每一个AXI传输通道都是单方向的。

2、每一个事务都有地址和控制信息在地址通道(address channel)中,用来描述被传输数据的性质。

3、读事务的结构图如下:4、写事务的结构图如下:5、这5条独立的通道都包含一个信息信号和一个双路的V ALD、READY握手机制。

AXI4整理解析

AMBA AXI Protocol Version:2.0序言面向的读者:这是AMBA (高速微控制器总线结构)AXI(高速可扩展接口)协议的说明书。

主要面向想熟悉AMBA、或是想去设计与AMBA AXI协议相兼容的系统和模块的读者。

说明书的内容安排:第一章绪论阅读本章,你会了解到AXI协议的结构、该协议中定义的基本的交易过程。

第二章信号描述本章主要介绍AXI一些信号的定义,如:写地址通道、读数据通道、写反应通道、读地址通道、读数据通道、以及低功耗接口等所用到信号。

第三章通道握手介绍通道握手的整个过程第四章地址选择主要讲AXI猝发类型、如何去计算地址、在一次猝发中使用字节通道传输的过程。

第五章附加的控制信息本章主要讲怎样让AXI协议支持系统级缓存和保护单元。

第六章自动访问本章主要讲互斥访问和锁定访问第七章反应信号主要讲AXI从模块的四种交易反应。

第八章模式调整主要讲AXI协议如何使用ID 标签去进行无序传输。

第九章数据总线主要讲在AXI读和写数据线上,如何处理交易大小可变的数据,以及如何用字节固定端的方式去处理混合端类型数据。

第十章非对齐传输主要讲如何使用AXI协议处理非对齐传输。

第十一章时钟和复字节主要讲述AXI时钟和复字节信号的时序。

第十二章低功耗接口主要讲如何使用AXI时钟控制接口,进入或者跳出一种低功耗的模式。

第十三章AXI4主要描述AXI协议中AXI3版本和AXI4版本技术上的不同。

第十四章AXI4-Lite主要讲述AXI4-Lite接口,它是一种简单控制寄存器类型的接口,在不需要AXI4全部功能的时候使用。

说明书中的约定如下:●印刷字体的类型●第四页的时序图●第四页中的信号印刷字体的类型:斜体此类型的字体用于突出显示重要的注释,介绍专用术语,指出文中所用到的参照和引用。

加粗字体此类型的字体用于突出显示接口包含的成分,如:菜单名。

指示出信号的名字。

在描述列表的适当之处,也可用来表示术语。

AMBA_AHB_APB_AXI协议对比分析..

9

HREADY:S应答M是否读写操作传输完成: 1-传输完 成, 0-需延长传输周期。需要注意的是,HREADY 做 为总线上的信号,它是M和S 的输入;同时每个S 需 要输出自己的HREADY。所以对于S 会有两个 HREADY 信号,一个来自总线的输入,一个自己给到 多路器的输出。 HRESP:S应答当前传输状态,OKAY、ERROR、 RETRY、SPLIT HRDATA:读数据总线,从S读到M

3

一个典型的基于AMBA 总线的SOC 系统架构

这种SOC架构以AHB为主干,挂上CPU,片上内 存,和其它DMA设备。

4

AHB 主要是针对高效率、高频宽及快速系统模块所设 计的总线,它可以连接如微处理器、芯片上或芯片外 的内存模块和DMA等高效率模块 AMBA 中的APB 主要用在低速且低功率的外围,可 针对外围设备作功率消耗及复杂接口的最佳化 APB在AHB和低带宽的外围设备之间提供了通信的桥 梁,所以APB是AHB或者ASB的二级扩展总线

19

APB/AHB/AXI对比

APB 低功耗 AHB 高速度 AXI 高速度,高带宽 管道化互联 单向通道 只需首地址 读写并行 支持乱序 支持非对齐操作 有效支持初始延迟 较高的外设

20

连线非常多

AHB总线互连

7

允许某个主设备控制总线 发起一个请求给仲 裁器

驱动地址和控 制信号

仅选中的从设备响应地 址/控制信号

拉高HREADY信号,总线 传输完成

8

AHB基本信号

HADDR:32位系统地址总线 HTRANS: M指示传输状态,NONSEQ、SEQ、IDLE、 BUSY HWRITE:传输方向:1-写,0-读 HSIZE:传输单位 HBURST:传输的burst类型 HWDATA:写数据总线,从M写到S

AMBA_AXI4协议

从 接 口

写响应通道 写响应

图2.2 写通道结构

AXI4全局信号

信号 ACLK ARESETn

源 时钟源 复位源

描述 全局时钟信号。所有的信号在全局时钟的上升沿采样。 全局复位信号。该信号低有效。

低功耗接口信号

信号 CSYSREQ 源 时钟控制器 描述 系统低功耗请求。这个信号来自系统时钟控制器使外设进入低功耗 状态 低功耗请求响应信号。这个信号来自系统低功耗请求外设的响应信 号 时钟活动。该信号表示外设是否要求它的时钟信号。1=要求外设时 钟。

从 从

从 从 主

AXI4通道及信号

--写数据通道

写数据通道传送所有从主设备到从设备的写数据。 表2.6给出了写数据通道信号及信号定义。写数据通道 包括: (1) 数据总线宽度:8、16、32、64、128、256、 512和1024位宽度; (2) 每8位有一个字节通道选通,用来表示数据总线 上的哪个字节是有效的;

BVALID BREADY

从 主

AXI4通道及信号

--写响应通道

图2.3给出了读猝发交易过程中典型信号的交互 过程。

图2.3读猝发交易过程中典型信号的交互过程

AXI4通道及信号

--写响应通道

图2.4给出了写交易过程中典型信号的交互过程。

图2.4写猝发交易过程中典型信号的交互过程

AXI4交易通道的握手信号关系

AWREADY

AWQOS[3:0] AWREGION[3:0]

从

主 主

写地址准备。这个信号表示从设备准备接受地址和相关的控制信号。

用于每个写交易的地址通道上的4位QoS标识符(可作为优先级标志) 用于每个写交易的地址通道上的域标识符。

AXI4通道及信号

基于AMBAAXI总线的Crossbar互联设计与实现

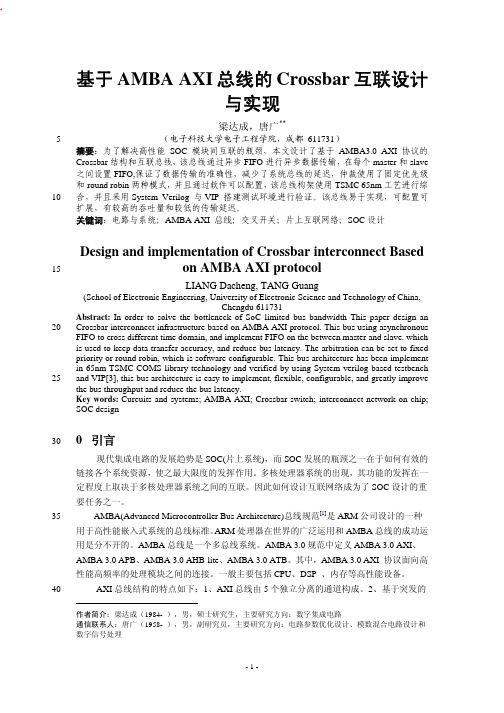

基于AMBA AXI 总线的Crossbar 互联设计与实现梁达成,唐广**作者简介:梁达成(1984- ),男,硕士研究生,主要研究方向:数字集成电路通信联系人:唐广(1958- ),男,副研究员,主要研究方向:电路参数优化设计、模数混合电路设计和数字信号处理(电子科技大学电子工程学院,成都 611731)5 摘要:为了解决高性能SOC 模块间互联的瓶颈,本文设计了基于AMBA3.0 AXI 协议的Crossbar 结构和互联总线,该总线通过异步FIFO 进行异步数据传输,在每个master 和slave 之间设置FIFO,保证了数据传输的准确性,减少了系统总线的延迟,仲裁使用了固定优先级和round robin 两种模式,并且通过软件可以配置,该总线构架使用TSMC 65nm 工艺进行综合,并且采用System Verilog 与VIP 搭建测试环境进行验证。

该总线易于实现,可配置可10扩展,有较高的吞吐量和较低的传输延迟。

关键词:电路与系统;AMBA AXI 总线;交叉开关;片上互联网络;SOC 设计Design and implementation of Crossbar interconnect Based on AMBA AXI protocol15 LIANG Dacheng, TANG Guang(School of Electronic Engineering, University of Electronic Science and Technology of China,Chengdu 611731Abstract: In order to solve the bottleneck of SoC limited bus bandwidth This paper design an Crossbar interconnect infrastructure based on AMBA AXI protocol. This bus using asynchronous 20 FIFO to cross different time domain, and implement FIFO on the between master and slave. which is used to keep data transfer accuracy, and reduce bus latency. The arbitration can be set to fixed priority or round robin, which is software configurable. This bus architecture has been implement in 65nm TSMC COMS library technology and verified by using System verilog based testbench and VIP[3], this bus architecture is easy to implement, flexible, configurable, and greatly improve 25the bus throughput and reduce the bus latency.Key words: Curcuits and systems; AMBA AXI; Crossbar switch; interconnect network on chip; SOC design0 引言30 现代集成电路的发展趋势是SOC(片上系统),而SOC 发展的瓶颈之一在于如何有效的链接各个系统资源,使之最大限度的发挥作用。

AMBA总线新一代标准AXI分析和应用

邮局订阅号:82-946360元/年技术创新片上系统SOC《PLC技术应用200例》您的论文得到两院院士关注AMBA总线新一代标准AXI分析和应用AnalysisandApplicationofNewGenerationAMBA3AXIProtocol(清华大学深圳研究生院)蒋周良权进国林孝康Jiang,ZhouliangQuan,Jin-guoLin,Xiaokang摘要:随着多核、多级内存及众多外设的SoC设计的复杂化,急需一种性能更好、更加灵活的片上互连总线体系结构。

AXI是ARM新推出的新一代AMBA片上总线,AXI的一序列新特点满足了高性能、高带宽、高速度的现代SoC设计的要求。

本文介绍了AXI的新特性,并和旧一代总线标准AHB性能做了详细的比较,同时给出了AXI的典型应用。

关键词:片上总线;AXI;AMBA;ARM;片上系统中图分类号:TP336文献标识码:AAbstract:Thegrowingcomplexityinmulti-processorSoCswithvariouslevelsofmemory,andmanydifferentperipherals,createsademandforaflexible,on-chipinterconnectarchitecturedesign.AXIisthenewgenerationofAMBAprotocol.TheAMBAAXIproto-colistargetedathigh-performance,high-frequency,high-speedsystemdesignsandincludesanumberoffeatures.Inthispaper,theAXIprotocolcharacteristicisintroducedandcomparedwithAHB.TheapplicationbasedonAXIisgiven.Keywords:on-chipBus,AXI,AMBA,ARM,SoC文章编号:1008-0570(2006)10-2-0275-031引言ARM作为业界顶尖的32位RISC嵌入式处理器,占有嵌入式处理器75%以上的市场。

AXI4协议规范

AXI4协议规范引言:AXI4(Advanced eXtensible Interface 4)是一种基于总线的互联标准,用于在现代计算机系统中连接多个IP核(Intellectual Property)。

它是由ARM公司开发的,旨在提供高性能、低功耗、可扩展的接口标准,方便IP核之间的通信和数据交换。

本文将详细介绍AXI4协议规范及其应用。

1. AXI4基本概念AXI4是AXI(Advanced eXtensible Interface)总线的第四个版本,相较于之前版本,它具有更加完善的功能和灵活性。

AXI4协议规范定义了一套一致的接口和通信机制,包括地址传输、数据传输、读写控制等。

它的设计目标是在高性能、高效能和低功耗之间取得平衡。

2. AXI4协议规范的主要特点2.1 高性能:AXI4使用了多种优化技术,例如乱序访问、多通道传输和同步等,以提供高性能的数据传输能力。

同时,它还支持全双工传输,能够同时进行读写操作,增强了系统的并行处理能力。

2.2 低功耗:AXI4在设计时考虑了功耗优化,采用了多种策略来减小功耗,例如自适应时钟门控、低功耗模式以及数据压缩等。

这些策略能够有效降低系统的功耗消耗。

2.3 可扩展性:AXI4协议规范支持多种方式的互连配置,包括单一主控模式、多主控模式和多从控模式等。

这在设计复杂的系统中具有重要的作用,能够方便地进行资源共享和IP核的扩展。

2.4 支持AMBA标准:AXI4兼容AMBA(Advanced Microcontroller Bus Architecture)标准,这使得它能够与其他AMBA协议兼容的IP核无缝集成,提高了系统的通用性和可拓展性。

3. AXI4的传输机制3.1 地址传输:AXI4使用32位或64位的地址总线进行地址传输,并支持4KB对齐的地址范围。

地址传输阶段包括有效地址和保留地址等信息。

3.2 数据传输:AXI4支持多种数据传输方式,包括单个传输、突发传输和无效传输等。

AMBA4_AXI4-Stream协议中文完整翻译

n

以 byte 为单位表示的数据总线的宽度

I

TID 宽度,推荐最大为 8-bits

d

TDEST 宽度,推荐最大为 4-bits

u

TUSER 宽度,推荐的 bit 数为以 byte 为单位表示的接口宽度的整数倍

信号 ACLK ARESETn TVALID

源 时钟源 复位源 主机

TREADY

从机

TDATA[(8n-1):0] 主机

小写 n

在信号名的开头或结尾,表示该信号为低有效

反馈

ARM 欢迎对于本产品及文档的反馈。

反馈关于本产品

如果你有任何关于本产品的看法和建议,请联系你的供应商并给出: 产品名 产品修订版本或版本 提供尽可能多的解释说明信息,如果合适的话,包括问题以及调试过程。

反馈关于内容

如果你有关于内容的意见,请发送邮件给 errata@,并给出: 标题:AMBA 4 AXI4-Stream Protocol Specification 数字:ARM IHI 0051A 你对内容有意见的页码 关于你的意见的一个简洁的解释说明

1 介绍

本章描述了 AXI4-流协议,并给出一些流类型的例子。本章包含以下章节: 关于 AXI4-流协议 数据流

1.1 关于 AXI4-流协议

AXI4-流协议作为一个标准接口,用于连接进行数据交换的组件。接口可以用来连接一个单一的主机,主机向接 收数据的单一从机发送数据。协议也可用于连接若干个主机和从机的组件。协议支持共用一组信号线的多个数据流, 允许构建一个通用互联(generic interconnect),可以执行 upsizing、downsizing 以及路由操作。

使用本文档

本文档包含以下章节: 1 介绍

一篇文章读懂读透FPGA AXI4 总线协议

一篇文章读懂读透FPGA AXI4 总线协议新一代0.绪论AXI是高级扩展接口,在AMBA3.0中提出,AMBA4.0将其修改升级为AXI4.0。

AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-stream1.简介1.1 关于AXI协议关键特点:适合高带宽低延时设计无需复杂的桥就能实现高频操作能满足大部分器件的接口要求适合高初始延时的存储控制器提供互联架构的灵活性与独立性向下兼容已有的AHB和APB接口分离的地址/控制、数据相位使用字节线来支持非对齐的数据传输使用基于burst的传输,只需传输首地址分离的读、写数据通道,能提供低功耗DMA支持多种寻址方式支持乱序传输允许容易的添加寄存器级来进行时序收敛1.2 AXI 架构共享地址与数据总线共享地址总线,多数据总线mul2.信号描述3.信号接口要求3.1时钟复位时钟复位3.2基本读写传输握手过程通道信号要求AXI协议要求通道间满足如下关系:写响应必须跟随最后一次burst的的写传输读数据必须跟随数据对应的地址通道握手信号的依耐关系3.3传输结构地址结构1)突发长度burst传输具有如下规则:wraburst 不能跨4KB边界不支持提前终止burst传输突发大小突发类型数据读写结构窄传输非对齐传输读写响应结构读传输的响应信息是附加在读数据通道上的,写传输的响应在写响应通道。

RRESP[1:0],读传输BRESP[1:0],写传输OKAY(‘b00):正常访问成功EXOKAY(‘b01):Exclusive 访问成功SLVERR(‘b10):从机错误。

表明访问已经成功到了从机,但从机希望返回一个错误的情况给主机。

DECERR(‘b11):译码错误。

一般由互联组件给出,表明没有对应的从机地址。

AMBA_AXI总线详解

AXI总线协议资料整理第一部分:1、AXI简介:AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。

它的地址/控制和数据相位是分离的,支持不对齐的数据传输,同时在突发传输中,只需要首地址,同时分离的读写数据通道、并支持显著传输访问和乱序访问,并更加容易就行时序收敛。

AXI 是AMBA 中一个新的高性能协议。

AXI 技术丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

2、AXI 特点:单向通道体系结构。

信息流只以单方向传输,简化时钟域间的桥接,减少门数量。

当信号经过复杂的片上系统时,减少延时。

支持多项数据交换。

通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道。

地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

第二部分:本部分对AXI1.0协议的各章进行整理。

第一章本章主要介绍AXI协议和AXI协议定义的基础事务。

1、AXI总线共有5个通道分别是read address channel、write address channel 、read data channel 、write data channel、write response channel。

每一个AXI传输通道都是单方向的。

2、每一个事务都有地址和控制信息在地址通道(address channel)中,用来描述被传输数据的性质。

3、读事务的结构图如下:4、写事务的结构图如下:5、这5条独立的通道都包含一个信息信号和一个双路的V ALD、READY握手机制。

一种AXI4总线转局部总线接口设计方法

· 103 ·

2020 年 4 月 25 日第 37 卷第 8 期

Key words:AXI4 bus;FPGA;local bus interface

0 引 言

AXI4(Advanced eXtensible Interface 4,高级可扩 展接口 4)总线是由 XILINX 公司和 ARM 公司共同 制定的新一代用于 SOC(System on Chip)片上系统内 IP(Intellectual Property)互联的总线规范,是第四版 AMBA(Advanced Microcontroller Bus Architecture, 高 级微控制器总线架构)规范中定义的七个总线 / 接口 之一 [1]。

2020 年 4 月 25 日第 37 卷第 8 期

doi:10.19399/ki.tpt.2020.08.031

Telecom Power Technology

Apr. 25,2020,Vol. 37 No. 8

设计应用

一种 AXI4 总线转局部总线接口设计方法

秦 冲,邓道杰,朱耀国 (航空工业西安航空计算技术研究所,陕西 西安 710065)

Telecom Power Technology

Apr. 25,2020,Vol. 37 No. 8

T0 ACLK

T0 ARACDLDKR

ARAVDADLIRD

AARRRVEAALDIDY

AMBA+AXI4总线的研究与实现

硕士学位论文AMBA AXI4总线的研究与实现RESEARCH AND IMPLEMENTATION OF AMBA AXI4 BUS杨舜琪哈尔滨工业大学2011年12月国内图书分类号:TN47 学校代码:10213 国际图书分类号:621.3 密级:公开工学硕士学位论文AMBA AXI4总线的研究与实现硕士研究生 :杨舜琪导 师 :张岩教授申请学位 :工学硕士学科 :微电子学与固体电子学所在单位 :深圳研究生院答辩日期 :2011年12月授予学位单位 :哈尔滨工业大学Classified Index: TN47U.D.C: 621.3Dissertation for the Master Degree in EngineeringRESEARCH AND IMPLEMENTATIONOF AMBA AXI4 BUSCandidate:Shunqi YANGSupervisor:Prof. Yan ZHANGAcademic Degree Applied for:Master of Engineering Speciality:Microelectronics and Solid-StateElectronicsAffiliation:Shenzhen Graduate SchoolDate of Defence:December, 2011Degree-Conferring-Institution:Harbin Institute of Technology哈尔滨工业大学工学硕士学位论文摘要随着集成电路设计复杂度的提高和产品上市时间压力的增大,基于IP核复用的SoC(System on Chip)设计已经成为一种重要的设计方法。

总线桥的设计和IP核的互连问题已经成为SoC平台中最重要的课题。

IP核互连的方法,总线桥的设计以及总线协议决定了SoC平台的性能。

AMBA(Advanced Microcontroller Bus Architecture)总线规范由ARM公司定义。

IP可重用的AMBA+AXI总线验证平台设计与实现

万方数据 万方数据 万方数据 万方数据IP可重用的AMBA AXI总线验证平台设计与实现作者:侯秋菊, 沈海华, HOU Qiu-ju, SHEN Hai-hua作者单位:中国科学院计算技术研究所,北京,100080刊名:计算机工程与设计英文刊名:COMPUTER ENGINEERING AND DESIGN年,卷(期):2008,29(7)被引用次数:4次参考文献(8条)1.Zhang Li-yuan The analysis and comparison of three SoC onchip buses[期刊论文]-Journal of Shandong University of Science and Technology(Natural Science) 2005(02)2.ARM Corp The AMBA specification Rev23.Srikanth Vijayaraghavan.Meyyappan Ramanathan System Verilog Assertions应用指南 20064.Haihua Shen.Lin Ma.Heng Zhang CRPG:A configurable random test program generator for microprocessors[外文会议] 20055.Hu weiwu.Zhang fuxin.Li zusong Micro architecture of the Godson-2 processor[期刊论文]-Journal of Computer Science and Technology 2005(02)6.Yue Huawei.Xu Yongjun.Zhang Zhimin A Simulation_Based method for SoC bus system[期刊论文]-Journal of Computer-Aided Design & Computer Graphics 2005(10)7.Sigal Asaf.Eitan Marcus.Avi Ziv Defining coverage views to improve functional coverage analysis[外文会议] 20048.张珩.沈海华龙芯2号微处理器的功能验证[期刊论文]-计算机研究与发展 2006(06)本文读者也读过(7条)1.Mick Posner.Fred Roberts充分发挥AMBA 3 AXI协议的性能优势[期刊论文]-电子元器件资讯2010(5)2.蒋周良.权进国.林孝康.Jiang,Zhouliang.Quan,Jin-guo.Lin,Xiaokang AMBA总线新一代标准AXI分析和应用[期刊论文]-微计算机信息2006,22(29)3.曹阳.郑文杰.李晓辉.王立伟.马秦生AMBA 3.0 AXI总线接口协议的研究与应用[会议论文]-20064.Mick Posner快速实现基于AMBA 3AXI协议的设计[期刊论文]-电子设计应用2007(1)5.仇培铭家庭网络核心SoC平台——基于AMBA的SoC通信架构研究[学位论文]20056.张珩.辜帆VMM验证方法在AXI总线系统中的实现——Verification IP应用一例[期刊论文]-中国集成电路2007,16(6)7.郭叙海多片大规模FPGA的ASIC原型验证平台快速设计方法[期刊论文]-中国集成电路2010,19(12)引证文献(4条)1.王凯.张建国基于System Verilog和MATLAB参考模型的WLAN基带功能验证[期刊论文]-微电子学与计算机2009(11)2.梁璞.王新安基于VMM实现的网络接口验证[期刊论文]-现代电子技术 2010(15)3.黄思远.邵智勇.于承兴.常华.张波VMM中功能覆盖率收敛技术[期刊论文]-现代电子技术 2010(4)4.谢立新基于重构原理的电路可扩展性设计[期刊论文]-柳州职业技术学院学报 2011(2)本文链接:/Periodical_jsjgcysj200807040.aspx。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硕士学位论文AMBA AXI4总线的研究与实现RESEARCH AND IMPLEMENTATION OF AMBA AXI4 BUS杨舜琪哈尔滨工业大学2011年12月国内图书分类号:TN47 学校代码:10213 国际图书分类号:621.3 密级:公开工学硕士学位论文AMBA AXI4总线的研究与实现硕士研究生 :杨舜琪导 师 :张岩教授申请学位 :工学硕士学科 :微电子学与固体电子学所在单位 :深圳研究生院答辩日期 :2011年12月授予学位单位 :哈尔滨工业大学Classified Index: TN47U.D.C: 621.3Dissertation for the Master Degree in EngineeringRESEARCH AND IMPLEMENTATIONOF AMBA AXI4 BUSCandidate:Shunqi YANGSupervisor:Prof. Yan ZHANGAcademic Degree Applied for:Master of Engineering Speciality:Microelectronics and Solid-StateElectronicsAffiliation:Shenzhen Graduate SchoolDate of Defence:December, 2011Degree-Conferring-Institution:Harbin Institute of Technology哈尔滨工业大学工学硕士学位论文摘要随着集成电路设计复杂度的提高和产品上市时间压力的增大,基于IP核复用的SoC(System on Chip)设计已经成为一种重要的设计方法。

总线桥的设计和IP核的互连问题已经成为SoC平台中最重要的课题。

IP核互连的方法,总线桥的设计以及总线协议决定了SoC平台的性能。

AMBA(Advanced Microcontroller Bus Architecture)总线规范由ARM公司定义。

它是一组基于ARM核的SoC通信的标准协议。

最新的AMBA 4.0总线协议具有带宽高、延迟小和设计灵活等诸多优点,它目前已成为业界首选的高性能总线标准。

本文分析并比较了Wishbone总线标准与AMBA 4.0总线标准的异同。

根据AMBA 4.0总线标准中AXI4协议和AXI4-Lite协议,设计并实现了总线桥以及互连模块的VLSI结构。

本文研究内容主要包含以下三个部分:首先,为了扩充AXI4总线可使用的IP核资源,本文设计了基于Wishbone 总线和AXI4总线的总线桥IP核,包括把基于Wishbone总线的主设备集成到AXI4总线系统的WB/AXI4总线桥,把基于Wishbone总线的从设备集成到AXI4总线系统的AXI4/WB总线桥,把基于Wishbone总线的主设备集成到AXI4-Lite总线系统的WB/AXI4-Lite总线桥和把基于Wishbone总线的从设备集成到AXI4-Lite总线系统的AXI4-Lite/WB总线桥。

其次,本文设计了基于AXI4总线的两种互连结构,包括交叉开关(crossbar switch)和分享型总线(share bus)。

两种互连结构设计主要模块包括地址解码器和仲裁器。

最后,本文针对设计的总线桥和互连结构,使用Verilog HDL语言进行了硬件实现,在ModelSim环境下通过了功能验证,使用ISE13.1工具进行逻辑综合,分析比较了各IP核的性能。

从验证和综合来看,本文的IP设计严格遵循Wishbone总线和AMBA4.0总线的协议规范,WB/AXI4总线桥,AXI4/WB总线桥,WB/AXI4-Lite总线桥和AXI4-Lite/WB总线桥在Xilinx公司Virtex5的FPGA芯片上达到的时钟频率分别279MHz,346 MHz,442 MHz和427 MHz,AXI4总线的交叉开关互连结构在284MHz的工作频率下,拥有22.5Gbps的数据吞吐量,AXI4总线的分享型互连结构在342MHz的工作频率下,拥有6.7Gbps的数据吞吐量,说明各IP 核都具备高速的数据传输能力,完全可以胜任实际应用。

关键词:互连总线;AMBA AXI4总线;Wishbone总线;协议转换哈尔滨工业大学工学硕士学位论文AbstractWith the improvement of IC design complexity and market pressure, SoC (System on Chip) design based on IP core reuse has become an important design approach. Then, bus bridge design and interconnect IP cores have become the most important issue in SoC platform. Interconnect IP core, the design of the bus bridge and bus protocol determine the performance of SoC platform. AMBA (Advanced Microcontroller Bus Architecture) bus specification defined by ARM company is a set of ARM core-based SoC communication standard protocol. The latest AMBA 4.0 bus protocol with high bandwidth, low delay and design flexibility has become the choice of industry standard.This project analyzes and compares the Wishbone bus and AMBA 4.0 bus. According to AXI4 protocol and AXI4-Lite protocol of AMBA 4.0 bus standard, the VLSI architectures of bus bridges and interconnect modules were designed and implemented in this dissertation. This research mainly includes the following three parts:First, in order to expand the IP core resources for AXI4 bus, based on Wishbone bus and AXI4 bus, this dissertation designed bus bridge IP cores, including WB/AXI4 bus bridge designed to integrate master devices based on Wishbone bus into an AXI4 bus system, AXI4/WB bus bridge designed to integrate slave devices based on Wishbone bus into an AXI4 bus system, WB/AXI4-Lite bus bridge designed to integrate master devices based on Wishbone bus into an AXI4-Lite bus system, AXI4-Lite/WB bus bridge designed to integrate master devices based on AXI4-Lite bus into a Wishbone bus system.Secondly, this dissertation designed two interconnect structures on AXI4 bus, including cross-switch and share-bus. Both of interconnect structures contained the main modules with address decoder and arbiter.Finally, all designs of the bus bridge and interconnect architecture were implemented into hardware by Verilog HDL language in the ModelSim environment. The analysis and comparison for the performance of all IP cores was completed by logic synthesis tools--ISE13.1.Results proved that all of IP designs strictly following the AMBA4.0 bus protocol specification and the Wishbone bus protocol specification. WB/AXI4 bus bridge, AXI4/WB bus bridge, WB/AXI4-Lite bus bridge and AXI4-Lite/WB bus bridge reached the clock frequency of 279MHz, 346 MHz, 442 MHz and 427 MHz under Virtex5 FPGA of Xilinx, AXI4 bus crossbar interconnect structure reach data throughput of 22.5 Gbps at the operating frequency of 284MHz, AXI4 bus哈尔滨工业大学工学硕士学位论文shared-bus interconnect structure reach data throughput of 6.7Gbps at the operating frequency of 342MHz, indicating that the IP cores are equipped with high speed and performance data transmission capability, fully adopt for practical application.Keywords: Interconnect bus, AMBA AXI4, Wishbone, protocol exchange哈尔滨工业大学工学硕士学位论文目录摘要 (I)ABSTRACT (II)第1章绪论 (1)1.1 课题背景 (1)1.2 国内外相关技术发展历史和现状 (1)1.2.1 片上总线的发展 (1)1.2.2 AMBA4.0总线产生的背景 (2)1.2.3 AMBA4.0总线的发展趋势 (2)1.3 本课题研究的目的及意义 (2)1.4 本文的主要研究内容 (3)第2章AMBA4.0总线和Wishbone总线分析 (4)2.1 概述 (4)2.2 AXI4总线协议 (4)2.2.1 AXI4总线简介 (4)2.2.2 AXI4总线信号描述 (5)2.2.3 AXI4总线的特性 (6)2.2.4 AXI4-Lite总线简介 (9)2.3 Wishbone总线协议 (10)2.3.1 Wishbone总线简介 (10)2.3.2 Wishbone总线信号描述 (10)2.3.3 Wishbone总线的特性 (10)2.4 AMBA4.0总线和Wishbone总线分析 (11)2.5 本章小结 (12)第3章AXI4总线桥的设计和实现 (13)3.1 AXI4总线桥总体设计及功能划分 (13)3.1.1 AXI4总线桥总体设计 (13)3.1.2 AXI4总线桥功能划分 (13)3.2 WB/AXI4总线桥的设计和实现 (14)3.2.1 WB/AXI4总线桥的设计 (14)3.2.2 WB/AXI4 总线桥的实现 (17)3.3 AXI4/WB总线桥的设计和实现 (20)哈尔滨工业大学工学硕士学位论文3.3.1 AXI4/WB总线桥的设计 (20)3.3.2 AXI4/WB总线桥的实现 (24)3.3 WB/AXI4-Lite总线桥的设计和实现 (29)3.3.1 WB/AXI4-Lite总线桥的设计 (29)3.3.2 WB/AXI4-Lite总线桥的实现 (29)3.4 AXI4-Lite/WB总线桥的设计和实现 (31)3.4.1 AXI4-Lite/WB总线桥的设计 (31)3.4.2 AXI4-Lite/WB总线桥的实现 (32)3.5 本章小结 (33)第4章AXI4互连结构的设计和实现 (34)4.1 AXI4总线的互连结构 (34)4.2 AXI4总线交叉开关互连结构的设计和实现 (34)4.2.1 AXI4总线交叉开关互连结构的设计 (34)4.2.2 AXI4总线交叉开关互连结构的实现 (37)4.3 AXI4总线分享型互连结构的设计和实现 (40)4.3.1 AXI4总线分享型互连结构的设计 (40)4.3.2 AXI4总线分享型互连结构的实现 (41)4.4 本章小结 (43)第5章AXI4总线性能分析与FPGA测试 (44)5.1 AXI4总线桥的性能分析 (44)5.2 AXI4总线互连结构的性能分析 (45)5.3 AXI4-Lite SoC系统的FPGA仿真综合及实现 (46)5.4 本章小结 (50)结论 (51)参考文献 (52)攻读硕士学位期间发表的论文及其它成果 (55)哈尔滨工业大学学位论文原创性声明及使用授权说明 (56)致谢 (57)哈尔滨工业大学工学硕士学位论文第1章绪论1.1 课题背景集成电路(Integrated Circuit,IC)发展的开始阶段,电路工程师都直接在物理版图层完成设计,在一定程度上限制了IC产业的发展。