7总线与接口

数字ic中的总线、接口、协议相关书籍

数字ic中的总线、接口、协议相关书籍【引言】在数字集成电路(IC)领域,总线、接口和协议是三个关键概念。

为了帮助大家更好地理解这些概念,本文将介绍一些与之相关的书籍,并为大家提供阅读建议。

【数字IC中总线、接口、协议的基本概念】总线:数字IC中用于传输数据和控制信号的物理通道。

接口:连接两个不同设备或系统的部件,负责实现数据交换和控制。

协议:规定了设备之间通信的规则,包括数据格式、传输速率、时序等。

【相关书籍的分类与推荐】1.总线相关书籍- 《计算机体系结构:量化研究方法》(经典教材,讲述总线、接口、协议等相关内容)2.接口相关书籍- 《嵌入式系统接口设计与实现》(重点介绍嵌入式系统接口的设计与实现方法)3.协议相关书籍- 《计算机网络:自顶向下方法》(全面讲述计算机网络协议的的经典教材)【各书籍的内容概述及适用读者】1.《计算机体系结构:量化研究方法》- 内容概述:该书详细介绍了计算机体系结构的基本概念、设计方法和评估技术。

- 适用读者:本科生、研究生学习计算机体系结构的基本知识,以及对总线、接口、协议感兴趣的工程师。

2.《嵌入式系统接口设计与实现》- 内容概述:该书从实际应用出发,讲解了嵌入式系统接口的设计方法和实现技巧。

- 适用读者:嵌入式系统开发人员,以及对接口设计有一定兴趣的技术人员。

3.《计算机网络:自顶向下方法》- 内容概述:该书系统地介绍了计算机网络的基本原理、体系结构和协议技术。

- 适用读者:计算机网络初学者,以及对协议技术感兴趣的工程师和研究人员。

【总结与建议】了解数字IC中的总线、接口、协议对于工程师而言至关重要。

通过阅读以上书籍,您可以系统地学习这些概念的基本知识和应用技巧。

对于本科生和研究生来说,这些书籍是学习计算机系统和网络技术的好教材。

对于从事相关工作的工程师来说,这些书籍可以帮助您巩固基础知识,提高技术水平。

总之,阅读这些书籍将对您的学术和职业发展大有裨益。

总线形式接口电路原理图设计

• 总线接口概述 • 总线接口电路设计基础 • 总线接口电路原理图绘制 • 总线接口电路仿真与调试 • 总线接口电路优化与改进

01

总线接口概述

总线接口定义

总线接口是指计算机内部或设备之间 用于数据传输的连接方式,通过总线 接口可以实现设备之间的数据交换和 通信。

总线接口通常由一组标准化的信号线 组成,用于连接多个设备,实设备 之间的数据传输和控制。

感谢观看

方案设计

根据需求分析,设计电路 方案,包括元件选择、电

路结构等。

仿真测试

通过仿真软件对电路原理 图进行测试和验证,确保

电路功能正确。

样品制作与测试

制作电路板样品,进行实 际测试和验证,确保满足

设计要求。

电路设计工具介绍

EDA工具

Electronic Design Automation,如AutoCAD、 OrCAD等,用于绘制原理图和PCB图。

信号的准确性和稳定性。

未来发展方向

集成化与小型化

随着集成电路技术的发展,总线接口电路将进一步向集成化和小型 化方向发展。

低功耗设计

随着对节能环保需求的增加,低功耗设计将成为总线接口电路的重 要发展方向。

高速传输与高带宽

随着数据传输速率的不断提高,总线接口电路将向高速传输和高带宽 方向发展。

THANKS

合理使用模板

利用原理图模板提高设计效率,减少重复绘制的工作量。

原理图绘制实例

UART总线接口电路原理图

SPI总线接口电路原理图

I2C总线接口电路原理图

实例1

实例2

实例3

04

总线接口电路仿真与调试

仿真工具介绍

01

PCS7系统中的OS架构详解

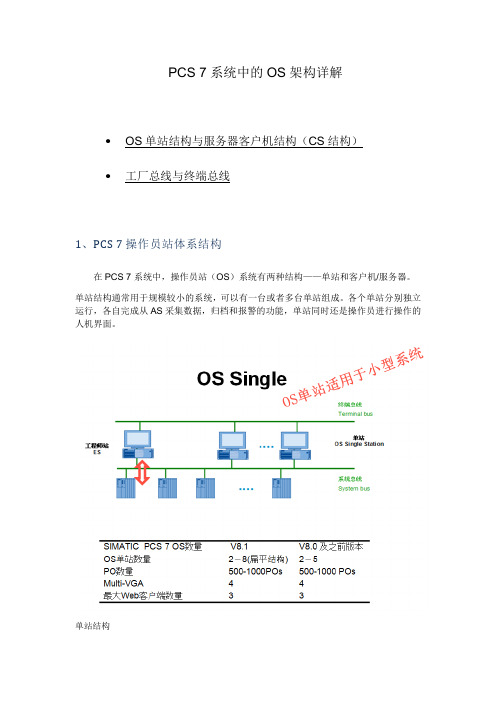

PCS 7系统中的OS架构详解•OS单站结构与服务器客户机结构(CS结构)•工厂总线与终端总线1、PCS 7 操作员站体系结构在PCS 7 系统中,操作员站(OS)系统有两种结构——单站和客户机/服务器。

单站结构通常用于规模较小的系统,可以有一台或者多台单站组成。

各个单站分别独立运行,各自完成从AS采集数据,归档和报警的功能,单站同时还是操作员进行操作的人机界面。

单站结构对于规模较大的系统,通常使用客户机/服务器结构。

在这种结构中有一个或者多个服务器负责AS数据采集,归档和报警信息的处理,从性能考虑,服务器一般不提供操作员界面。

由于服务器在整个OS体系中的关键地位,常常将OS服务器配置为冗余服务器。

在整个网络中,最多可以容纳18个(对)服务器,每个(对)服务器可以连接40个客户机(如果客户机使用多屏操作,则每一个屏幕算作一个客户机)。

在系统结构中,至少存在一个工程师站(ES)用于项目组态。

网络结构分为两层,分别是终端总线(Terminal Bus)和系统总线(System Bus)。

系统总线用于PC和控制器(AS)之间的通讯,例如,服务器和控制器之间的通讯以及ES和控制器之间的通讯;终端总线用于PC之间的通讯,例如,客户机和服务器之间的通讯以及工程师站和OS之间的通讯。

客户机/服务器结构大型PCS 7系统可以是两种OS结构的灵活混合。

除了过程生产的必备OS外,还可以通过附加选件配置PH中央归档服务器/BATCH服务器/MS维护站/RouteControl路径控制服务器等多种上位系统应用。

PCS 7系统是开放的过程系统,可以通过OPC、WEB方式提供上层网络的通讯接口。

PCS 7单站结构,客户机服务器结构以及冗余配置(方法本号内搜索)PCS 7项目结构数量一个多项目中最多允许的OS服务器、客户机数量SIMATIC PCS 7 OS数量 V8.1及之后V8.0 及之前版本最大服务器/服务器对数量18 12最大服务器PO数量12000 POs 8500 POs最大客户机数量40 32最大Web客户端数量100 50PCS 7 标准架构根据项目规模,PCS 7可以配置为单站、服务器/客户机模式,那么什么的项目规模时采用单站,什么时候采用服务器/客户机模式,分别需要购买哪些硬件和软件呢?(方法本号内搜索)PCS 7 最小配置对于中小型项目来说,总是期望PC站尽可能的少,那么ES作为OS站运行是否允许,有哪些要求和限制,如何一步步组态呢?(方法本号内搜索)PCS 7 扁平结构(Flat Structure)PCS 7 V8 之后,对于小规模项目,可以采用多个单站的扁平结构。

微机原理与接口技术(第二版)课后习题答案完整版

习题11.什么是汇编语言,汇编程序,和机器语言?答:机器语言是用二进制代码表示的计算机能直接识别和执行的一种机器指令的集合。

汇编语言是面向及其的程序设计语言。

在汇编语言中,用助记符代替操作码,用地址符号或标号代替地址码。

这种用符号代替机器语言的二进制码,就把机器语言编程了汇编语言。

使用汇编语言编写的程序,机器不能直接识别,要由一种程序将汇编语言翻译成机器语言,这种起翻译作用的程序叫汇编程序。

2.微型计算机系统有哪些特点?具有这些特点的根本原因是什么?答:微型计算机的特点:功能强,可靠性高,价格低廉,适应性强、系统设计灵活,周期短、见效快,体积小、重量轻、耗电省,维护方便。

这些特点是由于微型计算机广泛采用了集成度相当高的器件和部件,建立在微细加工工艺基础之上。

3.微型计算机系统由哪些功能部件组成?试说明“存储程序控制”的概念。

答:微型计算机系统的硬件主要由运算器、控制器、存储器、输入设备和输出设备组成。

“存储程序控制”的概念可简要地概括为以下几点:①计算机(指硬件)应由运算器、存储器、控制器和输入/输出设备五大基本部件组成。

②在计算机内部采用二进制来表示程序和数据。

③将编好的程序和原始数据事先存入存储器中,然后再启动计算机工作,使计算机在不需要人工干预的情况下,自动、高速的从存储器中取出指令加以执行,这就是存储程序的基本含义。

④五大部件以运算器为中心进行组织。

4.请说明微型计算机系统的工作过程。

答:微型计算机的基本工作过程是执行程序的过程,也就是CPU自动从程序存放的第1个存储单元起,逐步取出指令、分析指令,并根据指令规定的操作类型和操作对象,执行指令规定的相关操作。

如此重复,周而复始,直至执行完程序的所有指令,从而实现程序的基本功能。

5.试说明微处理器字长的意义。

答:微型机的字长是指由微处理器内部一次可以并行处理二进制代码的位数。

它决定着计算机内部寄存器、ALU和数据总线的位数,反映了一台计算机的计算精度,直接影响着机器的硬件规模和造价。

PCS7工厂总线与终端总线技术分析

PCS7 工厂总线与终端总线技术分析目录PCS 7 系统的网络结构 ..................................................................................................................1 组态工厂总线和终端总线 ............................................................................................................... 2 PCS 7 共用工厂总线和终端总线,有何限制? ............................................................................3 在 PCS 7 系统中共用工厂总线和终端总线,有何要求? .........................................................3 PCS 7 中实现工厂总线和终端总线的冗余配置 ............................................................................4 工厂总线与终端总线的冗余配置 ................................................................................................... 4 容错终端总线 ..................................................................................................................................5 容错工厂总线。

江苏开放大学计算机组成原理单元作业7

江苏开放大学计算机组成原理单元作业71早期微型机中,不常用的I/O信息交换方式是O客观题总分值:3分得分:3分A:程序查询方式B:中断方式C:DMA方式D:通道方式正确答案:D:2串行接口是指O客观题总分值:3分得分:3分A:接口与系统总线之间串行传送,接口与I/O设备之间串行传送B:接口与系统总线之间串行传送,接口与I/O设备之间并行传送C:接口与系统总线之间并行传送,接口与I/O设备之间串行传送D:接口与系统总线之间并行传送,接口与I/O设备之间并行传送正确答案:C:3中断向量可提供0客观题总分值:4分得分:4分A:被选中设备的地址B:传送数据的起始地址C:中断服务程序人口地址D:主程序的断点地址正确答案:C:4在中断系统中,CPU一旦响应中断,那么立即关闭标志,以防止本次中断响应过程被其他中断源产生另一次中断干扰。

客观题总分值:3分得分:3分A:中断允许B:中断请求C:中断屏蔽D:设备完成正确答案:C:5为了便于实现多级中断,保存现场信息最有效的方法是采用。

客观题总分值:3分得分:3分A:通用寄存器B:堆栈C:存储器D:外存正确答案:B:6CPU输出数据的速度远远高于打印机的打印速度,为解决这一矛盾,可采用客观题总分值:3分得分:3分A:并行技术B:通道技术C:缓冲技术D:虚存技术正确答案:C:7硬中断服务程序的末尾要安排一条指令IRET,它的作用是o客观题总分值:3分得分:3分A:构成中断结束命令B:转移到IRET的下一条指令U恢复断点信息并返回D:返回到断点处正确答案:C:8在采用DMA方式高速传输数据时,数据传送是o客观题总分值:4分得分:4分A:在总线控制器发出的控制信号控制下完成的B:在DMA控制器本身发出的控制信号控制下完成的C:由CPU执行的程序完成的D:由CPU响应硬中断处理完成的正确答案:B: 9采用DMA方式传送数据时,每传送一个数据就要占用一个时间。

客观题总分值:4分得分:4分A:指令周期B:机器周期C:存储周期D:总线周期正确答案:C:10周期挪用方式常用于方式的输入/输出中。

计算机组成原理(第4版)课件第7章 总线(第4版)

7.4 总线标准

总线的标准制定通常有两种途径,一 种是由具有权威性的国际标准化组织制定 并推荐使用的,称为正式标准;另一种是 由某个或某几个在业界具有影响力的设备 制造商提出,而又被业内其他厂家认可并 广泛使用的标准,即所谓事实标准,这些 标准可能需要经过一段时间的使用,被厂 商提供给有关组织讨论之后才能成为正式 标准。

8

2.总线事务

通常把在总线上一对设备之间的一次信

息交换过程称为一个“总线事务”,把发出

总线事务请求的部件称为主设备,与主设备

进行信息交换的对象称为从设备。例如CPU

要求读取存储器中某单元的数据,则CPU是

主设备,而存储器是从设备。总线事务类型

通常根据它的操作性质来定义,典型的总线

事务类型有“存储器读”、“存储器写”、

34

7.4.1 系统总线标准

通常,微机的系统总线都做成多个插 槽的形式,各插槽引脚通过总线连在一起。 总线接口引脚的定义、传输速率的设定、 驱动能力的限制、信号电平的规定、时序 的安排以及信息格式的约定等,都有统一 的标准。

35

7.4.1 系统总线标准(续)

1.PC/XT总线

PC/XT总线是早期PC/XT微机所配备 的系统总线,是9位总线标准。

5

7.1 总线概述

总线是一组能为多个部件分时共享的 公共信息传送线路。共享是指总线上可以 挂接多个部件,各个部件之间相互交换的 信息都可以通过这组公共线路传送;分时 是指同一时刻总线上只能传送一个部件发 送的信息。

6

7.1 .1 总线的基本概念

总线采用分时共享技术,当总线空闲 (所有部件都以高阻状态连接在总线上) 时,如果有一个部件要与目的部件通信, 则发起通信的部件驱动总线,发出地址和 数据。其他以高阻状态连接在总线上的部 件如果收到与自己相符的地址信息后,即 接收总线上的数据。发送部件完成通信后, 将总线让出(输出变为高阻态)。

第7讲现场总线设备

减压过程: 压电挡板上移控制室气压降 低提升阀上移,开度减小 输出气压减小

Beijing Institute of Technology

23

现场总线设备

现场总线设备

第 五 部 分 现场总线接口类设备

Beijing Institute of Technology

24

7.5.1 概述

用于将其它总线连接到现场总线系统

主要功能块:输出功能块、PID功能块等

Beijing Institute of Technology

22

7.4.3 现场总线-气压转换器FP302

现场总线设备

工作原理

增压过程: 控制电路使压电挡板靠近喷嘴 喷嘴背压增加控制室气压 增大提升阀芯下移提升阀 打开,气源提供的压缩空气流 入输出室输出气压增加

现场总线设备

Smar公司现场总线(FF)/以太网 (Ethernet)通用网桥: DFI302 Smar公司ISA现场总线(H1)接口卡:PCI302

Smar公司HART/FF 接口:HI302

Beijing Institute of Technology

25

7.5.2 Smar DFI302现场总线通用网桥

在同时传送交变信号和直流电源的总线上,为避免电源 在终端电阻上的能量消耗,应串连电容。

基金会现场总线终端器:

100欧

1uF

现场总线需两个终端器,分别设置在导线的最远端。为简化,可内置在 电源调整器内。

Beijing Institute of Technology

33

7.6.2 现场总线终端器(BT302)

若线路末端没有终端电阻,则Z2等于无穷,此时电压透 过系数为0,反射系数为1(全部反射),反射信号会引起很 大干扰;

ARM7TDMI总线接口

MAS[1:0] – 输出 : 存储器访问大小 指示字、半字或字节访问。

BL[3:0] – 输入 : 数据总线上的字节区段锁存使能 容许数据由小数构成。

存储器控制

MCLK

nMREQ SEQ

写入数据在相位1改变,保持稳定贯穿相位2。

nENOUT – 输出 (和 nENIN – 输入) : 数据总线控制 如果采用片外双向数据总线的话,可以用来控制数据总线的方向。

数据总线配置 (1)

ARM7TDM Macrocell

EmbeddedICE macrocell

32

32

bMDen

DoutlatEn

MCLK – 输入 处理器工作的时钟。 静态设计的ARM通过延长时钟周期来访问慢速的设备。

nWAIT – 输入 在ARM内部与MCLK相与。 必须在MCKL为低的相位阶段改变。 容许该信号从一个周期扩展到另一个周期,延长总线访问周期。

ECLK – 输出 核心逻辑的时钟的输出。 在正常和调试状态下反映内部时钟。

nMREQ, SEQ BIGEND nRW BL[3:0] MAS[1:0] LOCK

TBIT nTRANS nM[4:0] ABORT

Data and Address

Bus Control

Memory Access Control

Memory Management

Memory Interface

时钟与时钟控制

DIN[31:0]

D[31:0] DOUT[31:0]

G

数据总线配置 (2)

MCLK D[31:0] DIN[31:0] DOUT[31:0]

7-数据总线诊断接口J533

e.g. ECU A4 1.9 TDI = 66 Ohm

ECU

ABS

In Convenience and Infotainment CAN bus

it is not possible to measure terminal resistors ! 舒适、信息总线系统不能测量

Terminal Resistors

• 132 Tire pressure/ Steering column module/ Climate / Parking aid

• 133 Auxiliary heater/ Convertible top/ Trailer / Passenger seat memory

VW◆Service Training

经销商在销售给用户前, 必须用VAS5051的自诊 断功能来进行关闭运输 功能。

运输模式在里程数小于 150KM时,可以用网关 来进行切换,当高于此 值时,系统自动关闭运 输模式。

VW◆Service Training

网关

SAGITAR AB075

诊断插头的变化

VW◆Service Training

网口-网关

VW◆Service Training

网关

SAGITAR AB075

功能描述: 由于车控网络功能日益强大,需 要大量的数据信息在不同的数据 总线之进行有效的传递;网关可 以将不同的总线连接在一起,同 时使相互传递成为可能。

类型: •集成在组合仪表或汽车电气控制 单元内部 •单独的网关

VW◆Service Training

SAGITAR AB075

KWP200

整车电器网络

J220

J220

J533 J431

计算机原理职教(中专)版 第7章 系统总线

7.2 总线结构与接口

7.2.1 总线结构

1. 总线结构及连接方式

系统总线的实体是一组传送线,但实际上还包括了 一系列相关的逻辑,如总线控制权的申请、批准 与转移、总线状态信号产生、总线传送操作的时 序控制、读/写操作控制等。这些逻辑或在CPU 中,或设置专门的总线控制器。在现代计算机系 统中,各大部件均以系统总线为基础进行互连, 系统总线的结构有多种,按照连接方式的不同, 计算机系统中采用的总线结构有单总线结构和多 总线结构

3. 控制总线CB(ControI Bus)

控制总线是专供各种控制信号和状态 信息使用的传递通道,总线操作各项 功能都是由控制总线完成的。它主要 用于传送各类控制/状态信号,控制总 线信号是总线信号中种类最多、变化 最大、功能最强的信号,也是最能体 现总线特色的信号。

。

4. 电源线

许多总线标准中都包含了电源线的定义, 主要有十5V逻辑电源;6ND逻辑电源 地;一5V辅助电源;土12V辅助电源; AGND辅助地线。

准同步总线:采用同步异步相结合的方式。 既有同步总线控制简单的优点,又具有异 步总线时间利用率高的优点。

7.1.3系统总线的组成

系统总线由数据总线、地址总线、控制 总线和电源线组成。

1. 数据总线DB(Data Bus)

数据总线用于设备之间的数据传送,一 般为双向传送。数据总线的一个重要 指标是宽度,根据数据总线的宽度可 将系统总线分为8位总线、16位总线、 32位总线、64位总线等。

·并行总线 并行总线中的数据线有多根, 可同时传送多个二进制位,通常将数据总 线上可同时传送的二进制位数称为数据通 路宽度。系统总线一般是并行总线,其数 据通路宽度多与CPU一致,并为字节(8位) 的整数倍。

第7章总线技术1

• 1.

同步传输方式

• 该方式的数据传输在一个共同的时钟信号控制下进行, 时钟通常由时钟发生器/驱动器发出,经分频电路送到 总线上的所有模块。总线操作有固定的时序,所有信 号与时钟的关系在时序上是固定的,主控模块和受控 模块之间没有其它的应答、控制信号。

• 在同步方式中,为了保持可靠的数据传输,地址 信号、数据信号和有关读写命令信号相对于时钟 脉冲的前沿和后沿要有一定的建立时间和保持时 间。 • 总线同步通信方式在早期微机中有使用,如 MC6800的MPU。IBM PC/XT机因未用READY信号线 (该机中8088 CPU的READY输入信号线固定接高电 平)也被视为同步方式。 • 同步通信方式中系统的所有模块由单一时钟信号 控制,突出的优点是简单快速,缺点也很明显: 系统中快速模块必须迁就慢速模块,总线响应速 度由速度最慢的模块确定,使系统整体性能大为 降低。而且无法确知被访问的模块是否已经真正 响应,故可靠性亦较低。

7.4 总线类型

• ISA ISA(industrial standard architecture,工业标准架构)总线标准是 IBM公司1984年为推出PC/AT机而建立的系 统总线标准,所以也叫AT总线。它是对XT 总线的扩展,以适应8/16位数据总线要求。 它在80286至80486时代应用非常广泛,以 至于现在奔腾机中还保留有ISA总线插槽。 ISA总线有98只引脚。

• “请求”和“应答”信号都有一定的时间宽度, 根据它们的撤消是否互锁,异步方式又分为三种, 如下图所示。

不互锁:“请求”信号的结束和“应答”信号无关,两 信号的结束都由各自模块决定。 ◆半互锁:“请求”信号的撤消取决于“应答”信号的到 来,而“应答”信号的撤消由从模块自身决定。 ◆全互锁:“请求”信号的撤消取决于“应答”信号的到 来,而“应答”信号的撤消又必须等到“请求”信号撤消 全互锁方式互以对方联络信号的变化为前提来确保地址总 线和数据总线上的信息不会发生冲突,保证了传输的可靠 ,提 供 了很 大 的灵 活 性 , 当 然接 口 电路 也 相应 复 杂 。 MC68000系列微处理器就是全互锁异步传输方式的代表。 异步通信方式,两个模块的互锁控制信号要经过两个来回 传送,因此总线周期长,传输速度慢。

第 7 章 总线技术

总线技术

2013-12-5

1

©2012 第8版

本章学习内容

• • • • 总线的组成与结构 总线的设计与实现 总线与计算机系统 常见的总线

2013-12-5

2

7.1

总线概述

• 总线作为计算机传送信息的通道,是连接 各个功能部件的纽带。 • 总线由多条通信线路(或线缆)组成。 • 计算机系统中通常包含许多不同种类的总 线,它们在不同层次上为计算机组件之间 提供通信通路。

• 总线定时方式是指为了协调总线上发生 的事件所采用的方法。 • 总线上发生的事件是指那些为了使用总 线传输信息,总线所作的各种必要的动 作。 • 总线定时的方法分为同步定时和异步定 时,由此总线又可分为同步总线和异步 总线。

2013-12-5 40

⑴ 同步总线

• 在同步总线中,总线上所有事件的发生, 都要由一个时钟脉冲序列来定时。 • 在同步定时方式下,总线中包含一条时 钟信号线 ,所有的总线事件都应在一个 时钟周期的开始时(即高电平有效时) 启动动作。

2013-12-5

25

7.3

总线的设计与实现

总线的设计要素

总线宽度: 地址线宽度 数据线宽度

数据传输类型: 读 写 读—修改—写 写后读 块传输(连续数据传输)

26

• 7.3.1

信号线类型: 专用信号线 复用信号线

总线仲裁的方法: 集中仲裁 分布仲裁 总线定时方法: 同步 异步

2013-12-5

1. 信号线类型

2013-12-5 38

• 固定优先级策略的优点

• 硬件实现简单。

• 固定优先级策略的缺点

• 当设备较多时,优先级低的设备就很难有机会 使用总线。

7(6)航电总线数据处理软件设计

航电总线数据处理软件设计 Design of Data processing software for Avionic Bus'Data(中国飞行试验研究院,陕西 西安,710089)王建军 李筱雅 陈惠君摘 要:介绍了航电总线的组成及其结构特点,分析了其消息类型及数据格式,重点介绍了航电总线数据处理软件的设计方法,包括ICD文件的组织建立及程序设计方法。

关键字:航电总线;消息;ICD信息库Abstract:The composition and structure features of the avionic bus are introduced.The classes of the message and the formats of the data are analysed.The method for designing software to process the data from the avionic bus is discussed,including forming the ICD files and programming method.Key words:a vionic bus;message;interface control document database国军标数字式时分制指令/响应型多路传输数据总线(以下简称航电总线),从上个世纪70年代提出以来,经历了快速的应用和发展,目前作为一种国家军用标准,已经成为新一代飞机航空电子系统的重要组成部分。

随着航电总线技术在我国航空产品中的广泛应用,飞行试验中对航电总线数据进行采集和处理,已经成为新一代飞机试飞数据分析的重要内容之一,它对飞行试验测试系统也提出了新的要求。

德国HEIM公司生产的D40F多功能数据记录器是一种高性能的多数据流记录设备,可同时记录PCM数据流、航电总线数据和视频数据等多种格式的数据。

计算机总线发展历程

D

它的出现使得计算机与外部设备 的连接更加高效和灵活

Thunderbolt总线

总结:计算机总线的发展历程是一个不断追求高速、高 效、可靠和可扩展的过程。从早期的单线或双线方式到 现在的PCI-Express和Thunderbolt总线标准,每一次 变革都为计算机性能的提升和应用的拓展提供了有力的 支持。未来随着技术的不断进步和应用需求的不断变化, 计算机总线还将继续发展创新

这种总线采用了16位数据宽度,传输速率可达8.33MB/s

它还支持多达10个设备的并行连接,并且支持即插即用和热插拔功能

Chapter 3

PCI总线

PCI总线

为了提高数据传输速率 和可扩展性,

PCI(Peripheral Component

Interconnect)总线诞 生了

Step.01

它采用了32位数据宽度, 传输速率可达133MB/s

-

谢谢

Serial Bus)总线诞 生了

它采用了串行接口, 支持多个设备的连 接,并且支持即插

即用功能

USB总线还支持 高速数据传输, 传输速率可达

480MB/s

此外,USB总线还支

它的出现使得

持多个传输类型,如 控制传输、中断传输 和块传输等,满足了

外部设备的连 接变得更加方

不同类型设备的需求

便和可靠

Chapter 7

Chapter 1

早期总线

早期总线

在计算机发展的早期,各个 部件之间的连接并不紧密, 总线通常采用单线或双线方 式

这种总线方式传输速率低, 信号不稳定,无法满足高速 数据传输的需求

Chapter 2

ISA总线

ISA总线

随着计算机硬件的不断增多,为了更好地管理和控制计算机各个部件之 间的连接,出现了ISA(Industry Standard Architecture)总线

测控总线技术第七章7.

CRC序列是由发送器完成的CRC计算结果组成的。接收 器以与发送器相同的方法计算CRC。如果计算结果与接收到 的CRC序列不相同,则检出一个CRC错误。

➢形式错误(Form Error)

当固定形式的位场中出现一个或更多非法位时,则检出一 个形式错误。

➢应答错误(Acknowledgement Error)

I D

E

r 0

DLC

显 性

仲裁场

S

O F

11 位标识符

SI RD RE

18 位标识符

Rr

T R

1

数据场

控制场

r 0

DLC

数据场

隐 性

11位基本ID,18为扩展ID。IDE:ID extension。

SSR:替代远程请求substitute remote request,为隐性位。

控制场:

仲裁场 IDE/r1

计数规则 (12个规则):

➢接收器检出错误时,接收错误计数加1。 ➢接收器在送出错误标志后的第一位检出一个

“显性”位时,接收错误计数加8。

计数规则(续) :

➢ 发送器送出一个错误标志时,发送错误计数加8。有两 种例外情况,发送错误计数不改变。

一个是如果发送器为“错误认可”,因未检测到 “显性”应答而检测到一个应答错误,并且在送出其认 可错误标志时,未检测到“显性”位。

➢ 若沿处于SYNC-SEG之内,则e = 0 ➢ 若沿处于采样点之前,则e > 0 ➢ 若沿处于前一位采样点之后,e < 0

同步规则 (Synchronization Rules):

➢ ①在一个位时间内仅允许一种同步。

➢ ②只要在先前采样点上检测到的数值与一个沿过后立即 得到的总线数值不同,则该沿将被用于同步。

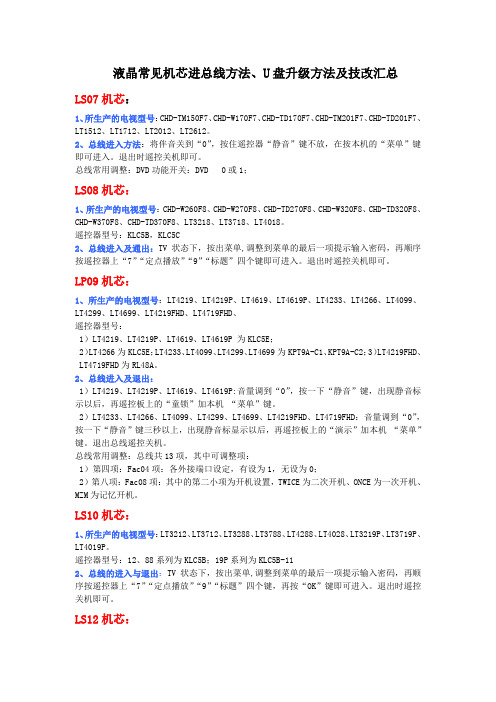

长虹液晶常见机芯进总线方法U盘升级方法及技改

液晶常见机芯进总线方法、U盘升级方法及技改汇总LS07机芯:1、所生产的电视型号:CHD-TM150F7、CHD-W170F7、CHD-TD170F7、CHD-TM201F7、CHD-TD201F7、LT1512、LT1712、LT2012、LT2612。

2、总线进入方法:将伴音关到“0”,按住遥控器“静音”键不放,在按本机的“菜单”键即可进入。

退出时遥控关机即可。

总线常用调整:DVD功能开关:DVD 0或1;LS08机芯:1、所生产的电视型号:CHD-W260F8、CHD-W270F8、CHD-TD270F8、CHD-W320F8、CHD-TD320F8、CHD-W370F8、CHD-TD370F8、LT3218、LT3718、LT4018。

遥控器型号:KLC5B,KLC5C2、总线进入及通出:TV状态下,按出菜单,调整到菜单的最后一项提示输入密码,再顺序按遥控器上“7”“定点播放”“9”“标题”四个键即可进入。

退出时遥控关机即可。

LP09机芯:1、所生产的电视型号:LT4219、LT4219P、LT4619、LT4619P、LT4233、LT4266、LT4099、LT4299、LT4699、LT4219FHD、LT4719FHD、遥控器型号:1)LT4219、LT4219P、LT4619、LT4619P 为KLC5E;2)LT4266为KLC5E;LT4233、LT4099、LT4299、LT4699为KPT9A-C1、KPT9A-C2;3)LT4219FHD、LT4719FHD为RL48A。

2、总线进入及退出:1)LT4219、LT4219P、LT4619、LT4619P:音量调到“0”,按一下“静音”键,出现静音标示以后,再遥控板上的“童锁”加本机“菜单”键。

2)LT4233、LT4266、LT4099、LT4299、LT4699、LT4219FHD、LT4719FHD:音量调到“0”,按一下“静音”键三秒以上,出现静音标显示以后,再遥控板上的“演示”加本机“菜单”键。

计算机接口与通信第9章 USB 通用串行总线

9.2

USB总线的体系结构 USB总线的体系结构

9.2.1 USB总线的物理接口 USB总线的物理接口 USB总线的物理传输介质由一根4线的电 USB总线的物理传输介质由一根4线的电 缆组成,如图9 所示。其中两条(VBus、 缆组成,如图9-1所示。其中两条(VBus、 GND)用于提供设备工作所需电源。VBus GND)用于提供设备工作所需电源。VBus 在源端的标称电压值为+5V,GND为其对 在源端的标称电压值为+5V,GND为其对 应地线。另两条(V+、V-)为绞线形式 应地线。另两条(V+、V 的信号传输线,90 的信号传输线,90 的阻抗。

9.2.3

USB的信号和编码 USB的信号和编码

USB数据收发器包含了发送数据所需的差 USB数据收发器包含了发送数据所需的差 模输出驱动器和接收数据用的差模输入接 收器。 USB输出信号时,差模输出驱动器向USB USB输出信号时,差模输出驱动器向USB 电缆传送USB信号。 电缆传送USB信号。 在信号的低输出状态,驱动器稳态输出值 必须小于0.3V,且要承担1.5K 必须小于0.3V,且要承担1.5K 的负载加到 3.6V电源的灌电流。 3.6V电源的灌电流。 在信号的高输出状态,驱动器稳态输出值 必须大于2.8V,且要承担15K 必须大于2.8V,且要承担15K 的负载到地 的拉电流。

带USB接口的PC(百万) USB接口的PC(百万)

800 700 600 500 400 300 200 100 0 1999 2000 2001 2002 2003 2004

带USB接口的外设(百万) USB接口的外设(百万)

600 500 400 300 200 100 0 1999 2000 2001 2002 2003 2004

《计算机组成原理》7-总线

PC CPU

接口 主存

外部设备

7.2.1 单总线结构

使用单总线在CPU和内存之间传数据 在单总线系统中,访存指令与输入/输出指令在形式上完全相同,区别仅在于地址 的数值。这就是说,对输入/输出设备的操作,完全和内存的操作方法一样来处理。 这样,当CPU把指令的地址字段送到总线上时,如果该地址字段对应的地址是主 存地址,则主存予以响应。此时,在CPU和主存之间将发生数据传送,而数据传 送的方向由指令的操作码决定,其过程如图所示。

7.1.2 总线的分类

计算机系统中使用的总线可分成3类。 1.片内总线 片内总线是芯片内部的总线,计算机系统中各部件内部传送信息的通路。例如运 算器内部寄存器与寄存器之间、寄存器与算逻运算单元(ALU)之间的传送通路, 通常称之为内部总线。 2.系统总线 计算机系统中个部件之间传送信息的通路。例如CPU与主存储器之间,CPU与I/O 接口之间传送信息的通路,通常称之为“系统总线”,由于这些部件通常都制作 在各个插件板上,故又叫作板级总线(在一块电路板上各芯片之间的连线)和板 间总线。

7.1.1存储器分类

3.总线特性 总线特性是指机械特性(尺寸、形状)、电气特性(传输方向和有效的电平范 围)、功能特性(每根传输线的功能)和时间特性(信号和时序的关系)。 4.总线的猝发传输方式 在一个总线周期内传输存储地址连续的多个数据字的总线传输方式叫作猝发传送。 5.总线上信息传输方式 在计算机中,总线上的信息传输一般有串行、并行、并串行、分时四种方式。

小结 总线的基本概念和分类

总线基本概念 总线的分类

7.2总线结构

01

单总线结构

02

多总线结构

7.2.1 单总线结构

在许多微小型计算机中,将CPU、主存和I/O设备连接在一条单一的系统总线上, 叫作单总线结构,如图所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

总线与接口部分

09-20.假设某系统总线在一个总线周期中并行传输4字节信息,一个总线周期占用2个时钟周期,总线时钟频率为10 MHz,则总线带宽是

A.10 MB/s B.20 MB/s C.40 MB/s D.80 MB/s

10-20.下列选项中的英文缩写均为总线标准的是

A.PCI、CRT、USB、EISA B.ISA、CPI、VESA、EISA

C.ISA、SCSI、RAM、MIPS D.ISA、EISA、PCI、PCI-Express

11-20.在系统总线的数据线上,不可能传输的是

A.指令B.操作数C.握手(应答)信号D.中断类型号

12-19.某同步总线的时钟频率为100MHz,宽度为32位,地址/数据线复用,每传输一个地址或数据占用一个时钟周期。

若该总线支持突发(猝发)传输方式,则一次“主存写”总线事务传输128位数据所需要的时间至少是()。

A.20ns

B.40ns

C.50ns

D.80ns

12-20. 下列关于USB总线特性的描述中,错误的是()。

A.可实现外设的即插即用和热插拔

B.可通过级联方式连接多台外设

C.是一种通信总线,可连接不同外设

D.同时可传输2位数据,数据传输率高

12-21.下列选项中,在I/O总线的数据线上传输的信息包括()。

Ⅰ、I/O接口中的命令字Ⅱ、I/O接口中的状态字Ⅲ、中断类型号

A. 仅Ⅰ、Ⅱ

B. 仅Ⅰ、Ⅲ

C. 仅Ⅱ、Ⅲ

D.Ⅰ、Ⅱ、Ⅲ

13-19、下列选项中,用于设备和设备控制器(I/O接口)之间互连的接口标准是

PCI B、USB C、AGP D、PCI-Express

14-19. 某同步总线采用数据线和地址线复用方式。

其中数据线有32根,总线时钟频率为66MHZ,每个时钟周期传送两次数据。

(上升沿和下降沿各传送一次数据)该总线的最大数据传输率是(总线带宽):()

A. 132MB/S

B. 264 MB/S

C.528 MB/S

D. 1056 MB/S

14- 20.一次总线事务中,主设备只需给出一个首地址,从设备就能从首地址开始的若干连续单元中读出或写入多个数,这种总线事务方式称为()

A. 并行传输

B.串行传输

C.突发传输

D.同步传输

14-21.下列有关I/O借口的叙述中错误的是:

A.状态端口和控制端口可以合用同一寄存器

B. I/O接口中CPU可访问寄存器,称为I/O端口

C.采用独立编址方式时,I/O端口地址和主存地址可能相同

D.采用统一编址方式时,CPU不能用访存指令访问I/O端口

15-19.下列有关总线定时的叙述中,错误的是()

A.异步通信方式中,全互锁协议最慢

B.异步通信方式中,非互锁协议的可靠性最差

C.同步通信方式中,同步时钟信号可由多设备提供

D.半同步通信方式中,握手信号的采样由同步时钟控制

15-21.在采用中断I/O方式控制打印输出的情况下,CPU和打印控制接口中的I/O端口之间交换的信息不可能是( )

A.打印字符B.主存地址C.设备状态D.控制命令

13-43. (9分)某32位计算机,CPU主频为800 MHz,Cache命中时的CPI为4,Cache块大小为32字节;主存采用8体交叉存储方式,每个体的存储字长为32位、存储周期为40ns;存储器总线宽度为32位,总线时钟频率为200 Mhz,支持突发传送总线事务。

每次读突发传送总线事务的过程包括:送首地址和命令、存储器准备数据、传送数据。

每次突发传送32字节,传送地址或32位数据均需要一个总线时钟周期。

请回答下列问题,要求给出理由或计算过程。

(1)CPU和总线时钟周期各为多少?总线带宽(即最大数据传输率)为多少?

(2)Cache缺失时,需要用几个读突发传送总线事务来完成一个主存块的读取?

(3)存储器总线完成一次读突发传送总线事务所需的时间是多少?

(4)若程序BP执行过程中,共执行了100条指令,平均每条指令需进行1.2次访存,Cache 缺失率为5%,不考虑替换等开销,则BP的CPU执行时间是多少?

09-20[答案] B。

[解析] 1、总线的带宽等于总线周期的频率×每个总线周期传送的信息数量。

按题意,(10×106 /2)×4 = 20×106 (MB/s)。

10-20[答案] D

[解析] CRT、CPI、RAM、MIPS都与总线标准无关。

11-20参考答案:C。

【解析】:一般而言,系统总线采用同步方式传输,握手信号属于控制信号,不在数据总线上传输。

12-19参考答案C。

首先需要求出总线带宽。

针对此题,总线工作频率=总线时钟频率/1=100MHz。

故总线带宽=总线工作频率×总线宽度/8 = 400MB/s。

一次“主存写”总线事务传输128位数据所需要的时间为16B/(400MB/s)=40ns。

突发传输方式还需要一次地址传输,时间为一个时钟周期,即1/100MHz=10ns。

故总时间为40ns +10ns =50ns。

12-20:D。

USB总线是串行总线,即一位位的传输,不可能同时传输2位数据。

12-21:D。

在程序查询方式中,向I/O接口发出的命令字和从I/O接口取回的状态字,以及中断方式中的中断类型号(确定相应的终端向量)都是通过I/O总线传输的。

13-19: B

14-19:C

14-20 C

14-21 D

15-19.B

15-21.A

13-43. 答案:

(1) CPU的时钟周期为:1/800MHz=1.25ns。

(1分)

总线的时钟周期为:1/200MHz=5ns。

(1分)

总显的带宽为:4B×200MHz=800MB/s 或4B/5ns=800MB/s。

(1分)

(2) Cache块大小是32B,因此Cache缺失时需要一个读突发传送总线事务读取一个主存块。

(1分)

(3) 一次读突发传送总线事务包括一次地址传送和32B 数据传送:用一个总线时钟周期传输地址;每隔40n/s=5ns 启动一个体工作(各进行1次存取),第一个体读数花费40ns,之后数据存取与数据传输重叠:用8个总线时钟周期传输数据。

读突发传送总线事务时间:5ns+40ns+8×5ns=85ns。

(2分)

(4) BP的CPU执行时间包括Cache命中时的指令执行时间和Cache缺失时带来的额外开销。

命中时的指令执行时间:100×4×1.25ns=500ns。

(1分)指令执行过程中Cache缺失时的额外开销:1.2×100×%5×85ns=510ns。

BP的CPU执行时间:500ns+510ns=1010ns。

(2分)【评分说明】

执行时间采用如下公式计算时,可酌情给分。

执行时间=指令条数×CPI×时钟周期×命中率+访存次数×缺失率×缺失损失

计算公式正确但运算结果不正确时,可酌情给分。