CPU状态和控制寄存器

DSP芯片技术及应用

DSP总结:以下总结仅针对宁波大学DSP芯片技术及应用(通信类非控制类)这门课,个人根据重点、考点总结的,用于期末复习(请结合课本以及PPT的例子),不足之处请见谅,基本能过就是,如若其中有错请联系QQ:493288964。

还是建议您平时学点,理解为先!!!将该文章用于百度等兑换积分的行为是可耻的!第一章绪论(简介)1、DSP芯片特点:采用哈佛结构;多总线结构;流水线技术;专用的硬件乘法器;特殊的DSP指令;快速的指令周期;硬件配置强;支持多处理器结构1)CPU是冯.诺伊曼结构;DSP是数据和地址空间分开的哈佛结构。

冯.诺依曼结构:单存储空间;统一的程序和数据空间;共享的程序和数据总线;程序指令只能串行执行单指令周期:100ns,现在单指令周期为:10ns哈佛结构:双存储空间;程序存储器和数据存储器分开;程序总线和数据总线分开;独立编址、独立访问改进型哈佛结构:双存储空间、多条总线;多条数据总线;高速缓冲器(重复指令,只需读入一次)2)采用多总线结构:TMS320C54X:4组总线;单机器周期内可完成的操作;3)流水线操作4)专用的硬件乘法器硬件乘法累加器是DSP区别于通用微处理器的一个重要标志MAC(乘累加)单元(独立的乘法器和加法器;单周期内完成一次乘法和一次加法运算;MPY,MAC,MACA, MACSU等指令)分类:工作时钟和指令类型:静态和一致性DSP芯片;用途分:通用和专用型;数据格式分:定点和浮点型2、DSP按数据格式分为定点型和浮点型定点DSP芯片:数据长度16位/24位TMS320C2000/5000/6000价格便宜、功耗较低、但运算精度稍低。

浮点DSP芯片:数据长度32位/40位MS320C3X/4X/VC33/C67X/C8X价格稍贵、功耗较大、但运算精度高。

3、芯片简介TMS320VC5416PGE160 主处理器芯片的性能:频率:160MHz 速度:160MIPS 周期:6.25ns第二章:TMS320C54X的硬件结构1、C54X:为低功耗,高性能而专门设计的16位定点DSP芯片C54基本结构:中央处理器(CPU)、内部总线结构、存储器、片内外设。

计算机cpu是什么

计算机cpu是什么CPU作为电脑的核心组成部份,它的好坏直接影响到电脑的性能。

下面是店铺带来的关于计算机cpu是什么的内容,欢迎阅读!计算机cpu是什么:cpu又称处理器CPU包括运算逻辑部件、寄存器部件和控制部件。

CPU从存储器或高速缓冲存储器中取出指令,放入指令寄存器,并对指令译码。

它把指令分解成一系列的微操作,然后发出各种控制命令,执行微操作系列,从而完成一条指令的执行。

指令是计算机规定执行操作的类型和操作数的基本命令。

指令是由一个字节或者多个字节组成,其中包括操作码字段、一个或多个有关操作数地址的字段以及一些表征机器状态的状态字和特征码。

有的指令中也直接包含操作数本身。

运算逻辑部件运算逻辑部件,可以执行定点或浮点的算术运算操作、移位操作以及逻辑操作,也可执行地址的运算和转换。

寄存器部件寄存器部件,包括通用寄存器、专用寄存器和控制寄存器。

32位CPU的寄存器通用寄存器又可分定点数和浮点数两类,它们用来保存指令中的寄存器操作数和操作结果。

通用寄存器是中央处理器的重要组成部分,大多数指令都要访问到通用寄存器。

通用寄存器的宽度决定计算机内部的数据通路宽度,其端口数目往往可影响内部操作的并行性。

专用寄存器是为了执行一些特殊操作所需用的寄存器。

控制寄存器通常用来指示机器执行的状态,或者保持某些指针,有处理状态寄存器、地址转换目录的基地址寄存器、特权状态寄存器、条件码寄存器、处理异常事故寄存器以及检错寄存器等。

有的时候,中央处理器中还有一些缓存,用来暂时存放一些数据指令,缓存越大,说明CPU的运算速度越快,目前市场上的中高端中央处理器都有2M左右的二级缓存。

控制部件控制部件,主要负责对指令译码,并且发出为完成每条指令所要执行的各个操作的控制信号。

其结构有两种:一种是以微存储为核心的微程序控制方式;一种是以逻辑硬布线结构为主的控制方式。

微存储中保持微码,每一个微码对应于一个最基本的微操作,又称微指令;各条指令是由不同序列的微码组成,这种微码序列构成微程序。

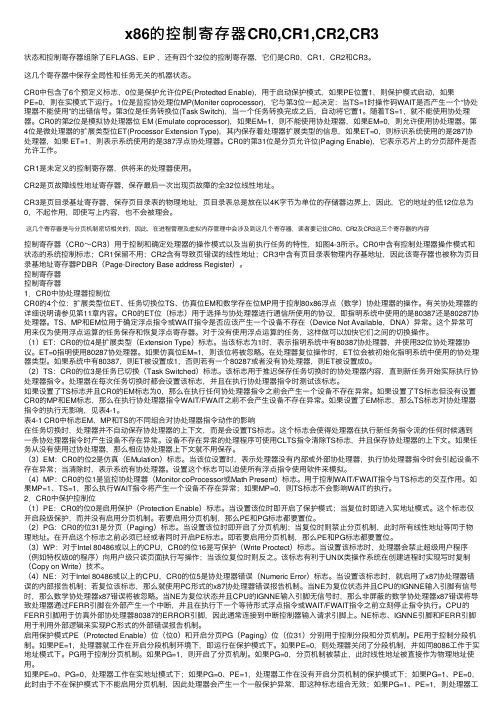

x86的控制寄存器CR0,CR1,CR2,CR3

x86的控制寄存器CR0,CR1,CR2,CR3状态和控制寄存器组除了EFLAGS、EIP ,还有四个32位的控制寄存器,它们是CR0,CR1,CR2和CR3。

这⼏个寄存器中保存全局性和任务⽆关的机器状态。

CR0中包含了6个预定义标志,0位是保护允许位PE(Protedted Enable),⽤于启动保护模式,如果PE位置1,则保护模式启动,如果PE=0,则在实模式下运⾏。

1位是监控协处理位MP(Moniter coprocessor),它与第3位⼀起决定:当TS=1时操作码WAIT是否产⽣⼀个“协处理器不能使⽤”的出错信号。

第3位是任务转换位(Task Switch),当⼀个任务转换完成之后,⾃动将它置1。

随着TS=1,就不能使⽤协处理器。

CR0的第2位是模拟协处理器位 EM (Emulate coprocessor),如果EM=1,则不能使⽤协处理器,如果EM=0,则允许使⽤协处理器。

第4位是微处理器的扩展类型位ET(Processor Extension Type),其内保存着处理器扩展类型的信息,如果ET=0,则标识系统使⽤的是287协处理器,如果 ET=1,则表⽰系统使⽤的是387浮点协处理器。

CR0的第31位是分页允许位(Paging Enable),它表⽰芯⽚上的分页部件是否允许⼯作。

CR1是未定义的控制寄存器,供将来的处理器使⽤。

CR2是页故障线性地址寄存器,保存最后⼀次出现页故障的全32位线性地址。

CR3是页⽬录基址寄存器,保存页⽬录表的物理地址,页⽬录表总是放在以4K字节为单位的存储器边界上,因此,它的地址的低12位总为0,不起作⽤,即使写上内容,也不会被理会。

这⼏个寄存器是与分页机制密切相关的,因此,在进程管理及虚拟内存管理中会涉及到这⼏个寄存器,读者要记住CR0、CR2及CR3这三个寄存器的内容控制寄存器(CR0~CR3)⽤于控制和确定处理器的操作模式以及当前执⾏任务的特性,如图4-3所⽰。

dsp复习重点电信

第二章1、DSP芯片内有3个CPU状态控制寄存器,用于表示工作状态和控制之用,分别说明是哪3个寄存器,并指出其中的状态位或者控制位。

ARP,DP,XF,INTM,IPTR,MP/MC,OVLY,DROM的作用。

’C54x提供三个16位寄存器来作为CPU状态和控制寄存器,它们分别为:状态寄存器0(ST0)状态寄存器1(ST1)工作方式状态寄存器(PMST) ST0和ST1主要包含各种工作条件和工作方式的状态;PMST包含存储器的设置状态和其他控制信息。

1.状态寄存器0(ST0)表示寻址方式和运行状态。

DP:数据存储器页指针。

用来与指令中提供的7位地址结合形成1个16位数据存储器的地址。

OVA/B:累加器A/B的溢出标志。

用来反映A/B是否产生溢出。

C:进位标志位。

用来保存ALU加减运算时所产生的进/借位。

TC:测试/控制标志。

用来保存ALU测试操作的结果。

ARP:辅助寄存器指针。

用来选择使用单操作数间接寻址时的辅助寄存器AR0~AR7。

2.状态寄存器1 (ST1)表示寻址要求、初始状态的设置、I/O及中断的控制等。

BRAF:块重复操作标志位。

用来指示当前是否在执行块重复操作。

BRAF=0 表示当前不进行重复块操作;BRAF=1 表示当前正在进行块重复操作。

CPL:直接寻址编辑方式标志位;用来指示直接寻址选用何种指针。

CPL=0 选用数据页指针DP的直接寻址;CPL=1 选用堆栈指针SP的直接寻址。

XF:外部XF引脚状态控制位。

用来控制XF通用外部输出引脚的状态。

执行SSBX XF=1 XF通用输出引脚为1;执行RSBX XF=0 XF通用输出引脚为0。

HM:保持方式位;响应HOLD信号时,指示CPU是否继续执行内部操作。

HM=0 CPU从内部程序存储器取指,继续执行内部操作。

HM=1 CPU停止内部操作。

INTM:中断总开关INTM=0 开放全部可屏蔽中断;INTM=1 禁止所有可屏蔽中断。

0:保留位,未被使用,总是读为0。

cpu基本组成部件

cpu基本组成部件

CPU(Central Processing Unit,中央处理器)是计算机系统的核心元件,用于进行数据处理和控制。

CPU基本组成部件包括:

1. 寄存器:用于存储临时的程序指令和数据。

它们是CPU直接控制和操作的存储单元,具有很高的数据访问速度。

2. 状态寄存器:记录系统状态的特殊寄存器,用来控制CPU运行状态,如正常运行状态,中断处理状态,异常处理状态等。

3. 控制器:用于管理和控制CPU的主要部件,包括指令控制器、数据传输控制器、地址控制器等。

4. 指令储存器:用于存放指令的存储器,由内存组成。

它将指令从内存调入CPU,以便进行操作。

5. 时钟电路:用于给处理器一个定时信号,以便控制指令的顺序和执行速度。

6. 运算器:用于完成数学运算和逻辑操作的部件,它负责完成各种处理指令要求的运算。

- 1 -。

CPU寄存器的功能和说明

CPU寄存器的功能和说明4个数据寄存器(EAX、EBX、ECX和EDX)2个变址和指针寄存器(ESI和EDI)2个指针寄存器(ESP和EBP)6个段寄存器(ES、CS、SS、DS、FS和GS)1个指令指针寄存器(EIP)1个标志寄存器(EFlags)1、数据寄存器数据寄存器主要⽤来保存操作数和运算结果等信息,从⽽节省读取操作数所需占⽤总线和访问存储器的时间。

32位CPU有4个32位的通⽤寄存器EAX、EBX、ECX和EDX。

对低16位数据的存取,不会影响⾼16位的数据。

这些低16位寄存器分别命名为:AX、BX、CX和DX,它和先前的CPU中的寄存器相⼀致。

4个16位寄存器⼜可分割成8个独⽴的8位寄存器(AX:AH-AL、BX:BH-BL、CX:CH-CL、DX:DH-DL),每个寄存器都有⾃⼰的名称,可独⽴存取。

程序员可利⽤数据寄存器的这种”可分可合”的特性,灵活地处理字/字节的信息。

寄存器AX和AL通常称为累加器(Accumulator),⽤累加器进⾏的操作可能需要更少时间。

累加器可⽤于乘、除、输⼊/输出等操作,它们的使⽤频率很⾼;寄存器BX称为基地址寄存器(Base Register)。

它可作为存储器指针来使⽤;寄存器CX称为计数寄存器(Count Register)。

在循环和字符串操作时,要⽤它来控制循环次数;在位操作中,当移多位时,要⽤CL来指明移位的位数;寄存器DX称为数据寄存器(Data Register)。

在进⾏乘、除运算时,它可作为默认的操作数参与运算,也可⽤于存放I/O的端⼝地址。

在16位CPU中,AX、BX、CX和DX不能作为基址和变址寄存器来存放存储单元的地址,但在32位CPU中,其32位寄存器EAX、EBX、ECX和EDX不仅可传送数据、暂存数据保存算术逻辑运算结果,⽽且也可作为指针寄存器,所以,这些32位寄存器更具有通⽤性。

2、变址寄存器32位CPU有2个32位通⽤寄存器ESI和EDI。

cpu中控制器的功能是

cpu中控制器的功能是CPU中控制器(Control Unit)是计算机中的重要组成部分,它承担着指挥和控制计算机各个部件协同工作的任务。

下面将详细介绍CPU中控制器的功能。

首先,CPU中控制器的主要功能是解释并执行存储在内存中的程序。

它通过从内存中读取指令,然后按照指令的要求运行或执行其他的操作。

它负责将指令转换为计算机可执行的微操作或机器码,并将其发送到相应的执行单元(如算术逻辑单元ALU)执行。

控制器根据指令的类型和操作码,确定下一步应该执行哪些操作。

其次,CPU中控制器还负责处理和解析指令中的地址和数据。

当CPU执行指令时,控制器从指令中解析出内存的地址,然后将其发送给内存单元,以获取所需要的数据或指令。

它还负责将数据从内存中读取到寄存器中,以供后续的操作使用。

此外,CPU中控制器还负责处理中断和异常。

中断是一种由外部事件触发的信号,用于打断CPU当前的执行过程,进行其他的任务。

例如,当有输入设备准备好向CPU发送数据时,控制器会接收到中断信号,并暂时中断当前任务,处理输入设备发送的数据。

同样,异常是指程序执行过程中出现的错误或非正常情况,例如除零错误或溢出错误。

控制器会根据异常的类型,采取相应的措施来处理异常,并保证程序的正常执行。

另外,CPU中控制器还负责协调和控制各个硬件组件的工作。

它发送时钟信号,以同步各个部件的操作,并调度和分配任务。

例如,当多个指令需要同时执行时,控制器会将它们分配给多个执行单元,并协调它们的执行顺序和完成时间。

最后,CPU中控制器还负责管理和维护CPU的状态寄存器和程序计数器(PC)。

状态寄存器用于保存CPU的当前状态,包括运行状态、异常状态、中断状态等。

程序计数器用于保存CPU当前执行的指令地址,控制器根据程序计数器的值来决定下一条指令的地址和执行顺序。

总结起来,CPU中控制器是计算机中的大脑,它负责指挥和控制计算机的各个部件,执行程序,处理中断和异常,协调各个部件的工作,并管理CPU的状态和程序计数器。

DSP原理及应用-(修订版)--课后习题答案

第一章:1、数字信号处理的实现方法一般有哪几种?答:数字信号处理的实现是用硬件软件或软硬结合的方法来实现各种算法。

(1) 在通用的计算机上用软件实现;(2) 在通用计算机系统中加上专用的加速处理机实现;(3) 用通用的单片机实现,这种方法可用于一些不太复杂的数字信号处理,如数字控制;(4)用通用的可编程 DSP 芯片实现。

与单片机相比,DSP 芯片具有更加适合于数字信号处理的软件和硬件资源,可用于复杂的数字信号处理算法;(5) 用专用的 DSP 芯片实现。

在一些特殊的场合,要求的信号处理速度极高,用通用 DSP 芯片很难实现( 6)用基于通用 dsp 核的asic 芯片实现。

2、简单的叙述一下 dsp 芯片的发展概况?答:第一阶段, DSP 的雏形阶段( 1980 年前后)。

代表产品: S2811。

主要用途:军事或航空航天部门。

第二阶段, DSP 的成熟阶段( 1990 年前后)。

代表产品: TI 公司的 TMS320C20主要用途:通信、计算机领域。

第三阶段, DSP 的完善阶段( 2000 年以后)。

代表产品:TI 公司的 TMS320C54 主要用途:各个行业领域。

3、可编程 dsp 芯片有哪些特点?答: 1、采用哈佛结构( 1)冯。

诺依曼结构,( 2)哈佛结构( 3)改进型哈佛结构2、采用多总线结构 3.采用流水线技术4、配有专用的硬件乘法-累加器5、具有特殊的 dsp 指令6、快速的指令周期7、硬件配置强8、支持多处理器结构9、省电管理和低功耗4、什么是哈佛结构和冯。

诺依曼结构?它们有什么区别?答:哈佛结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输,使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的执行速度,非常适合于实时的数字信号处理。

冯。

诺依曼结构:该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数据总线,取指令和取操作数都是通过一条总线分时进行。

DSP(知识点+思考题)

DSP复习要点第一章绪论1、数的定标:Qn表示。

例如:16进制数2000H=8192,用Q0表示16进制数2000H=0.25,用Q15表示2、‟C54x小数的表示方法:采用2的补码小数;.word 32768 *707/10003、定点算术运算:乘法:解决冗余符号位的办法是在程序中设定状态寄存器STl中的FRCT位为1,让相乘的结果自动左移1位。

第二章CPU结构和存储器设置一、思考题:1、C54x DSP的总线结构有哪些特点?答:TMS320C54x的结构是围绕8组16bit总线建立的。

(1)、一组程序总线(PB):传送从程序存储器的指令代码和立即数。

(2)、三组数据总线(CB,DB和EB):连接各种元器件,(3)、四组地址总线(PAB,CAB,DAB和EAB)传送执行指令所需要的地址。

2、C54x DSP的CPU包括哪些单元?答:'C54X 芯片的CPU包括:(1)、40bit的算术逻辑单元(2)、累加器A和B(3)、桶形移位寄存器(4)、乘法器/加法器单元(5)、比较选择和存储单元(6)、指数编码器(7)、CPU状态和控制寄存器(8)、寻址单元。

1)、累加器A和B分为三部分:保护位、高位字、地位字。

保护位保存多余高位,防止溢出。

2)、桶形移位寄存器:将输入数据进行0~31bits的左移(正值)和0~15bits的右移(负值)3)、乘法器/加法器单元:能够在一个周期内完成一次17*17bit的乘法和一次40位的加法4)、比较选择和存储单元:用维比特算法设计的进行加法/比较/选择运算。

5)、CPU状态和控制寄存器:状态寄存器ST0和ST1,由置位指令SSBX和复位指令RSBX控制、处理器模式状态寄存器PMST2-3、简述’C54x DSP的ST1,ST0,PMST的主要功能。

答:’C54x DSP的ST1,ST0,PMST的主要功能是用于设置和查看CPU的工作状态。

•ST0主要反映处理器的寻址要求和计算机的运行状态。

DSP原理及应用课程重点知识讲解

1、简述DSP系统的构成和工作过程。

答:DSP系统的构成:一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等。

DSP系统的工作过程:①将输入信号x(t)经过抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠。

②经过采样和A/D转换器,将滤波后的信号转换为数字信号x(n)。

③数字信号处理器对x(n)进行处理,得数字信号y(n)。

④经D/A转换器,将y(n)转换成模拟信号;⑤经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。

2、简述DSP系统的设计步骤。

答:①明确设计任务,确定设计目标。

②算法模拟,确定性能指令。

③选择DSP芯片和外围芯片。

④设计实时的DSP芯片系统。

⑤硬件和软件调试。

⑥系统集成和测试3、TMS320C54X芯片的基本结构都包括哪些部分?答:①中央处理器②内部总线结构③特殊功能寄存器④数据存储器RAM⑤程序存储器ROM⑥I/O口⑦串行口⑧主机接口HPI⑨定时器⑩中断系统4、TMS320C54X芯片的CPU主要由哪几部分组成?答:①40位的算术运算逻辑单元(ALU)。

②2个40位的累加器(ACCA、ACCB)。

③1 个运行-16至31位的桶形移位寄存器。

④17×17位的乘法器和40位加法器构成的乘法器-加法器单元(MAC)。

⑤比较、选择、存储单元(CSSU)。

⑥指令编码器。

⑦CPU状态和控制寄存器。

0、TMS320VC5402共有多少可屏蔽中断?它们分别是什么?RS和NMI属于哪一类中断源?答:TMS320VC5402有13个可屏蔽中断,RS和NMI属于外部硬件中断1.‘C54参数指令周期:即执行一条指令所需的时间,通常以ns(纳秒)为单位.MAC时间:即完成一次乘法-累加运算所需要的时间。

FFT执行时间:即运行一个N点FFT程序所需的时间MIPS:即每秒执行百万条指令;MOPS:即每秒执行百万次操作;MFLOPS:即每秒执行百万次浮点操作;BOPS:即每秒执行十亿次操作。

CPU状态和控制寄存器

• 1.状态寄存器0(ST0):主要反映处理器 .状态寄存器 ( ) 主要反映处理器 的寻址要求和计算机的运行状态。 的寻址要求和计算机的运行状态。

15 —13 12 11 10 9 8 —— 0

ST0: ARP :

TC TC

C

OVA

OVB

DP

DP:进位标志位。 的溢出标志。 DP:进位标志位。 。 。 数据存储器页指针 ARP:辅助寄存器指针。 ARP 测试/控制标志。 OVA/B:累加器A/B的溢出标志。 OVA/B:累加器A/B的溢出标志 C :数据存储器页指针。 TC::辅助寄存器指针。 TC:测试/控制标志 用来与指令中提供的7位地址结合形成1 用来与指令中提供的7位地址结合形成1个 用来选择使用单操作数间接寻址时的 用来保存ALU测试操作的结果 用来反映A/B是否产生溢出 测试操作的结果。 是否产生溢出。 用来保存ALU测试操作的结果。 用来反映A/B是否产生溢出 用来保存ALU加减运算时所产生的进 借位。 加减运算时所产生的进/ 用来保存ALU加减运算时所产生的进/借位。 16位数据存储器的地址 16位数据存储器的地址。 。 位数据存储器的地址。 辅助寄存器AR0~AR7 辅助寄存器AR0~AR7。

2.状态寄存器 (ST1):主要反映处理器的寻 . 状态寄存器1 主要反映处理器的寻 址要求、计算初始状态的设置、I/O及中断 址要求 、 计算初始状态的设置 、 I/O 及中断ቤተ መጻሕፍቲ ባይዱ的控制等。 的控制等。

15 14 13 XF 12 11 10 0 9 8 7 6 5 4~0 BRAF CPL HM INTM HM INTM OVM SXM C16 FRCT CMPT ASM C16 FRCT CMPT ASM

中 断 向 量 指 针

CPU的结构和功能

指令周期

资料仅供参考

程序的执行过程:

冯. 诺依曼 结构的计算机执行程序的顺序: 1. 正确从程序首地址开始. 2. 正确分步执行每一条指令,并形成下条待 执行指令的地址. 3.正确并自动地连续执行指令,直到程序的最 后一条指令.

指令周期

资料仅供参考

•指令的执行过程

—读取指令

指令地址送入主存地址寄存器

30 000 006

40 000 006

STA

00S0TA006

c

缓冲寄存器DR

数据总线DBUS

40

c

指令寄存器IR

指令周期

资料仅供参考

NOP指令和JMP指令的指令周期

NOP指令是一条空指令,包含两个CPU周期,第一个周 期取指令,第二个周期执行指令,因是空指令,所以操作 控制器不发出任何控制信号。

指令周期的基本概念

1. 指令周期:CPU每取出并执行一条指令,都要完成一系列 的操作,这一系列操作所需用的时间通常叫做一个指令 周期。

2. 机器周期:指令周期常常用若干个CPU周期数来表示, CPU周期也称为机器周期。

3. 时钟周期:由于CPU内部的操作速度较快,而CPU访问一 次内存所花的时间较长,因此通常用内存中读取一个指 令字的最短时间来规定CPU周期。而一个CPU周期时间又 包含有若干个时钟周期(通常称为节拍脉冲或T周期,它 是处理操作的最基本单位)。这些时钟周期的总和则规 定了一个CPU周期的时间宽度。

资料仅供参考

状态条件寄存器

程序记数器PC 000 02451 000000002241

地址寄存器AR

地址总线ABUS

算术逻辑单元

ALU

累加器AC 000 006

+1

第一章、系统DSP-CPU使用说明

第一章、开发系统使用说明本章主要对开发系统选用的DSP芯片及开发系统的硬件使用方法进行介绍,使用户对本产品有一个具体深入的了解。

1.1 DSP芯片简介本产品选用的是TI公司的TMS320C54X系列的DSP芯片,TMS320C5X是TI公司的第五代产品,是继TMS320C1X和TMS320C2X之后的第三代16位定点DSP处理器。

TMS320C5X的性能达到20~50MIPS,在典型应用中能耗降至2.35mA/MIPS。

它的核心中央处理器(CPU)以TMS320C25的核心CPU为基础,增强型结构大幅度地提高了整体性能。

TMS320C5X工作速度是TMS320C25的2倍以上,对于TMS320C1X和TMS320C2X具有源代码向下兼容特性。

这种兼容性保留了过去开发的软件,便于系统升级到更高性能的DSP系统。

TMS320C5X系列有TMS320C50/C51/C52/C53/C54等多种产品,它们的主要区别是片内RAM,ROM等资源的多少。

而其中TMS320C54X具有以下优点:●改进的哈佛结构。

围绕一组程序总线,三组数据总线和四组地址总线建立的哈佛结构,使得性能和多功能性都得以提高。

●具有高度并行性和专用硬件逻辑的CPU设计,使芯片性能大大提高。

●高度专业化指令集,更适用于快捷算法的实现和高级语言编程的优化。

●模块化结构的设计,使派生器件得到了更快的发展。

●最新的IC制造工艺,提高了芯片性能,降低了功耗。

●最新的静态设计技术使得芯片具有更低的功耗和更强的辐射能力。

这些使得C54X 特别适用于远程通信实时嵌入式应用的需要。

1.2 TMS320C54X的主要特性●多总线结构,三组16bit数据总线和一组程序总线。

●40bit算术逻辑单元(ALU),包括一个40bit桶形移位器和两个独立的40bit累加器。

●17×17bit并行乘法器,连接一个40bit的专用加法器,可用来进行非流水单周期乘/加(MAC)运算。

计算机组成原理第六章

指令周期的基本概念

节拍的宽度取决于CPU完成一次基本的微操作的时 间,如:ALU完成一次正确的运算,寄存器间的一 次数据传送等。

不同的指令,可能包含不同数目的机器周期。 一个机器周期中,包含若干个时钟周期(节拍脉冲

或T脉冲)。 CPU周期规定,不同的计算机中规定不同

2. 每条指令的指令周期不同

➢译码器经过对指令进行分析和解释,产生相应的控 制信号提供给时序控制信号形成部件。

机器周期、工作节拍、脉冲及启停控制线路

➢由脉冲源产生一定频率的脉冲信号作为整个机器的 时钟脉冲

时序控制信号形成部件

➢时序控制信号形成部件又称微操作信号发生器,真 正控制各部件工作的微操作信号是由指令部件提供 的操作信号、时序部件提供的时序信号、被控制功 能部件所反馈的状态及条件综合形成的。

2. 微操作:是微命令的操作过程。

– 微命令和微操作是一一对应的。 – 微命令是微操作的控制信号,微操作是微命令的操作过程。 – 微操作是执行部件中最基本的操作。

由于数据通路的结构关系,微操作可分为相容的和互斥:

1. 互斥的微操作,是指不能同时或不能在同一个节拍内并行执行的 微操作。可以编码

2. 相容的微操作,是指能够同时或在同一个节拍内并行执行的微操 作。必须各占一位

联合控制方式

– 大部分指令在固定的周期内完成,少数难以确定的操作采 用异步方式

– 机器周期的节拍脉冲固定,但是各指令的机器周期数不固 定(微程序控制器采用)

微程序控制原理

1. 微命令:控制部件向执行部件发出的各种控制命令叫作 微命令,它是构成控制序列的最小单位。

– 例如:打开或关闭某个控制门的电位信号、某个寄存器的打入脉 冲等。

读写时序信号的译码逻辑表达式

TMS320C54X_结构

一、 TMS320C54X的结构1,TMS320有定点、浮点和多处理器三种数字信号处理器,其中定点处理器有:C1X,C2X,C2XX,C5X,C55X ,C54X,C54XX;浮点处理器有:C3X,C4X,C67X;多处理器只有:C8X。

2,TMS320C54X内部硬件结构图3,TMS320C54X是16位定点处理器,采用改进的哈佛结构,降低了功耗,提高了并行性。

具有四组地址总线(PAB,CAB,DAB,EAB)、一组程序总线(PB)和三组数据总线(CB,DB,EB):A.程序和数据空间分开,提高并行性,一个周期里可完成两个读和一个写操作;B. 数据可以在程序和数据空间这间进行传送;C. 程序总线(PB)传送从程序存储器来的指令代码和立即数;三组数据总线连接各种元器件,CB和DB总线传送从数据存储器读出的操作数,EB总线传送写入到存储中的数据;D. PB总线能把存储在程序空间的数据操作数(如系数表)传到乘法器的和加法器中进行乘/累加运算;或者在数据移动指令(MVPD和READA)中传送到数据空间。

这种能力加上双操作数读的特性,支持单周期三操作数指令的执行,如FIRS指令。

4,各部件简介:A. 中央处理单元一个40位的算术逻辑单元(ALU)外加两个独立的40位累加器(ACC A和ACC B)和一个40位桶形移位器;一个17×17位并行乘法器连到一专用40位加法器(完成非流水线的单周期的乘/累加操作);比较/选择和存储单元(CSSU)(用于Viterbi操作的加/比较选择);指数编码器(在单周期内计算一个40位累加器值的指数);两个地址产生器,包括八个辅助寄存器和两个辅助寄存器算术单元;各种CPU寄存器(CPU寄存器是存储器映射的,能快速恢复和保存)。

B. 算术逻辑单元(ALU)用40位的算术逻辑单元(ALU)和两个40位的累加器(ACC A和ACC B)来完成二进制补码的算术运算。

ALU也能完成布尔运算。

TMS320C54X数字信号处理器的内部CPU的各个组成部分

TMS320C54X数字信号处理器的内部CPU的各个组成部分摘要:本文简单介绍了TMS320C54X数字信号处理器的内部CPU 的各个组成部分,使读者对其有一个初步的了解和认识。

关键词:总线结构算术逻辑运算单元桶形移位器比较、选择和存储单元引言TMS320C54X是TI公司于1996年推出的新一代定点数字信号处理器。

它采用先进的修正哈佛结构 ,片内共有8条总线(1条程序存储器总线,3条数据存储器总线和4 条地址总线) 、CPU、在片存储器和在片内围电路等硬件,加上高度专业化的指令系统,使TMS320C54X具有功耗小,高度并行等优点,可以满足电信等众多领域的高时处理的要求。

TMS320C54X- DSP 同其他类型的DSP一样,CPU 仍是其核心部分,高度并行和带有专用硬件逻辑是其所用DSP 的主要特点。

现简单介绍如下:a. 先进的多总线结构(1条程序总线、3条数据总线和4条地址总线) 。

b. 40位算术逻辑运算单元(ALU) ,包括1个40位桶形移位寄存器和2个独立的40 位累加器。

c. 17×17位并行乘法器,与40位专用加法器相连,用于非流水线式单周期乘法累加(MAC)运算。

d. 比较、选择、存储单元(CSSU) ,用于加法/ 比较选择。

e. 指数编码器,可以在单个周期内计算40 位累加器中数值的指数。

f . 双地址生成器,包括8 个辅助寄存器和2 个辅助寄存器算术运算单元(ARAU) 。

总线结构TMS320C54X片内有8条16位主总线:4条程序、数据总线和4条地址总线。

这些总线的功能如下:a. 程序总线(PB)传送取自程序存储器的指令代码和立即操作数。

b. 3条数据总线(CB、DB和EB)将内部个单元(如CPU、数据地址生成电路、程序地址生成电路、在片外围电路以及数据存储器)连接在一起。

CB和DB传送读自数据存储器的操作数。

EB传送写到存储器的数据。

c. 4个地址总线(PAB、CAB、DAB 和EAB)传送执行指令所需的地址由于其总线结构采用了增强型哈佛结构,分为程序、数据和地址三种总线方式,使得TMS320C54X 的CPU 有高速和并行执行指令的能力,大大提高了其运算速度和效率。

cpu的daif状态

cpu的daif状态CPU的DAIF状态是指CPU的中断控制器状态寄存器中的Disable Interrupt Acknowledge(DI)、Disable Interrupt(EI)、Disable Fault(FI)和Disable Abort(AI)四个标志位。

当这四个标志位全部置位时,CPU进入DAIF状态,即中断和异常被禁止。

在DAIF状态下,CPU会屏蔽掉所有的中断和异常,不会响应外部的中断请求和内部的异常触发。

这种状态的作用是保护关键代码的执行,确保其能够顺利完成,不会被中断打断。

在一些对实时性要求较高的系统中,需要使用DAIF状态来保证关键任务的执行效果。

DAIF状态的设置是通过修改中断控制寄存器中的相关标志位来实现的。

当需要屏蔽中断和异常时,将DI、EI、FI和AI标志位置位;当需要恢复中断和异常时,将这四个标志位清零即可。

这种灵活的设置方式可以根据实际需要对中断和异常进行控制。

在实际应用中,DAIF状态通常用于一些对实时性要求较高的关键任务。

例如,在一些实时控制系统中,需要保证控制任务的执行不被其他中断和异常打断,以保证系统的响应速度和稳定性。

在这种情况下,可以在关键任务执行前将CPU置于DAIF状态,以屏蔽掉其他中断和异常的干扰。

值得注意的是,虽然DAIF状态可以屏蔽中断和异常,但并不意味着完全消除了中断和异常的影响。

在DAIF状态下,中断和异常仍然会被触发,只是CPU不会响应它们。

当关键任务执行完成,需要恢复中断和异常时,CPU会根据中断和异常的优先级进行响应,确保系统的正常运行。

除了保护关键任务的执行,DAIF状态还可以在某些特殊情况下使用。

例如,在一些需要对系统进行全局调试或者测试的场景下,可以将CPU置于DAIF状态,以屏蔽掉所有的中断和异常,保证系统的稳定性和一致性。

这样,就可以更加准确地进行调试和测试工作,提高系统的可靠性和可调试性。

CPU的DAIF状态是一种用于屏蔽中断和异常的状态,可以在对实时性要求较高的关键任务执行时使用,也可以在系统调试和测试时使用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

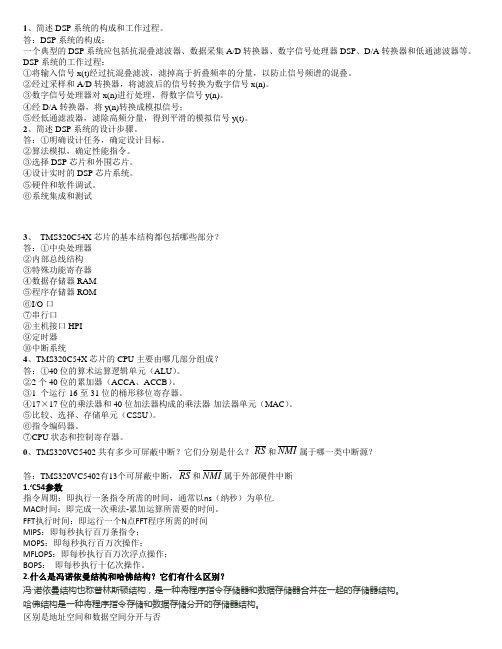

’C54x提供三个16位寄存器来作为CPU状态和 控制寄存器,它们分别为: 状态寄存器0(ST0) 状态寄存器1(ST1) 工作方式状态寄存器(PMST)

ST0和ST1主要包含各种工作条件和工作方式

的状态;

PMST包含存储器的设置状态和其他控制信息。

1.状态寄存器0(ST0)

CPL:直接寻址编辑方式标志位; 用来指示直接寻址选用何种指针。 CPL=0 选用数据页指针DP的直接寻址; CPL=1 选用堆栈指针SP的直接寻址。

INTM:中断方式控制位; 用于屏蔽或开放所有可屏蔽中断。 INTM=0 开放全部可屏蔽中断; INTM=1 禁止所有可屏蔽中断。 0:保留位,未被使用,总是读为0。

C16:双16位/双精度算术运算方式控制位; 用来决定ALU的算术运算方式。 C16=0 ALU工作在双精度算术运算方式; C16=1 ALU工作在双16位算术运算方式。

ASM:累加器移位方式控制位。 为某些具有移位操作的指令设定一个从16~15范围内的移位值。

15

14

13 XF

12

11

10 0

9

3.工作方式状态寄存器PMST

主要设定和控制处理器的工作方式和存储器的 配置,反映处理器的工作状态。

15~7 IPTR 6 5 4 AVIS 3 2 1 0 SST

MP/MC OVLY

DROM CLKOFF SMUL

中 断 向 量 指 针

CPU 工 作 方 式 选 择 位

RAM 重 复 占 位 标 志

15 —13 12 11 10 9 8 —— 0

ST0: ARP

TC TC

C

OVA

OVB

DP

C:进位标志位。 用来保存ALU加减运算时所产生的进/借位。

DP:数据存储器页指针。 用来与指令中提供的7位地址结合形成1个 16位数据存储器的地址。

2.状态寄存器1(ST1)

主要反映处理器的寻址要求、计算初始状态的 设置、I/O及中断的控制等。

DROM:用来决定片内ROM是否可以映射到 数据存储空间; CLKOFF:用来决定时钟输出引脚CLKOUT 是否有信号输出; SMUL:用来决定乘法结果是否需要进行饱和 处理; SST:用来决定累加器中的数据在存储到存储 器之前,是否需要饱和处理。

TMS320VC5402存储器配置结构

地址 程序存储空间 地址 程序存储空间 地址

15 14 13 XF 12 11 10 0 9 8 7 6 5 4~0

BRAF CPL BRAF

Hห้องสมุดไป่ตู้ INTM HM INTM

OVM SXM C16 FRCT CMPT ASM C16 FRCT CMPT ASM

BRAF:块重复操作标志位。 用来指示当前是否在执行块重复操作。 BRAF=0 表示当前不进行重复块操作; BRAF=1 表示当前正在进行块重复操作。

8

7

6

5

4~0

BRAF CPL BRAF

HM INTM HM INTM

OVM SXM C16 FRCT CMPT ASM C16 FRCT CMPT ASM

CMPT:间接寻址辅助寄存器修正方式控制位;用来决定 ARP是否进行修正。 CMPT=0 CMPT=1 在进行间接寻址单操作数时,不修正ARP; 在进行间接寻址单操作数时,修正ARP。

FRCT:小数方式控制位; 用来确定乘法器的运算方式。 FRCT=1 乘法器的输出左移一位, 消除多余的符号位。

15

14

13 XF

12

11

10 0

9

8

7

6

5

4~0

BRAF CPL BRAF

HM INTM HM INTM

OVM SXM C16 FRCT CMPT ASM C16 FRCT CMPT ASM

地 址 可 见 控 制 位

数 据 ROM 映 射 选 择 位

时 钟 输 出 选 择 位

乘 法 饱 和 方 式 位

存 储 饱 和 位

IPTR:用来指示中断向量所驻留的128字程序 存储器的位置; MP/MC:用来确定是否允许使用片内程序存 储器ROM; OVLY:用来决定片内双寻址数据RAM是否映 射到程序空间; AVIS:用来决定是否可以从器件地址引脚线看 到内部程序空间地址线;

15 14 13 XF 12 11 10 0 9 8 7 6 5 4~0

BRAF CPL BRAF

HM INTM HM INTM

OVM SXM C16 FRCT CMPT ASM C16 FRCT CMPT ASM

HM:保持方式位;响应HOLD信号时,指示 CPU是否继续执行内部操作。 HM=0 CPU从内部程序存储器取指, 继续执行内部操作。 HM=1 CPU停止内部操作。

OVM SXM C16 FRCT CMPT ASM C16 FRCT CMPT ASM

OVM:溢出方式控制位;用来确定累加器溢出时,对累加 器的加载方式。 OVM=0 将运算的溢出结果直接加载到累加器中; OVM=1 当正溢出时,将007FFFFFFFH加载累加器; 当负溢出时,将FF80000000H加载累加器。

主要反映处理器的寻址要求和计算机的运行状态。

TC:测试/控制标志。 用来保存ALU测试操作的结果。

15 —13 12 11 10 9 8 —— 0

ST0: ARP

TC TC

C

OVA

OVB

DP

ARP:辅助寄存器指针。 用来选择使用单操作数间接寻址时的 辅助寄存器AR0~AR7。

OVA/B:累加器A/B的溢出标志。 用来反映A/B是否产生溢出。

XF:外部XF引脚状态控制位。 用来控制XF通用外部输出引脚的状态。 执行SSBX XF=1 XF通用输出引脚为1; 执行RSBX XF=0 XF通用输出引脚为0。

15 14 13 XF 12 11 10 0 9 8 7 6 5 4~0

BRAF CPL BRAF

HM INTM HM INTM

OVM SXM C16 FRCT CMPT ASM C16 FRCT CMPT ASM

FFFFH

FFFFH

DROM控制的 数据存储空间

SXM:符号位扩展方式控制位;用来确定数据 在运算之前是否需要符号位扩展。 SXM=0 数据进入ALU之前禁止符号位扩展; SXM=1 数据进入ALU之前进行符号位扩展。

15 14 13 XF 12 11 10 0 9 8 7 6 5 4~0

BRAF CPL BRAF

HM INTM HM INTM

0000H 0000H

数据存储空间

0000H OVLY=1 保留 (0页) OVLY=0 外部存储器 007FH 0080H OVLY=1 内部DARAM 3FFFH 4000H EFFFH F000H 内部ROM OVLY=0 外部存储器 外部存储器

0000H OVLY=1 保留 (0页) OVLY=0 外部存储器 007FH 0080H OVLY=1 内部DARAM 3FFFH 4000H OVLY=0 外部存储器

外部存储器

FEFFH FF00H

保留 FF7FH FF80H FFFFH 中断矢量表 (内部存储器) MP/MC=0 微计算机模式 FF7FH FF80H FFFFH 中断矢量表 (外部存储器) MP/MC=1 微处理器模式

存储器映像 005FH 存储器映像寄存器 寄存器 0060H 005FH 暂存寄存器 007FH 0060H 暂存器 0080H SPRAM 内部DARAM 007FH 0080H (16K×16位) 内部DARAM 3FFFH 3FFFH 4000H (16K×16位字) 4000H 外部存储器 外部存储器 EFFFH EFFFH F000H F000H DROM=0 外部ROM DROM=1 内部ROM DROM=1 内部ROM FEFFH DROM=0 外部存储器 FEFFH FF00H FF00H DROM=0 外部存储器 DROM=1 保留 DROM=0 外部存储器 DROM=1 保留