半导体物理学第七版(刘恩科朱秉升著)电子工业出版社课后答案

半导体物理学(刘恩科)第七版 完整课后题答案)

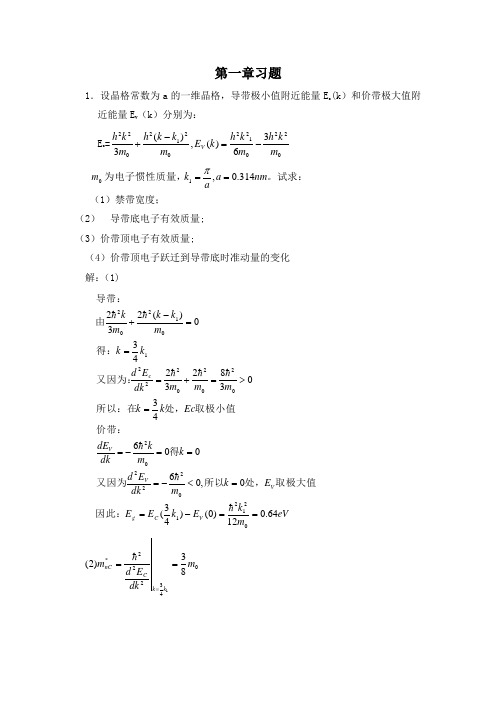

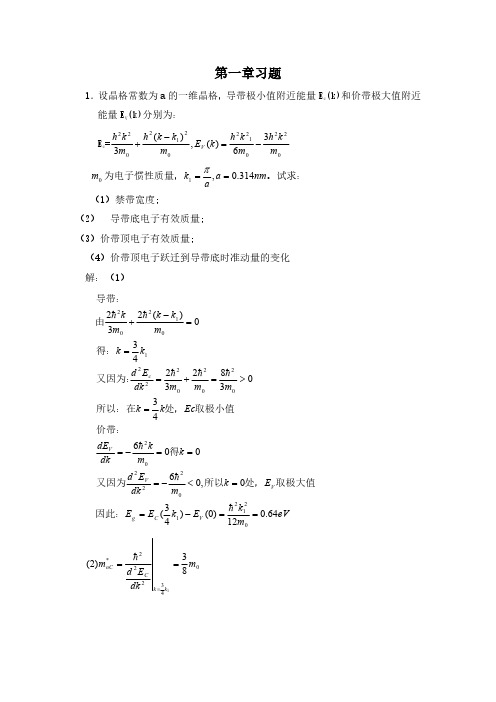

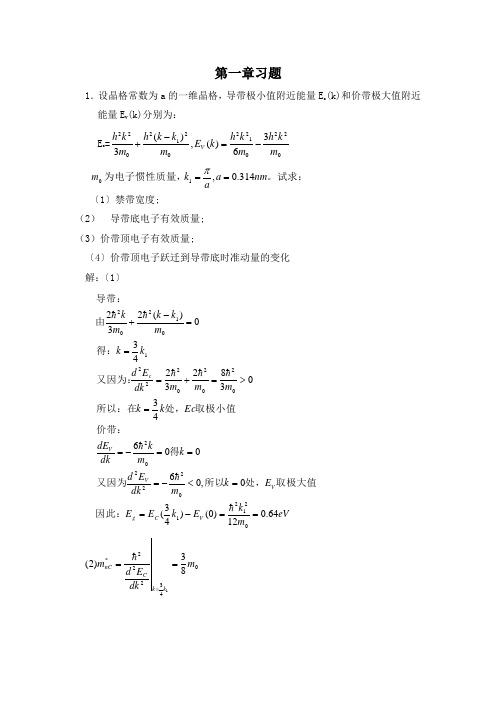

第一章习题1.设晶格常数为a 的一维晶格,导带极小值附近能量E c (k )和价带极大值附近能量E V (k )分别为:E c =0220122021202236)(,)(3m k h m k h k E m k k h m k h V -=-+ 0m 。

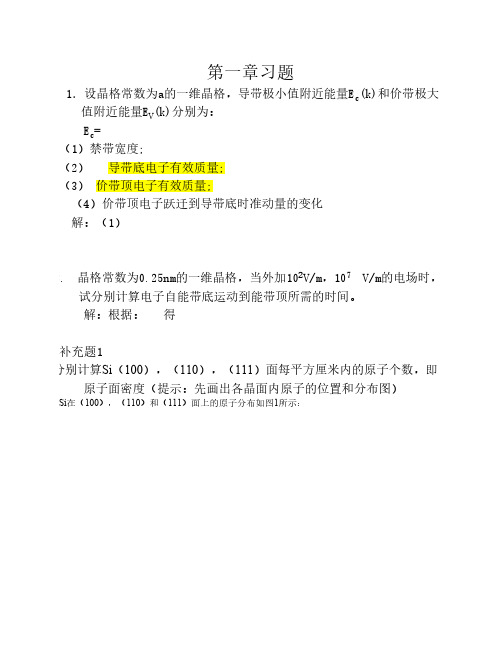

试求:为电子惯性质量,nm a ak 314.0,1==π(1)禁带宽度; (2) 导带底电子有效质量; (3)价带顶电子有效质量;(4)价带顶电子跃迁到导带底时准动量的变化 解:(1)eV m k E k E E E k m dk E d k m kdk dE Ec k k m m m dk E d k k m k k m k V C g V V V c 64.012)0()43(0,060064338232430)(2320212102220202020222101202==-==<-===-==>=+===-+ 因此:取极大值处,所以又因为得价带:取极小值处,所以:在又因为:得:由导带:043222*83)2(1m dk E d mk k C nC===sN k k k p k p m dk E d mk k k k V nV/1095.7043)()()4(6)3(25104300222*11-===⨯=-=-=∆=-== 所以:准动量的定义:2. 晶格常数为0。

25nm 的一维晶格,当外加102V/m ,107 V/m 的电场时,试分别计算电子自能带底运动到能带顶所需的时间。

解:根据:tkhqE f ∆∆== 得qE k t -∆=∆sat sat 137192821911027.810106.1)0(1027.810106.1)0(----⨯=⨯⨯--=∆⨯=⨯⨯--=∆ππ补充题1分别计算Si (100),(110),(111)面每平方厘米内的原子个数,即原子面密度(提示:先画出各晶面内原子的位置和分布图)Si 在(100),(110)和(111)面上的原子分布如图1所示:(a )(100)晶面 (b )(110)晶面(c )(111)晶面补充题2一维晶体的电子能带可写为)2cos 81cos 87()22ka ka ma k E +-= (, 式中a 为 晶格常数,试求(1)布里渊区边界; (2)能带宽度;(3)电子在波矢k 状态时的速度;(4)能带底部电子的有效质量*n m ;(5)能带顶部空穴的有效质量*p m解:(1)由0)(=dk k dE 得 an k π= (n=0,±1,±2…) 进一步分析an k π)12(+= ,E(k )有极大值,214221422142822/1083.7342232212414111/1059.92422124142110/1078.6)1043.5(224141100cm atom a a a cm atom a a a cm atom a a ⨯==⨯+⨯+⨯⨯==⨯⨯+⨯+⨯=⨯==⨯+-):():():(222)mak E MAX=( ank π2=时,E (k)有极小值所以布里渊区边界为an k π)12(+=(2)能带宽度为222)()ma k E k E MIN MAX =-( (3)电子在波矢k 状态的速度)2sin 41(sin 1ka ka ma dk dE v -== (4)电子的有效质量)2cos 21(cos 222*ka ka mdkEd m n-==能带底部 an k π2=所以m m n 2*= (5)能带顶部 an k π)12(+=, 且**n p m m -=,所以能带顶部空穴的有效质量32*mm p =半导体物理第2章习题1。

半导体物理学 刘恩科 第七版 完整课后题答案

第一章习题1.设晶格常数为a 的一维晶格,导带极小值附近能量E c (k)和价带极大值附近能量E V (k)分别为:E c =0220122021202236)(,)(3m k h m k h k E m k k h m k h V -=-+0m 。

试求:为电子惯性质量,nm a ak 314.0,1==(1)禁带宽度;(2)导带底电子有效质量;(3)价带顶电子有效质量;(4)价带顶电子跃迁到导带底时准动量的变化解:(1)eVm k E k E E E k m dk E d k m kdk dE Ec k k m m m dk E d k k m k k m k V C g V V V c 64.012)0()43(0,060064338232430)(2320212102220202020222101202==-==<-===-==>=+===-+ 因此:取极大值处,所以又因为得价带:取极小值处,所以:在又因为:得:由导带:043222*83)2(1m dk E d mk k C nC===sN k k k p k p m dk E d mk k k k V nV/1095.7043)()()4(6)3(25104300222*11-===⨯=-=-=∆=-== 所以:准动量的定义:2.晶格常数为0.25nm 的一维晶格,当外加102V/m,107V/m 的电场时,试分别计算电子自能带底运动到能带顶所需的时间。

解:根据:tk hqE f ∆∆==得qEk t -∆=∆ sat sat 137192821911027.810106.1)0(1027.810106.1)0(----⨯=⨯⨯--=∆⨯=⨯⨯--=∆ππ补充题1分别计算Si (100),(110),(111)面每平方厘米内的原子个数,即原子面密度(提示:先画出各晶面内原子的位置和分布图)Si 在(100),(110)和(111)面上的原子分布如图1所示:(a )(100)晶面(b )(110)晶面(c )(111)晶面补充题2一维晶体的电子能带可写为)2cos 81cos 87()22ka ka ma k E +-= (,式中a 为晶格常数,试求(1)布里渊区边界;(2)能带宽度;(3)电子在波矢k 状态时的速度;(4)能带底部电子的有效质量*n m ;(5)能带顶部空穴的有效质量*pm 解:(1)由0)(=dk k dE 得an k π=(n=0,±1,±2…)进一步分析an k π)12(+=,E(k)有极大值,214221422142822/1083.7342232212414111/1059.92422124142110/1078.6)1043.5(224141100cm atom a a a cm atom a a a cm atom a a ⨯==⨯+⨯+⨯⨯==⨯⨯+⨯+⨯=⨯==⨯+-):():():(222)ma k E MAX =(ank π2=时,E(k)有极小值所以布里渊区边界为an k π)12(+=(2)能带宽度为222)()ma k E k E MIN MAX =-((3)电子在波矢k 状态的速度)2sin 41(sin 1ka ka ma dk dE v -== (4)电子的有效质量)2cos 21(cos 222*ka ka mdkEd m n-== 能带底部an k π2=所以mm n 2*=(5)能带顶部an k π)12(+=,且**n p m m -=,所以能带顶部空穴的有效质量32*m m p =半导体物理第2章习题1.实际半导体与理想半导体间的主要区别是什么?答:(1)理想半导体:假设晶格原子严格按周期性排列并静止在格点位置上,实际半导体中原子不是静止的,而是在其平衡位置附近振动。

半导体物理学(刘恩科第七版)课后答案(完整版)-阳光大学生网

1000 3L3

欢迎光临阳光大学生网,提供最全面的大学生课后习题答案和复习试题免费下载,/

2. 试证明实际硅、锗中导带底附近状态密度公式为式(3-6) 。

2.证明:si、Ge 半导体的E(IC) ~ K关系为

2 2 h 2 k x k y k z2 E( EC ( ) C k) 2 mt ml ' 令k x ( 1 ma m 1 m 1 ' ) 2 kx , ky ( a ) 2 k y , k z' ( a ) 2 k z mt mt ml

2 8 mn l

1 Z0 V 4 (

Ec

100 h 2

2 8 mn l

EC * n

g ( E )dE

3 2

EC

2

4 (

1 * 3 2m n 2 2 ) ( E E ) dE C 2 h

2m ) h2

2 ( E EC ) 3

3

Ec Ec

100h 2 2 8mn L

欢迎光临阳光大学生网,提供最全面的大学生课后习题答案和复习试题免费下载,/

第三章习题

1. 计算能量在 E=Ec 到 E E C 解:

100h 2 之间单位体积中的量子态数。 2 8m * nL

1 * 3 2m n 2 g ( E ) 4 ( 2 ) ( E EC ) 2 V h dZ g ( E )dE dZ 单位体积内的量子态数Z 0 V Ec 100 h 2

所以布里渊区边界为 k ( 2n 1)

a 2 2 ma 2

(2)能带宽度为 E(k ) MAX E ( k ) MIN (3)电子在波矢 k 状态的速度 v (4)电子的有效质量

半导体物理学(刘恩科、朱秉升)第七版-最全课后题答案

第一章习题1.设晶格常数为a 的一维晶格,导带极小值附近能量E c (k)和价带极大值附近能量E V (k)分别为:E c =0220122021202236)(,)(3m k h m k h k E m k k h m k h V -=-+ 0m 。

试求:为电子惯性质量,nm a ak 314.0,1==π(1)禁带宽度;(2) 导带底电子有效质量; (3)价带顶电子有效质量;(4)价带顶电子跃迁到导带底时准动量的变化 解:(1)eV m k E k E E E k m dk E d k m kdk dE Ec k k m m m dk E d k k m k k m k V C g V V V c 64.012)0()43(0,060064338232430)(2320212102220202020222101202==-==<-===-==>=+===-+ 因此:取极大值处,所以又因为得价带:取极小值处,所以:在又因为:得:由导带:043222*83)2(1m dk E d mk k C nC===sN k k k p k p m dk E d mk k k k V nV/1095.7043)()()4(6)3(25104300222*11-===⨯=-=-=∆=-== 所以:准动量的定义:2. 晶格常数为0.25nm 的一维晶格,当外加102V/m ,107 V/m 的电场时,试分别计算电子自能带底运动到能带顶所需的时间。

解:根据:tkhqE f ∆∆== 得qE k t -∆=∆sat sat 137192821911027.810106.1)0(1027.810106.1)0(----⨯=⨯⨯--=∆⨯=⨯⨯--=∆ππ补充题1分别计算Si (100),(110),(111)面每平方厘米内的原子个数,即原子面密度(提示:先画出各晶面内原子的位置和分布图)Si 在(100),(110)和(111)面上的原子分布如图1所示:(a )(100)晶面 (b )(110)晶面(c )(111)晶面补充题2一维晶体的电子能带可写为)2cos 81cos 87()22ka ka ma k E +-=(, 式中a 为 晶格常数,试求(1)布里渊区边界; (2)能带宽度;(3)电子在波矢k 状态时的速度;(4)能带底部电子的有效质量*n m ;(5)能带顶部空穴的有效质量*p m解:(1)由0)(=dk k dE 得 an k π=(n=0,±1,±2…) 进一步分析an k π)12(+= ,E (k )有极大值,222)ma k E MAX=( 214221422142822/1083.7342232212414111/1059.92422124142110/1078.6)1043.5(224141100cmatom a a a cm atom a a a cm atom a a ⨯==⨯+⨯+⨯⨯==⨯⨯+⨯+⨯=⨯==⨯+-):():():(ank π2=时,E (k )有极小值所以布里渊区边界为an k π)12(+=(2)能带宽度为222)()ma k E k E MIN MAX =-( (3)电子在波矢k 状态的速度)2sin 41(sin 1ka ka ma dk dE v -== (4)电子的有效质量)2cos 21(cos 222*ka ka mdkEd m n-==能带底部 an k π2=所以m m n 2*= (5)能带顶部 an k π)12(+=, 且**n p m m -=,所以能带顶部空穴的有效质量32*mm p =半导体物理第2章习题1. 实际半导体与理想半导体间的主要区别是什么?答:(1)理想半导体:假设晶格原子严格按周期性排列并静止在格点位置上,实际半导体中原子不是静止的,而是在其平衡位置附近振动。

【精品】半导体物理学(刘恩科第七版)习题答案(比较完全)

半导体物理学(刘恩科第七版)习题答案(比较完全)------------------------------------------作者------------------------------------------日期第一章习题1.设晶格常数为a 的一维晶格,导带极小值附近能量E c (k)和价带极大值附近能量E V (k)分别为:E c =0220122021202236)(,)(3m k h m k h k E m k k h m k h V -=-+ 0m 。

试求:为电子惯性质量,nm a ak 314.0,1==π(1)禁带宽度;(2)导带底电子有效质量; (3)价带顶电子有效质量;(4)价带顶电子跃迁到导带底时准动量的变化 解:(1)eVm k E k E E E k m dk E d k m kdk dE Ec k k m m m dk E d k k m k k m k V C g V V V c 64.012)0()43(0,060064338232430)(2320212102220202020222101202==-==<-===-==>=+===-+ 因此:取极大值处,所以又因为得价带:取极小值处,所以:在又因为:得:由导带:043222*83)2(1m dk E d mk k C nC=== sN k k k p k p m dk E d mk k k k V nV/1095.7043)()()4(6)3(25104300222*11-===⨯=-=-=∆=-== 所以:准动量的定义:2. 晶格常数为0.25nm 的一维晶格,当外加102V/m ,107 V/m 的电场时,试分别计算电子自能带底运动到能带顶所需的时间。

解:根据:tkhqE f ∆∆== 得qE k t -∆=∆sat sat 137192821911027.810106.1)0(1027.810106.1)0(----⨯=⨯⨯--=∆⨯=⨯⨯--=∆ππ补充题1分别计算Si (100),(110),(111)面每平方厘米内的原子个数,即原子面密度(提示:先画出各晶面内原子的位置和分布图) Si 在(100),(110)和(111)面上的原子分布如图1所示:(a )(100)晶面 (b )(110)晶面(c )(111)晶面补充题2一维晶体的电子能带可写为)2cos 81cos 87()22ka ka mak E +-= (, 式中a 为 晶格常数,试求214221422142822/1083.7342232212414111/1059.92422124142110/1078.6)1043.5(224141100cmatom a a a cm atom a a a cmatom a a ⨯==⨯+⨯+⨯⨯==⨯⨯+⨯+⨯=⨯==⨯+-):():():((1)布里渊区边界; (2)能带宽度;(3)电子在波矢k 状态时的速度;(4)能带底部电子的有效质量*n m ;(5)能带顶部空穴的有效质量*p m解:(1)由0)(=dk k dE 得 an k π=(n=0,±1,±2…) 进一步分析an k π)12(+= ,E (k )有极大值,222)ma k E MAX=( ank π2=时,E (k )有极小值所以布里渊区边界为an k π)12(+=(2)能带宽度为222)()mak E k E MIN MAX =-( (3)电子在波矢k 状态的速度)2sin 41(sin 1ka ka ma dk dE v -==(4)电子的有效质量)2cos 21(cos 222*ka ka mdkEd m n-==能带底部 an k π2=所以m m n 2*= (5)能带顶部 an k π)12(+=, 且**n p m m -=,所以能带顶部空穴的有效质量32*mm p =第二章习题1. 实际半导体与理想半导体间的主要区别是什么?答:(1)理想半导体:假设晶格原子严格按周期性排列并静止在格点位置上,实际半导体中原子不是静止的,而是在其平衡位置附近振动。

半导体物理学(刘恩科)第七版-完整课后题答案

第一章习题1.设晶格常数为a 的一维晶格,导带极小值附近能量E c (k)和价带极大值附近能量E V (k)分别为:E c =0220122021202236)(,)(3m k h m k h k E m k k h m k h V -=-+ 0m 。

试求:为电子惯性质量,nm a ak 314.0,1==π〔1〕禁带宽度;(2) 导带底电子有效质量; (3)价带顶电子有效质量;〔4〕价带顶电子跃迁到导带底时准动量的变化 解:〔1〕eV m k E k E E E k m dk E d k m kdk dE Ec k k m m m dk E d k k m k k m k V C g V V V c 64.012)0()43(0,060064338232430)(2320212102220202020222101202==-==<-===-==>=+===-+ 因此:取极大值处,所以又因为得价带:取极小值处,所以:在又因为:得:由导带:043222*83)2(1m dk E d mk k C nC===sN k k k p k p m dk E d mk k k k V nV/1095.7043)()()4(6)3(25104300222*11-===⨯=-=-=∆=-== 所以:准动量的定义:2. 晶格常数为0.25nm 的一维晶格,当外加102V/m ,107 V/m 的电场时,试分别计算电子自能带底运动到能带顶所需的时间。

解:根据:tkhqE f ∆∆== 得qE k t -∆=∆sat sat 137192821911027.810106.1)0(1027.810106.1)0(----⨯=⨯⨯--=∆⨯=⨯⨯--=∆ππ补充题1分别计算Si 〔100〕,〔110〕,〔111〕面每平方厘米内的原子个数,即原子面密度〔提示:先画出各晶面内原子的位置和分布图〕Si 在〔100〕,〔110〕和〔111〕面上的原子分布如图1所示:〔a 〕(100)晶面 〔b 〕(110)晶面〔c 〕(111)晶面补充题2一维晶体的电子能带可写为)2cos 81cos 87()22ka ka ma k E +-= (, 式中a 为 晶格常数,试求〔1〕布里渊区边界; 〔2〕能带宽度;〔3〕电子在波矢k 状态时的速度;〔4〕能带底部电子的有效质量*n m ;〔5〕能带顶部空穴的有效质量*p m解:〔1〕由0)(=dk k dE 得 an k π= 〔n=0,±1,±2…〕 进一步分析an k π)12(+= ,E 〔k 〕有极大值,214221422142822/1083.7342232212414111/1059.92422124142110/1078.6)1043.5(224141100cm atom a a a cm atom a a a cm atom a a ⨯==⨯+⨯+⨯⨯==⨯⨯+⨯+⨯=⨯==⨯+-):():():(222)mak E MAX=( ank π2=时,E 〔k 〕有极小值所以布里渊区边界为an k π)12(+=(2)能带宽度为222)()ma k E k E MIN MAX =-( (3〕电子在波矢k 状态的速度)2sin 41(sin 1ka ka ma dk dE v -== 〔4〕电子的有效质量)2cos 21(cos 222*ka ka mdkEd m n-==能带底部 an k π2=所以m m n 2*= (5)能带顶部 an k π)12(+=, 且**n p m m -=,所以能带顶部空穴的有效质量32*mm p =半导体物理第2章习题1. 实际半导体与理想半导体间的主要区别是什么?答:〔1〕理想半导体:假设晶格原子严格按周期性排列并静止在格点位置上,实际半导体中原子不是静止的,而是在其平衡位置附近振动。

半导体物理学(刘恩科、朱秉升)第七版-最全课后题答案

第一章习题1.设晶格常数为a 的一维晶格,导带极小值附近能量E c (k)和价带极大值附近能量E V (k)分别为:E c =0220122021202236)(,)(3m k h m k h k E m k k h m k h V -=-+ 0m 。

试求:为电子惯性质量,nm a ak 314.0,1==π(1)禁带宽度;(2) 导带底电子有效质量; (3)价带顶电子有效质量;(4)价带顶电子跃迁到导带底时准动量的变化 解:(1)eV m k E k E E E k m dk E d k m kdk dE Ec k k m m m dk E d k k m k k m k V C g V V V c 64.012)0()43(0,060064338232430)(2320212102220202020222101202==-==<-===-==>=+===-+ 因此:取极大值处,所以又因为得价带:取极小值处,所以:在又因为:得:由导带:043222*83)2(1m dk E d mk k C nC=== sN k k k p k p m dk E d mk k k k V nV/1095.7043)()()4(6)3(25104300222*11-===⨯=-=-=∆=-== 所以:准动量的定义:2. 晶格常数为0.25nm 的一维晶格,当外加102V/m ,107 V/m 的电场时,试分别计算电子自能带底运动到能带顶所需的时间。

解:根据:tkhqE f ∆∆== 得qE k t -∆=∆sat sat 137192821911027.810106.1)0(1027.810106.1)0(----⨯=⨯⨯--=∆⨯=⨯⨯--=∆ππ补充题1分别计算Si (100),(110),(111)面每平方厘米内的原子个数,即原子面密度(提示:先画出各晶面内原子的位置和分布图)Si 在(100),(110)和(111)面上的原子分布如图1所示:(a )(100)晶面 (b )(110)晶面(c )(111)晶面214221422142822/1083.7342232212414111/1059.92422124142110/1078.6)1043.5(224141100cmatom a a a cm atom a a a cm atom a a ⨯==⨯+⨯+⨯⨯==⨯⨯+⨯+⨯=⨯==⨯+-):():():(补充题2一维晶体的电子能带可写为)2cos 81cos 87()22ka ka ma k E +-= (, 式中a 为 晶格常数,试求(1)布里渊区边界; (2)能带宽度;(3)电子在波矢k 状态时的速度;(4)能带底部电子的有效质量*n m ;(5)能带顶部空穴的有效质量*p m解:(1)由0)(=dk k dE 得 an k π= (n=0,±1,±2…) 进一步分析an k π)12(+= ,E (k )有极大值,222)mak E MAX=( ank π2=时,E (k )有极小值所以布里渊区边界为an k π)12(+=(2)能带宽度为222)()ma k E k E MIN MAX =-( (3)电子在波矢k 状态的速度)2sin 41(sin 1ka ka ma dk dE v -== (4)电子的有效质量)2cos 21(cos 222*ka ka mdkEd m n-==能带底部 an k π2=所以m m n 2*= (5)能带顶部 an k π)12(+=, 且**n p m m -=,所以能带顶部空穴的有效质量32*mm p =半导体物理第2章习题1. 实际半导体与理想半导体间的主要区别是什么?答:(1)理想半导体:假设晶格原子严格按周期性排列并静止在格点位置上,实际半导体中原子不是静止的,而是在其平衡位置附近振动。

半导体物理学(刘恩科、朱秉 升)第七版-最全课后题答案

(5)能带顶部空穴的有效质量

解:(1)由 得 (n=0,1,2…) 进一步分析 ,E(k)有极大值,

时,E(k)有极小值 所以布里渊区边界为 (2)能带宽度为 (3)电子在波矢k状态的速度 (4)电子的有效质量 能带底部 所以 (5)能带顶部 , 且, 所以能带顶部空穴的有效质量

20. 制造晶体管一般是在高杂质浓度的n型衬底上外延一层n型外延层, 再在外延层中扩散硼、磷而成的。

(1)设n型硅单晶衬底是掺锑的,锑的电离能为0.039eV,300K时的EF 位于导带下面0.026eV处,计算锑的浓度和导带中电子浓度。

(2)设n型外延层杂质均匀分布,杂质浓度为4.61015cm-3,计算300K 时EF的位置及电子和空穴浓度。

8. 利用题 7所给的Nc 和NV数值及Eg=0.67eV,求温度为300K和500K 时,含施主浓度ND=51015cm-3,受主浓度NA=2109cm-3的锗中电子及

空穴浓度为多少?

9.计算施主杂质浓度分别为1016cm3,,1018 cm-3,1019cm-3的硅在室温下 的费米能级,并假定杂质是全部电离,再用算出的的费米能 级核对 一下,上述假定是否在每一种情况下都成立。计算时,取施主能级 在导带底下的面的0.05eV。

17. 施主浓度为1013cm3的n型硅,计算400K时本征载流子浓度、多子浓 度、少子浓度和费米能级的位置。

18. 掺磷的n型硅,已知磷的电离能为0.044eV,求室温下杂质一 半电离时费米能级的位置和浓度。

19. 求室温下掺锑的n型硅,使EF=(EC+ED)/2时锑的浓度。已知锑的 电离能为0.039eV。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3)价带顶电子有效质量;

(4)价带顶电子跃迁到导带底时准动量的变化

解:(1)

导带:

由 2 2k 2 2 (k k1 ) 0

3m0

m0

得:k

3 4

k1

又因为:d 2 Ec dk 2

2 2 3m0

2 2 m0

8 2 3m0

0

所以:在k 3 k处,Ec取极小值 4

价带:

dEV 6 2k 0得k 0

(a)(100)晶面

(b)(110)晶面

(c)(111)晶面

1 4 1 (100): a 2 4

2 a2

2

(5.43 108 ) 2

6.78 1014 atom / cm2

24 1 2 1

(110):

4

2

4

9.59 1014 atom / cm2

2a a

2a 2

4 1 2 1 2

(111): 4

(5)能带顶部空穴的有效质量

m

* p

解:(1)由 dE(k) 0 得 k n

dk

a

(n=0,1,2…)

进一步分析 k (2n 1) ,E(k)有极大值, a

E(k ) MAX

2 2 ma 2

k

2n

时,E(k)有极小值

a

所以布里渊区边界为 k (2n 1) a

(2)能带宽度为 E(k ) MAX

所以:p

(k

)

k

3 4

k1

(k )k0

3 4

k1

0

7.95 1025 N

/s

2. 晶格常数为 0.25nm 的一维晶格,当外加 102V/m,107 V/m 的电场时,试分别计

ห้องสมุดไป่ตู้

算电子自能带底运动到能带顶所需的时间。

解:根据: f

qE

h

k t

得

t

k qE

(0 )

t1

a 1.6 1019 102

双性行为。 Si 取代 GaAs 中的 Ga 原子则起施主作用; Si 取代 GaAs 中的 As 原子则起受主 作用。导带中电子浓度随硅杂质浓度的增加而增加,当硅杂质浓度增加到一定 程度时趋于饱和。硅先取代 Ga 原子起施主作用,随着硅浓度的增加,硅取代 As 原子起受主作用。 5. 举例说明杂质补偿作用。 当半导体中同时存在施主和受主杂质时, 若(1) ND>>NA 因为受主能级低于施主能级,所以施主杂质的电子首先跃迁到 NA 个受主能级上, 还有 ND-NA 个电子在施主能级上,杂质全部电离时,跃迁到导带中的导电电子 的浓度为 n= ND-NA。即则有效受主浓度为 N ≈ Aeff ND-NA (2)NA>>ND

且

m

* p

mn* ,

所以能带顶部空穴的有效质量

m

* p

2m 3

第二章习题

1. 实际半导体与理想半导体间的主要区别是什么? 答:(1)理想半导体:假设晶格原子严格按周期性排列并静止在格点位置上,

实际半导体中原子不是静止的,而是在其平衡位置附近振动。 (2)理想半导体是纯净不含杂质的,实际半导体含有若干杂质。 (3)理想半导体的晶格结构是完整的,实际半导体中存在点缺陷,线缺陷

2

3a 2a

2

4 7.83 1014 atom / cm2 3a 2

补充题 2

一维晶体的电子能带可写为

E(k )

2 ma 2

(7 8

cos

ka

1 8

cos 2ka)

,

式中 a 为 晶格常数,试求 (1)布里渊区边界; (2)能带宽度; (3)电子在波矢 k 状态时的速度;

(4)能带底部电子的有效质量 mn* ;

第一章习题

1.设晶格常数为 a 的一维晶格,导带极小值附近能量 Ec(k)和价带极大值附近 能量 EV(k)分别为:

Ec=

h2k 2 3m0

h2 (k k1 )2 m0

, EV

(k)

h

2

k

2 1

6m0

3h 2 k 2 m0

m0

为电子惯性质量,k1

a

,a

0.314nm。试求:

(1)禁带宽度;

(2)导带底电子有效质量;

和面缺陷等。 2. 以 As 掺入 Ge 中为例,说明什么是施主杂质、施主杂质电离过程和 n 型半导体。

As 有 5 个价电子,其中的四个价电子与周围的四个 Ge 原子形成共价键,还剩 余一个电子,同时 As 原子所在处也多余一个正电荷,称为正离子中心,所以,一 个 As 原子取代一个 Ge 原子,其效果是形成一个正电中心和一个多余的电子.多余 的电子束缚在正电中心,但这种束缚很弱,很小的能量就可使电子摆脱束缚,成为 在晶格中导电的自由电子,而 As 原子形成一个不能移动的正电中心。这个过程叫 做施主杂质的电离过程。能够施放电子而在导带中产生电子并形成正电中心,称

为施主杂质或 N 型杂质,掺有施主杂质的半导体叫 N 型半导体。 3. 以 Ga 掺入 Ge 中为例,说明什么是受主杂质、受主杂质电离过程和 p 型半导体。 Ga 有 3 个价电子,它与周围的四个 Ge 原子形成共价键,还缺少一个电子,于是在 Ge 晶体的共价键中产生了一个空穴,而 Ga 原子接受一个电子后所在处形成一个负 离子中心,所以,一个 Ga 原子取代一个 Ge 原子,其效果是形成一个负电中心和 一个空穴,空穴束缚在 Ga 原子附近,但这种束缚很弱,很小的能量就可使空穴摆 脱束缚,成为在晶格中自由运动的导电空穴,而 Ga 原子形成一个不能移动的负电 中心。这个过程叫做受主杂质的电离过程,能够接受电子而在价带中产生空穴, 并形成负电中心的杂质,称为受主杂质,掺有受主型杂质的半导体叫 P 型半导体。 4. 以 Si 在 GaAs 中的行为为例,说明 IV 族杂质在 III-V 族化合物中可能出现的

dk

m0

又因为 d 2 EV dk 2

6 2 m0

0,所以k 0处,EV 取极大值

因此:E g

EC

(

3 4

k1 )

EV

(0)

2 k12 12m0

0.64eV

(2)mn*C

2 d 2 EC

3 8

m0

dk 2

k

3 4

k1

(3)mn*V

2 d 2 EV

m0 6

dk 2 k 01

(4)准动量的定义:p k

E(k ) MIN

2 2 ma 2

(3)电子在波矢

k

状态的速度 v

1

dE dk

ma

(sin ka

1 sin 4

2ka)

(4)电子的有效质量

mn*

2 d 2E

m (cos ka 1 cos 2ka)

dk 2

2

能带底部 k 2n a

所以 mn* 2m

(5)能带顶部 k (2n 1) , a

8.27 108 s

(0 )

t 2

a 1.6 1019 107

8.27 1013 s

补充题 1 分别计算 Si(100),(110),(111)面每平方厘米内的原子个数,即原子面密度(提

示:先画出各晶面内原子的位置和分布图)

Si 在(100),(110)和(111)面上的原子分布如图 1 所示: