ICcomplier安装教程

亨特I-Core控制器安装手册(完成版)

产品简介

Hunter I-CORE 控制器是一款功能齐全、性能优越的控制器,主要针对商用和高端客户使用。I-CORE 功能齐全的 特点,使它成为灌溉控制器的最佳选择。

I-CORE 特性:

z 模块式设计可是控制器站点由 6 站扩容至 30 站(塑料外壳)或 42 站(金属外壳)。

z 4 个完全独立程序。 z Diagnostic Dashboard™ 诊断表盘检测系统, 并且提供实时传感器和控制器工作状态。 z 流量实时监测 z 预装 Smart Port 智能遥控接口。 z 可编制独立的季节灌溉计划,比如全局灌溉, 逐月灌溉,或者通过 Solar Sync 气候传感器调整灌溉。 z 灌 溉 过 程 中 , 用 户 可 通 过 Water Window Manager TM 灌水控制窗口,设置灌水时间。 z Easy Retrieve TM 易恢复信息功能:信息会被 优先保存。 z 更大的背光显示屏,便于编程操作。 z 多国语言版编程提示 z 短路自动保护功能

I-CORE 控制面板和主要元件

1.LCD 显示屏 — 背光,可调对比度 2. “+”键 — 增加所选功能的闪亮值。 3. “–“键 — 降低所选功能的闪亮值。 4.ST(上、下键)— 用于不同工作界面中功能键 的上下选择,以及同一操作界面下不同选项之间的切换。 5.WX(左、右键)— 用于不同界面的左右切换, 以及某些界面下重要的功能选择,比如:站点、启动时 间、灌溉日等 6.PRG(程序按键)— 选择 A‐D 中的一个自动程序, 并同时启动测试程序。 7.控制转柄 — 用于选择 I‐CORE 控制器中的所有功 能。在前 4 个刻度位置,可设置最基本的自动灌溉程序。 8. 传感器旁路开关 — 如果客户安装了天气传感 器,此开关可允许用户忽略此装置程序。 9.系统状态显示面板 — LED 灯显示出传感器的实时 状态,以及阀门运行和流量监测等信息。 10. 可拆卸面板:I‐CORE 控制器的面板可拆卸,便 于在任何地方编程。

ICcomplier安装教程

ICcomplier安装教程synopsys ic compiler (v2005.linux)是基于Galaxy设计平台开发的产品。

主要的⼯具有:LEDALEDA是可编程的语法和设计规范检查⼯具,它能够对全芯⽚的VHDL和Verilog描述、或者两者混合描述进⾏检查,加速SoC 的设计流程。

LEDA预先将IEEE可综合规范、可仿真规范、可测性规范和设计服⽤规范集成,提⾼设计者分析代码的能⼒VCSVCS是编译型Verilog模拟器,它完全⽀持OVI标准的Verilog HDL语⾔、PLI和SDF。

VCS具有⽬前⾏业中最⾼的模拟性能,其出⾊的内存管理能⼒⾜以⽀持千万门级的ASIC设计,⽽其模拟精度也完全满⾜深亚微⽶ASIC Sign-Off的要求。

VCS结合了节拍式算法和事件驱动算法,具有⾼性能、⼤规模和⾼精度的特点,适⽤于从⾏为级、RTL到Sign-Off等各个阶段。

VCS已经将CoverMeter中所有的覆盖率测试功能集成,并提供VeraLite、CycleC 等智能验证⽅法。

VCS和Scirocco也⽀持混合语⾔仿真。

VCS和Scirocco都集成了Virsim 图形⽤户界⾯,它提供了对模拟结果的交互和后处理分析。

SciroccoScirocco是迄今为⽌性能最好的VHDL模拟器,并且是市场上唯⼀为SoC验证度⾝定制的模拟⼯具。

它与VCS⼀样采⽤了⾰命性的模拟技术,即在同⼀个模拟器中把节拍式模拟技术与事件驱动的模拟技术结合起来。

Scirocco的⾼度优化的VHDL编译器能产⽣有效减少所需内存,⼤⼤加快了验证的速度,并能够在⼀台⼯作站上模拟千万门级电路。

这⼀性能对要进⾏整个系统验证的设计者来说⾮常重要。

VeraVera验证系统满⾜了验证的需要,允许⾼效、智能、⾼层次的功能验证。

Vera验证系统已被Sun、NEC、Cisco等公司⼴泛使⽤以验证其实际的产品,从单⽚ASIC到多⽚ASIC 组成的计算机和⽹络系统,从定制、半定制电路到⾼复杂度的微处理器。

iC Software 预安装指南说明书

Pre-Inst all ati o nG ui de Computer Specifications Guidance for iC Software This document is intended to help users select an appropriate computer to run iC Software. Please take the time to read through this brief guidance document. For questions please contact iC software support at ********* or your local account manager. 1 Minimum Requirements The minimum computer requirements to run iC software differ by product and version. Please check the Installation Guide delivered with your software to the specific specifications for your product. Each version is tested on a machine meeting the minimum specifications to ensure the software will install and run correctly, but this does not guarantee reasonable performance, particularly when running longer experiments that collect more data. Higher performance processors are recommended to provide the best user experience, as specified in the following section. 2 Recommendations for Peak Performance The specifications for laptop computers that we currently ship with new instruments are included below. This setup has been tested with several instruments connected at one time and performs well. This laptop or a similar high end model is a good choice for almost any application using iC software. Characteristics Shipped (Dell Mobile Precision 7730) CPU Intel Core i7-8850H, 2.60 GHz, 9 MB Cache Memory 16 GB DDR4 SDRAM at 2666 MHz Hard Drive 256 GB Solid State Graphics 17.3 inch FHD displayIt is important to note that the processor type is often more important than the CPU speed when considering performance.Note on Ports: Ensure that the computer includes an Ethernet port if connecting any EasyMax, OptiMax, RC1mx, RX-10 or ReactRaman instruments and has at least one USB type A port available for each ReactIR 700, EasyViewer and ParticleTrack instrument that will be connected. 3 Operating System SupportThe operating systems supported depend on the exact software product version and the instrument model being controlled. The most recent versions are included on the next page and a full list of all versions and instruments can be found at https:///ic-comp-tables .P re-I nst all ati o nG ui de Product/Version Microsoft ® Windows ® XP Microsoft ® Windows ® 7, 32-bit Microsoft ® Windows ® 7, 64-bit Microsoft ® Windows ® 8.1 Microsoft ® Windows ® 10 iC IR 7.0 / 7.1 iC IR 4.3 ReactIR 45P systems only * iC FBRM 4.4 * iC FBRM 4.3 (except for FBRM D600/S400) iC Vision 8.0 iC PVM 7.0 SP (only for PVM V19) iC Raman 7.1 iControl 6.0EasyMax/OptiMax/RX-10/RC1mx iControl 6.1EasyMax/OptiMax/RX-10/RC1mx iControl RC1e 5.3 iControl RC1e 5.6 iControl LabMax 5.3 iC FBRM 4.4/iC IR 4.3 may require installing a Hotfix or Service Pack to work on some Microsoft Windows 10 computersNote on Microsoft Windows 11: The currently available versions of iC software have not been tested with Windows 11 so it is not officially supported. Initial testing has not encountered any issues so far, so the iC software may work fine on this operating system, but using it is at the customer's own risk.4 Other Required/Recommended SoftwareAdobe Reader: In order to easily read the documentation portfolios and PDF files that are delivered with iC Software, it is recommended that the latest version of Adobe Acrobat reader is installed (go to/reader/ to get the installer).Microsoft ® Office: iC software allows users to generate reports using Microsoft ® Word ® and import and export data from Microsoft ® Excel ®. To use these functions, Microsoft ® Office 2003 or later must be available on the iC PC. Note that if you intend to use the iC Data Share Excel Add-in, then you need Office 2007 or newer. Microsoft ® Windows ® Media Player: For iControl software, the computer should have the latest Microsoft ® Windows ® Media Player installer in order to view the Mixing Guidelines or Tutorial Videos (go to/en-US/windows/downloads/windows-media-player to get the installer).。

synopsys iC Compiler II 数据手册说明书

DATASHEETOverview IC Compiler™ II is the industry leading place and route solution that delivers best-in-class quality-of-results (QoR) for next-generation designs across all market verticals and process technologies while enabling unprecedented productivity. IC Compiler II includes innovative for flat and hierarchical design planning, early design exploration, congestion aware placement and optimization, clock tree synthesis, advanced node routing convergence, manufacturing compliance, and signoff closure.IC Compiler II is specifically architected to address aggressive performance, power, area (PPA), and time-to-market pressures of leading-edge designs. Key technologies include a pervasively parallel optimization framework, multi-objective global placement, routing driven placement optimization, full flow Arc based concurrent clock and data optimization, total power optimization, multi-pattern and FinFET aware flow and machine learning (ML) driven optimization for fast and predictive design closure. Advanced Fusion technologies offer signoff IR drop driven optimization, PrimeTime ® delay calculation within IC Compiler II, exhaustive path-based analysis (PBA) and signoff ECO within place and route for unmatched QoR and design convergence. F U S I O N D E S I G N P L A T F O R M PrimeTime, StarRC, PrimePower,IC Validator, RedHawk Analysis Fusion Fusion Compiler IC Compiler II Design Compiler NXT TestMAX F o r m a l i t y ECO Fusion S i g n o f f F u s i o n S i g n o f f F u s i o n Test Fusion Figure 1: IC Compiler II Anchor in Synopsys Design PlatformAccelerating DesignClosure on AdvancedDesignsIC Compiler II Industry Leading Place and Route SystemKey BenefitsProductivity• The highest capacity solution that supports 500M+ instances with a scalable and compact data model• A full suite of design planning features including transparent hierarchical optimization• Out-of-the-box simple reference methodology for easy setup• Multi-threaded and distributed computing for all major flow steps• Golden signoff accuracy with direct access to PrimeTime delay calculationPPA• Unified TNS driven optimization framework• Congestion, timing, and power-driven logic re-synthesis• IEEE 1801 UPF/multi-voltage support• Arc-based concurrent clock and data optimization• Global minima driven total power optimizationAdvanced Nodes• Multi-pattern and FinFET aware design flow• Next generation advanced 2D placement and legalization• Routing layer driven optimization, auto NDR, and via pillar optimization• Machine learning driven congestion prediction and DRC closure• Highest level of foundry support and certification for advanced process nodes• IC Validator in the loop signoff driven DRC validation and fixingAdvanced Fusion Technology• Physically aware logic re-synthesis• IR drop driven optimization during all major flow steps• PrimeTime delay calculation based routing optimization for golden accuracy• Integrated PrimeTime ECO flow during routing optimization for fastest turnaround timeEmpowering Design Across Diversified ApplicationsThe dizzying pace of innovation and highly diversified applications across the design spectrum is forcing a complete rethink of the place and route systems to design and implement differentiated designs in a highly competitive semiconductor market on schedule. Designers on emerging process nodes must meet aggressive PPA and productivity goals. It essentially means efficient and intelligent handling of 100s of millions of place-able instances, multiple levels of hierarchy, 1000s of hard macros, 100s of clocks, wide busses, and 10s of modes and corners power domains and complex design constraints and process technology mandates. Emphasis on Designer ProductivityIC Compiler II is architected from the ground up for speed and scalability. Its hierarchical data model consumes 2-3X less memory than conventional tools, boosting the limits of capacity to 500M placeable instances and beyond. Adaptive abstraction and on-the-fly data management minimize memory requirements and enable fast responsive data manipulation. Near-linear multi-core threading of key infrastructural components and core algorithms such as database access and timing analysis speed up optimization at all phases of design. Patented, lossless compact modeling and independent R and C extraction allow handling more modes and corners (MCMM scenarios) with minimal runtime impact.IC Compiler II has built-in Reference Methodology(RM) that ensures fast flow bring up. This RM Flow is Foundry Process/Design Type specific to ensure a robust starting point and seamless bring up. IC Compiler II has direct access to the Golden PrimeTime delay calculation engine to minimize ECO iterations.IC Compiler II’s new data model enables designers to perform fast exploration and floorplanning with complex layout requirements. IC Compiler II can create bus structures, handle designs with n-levels of physical hierarchy, and support Multiply Instantiated Blocks (MIBs) in addition to global route driven pin assignment/feedthrough flow, timing driven macro placement, MV area design planning.A design data mismatch inferencing engine analyzes the quality of inputs and drives construct creation on the fly, delivering design insights even with “incomplete” data early in the design cycle. Concurrent traversal of logical and physical data models enables hierarchical Data-Flow Analysis (DFA) and fast interactive analysis through multi-level design hierarchies and MIBs. Data flow and feedthrough paths highlighted in Figure 2 allow analysis and manipulation through n-levels of hierarchy to complete early design exploration and prototyping.Figure 2: Fast interactive analysis through multiple-levels of physical hierarchy and MIBPipeline-register-planning shown in Figure 3, provides guidance for optimal placement to meet the stringent timing requirementsof high-performance designs. Interactive route editor integrated which is advanced node aware shown in Figure 4, allows intricate editing and routing functions, including the creation of special signal routes, buses, etc.Figure 3: Pipeline register placement enables superior QoR for designs with complex busesAchieving Best Performance, Power, Area, and TATIC Compiler II features a new optimization framework built on global analytics. This Unified TNS Driven Optimization framework is shared with Design Compiler NXT synthesis to enable physically-aware synthesis, layer assignment, and route-based optimization for improved PPA and TAT. Multi-Corner Multi-Mode (MCMM) and Multi-Voltage (MV) aware, level-based analytical algorithms continuously optimize using parallel heuristic algorithms. Multi-factor costing functions deliver faster results on both broad and targeted design goals. Concurrent PPA driven logic remapping, rewiring, and legalization interleaved with placement minimizes congested logic, resulting in simple localized logic cones that maximize routability and QoR.IC Compiler II minimizes leakage with fast and efficient cell-by-cell power selection across HVT, SVT and LVT cells and varying channel lengths. Activity-driven power optimization uses VCD/ SAIF, net toggle rates, or probability functions to drive placement decisions and minimize pin capacitances. Multi-bit register banking optimizes clock tree structures, reduces area, and net length, while automatically managing clock, data, and scan chain connections.Advanced modeling of congestion across all layers highlighted in Figure 4 provides accurate feedback throughput the flow from design planning to post- route optimization.Figure 4: Intelligent and accurate analysis for congestion and powerIC Compiler II introduces a new Concurrent Clock and Data (CCD) analysis and optimization engine that is built-in to every flow step resulting in meeting both aggressive performance and minimizing total power footprint. ARC-based CCD optimization performs clock tree traversal across all modes/corners in path-based fashion to ensure optimal delay budgeting.Robust support for clock distribution enables virtually any clock style, including mesh, multi-source, or H-tree topologies. Advanced analysis and debugging features perform accurate clock QoR analysis and debugging as highlighted in Figure 5.Figure 5: Accurate clock QoR analysis and debugging (a & b) Abstracted clock graph and schematic.(c) Latency clock graph. (d) Colored clock tree in layout.IC Compiler II features many innovative technologies that make it the ideal choice for high-performance, energy-efficient Arm®processor core implementation, resulting in industry-best milliwatts/megahertz (mW/MHz) for mobile and other applications across the board. Synopsys and Arm work closely together to offer optimized implementation of popular Arm cores for IC Compiler II,with reference flows available for Arm Cortex®-A high-performance processors and Mali GPUs. In addition, Arm offers off-the-shelf Artisan® standard cell and memory models that have been optimally tuned and tested for fast deployment in an IC Compiler II environment. Continuous technology innovation and close collaboration makes IC Compiler II the leading choice for Arm-based high- performance design.Highest Level of Advanced Node Certification and SupportIC Compiler II provides advanced node design enablement across major foundries and technology nodes—including 16/14nm,12/10nm, 7/5nm, and sub-5nm geometries. Zroute digital router technology ensures early and full compliance with the latest design rules required for these advanced node technologies. Synopsys collaborates closely with all the leading foundries to ensure that IC Compiler II is the first to deliver support for early prototype design rules and support for the final production design rules. IC Compiler II design technologies maximize the benefits of new process technologies and offer optimal return on investment for cutting-edge silicon applications.IC Compiler II advanced node design support includes multi-pattern/FinFET aware placement and routing, Next-generation advanced 2D placement and legalization, routing layer driven optimization, auto NDR, and via pillar optimization. IC Validator in the loop provides signoff DRC feedback during Implementation.Foundry fill Track based fillFigure 6: IC Validator In-Design metal fill color aware metal fill, optimized for density and foundry requirementsMachine learning driven congestion prediction and DRC closure allow for fastest routing convergence with best PPA. Multiple sets of training data are used to extract key predictive elements that guide the pre-route flow.Advanced Fusion TechnologyThe Fusion Design Platform™ delivers unprecedented full-flow QoR and time-to-results (TTR) to accelerate the next wave of semiconductor industry innovation. The industry’s first AI-enhanced, cloud-ready Design Platform with Fusion Technology™ isbuilt from Synopsys’ market-leading, massively-parallel digital design tools, and augmented with innovative capabilities to tacklethe escalating challenges in cloud computing, automotive, mobile, and IoT market segments and accelerate the next wave of industry innovation.Fusion Technology redefines conventional EDA tool boundaries across synthesis, place-and-route, and signoff, sharing integrated engines across the industry’s premier digital design products. It enables designers to accelerate the delivery of their next-generation designs with the industry-best QoR and the TTR.©2019 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks isavailable at /copyright.html . All other names mentioned herein are trademarks or registered trademarks of their respective owners.。

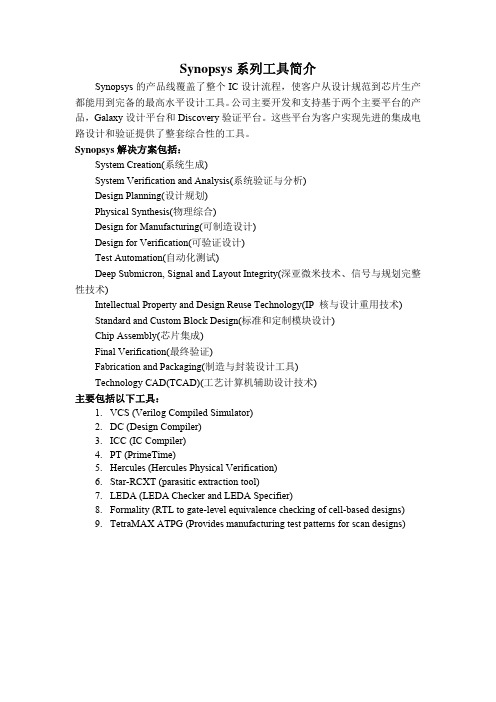

Synopsys系列工具简介

Synopsys系列工具简介Synopsys的产品线覆盖了整个IC设计流程,使客户从设计规范到芯片生产都能用到完备的最高水平设计工具。

公司主要开发和支持基于两个主要平台的产品,Galaxy设计平台和Discovery验证平台。

这些平台为客户实现先进的集成电路设计和验证提供了整套综合性的工具。

Synopsys解决方案包括:System Creation(系统生成)System Verification and Analysis(系统验证与分析)Design Planning(设计规划)Physical Synthesis(物理综合)Design for Manufacturing(可制造设计)Design for Verification(可验证设计)Test Automation(自动化测试)Deep Submicron, Signal and Layout Integrity(深亚微米技术、信号与规划完整性技术)Intellectual Property and Design Reuse Technology(IP 核与设计重用技术)Standard and Custom Block Design(标准和定制模块设计)Chip Assembly(芯片集成)Final Verification(最终验证)Fabrication and Packaging(制造与封装设计工具)Technology CAD(TCAD)(工艺计算机辅助设计技术)主要包括以下工具:1.VCS (Verilog Compiled Simulator)2.DC (Design Compiler)3.ICC (IC Compiler)4.PT (PrimeTime)5.Hercules (Hercules Physical Verification)6.Star-RCXT (parasitic extraction tool)7.LEDA (LEDA Checker and LEDA Specifier)8.Formality (RTL to gate-level equivalence checking of cell-based designs)9.TetraMAX ATPG (Provides manufacturing test patterns for scan designs)1.VCS (Verilog Compiled Simulator)VCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。

ccapitioner插件使用方法

ccapitioner插件使用方法【实用版3篇】目录(篇1)apitioner插件简介apitioner插件安装步骤apitioner插件使用方法apitioner插件的优点V.总结正文(篇1)ccapitioner插件是一款非常实用的工具,可以帮助用户快速地完成一些复杂的任务。

下面,我们将详细介绍ccapitioner插件的使用方法。

apitioner插件简介ccapitioner插件是一款由ccapitioner公司开发的软件,它可以帮助用户快速地完成一些复杂的任务,如数据采集、数据处理和分析等。

ccapitter插件可以与其他软件进行集成,从而为用户提供更加全面的解决方案。

apitioner插件安装步骤安装ccapitioner插件非常简单,只需要按照以下步骤操作即可:1.下载ccapitioner插件的安装包;2.解压缩安装包;3.双击安装程序,按照提示完成安装。

apitioner插件使用方法ccapitioner插件的使用方法可以分为以下几个步骤:1.打开ccapitter软件,并选择需要使用的插件;2.配置ccapitter插件的参数,包括采集频率、数据存储路径等;3.启动ccapitter插件,开始采集数据;4.对采集到的数据进行处理和分析。

apitioner插件的优点ccapitter插件具有以下优点:1.采集速度快,数据准确度高;2.数据分析功能强大,可以帮助用户快速找到问题的关键点;3.可与其他软件进行集成,扩展了ccapitter的应用范围。

V.总结ccapitter插件是一款非常实用的工具,可以帮助用户快速地完成一些复杂的任务。

目录(篇2)apitioner插件简介apitioner插件安装步骤apitioner插件使用方法apitioner插件的优点正文(篇2)ccapitioner插件是一款非常实用的工具,它可以实现各种数据的采集和分析。

ccapitioner插件可以广泛应用于工业、农业、林业、渔业等领域,能够提高数据的精度和效率,降低工作成本。

Calibre安装

Calibre安装本楼解释如何安装和破解Calibre2022:某86_cal_2022.2_34.26_mib.e某e[Calibre32bit版本]i某l_cal_2022.2_34.26_mib.e某e[Calibre64bit版本]当然了,如1楼解释,intall.i某l不必须,32bit和64bit版本二者选一即可。

========================================================现在开始安装软件,配置环境以及licene:1.安装Calibre1.1安装路径,我自己喜欢安装到“/ur/local/mentor”目录下,当然您可以安装到别处也行。

1.3安装方法2:将“某86_cal_2022.2_34.26_mib.e某e”或“i某l_cal_2022.2_34.26_mib.e某e”复制到您的安装目录下(因为我安装的32bit的Calibre,所以以下多以“某86_cal_2022.2_34.26”为例,安装64bit的朋友自己注意替换以下啦)。

发现Mentor的软件都是默认安装在源文件所在的目录的,所以想装到那儿就拷到哪儿。

接着执行“./某86_cal_2022.2_34.26_mib.e某e”或“./i某l_cal_2022.2_34.26_mib.e某e”。

至步骤1.4。

1.3.1如遇到权限问题,直接“chmod777”吧。

1.3.2如果遇到“uudecode”的问题,装“harutil-4.6.1-2.i386.rpm”包吧(见步骤2.2)。

1.4安装方法2:接下来安装过程会询问是否同意协议的问题,想学蝌蚪文就P键+回车:(P)ageThough一页页地看下,不想烦就D键+回车:(D)iplay一下。

总之后面是“ye+回车”。

(没辙,不同意不给装啊…)1.5等着进度条到底,安装就完成一半鸟!-------------------------------------------------------------------------------------------------------------2.生成licene:2.1首先需要说明的是,如果您机器上已经有Calibre2022(包括以上)的licene,本步骤请无视。

PICC编译器的安装与使用方法[5篇范例]

![PICC编译器的安装与使用方法[5篇范例]](https://img.taocdn.com/s3/m/c16f1b31876fb84ae45c3b3567ec102de2bddf10.png)

PICC编译器的安装与使用方法[5篇范例]第一篇:PICC 编译器的安装与使用方法首先我先说下,源于网上个人整理后分享的整理也要花费时间和精力,2个币下载也不算贵的,如果你不下可以去网上自己去找,请不要骂人。

PICC 编译器的安装与使用方法使用过汇编语言和C语言的朋友肯定会感觉到C语言的人性化与方便性,汇编语言起源的年代比较早,因此,有很多程序高手仍使用汇编语言,毕竟自己也已经习惯了,但对于一些单片机新手入门的,我们还是推荐使用C语言来写程序,相对来说比较通俗,易学。

在某些特定的场合,汇编语言仍然有不可代替的优势,毕竟指令执行时间很精确,但对于目前越来越长的程序代码,考虑到软件的升级性与维护性,我们还是强烈推荐用户使用C语言作为开发语言。

下面,我们来介绍一下,PIICC C编译器 for MPLAB IDE 的安装与使用方法,从此开始了我们的PIC单片机C语言时代。

运行安装程序,将出现如图1所示安装界面。

-->>点击下载PICC 编译器和破解注册机点击“下一步”出现如图2所示:单击“下一步”出现如图3所示单击“是”出现如图4所示,选择安装目录(也可以建议使用默认值)单击“下一步”出现如下安装进度界面等待完成以后将出现如下提示选择“是”继续安装,将显示如下提示到此安装完成,将提示你重新启动电脑,选择确定。

下面是软件的激活过程:首先从“开始菜单”选择“激活”菜单。

出现如下所示单击下一步,出现如图所示激活界面启动“激活”程序,如图所示把“Last Name”前的“√”并把生成的各项依次填入激活界面的相应位置,点击“下一步”若安装成功将显示如下图所示提示信息,否则需要返回上一步重新填写激活信息。

到此“激活”过程完成。

下面介绍在mplab中如何使用刚刚安装好的PICC软件:1:启动运行MPLAB IDE软件,这时还没有打开任何项目跟源文件,选择File---》New菜单项,打开文档窗口,在此输入c语言源程序。

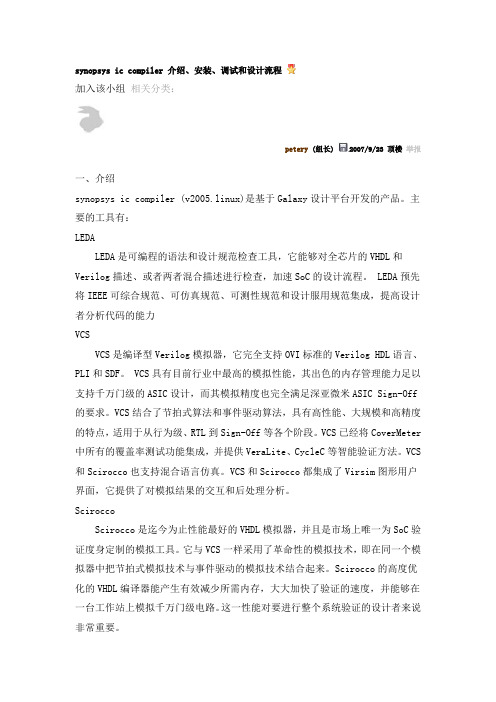

synopsys ic compiler 介绍、安装、调试和设计流程

synopsys ic compiler 介绍、安装、调试和设计流程加入该小组相关分类:petery (组长) 2007/9/23 顶楼举报一、介绍synopsys ic compiler (v2005.linux)是基于Galaxy设计平台开发的产品。

主要的工具有:LEDALEDA是可编程的语法和设计规范检查工具,它能够对全芯片的VHDL和Verilog描述、或者两者混合描述进行检查,加速SoC的设计流程。

LEDA预先将IEEE可综合规范、可仿真规范、可测性规范和设计服用规范集成,提高设计者分析代码的能力VCSVCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。

VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off 的要求。

VCS结合了节拍式算法和事件驱动算法,具有高性能、大规模和高精度的特点,适用于从行为级、RTL到Sign-Off等各个阶段。

VCS已经将CoverMeter 中所有的覆盖率测试功能集成,并提供VeraLite、CycleC等智能验证方法。

VCS 和Scirocco也支持混合语言仿真。

VCS和Scirocco都集成了Virsim图形用户界面,它提供了对模拟结果的交互和后处理分析。

SciroccoScirocco是迄今为止性能最好的VHDL模拟器,并且是市场上唯一为SoC验证度身定制的模拟工具。

它与VCS一样采用了革命性的模拟技术,即在同一个模拟器中把节拍式模拟技术与事件驱动的模拟技术结合起来。

Scirocco的高度优化的VHDL编译器能产生有效减少所需内存,大大加快了验证的速度,并能够在一台工作站上模拟千万门级电路。

这一性能对要进行整个系统验证的设计者来说非常重要。

VeraVera验证系统满足了验证的需要,允许高效、智能、高层次的功能验证。

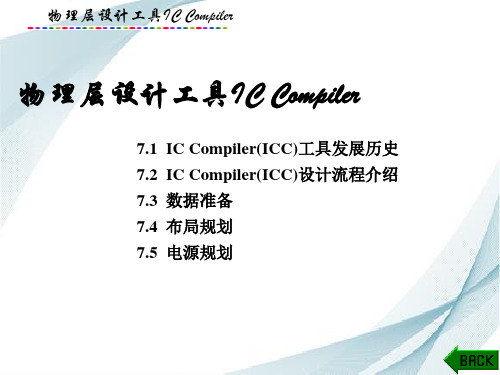

集成电路EDA与验证技术课件:物理层设计工具IC Compiler

物理层设计工具IC Compiler

2.设置逻辑库 ICC中针对逻辑库的设置主要是search_path, target_library,link_library这三个系统变量及命令 set_min_library。其中search_path是一个查找目录,需要包 含所有逻辑库文件所在的目录,这样在设置targe_library和 link_library中的db文件时,只需文件名即可,不需要再加上 其存放的路径。

物理层设计工具IC Compiler

6.读入SDC文件 前面已经介绍过,门级网表只是描述了设计中各个单元 之间的电路连接关系,SDC文件则是保证电路功能正确运行 的约束文件。该步骤就是运行命令行,将SDC文件读入该设 计所使用的命令:

read_sdc $sdc_file check_timing

7.6 布局 7.7 时钟树综合 7.8 布线 7.9 芯片ECO与DFM 7.10 小结

பைடு நூலகம்

物理层设计工具IC Compiler

7.1 IC Compiler(ICC)工具发展历史

ICC与Encounter是两大EDA软件巨头博弈的产物。它们 的发展历史,也可以看作微电子EDA业界风云变幻的历史。

早在20世纪80年代后期,微电子EDA厂商即呈现出两 强对峙的局面:Synopsys基本垄断了前端技术,占有将近六 成市场;Cadence基本垄断了后端技术与验证技术,占有将 近八成的市场。

物理层设计工具IC Compiler

图7.9 读入设计网表

物理层设计工具IC Compiler

通过该步骤,设计的网表就读入到已经打开的 $my_mw_lib设计库中。Layout窗口就会将设计所要用到的 所有单元都堆在坐标原点处。读入设计网表之后的Layout窗 口如图7.10所示。

Synopsys IC Complier设计流程指导书_Basic Flow

1- 16

Shortcuts…

import_designs orca.v \ -format verilog \ -top ORCA_TOP

Format can be verilog, db, ddc

Replaces: read_verilog –netlist orca.v current_design ORCA_TOP uniquify link save_mw_cel –as ORCA_TOP

1- 1

Unit Objectives

After completing this unit, you should be able to: Create a Milkyway library to hold your design Read all necessary files required to run

DEF MW

1- 6

Unit Flow: From Setup to Output

Logical Data Setup Physical Data Setup

place_opt clock_opt route_opt

Analysis Output

1- 7

Logical Data

LLooggicicaal lDDaatata Physical Data

Unit 1 Unit 5 Unit 2 Unit 3 Unit 6 Unit 7

1- 4

Placement, CTS, Routing with Optimizations

Gate-Level Netlist

IC Compiler

IP Optional: Floorplan

Placed, Routed & Optimized Design with Clock Trees

【极术公开课】新一代布局总线系统IC Compiler II 初识

极术公开课本PPT由极术社区提供,如需要观看回放请前往极术社区1Confidential © 2019 Arm China移知|半导体教育领航者初识ICC21.为什么学ICC22.NDM 与ICC23.融合技术CONTENTS为什么要学ICC2◼设计规模的挑战◼多电源域◼多电压域◼多模式◼先进工艺的挑战FINFETFDSOI◼先进工艺的挑战不断涌现的新的概念CCS NLDM OCV AOCV POCV LVF ECSM MCMMDoublepattern◼两个方向◼在原有的框架基础上进行改进◼稳定性◼学习成本低◼后期效果差◼重新设计新的框架◼学习成本提高◼初期的阵痛◼PPA 差◼bug 多◼后期效果好EDA 工具的发展ICCICCIIICCII vs ICC◼学ICC还是学ICCII?◼2014年, ICCII量产版正式发布(建议ICC)◼2020年,ICCII已经完善了6年(建议ICCII)◼Fusion Compiler=DCII+ICCII◼目前不建议◼PR部分完全与ICCII相同,脚本完全一样。

◼数据结构与ICCII一致NDM与ICCIINDM◼New Data Model:统一的数据结构◼Timing View◼包含timing power function等逻辑信息。

◼用于ICCII的时序分析,功耗分析及其优化◼Layout View◼物理形状信息(无连接信息),相当于GDS。

◼用于产生GDS◼Design View◼物理形状以及pin和连接信息◼可以用来产生Frame View◼可以用来产生flatten的网表,spef ◼Frame View◼物理信息的抽象形式。

◼进行PR优化时使用。

◼提高运行速度block library◼Design view (.design) –a complete physical view that contains the full designinformation of the cell, including placed block instances and routed nets. This is the default view type◼Frame view (.frame) –a limited physical view that contains only the information needed to perform placement of the block as an instance and routing to the ports of the instance: the block outline, pins, via regions, and routing blockages.◼Abstract view (.abstract) –a simplified view that contains only the interface information of a subdesign, used for placement and timing analysis at the next higher level of the design.◼Outline view (.outline) –a simplified view of a large child block that contains only the hierarchy information, without nets or leaf-level library cells, used for floorplan creation.新的基础架构◼ICCII是基于新的框架结构,用新的面向对象语言重写。

Avaya IC安装说明

Avaya IC安装环境说明Avaya IC组件说明在安装部署Avaya IC产品时,有多种配置和部署的方式。

一个典型的配置包含以下多个组件:Avaya IC core serversAvaya IC Design & Administration ToolsAgent interfacesAvaya Computer Telephony for ICWeb ManagementAvaya Email ManagementAvaya Business Advocate for Avaya ICAvaya Content AnalyzerAvaya IC Client Software Development KitAvaya IC core serversAvaya IC core servers 是Avaya IC产品的核心结构,用于管理和控制各个模块组件之间的通讯,管理路由策略。

Avaya IC core servers管理的以下组件间的通讯:●Telephony equipment,例如:ACD、PBX、IVR●Internet applications,例如:Web、Email、VOIP应用●数据库●Avaya IC administrative tools●Avaya IC client applicationsAvaya IC Design & Administration ToolsAvaya IC Design & Administration tools包含以下组件:●IC Manager●Avaya Workflow Designer●Avaya Database DesignerIC ManagerIC Manager是一个管理员使用的程序,可以用来监视IC中的各个服务状态并进行配置和管理。

联络中心的业务主管和系统管理员可以使用IC Manager完成以下工作:●对Agent、服务和设备进行添加、修改、删除●对IC中的服务进行配置、启动、停止●监视各个服务、Agent和设备的状态Avaya Workfl ow DesignerAvaya Workflow Designer是一个工作流客户化工具。

ic软件安装操作说明

收费管理软件安装方法软件安装说明:一、安装SQL SERVER数据库:1、首先安装SQL SERVER数据库个人版:双击光盘中的“SQLSERVER数据库个人版”文件夹---------然后双击AUTORUN.EXE自动运行:2、随之点击“安装SQL SERVER2000组件”---依次点击“安装操作服务器”,此时弹出如下界面3、请点击下一步:注:(如果提示:以前的某个程序在安装计算机上创建挂起的文件操作,运行安装程序前必须重起,请退出软件安装,打开光盘中“SQL安装提示挂起一键修复”,双击此图标:,然后弹出下图对话框:点“开始修复”。

之后再从第一步开始安装SQL SERVER个人版。

)4、依次再点“下一步”然后依次点击下一步即可。

点击下一步后出现下图,注意:下边姓名和公司显示的“微软用户和微软中国”,那是默认的。

这里不需要改,不同的计算机系统出现的都不一样。

不用管它显示什么,只要点击下一步即可!5、在安装过程中建议安装路径最好不要安装在电脑C盘下(系统盘)。

将其更改为其它盘符。

如图:在此安装类型中点击“浏览”----将C改为D或是E等其它盘符。

如图:将上图选中的C改为D然后点确定。

程序文件和数据文件都要改。

如下图:然后下一步;6、其中两步需要设置(1)设置为本地系统帐户如下图:然后点击下一步(2)设置为“混合模式”。

点击“空密码(不推荐)”------直接点下一步则安装成功。

如下图程序会弹出安装进度,请等待,直至提示成功!二、安装收费管理系统1、SQL SERVER安装完成后,点击电脑左下角的“开始”---所有程序---Microsoft SQL Server2000---服务管理器—点开始/继续:如图:2、安装收费管理软件:打开安装光盘—双击“IC收费管理系统V3.1.0.1”(或者在光盘启动后点安装IC收费管理系统)如下图所示点“安装IC收费管理系统”---下一步----同意协议---一直点击下一步直到提示完成。

intel11.1 编译器安装过程

intel11.1编译器安装标准文档1.1.安装Intel编译器版本:11.1.059 (在一台机器上面执行编译,其他机器直接拷贝)安装包位于/public/soucecode目录下,有三个文件:intel.lic、l_cproc_p_11.1.059_intel64.tgz、l_cprof_p_11.1.059_intel64.tgz。

附注:安装版本为11.1.059。

为了能成功安装,我们先要声明一个临时变量指向license的存放目录,以便安装时的license是可用的。

export INTEL_LICENSE_FILE=/public/sourcecode/a)安装intel C 编译器i.tar -zxvf l_cproc_p_11.1.059_intel64.tgzii.cd l_cproc_p_11.1.059_intel64/b)开始安装i. ./install.shii.在除下三个地方需要修改外,其它一律回车即可。

输入2回车输入2回车输入/public/software/intel/Compiler/11.1/059回车。

c)按同样的过程安装Fortran编译器,安装包为l_cprof_p_11.1.059_intel64.tgz。

d)安装完成后,设置环境变量,设置license filecp /public/software/intel/Compiler/11.1/059/bin/intel64/if*sh/etc/profile.d/cp /public/software/intel/Compiler/11.1/059/bin/intel64/ic*sh/etc/profile.d/cp/public/software/intel/Compiler/11.1/059/mkl/tools/environment/mklvarsem64t*sh /etc/profile.d/source /etc/profile.d/iccvars_intel64.shsource /etc/profile.d/ifortvars_intel64.shsource /etc/profile.d/mklvarsem64t*.shmkdir -p /public/software/intel/Compiler/11.1/059/licensescp intel.lic /public/software/intel/Compiler/11.1/059/licensesa)同步环境变量脚本/public/software/setup_cluster --sync_file /etc/profile.d/icc*sh/etc/profile.d/ifort*sh /etc/profile.d/mkl*sh。

iar安装教程

iar安装教程

以下是关于IAR安装的简易教程,不包含任何标题以防止重复:

1. 首先,下载IAR安装程序,并将其保存到本地计算机上。

2. 打开下载的安装程序,并按照提示进行安装。

接受许可协议并选择安装位置。

3. 在安装选项页面上,选择所需的组件进行安装。

您可以选择完整安装或自定义安装。

如果您只需要特定的组件,建议选择自定义安装以减少安装空间。

4. 继续进行安装,等待安装程序完成所有必要的文件复制和配置。

5. 完成安装后,您可以在开始菜单或桌面上找到IAR软件的快捷方式。

6. 打开IAR软件,并根据需要进行注册或激活。

根据您购买的许可证类型,可能需要提供许可证密钥或进行在线激活。

7. 完成注册或激活后,您可以开始使用IAR进行开发。

注意:以上步骤仅适用于一般情况,您可能会遇到特定于操作系统或IAR版本的差异。

在安装过程中,始终阅读并遵循提供的安装说明。

IC消费系统快速安装步骤说明

IC消费系统快速安装步骤说明一、安装数据库并运行1、安装SQL SERVER 2000首先将软件光盘放入光驱,打开数据库SQL server 2000文件夹,运行AUTORUN.EXE。

(如下图)1、单击系统弹出2、3、单击系统弹出4、5、单击【下一步】系统弹出6、7、选择单击【下一步】系统弹出8、9、单击【下一步】系统弹出10、11、12、输入SN文本上的序列号:GXKQH-VGTD2-K8QC4-9H3PK-HY9XW13、14、15、单击【下一步】系统弹出16、17、单击【下一步】系统弹出18、19、单击【下一步】系统弹出20、21、单击【下一步】系统弹出22、23、选择24、选择25、单击【下一步】系统弹出26、27、单击【下一步】直到系统安装完成28、完成安装后先运行数据库:点开始——程序——Microsoft SQL Server——服务管理器——点开始运行,运行成功系统右下角会显示图标。

二、安装消费系统软件从光盘中选择IC消费管理软件的执行程序,出现:单击【下一步】系统弹出先选择安装目录(非系统盘),一直单击【下一步】系统弹出最后完成安装。

三、建立消费系统数据库(以上操作完成后,打开桌面消费系统图标会提示第一次运行要建库,直接点建库就可以了)选择,单击打开提示单击提示四、安装USB设备驱动后,把发卡器与消费机连接电脑(检查设备管理器下,新插入设备驱动是否安装成功)如上图举例:当插入发卡器后:右击“我的电脑--管理--设备管理器--端口-”此时端口为3 (打开消费系统软件--高级设置--对应项发卡器串口号填写3 ,并保存)。

(当发卡器插到电脑上时,识别到的端口号是随机的,请根据实际情况,对应设置。

因普通消费机用RS232通讯,为非即插即用设备,固RS232通讯COM口不会消失,要手动填写对应端口号)五、登录消费系统软件设置参数1.弹出登录框输入默认密码123 进入软件,打开高级设置项,首先设置硬件通讯端口号:消费机串口号:如果消费机通过485转换器连接,且插入电脑上的COM1口,则消费机串口号为1; 如果消费机通过485接上USB转232转换器连接,则消费机串口号为USB转232在设备管理器下所占用的端口号,务必设置对应。

Design Complier 使用详解

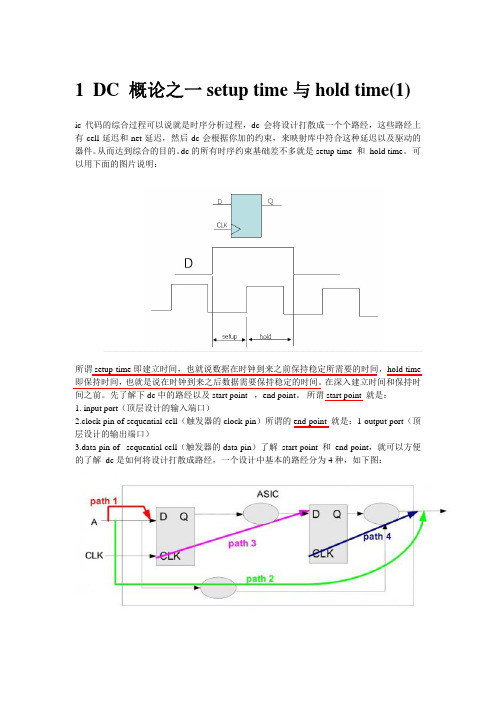

1DC 概论之一setup time与hold time(1)ic代码的综合过程可以说就是时序分析过程,dc会将设计打散成一个个路经,这些路经上有cell延迟和net延迟,然后dc会根据你加的约束,来映射库中符合这种延迟以及驱动的器件。

从而达到综合的目的。

dc的所有时序约束基础差不多就是setup time 和 hold time。

可以用下面的图片说明:所谓setup time即建立时间,也就说数据在时钟到来之前保持稳定所需要的时间,hold time 即保持时间,也就是说在时钟到来之后数据需要保持稳定的时间。

在深入建立时间和保持时间之前。

先了解下dc中的路经以及start point ,end point。

所谓start point 就是:1. input port(顶层设计的输入端口)2.clock pin of sequential cell(触发器的clock pin)所谓的end point 就是:1 output port(顶层设计的输出端口)3.data pin of sequential cell(触发器的data pin)了解 start point 和 end point,就可以方便的了解 dc是如何将设计打散成路经,一个设计中基本的路经分为4种,如下图:path1:input port to data pin of sequential cellpath2:input port to output portpath3:clock pin to data pin of next sequential cellpath4:clock pin to output port所有的设计也就这四种类型的路径。

另外一种就是带反馈的,也就是本身的clock pin to data pin 。

有了路径的概念之后,我们可以分析更复杂的setup time 和 hold time 。

dc中对于建立时间的分析是基于路径的最大延迟;而对于保持时间的分析是基于路径的最小延迟。

OTP开发工具

aP89W20OTP 系列 IC 开发工具操作指南广州市瑞华电子有限公司广州市天河路561号新赛格电子城2032柜http://www.isdapi.comz简述:aP89W20 烧录工具包括一个烧录器(PCB NO.:aP89W20)烧录工具和一套烧录软件(aP89W20.exe),可以烧录aP89xxx三个系列共 9 种型号的IC:其中,可直接烧录的IC(短秒数系列):-aP89010-aP89021-aP89042(请将短Texttool下方短路帽断开)需要通过短接跳线帽进行烧录的IC(5V 系列):-aP8910A-aP8921A-aP8942A(请将短Texttool下方短路帽合上)需要通过转接座(PCB NO.24D2D20)烧录的IC(长秒数系列):-aP89085-aP89170-aP89341(请将短Texttool下方短路帽断开)各种IC在烧录器上的放置方法可能会有所不同,具体请参照本指南的最后一部分的IC放置示意图。

说明:aP89W20 烧录工具主要有两大功能:编译和烧录。

-编译(complier):制作烧录所需要的文件(.DPM),包括声音的排列,IC功能和工作方式的设定等信息,都包含在这个文件内。

-烧录(writer):将编译好的文件(.DPM)烧入IC内,计算机通过并口与烧录器连接,由计算机发烧录指令,数据通过并口传到烧录器来进行烧录。

z安装指南:烧录器aP89W20与计算机连接时,无需对计算机进行特别的设置,即插即用。

一.连接方法:1. 通过并口线连接到计算机的并口(Print Port)。

2. 通过USB线将烧录器上的USB口与计算机的USB口连接起来;或者,直接将外加电源(+6V)烧录器的DC 接口;二者任选其一。

注意,计算机USB口的使用,只是对烧录器进行供电(+5V)而已,并不涉及数据传输,如果计算机连接的USB设备比较多,建议使用外加直流电源,否则可能会出现供电不足,从而导致烧录不完全的现象;另外,不要将USB和外加电源同时连接到烧录器,否则有可能会损坏计算机的USB口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

synopsys ic compiler (v2005.linux)是基于Galaxy设计平台开发的产品。

主要的工具有:LEDALEDA是可编程的语法和设计规范检查工具,它能够对全芯片的VHDL和Verilog描述、或者两者混合描述进行检查,加速SoC的设计流程。

LEDA预先将IEEE可综合规范、可仿真规范、可测性规范和设计服用规范集成,提高设计者分析代码的能力VCSVCS是编译型Verilog模拟器,它完全支持OVI标准的Verilog HDL语言、PLI和SDF。

VCS具有目前行业中最高的模拟性能,其出色的内存管理能力足以支持千万门级的ASIC设计,而其模拟精度也完全满足深亚微米ASIC Sign-Off的要求。

VCS结合了节拍式算法和事件驱动算法,具有高性能、大规模和高精度的特点,适用于从行为级、RTL到Sign-Off等各个阶段。

VCS已经将CoverMeter中所有的覆盖率测试功能集成,并提供VeraLite、CycleC 等智能验证方法。

VCS和Scirocco也支持混合语言仿真。

VCS和Scirocco都集成了Virsim 图形用户界面,它提供了对模拟结果的交互和后处理分析。

SciroccoScirocco是迄今为止性能最好的VHDL模拟器,并且是市场上唯一为SoC验证度身定制的模拟工具。

它与VCS一样采用了革命性的模拟技术,即在同一个模拟器中把节拍式模拟技术与事件驱动的模拟技术结合起来。

Scirocco的高度优化的VHDL编译器能产生有效减少所需内存,大大加快了验证的速度,并能够在一台工作站上模拟千万门级电路。

这一性能对要进行整个系统验证的设计者来说非常重要。

VeraVera验证系统满足了验证的需要,允许高效、智能、高层次的功能验证。

Vera验证系统已被Sun、NEC、Cisco等公司广泛使用以验证其实际的产品,从单片ASIC到多片ASIC 组成的计算机和网络系统,从定制、半定制电路到高复杂度的微处理器。

Vera验证系统的基本思想是产生灵活的并能自我检查的测试向量,然后将其结合到test-bench中以尽可能充分测试所设计的电路。

Vera验证系统适用于功能验证的各个层次,它具有以下特点:与设计环境的紧密集成、启发式及全随机测试、数据及协议建模、功能代码覆盖率分析。

Physical CompilerPhysical Compiler解决0.18微米以下工艺技术的IC设计环境,是Synopsys物理综合流程的最基本的模块,它将综合、布局、布线集成于一体,让RTL设计者可以在最短的时间内得到性能最高的电路。

通过集成综合算法、布局算法和布线算法。

在RTL到GDS II 的设计流程中,Physical Compiler向设计者提供了可以确保即使是最复杂的IC设计的性能预估性和时序收敛性。

Clocktree CompilerClockTree Compiler是嵌入于Physical Compiler的工具,它帮助设计者解决深亚微米IC 设计中时钟树的时序问题。

它不仅能够简化设计流程,而且可以极大的提高时钟树的质量:对于插入延时有5%-20%的改进,对时钟偏移有5%-10%的改进。

DC-ExpertDC得到全球60多个半导体厂商、380多个工艺库的支持。

据最新Dataquest的统计,Synopsys的逻辑综合工具占据91%的市场份额。

DC是十二年来工业界标准的逻辑综合工具,也是Synopsys最核心的产品。

它使IC设计者在最短的时间内最佳的利用硅片完成设计。

它根据设计描述和约束条件并针对特定的工艺库自动综合出一个优化的门级电路。

它可以接受多种输入格式,如硬件描述语言、原理图和网表等,并产生多种性能报告,在缩短设计时间的同时提高设计性能。

DC Ultra对于当今所有的IC设计,DC Ultra 是可以利用的最好的综合平台。

它扩展了DC Expert 的功能,包括许多高级的综合优化算法,让关键路径的分析和优化在最短的时间内完成。

在其中集成的Module Compiler数据通路综合技术,DC Ultra利用同样的VHDL/Verilog流程,能够创造处又快又小的电路。

DFT CompilerDFT Compiler提供独创的―一遍测试综合‖技术和方案。

它和Design Compiler 、Physical Compiler系列产品集成在一起的,包含功能强大的扫描式可测性设计分析、综合和验证技术。

DFT Compiler可以使设计者在设计流程的前期,很快而且方便的实现高质量的测试分析,确保时序要求和测试覆盖率要求同时得到满足。

DFT Compiler同时支持RTL级、门级的扫描测试设计规则的检查,以及给予约束的扫描链插入和优化,同时进行失效覆盖的分析。

Power CompilerPower Compiler?提供简便的功耗优化能力,能够自动将设计的功耗最小化,提供综合前的功耗预估能力,让设计者可以更好的规划功耗分布,在短时间内完成低功耗设计。

Power Compiler嵌入Design Compiler/Physical Compiler之上,是业界唯一的可以同时优化时序、功耗和面积的综合工具。

FPGA Compiler IIFPGA Compiler II是一个专用于快速开发高品质FPGA产品的逻辑综合工具,可以根据设计者的约束条件,针对特定的FPGA结构(物理结构)在性能与面积方面对设计进行优化,自动地完成电路的逻辑实现过程,从而大大降低了FPGA设计的复杂度。

FPGA Compiler II 利用了特殊的结构化算法,结合高层次电路综合方法,充分利用复杂的FPGA结构将设计输入综合成为满足设计约束条件,以宏单元或LUT为基本模块的电路,可以多种格式输出到用户的编程系统中。

FPGA Compiler II为FPGA设计者提供高层次设计方法,并为IC设计者用FPGA做样片而最后转换到ASIC提供了有效的实现途径。

Prime Power动态功耗的门级仿真和分析的工具,可精确分析基于门级的设计的功耗问题,逐渐成为ASIC 和对功耗要求较高的结构定制产品(袖珍计算机和通讯设备)设计者的高级解决方案。

PrimeTimePrimeTime® 是针对复杂、百万门芯片进行全芯片、门级静态时序分析的工具。

PrimeTime可以集成于逻辑综合和物理综合的流程,让设计者分析并解决复杂的时序问题,并提高时序收敛的速度。

PrimeTime是众多半导体厂商认可的、业界标准的静态时序分析工具。

FormalityFormality是高性能、高速度的全芯片的形式验证:等效性检查工具。

它比较设计寄存器传输级对门级或门级对门级来保证它没有偏离原始的设计意图。

在一个典型的流程中,用户使用形式验证比较寄存器传输级源码与综合后门级网表的功能等效性。

这个验证用于整个设计周期,在扫描链插入、时钟树综合、优化、人工网表编辑等等之后,以便在流程的每一阶段都能在门级维持完整的功能等效。

这样在整个设计周期中就不再需要耗时的门级仿真。

将Formality和PrimeTime这两种静态验证方法结合起来,一个工程师可以在一天内运行多次验证,而不是一天或一周只完成一次动态仿真验证。

SaberSaber是Synopsys公司开发并于1987年推出的模拟及混合信号仿真软件,被誉为全球最先进的系统仿真软件,也是唯一的多技术、多领域的系统仿真产品。

与传统仿真软件不同,Saber在结构上采用硬件描述语言(MAST)和单内核混合仿真方案,并对仿真算法进行了改进,使Saber仿真速度更快、更加有效、应用也越来越广泛。

应用工程师在进行系统设计时,建立最精确、最完善的系统仿真模型是至关重要的。

Saber可同时对模拟信号、事件驱动模拟信号、数字信号以及模数混合信号设备进行仿真。

利用Synopsys公司开发的Calaversas算法,Saber可以确保同时进行的两个仿真进程都能获得最大效率,而且可以实现两个进程之间的信息交换,并在模拟和数字仿真分析之间实现了无缝联接。

Saber适用领域广泛,包括电子学、电力电子学、电机工程、机械工程、电光学、光学、水利、控制系统以及数据采样系统等等。

只要仿真对象能够用数学表达式进行描述,Saber就能对其进行系统级仿真。

在Saber中,仿真模型可以直接用数学公式和控制关系表达式来描述,而无需采用电子宏模型表达式。

因此,Saber可以对复杂的混合系统进行精确的仿真,仿真对象不同系统的仿真结果可以同时获得。

为了解决仿真过程中的收敛问题,Saber内部采用5种不同的算法依次对系统进行仿真,一旦其中某一种算法失败,Saber 将自动采用下一种算法。

通常,仿真精度越高,仿真过程使用的时间也越长。

普通的仿真软件都不得不在仿真精度和仿真时间上进行平衡。

Saber采用其独特的设计,能够保证在最少的时间内获得最高的仿真精度。

Saber工作在SaberDesigner图形界面环境下,能够方便的实现与Cadence Design System和Mentor Graphics的集成。

通过上述软件也可以直接调用Saber进行仿真。

JupiterXT芯片设计者在层次化物理设计环境中完成从门级网表到布局布线收敛的重要工具,可以帮助您将Timing、Area和Power与您的设计进行匹配,JupiterXT通过下面的方法来管理和优化您的设计:1、物理版图的层次化管理2、精确的面积、寄生参数和时序估计3、层次化布局布线流程中,精确的子模块时序加载AstroAstro是Synopsys为超深亚微米IC设计进行设计优化、布局、布线的设计环境。

Astro 可以满足5千万门、时钟频率GHz、在0.10及以下工艺线生产的SoC设计的工程和技术需求。

Astro高性能的优化和布局布线能力主要归功于Synopsys在其中集成的两项最新技术:PhySiSys和Milkyway DUO结构。

Design VisionSynopsys综合环境的图形界面,在通用技术层和门级进行设计浏览和分析的分析工具。

Mars-railMars-Rail用于功耗和电漂移的分析和优化,以完成低功耗高可靠性的设计。

它将自动在Apollo-II的布局布线中起作用。

Mars-xtalkMars-Xtalk可以进行充分的串扰分析,并能够进行防止串扰发生的布局和布线,解决超深亚微米芯片设计中的信号完整性问题。

CosmosLE/SESynopsys的Cosmos解决方案可以进行自前向后的混合信号、全定制IC设计。

它可以很好的处理自动化的设计流程和设计的灵便性,使得设计周期可以缩短数周甚至几个月。

CosmosLE提供了一个基于Milkyway数据库的完整物理IC设计环境,同时可以无缝集成,动态交互操作所有Synopsys公司领先的物理设计工具。