Verilog语言实现设计交通灯控制器

基于VerilogHDL的通行时间可变的交通灯控制器

通行时间可变的交通灯控制器设计module tr1(ng,clk,reset,resets,emergency,lighta,lightb,seg,select); input ng,clk,reset,emergency,resets;output[6:0]seg;//显示用的output[3:0] lighta,lightb;//a是主干道,b是支干道output [3:0] select;//选择那一个管子进行显示reg clk1,clk2;//clk1要5HZ clk2要几千HZreg [3:0] select;reg tim1,tim2;//这是看你的等有没有变过颜色的控制信号reg [1:0] cont;reg[2:0]state1,state2,ste;两个控制颜色变化状态的信号。

reg[3:0]lighta,lightb;//a是主干道,b是支干道reg[3:0]num;//译码器是根据这个东西来译码的reg [35:0] fout;reg[6:0]seg;//显示reg[7:0] numa,numb;reg[7:0] red1,red2,green1,green2,yellow1,yellow2,left1,left2; always @(ng )if(!ng)begin //设置计数初值green1 <=8'b00110000;//30Sred1 <=8'b01010001;//51Syellow1<=8'b00000011;//3Sleft1 <=8'b00010101; //15Sgreen2 <=8'b00110000;//30Sred2 <=8'b01010001;//51Syellow2<=8'b00000011;//3Sleft2 <=8'b00010101; //15Sendalways @ (posedge clk)beginif (fout==36'b111111111111111111111111111111111111)fout<=0;else begin fout<=fout+1;clk1=fout[23];5HZclk2=fout[13];几千HZendendalways @(posedge clk1 )beginif(reset) //复位与特殊情况控制这是主干道的复位beginlighta<=4'b1000;//lighta是主干道的交通灯,lightb是支干道的交通灯,1000是红灯,0100是直行绿灯,0010是黄灯,0001是左转绿灯numa<=red1; //主干道的数码管从红灯开始记state1<=0;//这时候灯变化的控制信号为0endelse if(emergency)//紧急情况beginlighta<=4'b1000;//主干道红了numa<=red1;//计时也从红灯记endelse if(ng)//这下开始正常工作了begin //使能有效开始控制计数if(!tim1) //你有没有变过颜色啊?没有?那开始变颜色吧。

交通信号灯控制器的verilog实现

H a r b i n I n s t i t u t e o f T e c h n o l o g yV e r i l o g实验报告(2)实验内容:交通信号灯控制器班级:姓名:学号:哈尔滨工业大学2015年6月一、功能描述本设计利用Verilog HDL 语言,对一个十字路口的交通信号灯进行控制,可控制4个路口的红、黄、绿、左转四盏信号灯,让其按特定的规律进行变化。

并通过ModelSim软件对系统进行了仿真。

仿真结果表明系统可自动实现十字路口红绿灯及左转弯信号灯的控制。

实现设计目标如下:(1)设计一个十字路口的交通灯控制电路,每条路配有红、黄、绿、左转四盏交通信号灯。

通过控制器对四个路口的四组交通灯的状态实现自动循环控制;(2)实现两主干道车辆交替运行,每次通行直行时间为30 秒;左转时间为10秒,右转不受信号灯控制。

(3)黄灯作为绿灯转为左转灯,左转灯转为红灯的过渡信号灯,过渡时间为5s。

(4)系统设有总复位开关,可在任意时间对系统进行复位。

二、设计方案1.设计思路我们对图1所示的十字路口进行设计,路口A和路口C的车辆同时行驶,路口B和路口D的车辆同时行驶,所以虽然要控制4组信号灯,但其实它们可以俩俩合并,这样大大简化了设计。

由于我们采用自动控制方式,两个方向的灯按照顺序依次交替循环显示,每种灯亮的时间结合实际生活合理设定。

系统设有复位开关,可在任意时间内对系统进行复位。

图1 十字路口示意图由以上分析可知,该系统可视为一个状态机,而且共有8种状态,如表1所示。

表1 交通灯状态示意表由上表我们还可以得到状态转换图,如图2所示:图2 状态转移示意图该状态机共有两个输入信号rstn和clk,rstn为复位信号,当该信号为低电平时,状态机处于S0,且状态不发生改变。

当rstn为高电平时,这8个状态依次按时间顺序发生变化,每个状态保持多长时间由clk信号控制。

三、关键代码1.我们通过宏定义来设置每个状态保持的时间,这样既增强了代码的可读性,又方便以后的更改。

verilog 分频器,30s计数器及交通灯控制器设计

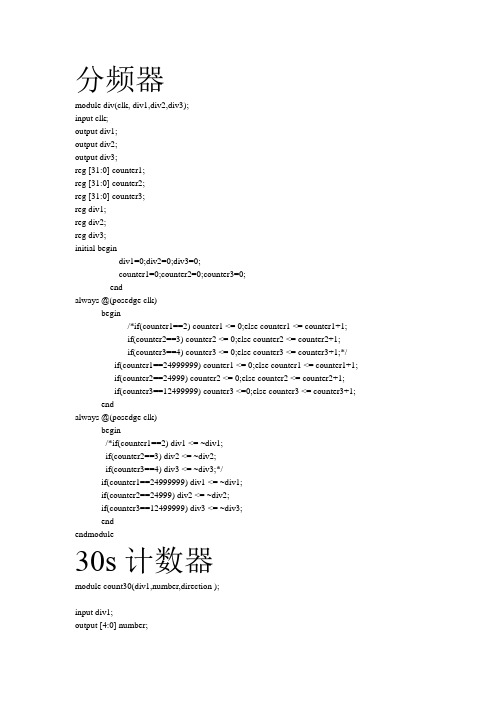

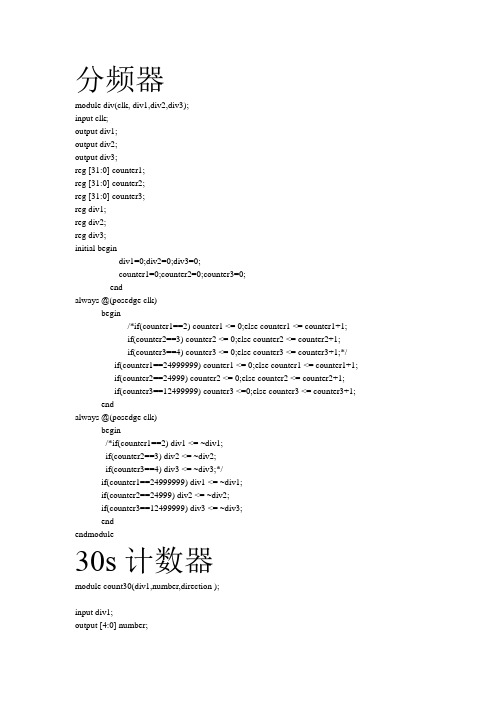

分频器module div(clk, div1,div2,div3);input clk;output div1;output div2;output div3;reg [31:0] counter1;reg [31:0] counter2;reg [31:0] counter3;reg div1;reg div2;reg div3;initial begindiv1=0;div2=0;div3=0;counter1=0;counter2=0;counter3=0;endalways @(posedge clk)begin/*if(counter1==2) counter1 <= 0;else counter1 <= counter1+1;if(counter2==3) counter2 <= 0;else counter2 <= counter2+1;if(counter3==4) counter3 <= 0;else counter3 <= counter3+1;*/ if(counter1==24999999) counter1 <= 0;else counter1 <= counter1+1;if(counter2==24999) counter2 <= 0;else counter2 <= counter2+1;if(counter3==12499999) counter3 <=0;else counter3 <= counter3+1;endalways @(posedge clk)begin/*if(counter1==2) div1 <= ~div1;if(counter2==3) div2 <= ~div2;if(counter3==4) div3 <= ~div3;*/if(counter1==24999999) div1 <= ~div1;if(counter2==24999) div2 <= ~div2;if(counter3==12499999) div3 <= ~div3;endendmodule30s计数器module count30(div1,number,direction );input div1;output [4:0] number;reg [4:0] number;reg direction;initialbegindirection=0;number=30;endalways@(posedge div1)beginif(number==0)begindirection<=~direction;number<=30;endelse number<=number-1;endendmodule控制器module moniter( div3,number,direction,eastred,eastyellow,eastgreen,northred,northyellow,northgreen );input div3;input direction;input [4:0]number;output eastred;output eastyellow;output eastgreen;output northred;output northyellow;output northgreen ;//wire [4:0] number;reg eastred;reg eastyellow;reg eastgreen;reg northred;reg northyellow;reg northgreen ;initial begineastred<=1;eastgreen<=0;northred<=1;northgreen<=0;northyellow<=eastyellow<=0;endalways @(posedge div3)beginif(number<=3)beginif (direction==0) eastyellow<=~eastyellow;else northyellow<=~northyellow;endelse begin eastyellow<=0;northyellow<=0;end endalways @(number )/*beginif(number==30&&direction==0)begin eastred<=1;eastgreen<=0;northred<=1;northgreen<=0;end*/if (number>2'b00010&&direction==0)begineastred<=0;eastgreen<=1;northred<=1;northgreen<=0;endelse if(number<3&&direction==0)begineastred<=0;eastgreen<=0;northred<=1;northgreen<=0;endelse if(number>2&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=1;endelse if(number<3&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=0;endendmodule译码器module yimaqi( clk,number,led1,led2);input clk;input [4:0] number;output [6:0] led1;output [6:0] led2;reg [6:0] led1;reg [6:0] led2;always @( number )begincase (number)5'b00000: begin led1 <= 7'b0000001; led2 <= 7'b0000001;end5'b00001: begin led1 <= 7'b0000001; led2 <= 7'b1001111;end5'b00010: begin led1 <= 7'b0000001; led2 <= 7'b0010010;end7'b0000110;end5'b00100: begin led1 <= 7'b0000001; led2 <= 7'b1001100;end5'b00101: begin led1 <= 7'b0000001; led2 <= 7'b0100100;end5'b00110: begin led1 <= 7'b0000001; led2 <= 7'b1100000;end5'b00111: begin led1 <= 7'b0000001; led2 <= 7'b0001111;end5'b01000: begin led1 <= 7'b0000001; led2 <= 7'b0000000;end5'b01001: begin led1 <= 7'b0000001; led2 <= 7'b0001100; end5'b01010: begin led1 <= 7'b1001111; led2 <= 7'b0000001;end5'b01011: begin led1 <= 7'b1001111; led2 <= 7'b1001111; end5'b01100: begin led1 <= 7'b1001111; led2 <= 7'b0010010;end5'b01101: begin led1 <= 7'b1001111; led2 <= 7'b0000110; end5'b01110: begin led1 <= 7'b1001111; led2 <= 7'b1001100;end5'b01111: begin led1 <= 7'b1001111; led2 <= 7'b0100100;end5'b10000: begin led1 <= 7'b1001111; led2 <= 7'b1100000;end5'b10001: begin led1 <= 7'b1001111; led2 <= 7'b0001111;end5'b10010: begin led1 <= 7'b1001111; led2 <= 7'b0000000;end5'b10011: begin led1 <= 7'b1001111; led2 <= 7'b0001100;end5'b10100: begin led1 <= 7'b0010010; led2 <= 7'b0000001;end5'b10101: begin led1 <= 7'b0010010; led2 <= 7'b1001111;end5'b10110: begin led1 <= 7'b0010010; led2 <= 7'b0010010;end5'b10111: begin led1 <= 7'b0010010; led2 <= 7'b0000110;end5'b11000: begin led1 <= 7'b0010010; led2 <= 7'b1001100;end7'b0100100;end5'b11010: begin led1 <= 7'b0010010; led2 <= 7'b1100000;end5'b11011: begin led1 <= 7'b0010010; led2 <= 7'b0001111;end5'b11100: begin led1 <= 7'b0010010; led2 <= 7'b0000000;end5'b11101: begin led1 <= 7'b0010010; led2 <= 7'b0001100;end5'b11110: begin led1 <= 7'b0000110; led2 <= 7'b0000001;enddefault: begin led1 <= 7'b0000000; led2 <= 7'b0000000;endendcaseendendmodulemodule dianzhen(direction,clk,div2,row,con);input div2;input clk;input direction;output[15:0] row;output[15:0] con;reg[15:0] row;reg[15:0] con;integer cnt,b;reg[15:0] r[48:0];initialbeginif (direction==0)begin// 丁r[0] <=16'b1111111111111111;r[1] <=16'b1011111111111111;r[2] <=16'b1011111111111111;r[3] <=16'b1011111111111111;r[4] <=16'b1011111111111111;r[5] <=16'b1011111111111011;r[6] <=16'b1011111111111101;r[7] <=16'b1000000000000011;r[8] <=16'b1011111111111111;r[9] <=16'b1011111111111111;r[10]<=16'b1011111111111111;r[11] <=16'b1011111111111111;r[12]<=16'b1011111111111111;r[13]<=16'b1011111111111111;r[14]<=16'b1011111111111111;r[15]<=16'b1111111111111111;// 乾r[16]<=16'b1101111111101111 ;r[17]<=16'b1101000000101111 ;r[18]<=16'b1101010101101111 ;r[19]<=16'b0000010101101111 ;r[20]<=16'b1101010100000000 ;r[21]<=16'b1101010101101111 ;r[22]<=16'b1101000000101111 ;r[23]<=16'b1101110111101111 ;r[24]<=16'b1111001111110011 ;r[25]<=16'b0000110111001101 ;r[26]<=16'b1010110110111101 ;r[27]<=16'b1110110101111101 ;r[28]<=16'b1110110011111101 ;r[29]<=16'b1110110111100001 ;r[30]<=16'b1110111111111011 ;r[31]<=16'b1111111111111111 ;// 全灭r[32]<=16'b1111111111111111;r[33]<=16'b1111111111111111;r[34]<=16'b1111111111111111;r[35]<=16'b1111111111111111;r[36]<=16'b1111111111111111;r[37]<=16'b1111111111111111;r[38]<=16'b1111111111111111;r[39]<=16'b1111111111111111;r[40]<=16'b1111111111111111;r[41]<=16'b1111111111111111;r[42]<=16'b1111111111111111;r[43]<=16'b1111111111111111;r[44]<=16'b1111111111111111;r[45]<=16'b1111111111111111;r[46]<=16'b1111111111111111;r[47]<=16'b1111111111111111;endelse if(direction==1)begin//1r[0] <=16'b 1111111111111111;r[1] <=16'b 1111111111111111;r[2] <=16'b 1111111111111111;r[3] <=16'b 1111111111111111;r[4] <=16'b 1111111111111111;r[5] <=16'b 1111011111111011;r[6] <=16'b 1111011111111011;r[7] <=16'b 1110000000000011;r[8] <=16'b 1111111111111011;r[9] <=16'b 1111111111111011;r[10]<=16'b 1111111111111111;r[11] <=16'b 1111111111111111;r[12]<=16'b 1111111111111111;r[13]<=16'b 1111111111111111;r[14]<=16'b 1111111111111111;r[15]<=16'b 1111111111111111;// 0r[16]<=16'b 1111111111111111;r[17]<=16'b 1111111111111111;r[18]<=16'b 1111111111111111;r[19]<=16'b 1111111111111111;r[20]<=16'b 1111111111111111;r[21]<=16'b 1111100000001111;r[22]<=16'b 1111011111110111;r[23]<=16'b 1110111111111011;r[24]<=16'b 1110111111111011;r[25]<=16'b 1111011111110111;r[26]<=16'b 1111100000001111;r[27]<=16'b 1111111111111111;r[28]<=16'b 1111111111111111;r[29]<=16'b 1111111111111111;r[30]<=16'b 1111111111111111;r[31]<=16'b 1111111111111111;// 9r[32]<=16'b 1111111111111111;r[33]<=16'b 1111111111111111;r[34]<=16'b 1111111111111111;r[35]<=16'b 1111111111111111;r[36]<=16'b 1111111111111111;r[37]<=16'b 1111100011111111;r[38]<=16'b 1111011101110011;r[39]<=16'b 1110111110111011;r[40]<=16'b 1110111110111011;r[41]<=16'b 1111011101110111;r[42]<=16'b 1111100000001111;r[43]<=16'b 1111111111111111;r[44]<=16'b 1111111111111111;r[45]<=16'b 1111111111111111;r[46]<=16'b 1111111111111111;r[47]<=16'b 1111111111111111;endendalways@(posedge clk )beginif (b==47)b<=0;else b<=b+1;endalways@(posedge div2)beginif(cnt==15)begincnt<=0;endelsecnt<=cnt+1;case(cnt)15: con<=16'b0000_0000_0000_0001; 14: con<=16'b0000_0000_0000_0010; 13: con<=16'b0000_0000_0000_0100; 12: con<=16'b0000_0000_0000_1000; 11: con<=16'b0000_0000_0001_0000; 10: con<=16'b0000_0000_0010_0000; 9: con<=16'b0000_0000_0100_0000; 8: con<=16'b0000_0000_1000_0000; 7: con<=16'b0000_0001_0000_0000; 6: con<=16'b0000_0010_0000_0000; 5: con<=16'b0000_0100_0000_0000; 4: con<=16'b0000_1000_0000_0000; 3: con<=16'b0001_0000_0000_0000; 2: con<=16'b0010_0000_0000_0000; 1: con<=16'b0100_0000_0000_0000; 0: con<=16'b1000_0000_0000_0000;endcasecase(cnt)0: row<=r[b+0];1: row<=r[b+1];2: row<=r[b+2];3: row<=r[b+3];4: row<=r[b+4];5: row<=r[b+5];6: row<=r[b+6];7: row<=r[b+7];8: row<=r[b+8];9: row<=r[b+9];10: row<=r[b+10];11: row<=r[b+11];12: row<=r[b+12];13: row<=r[b+13];14: row<=r[b+14];15: row<=r[b+15];endcaseendendmodule。

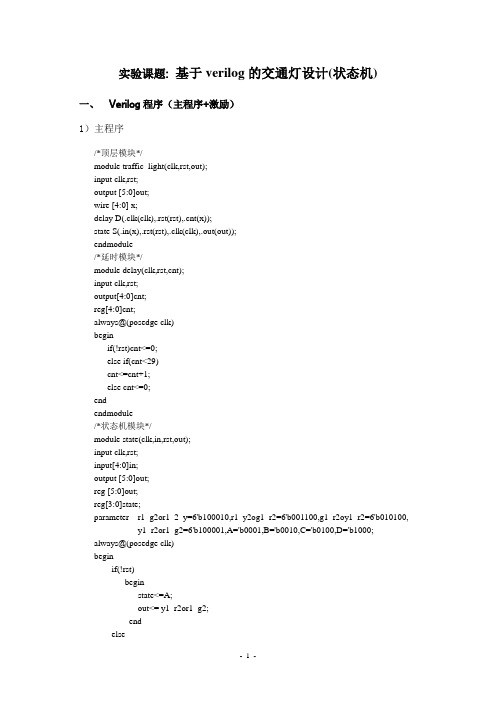

基于verilog的交通灯设计(状态机)

实验课题:基于verilog的交通灯设计(状态机)一、Verilog程序(主程序+激励)1)主程序/*顶层模块*/module traffic_light(clk,rst,out);input clk,rst;output [5:0]out;wire [4:0] x;delay D(.clk(clk),.rst(rst),.cnt(x));state S(.in(x),.rst(rst),.clk(clk),.out(out));endmodule/*延时模块*/module delay(clk,rst,cnt);input clk,rst;output[4:0]cnt;reg[4:0]cnt;always@(posedge clk)beginif(!rst)cnt<=0;else if(cnt<29)cnt<=cnt+1;else cnt<=0;endendmodule/*状态机模块*/module state(clk,in,rst,out);input clk,rst;input[4:0]in;output [5:0]out;reg [5:0]out;reg[3:0]state;parameter r1_g2or1_2_y=6'b100010,r1_y2og1_r2=6'b001100,g1_r2oy1_r2=6'b010100, y1_r2or1_g2=6'b100001,A='b0001,B='b0010,C='b0100,D='b1000;always@(posedge clk)beginif(!rst)beginstate<=A;out<= y1_r2or1_g2;endelsebegincase(state)A: beginif(in<25)state<=A;elsebeginstate<=B;out<=r1_g2or1_2_y;endendB: beginif(in>24)state<=B;elsebeginstate<=C;out<=r1_y2og1_r2;endendC: beginif(in<25)state<=C;elsebeginstate<=D;out<=g1_r2oy1_r2;endendD: beginif(in>24)state<=D;elsebeginstate<=A;out<=y1_r2or1_g2;endendendcaseendendendmodule2)激励module test;reg clk,rst;wire [5:0]out;traffic_light test(clk,rst,out);initialbeginclk='b1;forever #5 clk=~clk;endinitialbeginrst='b0;#10 rst='b1;#500 rst='b0;#10 rst='b1;endendmodule二、实验波形图截图三、波形分析输出out[5:0]分别对应:out[5]:主干道红灯out[4]:主干道黄灯out[3]:主干道绿灯out[2]:支干道红灯out[1]:支干道黄灯out[0]:支干道绿灯初始状态为:主干道红灯亮,支干道绿灯亮。

用verilog语言编写交通灯程序

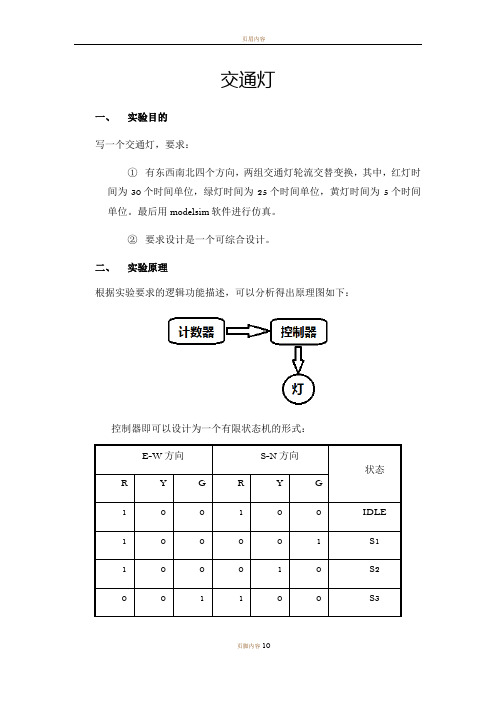

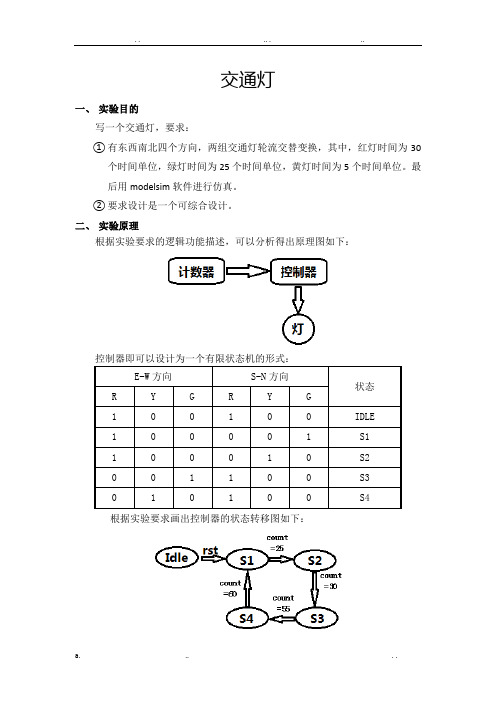

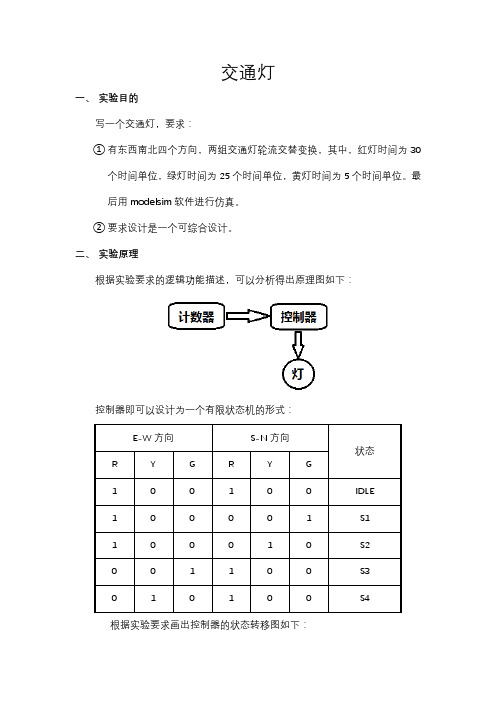

交通灯一、实验目的写一个交通灯,要求:①有东西南北四个方向,两组交通灯轮流交替变换,其中,红灯时间为30个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。

最后用modelsim软件进行仿真。

②要求设计是一个可综合设计。

二、实验原理根据实验要求的逻辑功能描述,可以分析得出原理图如下:控制器即可以设计为一个有限状态机的形式:E-W方向S-N方向状态R Y G R Y G100100IDLE100001S1100010S2001100S3010100S4根据实验要求画出控制器的状态转移图如下:三、代码1、源代码(1)控制器模块module traffic_lights(clk,rst,count,ew,sn);input clk,rst;input[5:0] count;output[2:0] ew,sn;reg[2:0] ew,sn;reg[3:0] state;parameter Idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100; always @(posedge clk)if(!rst)beginstate<=Idle;endelsecasex(state)Idle: if(rst)beginstate<=s1;ends1: if(count=='d25)beginstate<=s2;ends2: if(count=='d30)beginstate<=s3;ends3: if(count=='d55)beginstate<=s4;ends4: if(count=='d60)beginstate<=s1;endendcasealways @(posedge clk)beginif(!rst)beginew<=3'b100;sn<=3'b100;endelsecasex(state)Idle: if(rst)beginew<=3'b100;sn<=3'b001;ends1: if(count=='d25)beginew<=3'b100;sn<=3'b010;ends2: if(count=='d30)beginew<=3'b001;sn<=3'b100;ends3: if(count=='d55)beginew<=3'b010;sn<=3'b100;ends4: if(count=='d60)beginew<=3'b100;sn<=3'b001;enddefault: state<=Idle;endcaseendendmodule(2)计数器模块module counter(en,clk,rst,out);output[5:0]out;input en,clk,rst;reg[5:0] out;always@(posedge clk or negedge rst)beginif(!rst)out<='d0;else if(!en&&out<'d60)out<=out+1;elseout<='d1;endendmodule(3)将控制器与计数器进行连接module traffic_lights_top(out,clk,rst,en,ew,sn); input clk,rst,en;output[2:0] ew,sn;output[5:0]out;wire[5:0] out;traffic_lights u1(.clk(clk),.rst(rst),.count(out),.ew(ew),.sn(sn));counter u2(.en(en),.clk(clk),.rst(rst),.out(out));endmodule2、激励`timescale 1ns/100ps module traffic_lights_tb;reg clk,rst,en;wire[2:0] ew,sn;wire[5:0]out;traffic_lights_top m(.clk(clk),.rst(rst),.en(en),.ew(ew),.sn(sn),.out(out));always#5 clk=~clk;initialen<=1;initialbeginclk<=1;en<=0;rst<=0;#5 rst<=1;endendmodule四、仿真波形(图一)(图二)五、波形说明波形图中,从上至下依次为:时钟信号clk、复位信号rst、计数器使能端en、东西方向上灯的状态ew、南北方向上灯的状态sn、计数器的输出out。

基于Verilog的交通灯控制器的设计

武汉科技大学课题:交通灯控制器的设计编号:17指导老师:冯玉林班级:自动化0703班姓名:筱启…………………………坚持,就是胜利………………………目 录1. 设计内容与要求 (2)2. 交通灯控制系统的组成框图 (3)3. 交通灯控制电路的设计 (4)4. 交通灯控制电路设计的难点与解决方法 (5)5. 交通灯控制电路的Verilog 语句 (6)5. 交通灯控制电路的程序和波形分析 (12)6. EPF10K10LC84-4芯片引脚分配图 (20)7. 实验小结 (21)一、 设计内容与要求① 设计一个十字路口交通信号灯的定时控制电路。

要求红、绿灯按一定的规律亮和灭,并在亮灯期间进行倒计时,并将运行时间用数码管显示出来。

②绿灯亮时,为该车道允许通行信号,红灯亮时,为该车道禁止通行信号。

要求主干道每次通行时间为99秒,支干道每次通行时间为30秒。

每次变换运行车道前绿灯闪烁,持续时间为5秒。

即车道要由主干道转换为支干道时,主干道在通行时间只剩下5秒钟时,绿灯闪烁显示,支干道仍为红灯,以便主干道上已过停车线的车继续通行,未过停车线的车停止通行。

同理,当车道由支干道转换为主干道时,支干道绿灯闪烁显示5秒钟,主干道仍为红灯。

③ 对红、绿灯的运行时间要能比较方便的进行重新设置。

④ 添加左转灯的控制,可自行到实际十字路口观看规律并实现。

对器件进行在系统编程和实验验证。

⑤用Verilog 语言对设计进行描述,设计一个测试方案,通过Muxplus 对设计进行仿真验证。

并能够下载到实验板上调试成功。

二、交通灯控制系统的组成框图交通信号灯控制原理图绿 灯 左拐灯红 灯 绿 灯 左拐灯红 灯 交通信号灯控制系统框图三、交通灯控制电路的设计交通灯控制器设计的重点是控制电路的设计,根据设计要求分析,控制电路的算法可用下图所示的ASM图描述。

各状态的详细说明如下:S0状态:主干道绿灯亮,支干道红灯亮,此时若主干道有车等待左拐,而且主干道绿灯已亮足规定的时间间隔Ts;在主干道绿灯亮了(Ts-5)s后,则开始闪亮,直至绿灯亮了Ts;控制器发出状态转换信号Tempm==0,输出从状态S0转换到S1。

verilog 分频器,30s计数器及交通灯控制器设计

分频器module div(clk, div1,div2,div3);input clk;output div1;output div2;output div3;reg [31:0] counter1;reg [31:0] counter2;reg [31:0] counter3;reg div1;reg div2;reg div3;initial begindiv1=0;div2=0;div3=0;counter1=0;counter2=0;counter3=0;endalways @(posedge clk)begin/*if(counter1==2) counter1 <= 0;else counter1 <= counter1+1;if(counter2==3) counter2 <= 0;else counter2 <= counter2+1;if(counter3==4) counter3 <= 0;else counter3 <= counter3+1;*/ if(counter1==24999999) counter1 <= 0;else counter1 <= counter1+1;if(counter2==24999) counter2 <= 0;else counter2 <= counter2+1;if(counter3==12499999) counter3 <=0;else counter3 <= counter3+1;endalways @(posedge clk)begin/*if(counter1==2) div1 <= ~div1;if(counter2==3) div2 <= ~div2;if(counter3==4) div3 <= ~div3;*/if(counter1==24999999) div1 <= ~div1;if(counter2==24999) div2 <= ~div2;if(counter3==12499999) div3 <= ~div3;endendmodule30s计数器module count30(div1,number,direction );input div1;output [4:0] number;reg [4:0] number;reg direction;initialbegindirection=0;number=30;endalways@(posedge div1)beginif(number==0)begindirection<=~direction;number<=30;endelse number<=number-1;endendmodule控制器module moniter( div3,number,direction,eastred,eastyellow,eastgreen,northred,northyellow,northgreen );input div3;input direction;input [4:0]number;output eastred;output eastyellow;output eastgreen;output northred;output northyellow;output northgreen ;//wire [4:0] number;reg eastred;reg eastyellow;reg eastgreen;reg northred;reg northyellow;reg northgreen ;initial begineastred<=1;eastgreen<=0;northred<=1;northgreen<=0;northyellow<=eastyellow<=0;endalways @(posedge div3)beginif(number<=3)beginif (direction==0) eastyellow<=~eastyellow;else northyellow<=~northyellow;endelse begin eastyellow<=0;northyellow<=0;end endalways @(number )/*beginif(number==30&&direction==0)begin eastred<=1;eastgreen<=0;northred<=1;northgreen<=0;end*/if (number>2'b00010&&direction==0)begineastred<=0;eastgreen<=1;northred<=1;northgreen<=0;endelse if(number<3&&direction==0)begineastred<=0;eastgreen<=0;northred<=1;northgreen<=0;endelse if(number>2&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=1;endelse if(number<3&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=0;endendmodule译码器module yimaqi( clk,number,led1,led2);input clk;input [4:0] number;output [6:0] led1;output [6:0] led2;reg [6:0] led1;reg [6:0] led2;always @( number )begincase (number)5'b00000: begin led1 <= 7'b0000001; led2 <= 7'b0000001;end5'b00001: begin led1 <= 7'b0000001; led2 <= 7'b1001111;end5'b00010: begin led1 <= 7'b0000001; led2 <= 7'b0010010;end7'b0000110;end5'b00100: begin led1 <= 7'b0000001; led2 <= 7'b1001100;end5'b00101: begin led1 <= 7'b0000001; led2 <= 7'b0100100;end5'b00110: begin led1 <= 7'b0000001; led2 <= 7'b1100000;end5'b00111: begin led1 <= 7'b0000001; led2 <= 7'b0001111;end5'b01000: begin led1 <= 7'b0000001; led2 <= 7'b0000000;end5'b01001: begin led1 <= 7'b0000001; led2 <= 7'b0001100; end5'b01010: begin led1 <= 7'b1001111; led2 <= 7'b0000001;end5'b01011: begin led1 <= 7'b1001111; led2 <= 7'b1001111; end5'b01100: begin led1 <= 7'b1001111; led2 <= 7'b0010010;end5'b01101: begin led1 <= 7'b1001111; led2 <= 7'b0000110; end5'b01110: begin led1 <= 7'b1001111; led2 <= 7'b1001100;end5'b01111: begin led1 <= 7'b1001111; led2 <= 7'b0100100;end5'b10000: begin led1 <= 7'b1001111; led2 <= 7'b1100000;end5'b10001: begin led1 <= 7'b1001111; led2 <= 7'b0001111;end5'b10010: begin led1 <= 7'b1001111; led2 <= 7'b0000000;end5'b10011: begin led1 <= 7'b1001111; led2 <= 7'b0001100;end5'b10100: begin led1 <= 7'b0010010; led2 <= 7'b0000001;end5'b10101: begin led1 <= 7'b0010010; led2 <= 7'b1001111;end5'b10110: begin led1 <= 7'b0010010; led2 <= 7'b0010010;end5'b10111: begin led1 <= 7'b0010010; led2 <= 7'b0000110;end5'b11000: begin led1 <= 7'b0010010; led2 <= 7'b1001100;end7'b0100100;end5'b11010: begin led1 <= 7'b0010010; led2 <= 7'b1100000;end5'b11011: begin led1 <= 7'b0010010; led2 <= 7'b0001111;end5'b11100: begin led1 <= 7'b0010010; led2 <= 7'b0000000;end5'b11101: begin led1 <= 7'b0010010; led2 <= 7'b0001100;end5'b11110: begin led1 <= 7'b0000110; led2 <= 7'b0000001;enddefault: begin led1 <= 7'b0000000; led2 <= 7'b0000000;endendcaseendendmodulemodule dianzhen(direction,clk,div2,row,con);input div2;input clk;input direction;output[15:0] row;output[15:0] con;reg[15:0] row;reg[15:0] con;integer cnt,b;reg[15:0] r[48:0];initialbeginif (direction==0)begin// 丁r[0] <=16'b1111111111111111;r[1] <=16'b1011111111111111;r[2] <=16'b1011111111111111;r[3] <=16'b1011111111111111;r[4] <=16'b1011111111111111;r[5] <=16'b1011111111111011;r[6] <=16'b1011111111111101;r[7] <=16'b1000000000000011;r[8] <=16'b1011111111111111;r[9] <=16'b1011111111111111;r[10]<=16'b1011111111111111;r[11] <=16'b1011111111111111;r[12]<=16'b1011111111111111;r[13]<=16'b1011111111111111;r[14]<=16'b1011111111111111;r[15]<=16'b1111111111111111;// 乾r[16]<=16'b1101111111101111 ;r[17]<=16'b1101000000101111 ;r[18]<=16'b1101010101101111 ;r[19]<=16'b0000010101101111 ;r[20]<=16'b1101010100000000 ;r[21]<=16'b1101010101101111 ;r[22]<=16'b1101000000101111 ;r[23]<=16'b1101110111101111 ;r[24]<=16'b1111001111110011 ;r[25]<=16'b0000110111001101 ;r[26]<=16'b1010110110111101 ;r[27]<=16'b1110110101111101 ;r[28]<=16'b1110110011111101 ;r[29]<=16'b1110110111100001 ;r[30]<=16'b1110111111111011 ;r[31]<=16'b1111111111111111 ;// 全灭r[32]<=16'b1111111111111111;r[33]<=16'b1111111111111111;r[34]<=16'b1111111111111111;r[35]<=16'b1111111111111111;r[36]<=16'b1111111111111111;r[37]<=16'b1111111111111111;r[38]<=16'b1111111111111111;r[39]<=16'b1111111111111111;r[40]<=16'b1111111111111111;r[41]<=16'b1111111111111111;r[42]<=16'b1111111111111111;r[43]<=16'b1111111111111111;r[44]<=16'b1111111111111111;r[45]<=16'b1111111111111111;r[46]<=16'b1111111111111111;r[47]<=16'b1111111111111111;endelse if(direction==1)begin//1r[0] <=16'b 1111111111111111;r[1] <=16'b 1111111111111111;r[2] <=16'b 1111111111111111;r[3] <=16'b 1111111111111111;r[4] <=16'b 1111111111111111;r[5] <=16'b 1111011111111011;r[6] <=16'b 1111011111111011;r[7] <=16'b 1110000000000011;r[8] <=16'b 1111111111111011;r[9] <=16'b 1111111111111011;r[10]<=16'b 1111111111111111;r[11] <=16'b 1111111111111111;r[12]<=16'b 1111111111111111;r[13]<=16'b 1111111111111111;r[14]<=16'b 1111111111111111;r[15]<=16'b 1111111111111111;// 0r[16]<=16'b 1111111111111111;r[17]<=16'b 1111111111111111;r[18]<=16'b 1111111111111111;r[19]<=16'b 1111111111111111;r[20]<=16'b 1111111111111111;r[21]<=16'b 1111100000001111;r[22]<=16'b 1111011111110111;r[23]<=16'b 1110111111111011;r[24]<=16'b 1110111111111011;r[25]<=16'b 1111011111110111;r[26]<=16'b 1111100000001111;r[27]<=16'b 1111111111111111;r[28]<=16'b 1111111111111111;r[29]<=16'b 1111111111111111;r[30]<=16'b 1111111111111111;r[31]<=16'b 1111111111111111;// 9r[32]<=16'b 1111111111111111;r[33]<=16'b 1111111111111111;r[34]<=16'b 1111111111111111;r[35]<=16'b 1111111111111111;r[36]<=16'b 1111111111111111;r[37]<=16'b 1111100011111111;r[38]<=16'b 1111011101110011;r[39]<=16'b 1110111110111011;r[40]<=16'b 1110111110111011;r[41]<=16'b 1111011101110111;r[42]<=16'b 1111100000001111;r[43]<=16'b 1111111111111111;r[44]<=16'b 1111111111111111;r[45]<=16'b 1111111111111111;r[46]<=16'b 1111111111111111;r[47]<=16'b 1111111111111111;endendalways@(posedge clk )beginif (b==47)b<=0;else b<=b+1;endalways@(posedge div2)beginif(cnt==15)begincnt<=0;endelsecnt<=cnt+1;case(cnt)15: con<=16'b0000_0000_0000_0001; 14: con<=16'b0000_0000_0000_0010; 13: con<=16'b0000_0000_0000_0100; 12: con<=16'b0000_0000_0000_1000; 11: con<=16'b0000_0000_0001_0000; 10: con<=16'b0000_0000_0010_0000; 9: con<=16'b0000_0000_0100_0000; 8: con<=16'b0000_0000_1000_0000; 7: con<=16'b0000_0001_0000_0000; 6: con<=16'b0000_0010_0000_0000; 5: con<=16'b0000_0100_0000_0000; 4: con<=16'b0000_1000_0000_0000; 3: con<=16'b0001_0000_0000_0000; 2: con<=16'b0010_0000_0000_0000; 1: con<=16'b0100_0000_0000_0000; 0: con<=16'b1000_0000_0000_0000;endcasecase(cnt)0: row<=r[b+0];1: row<=r[b+1];2: row<=r[b+2];3: row<=r[b+3];4: row<=r[b+4];5: row<=r[b+5];6: row<=r[b+6];7: row<=r[b+7];8: row<=r[b+8];9: row<=r[b+9];10: row<=r[b+10];11: row<=r[b+11];12: row<=r[b+12];13: row<=r[b+13];14: row<=r[b+14];15: row<=r[b+15];endcaseendendmodule。

基于VerilogHDL的交通灯控制器设计

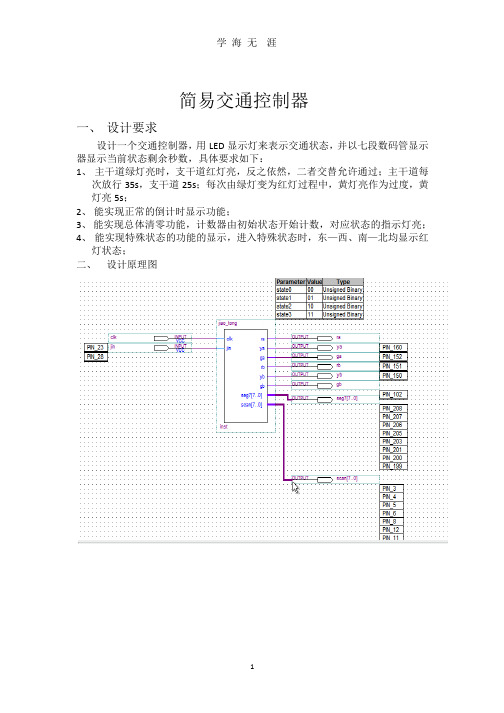

目录第一章设计原理 (1)1.1设计要求 (1)1.2设计思路和原理 (1)1.3实现方法 (1)第二章Verilog 程序设计 (2)2.1整体设计 (2)2.2 具体设计 (3)第三章仿真 (7)3.1 波形仿真 (7)第四章设计总结 (9)4.1 总结 (9)4.2参考资料 (9)程序清单 (10)交通灯控制器设计第一章 设计原理1.1设计要求设计一个交通控制器,用LED 显示灯表示交通状态,并以7段数码显示器显示当前状态剩余秒数 主干道绿灯亮时,支干道红灯亮;反之亦然,二者交替允许通行,主干道每次放行35s ,支干道每次放行25s 。

每次由绿灯变为红灯的过程中,亮光的黄灯作为过渡,黄灯的时间为5s 。

能进行特殊状态显示,特殊状态时东西、南北路口均显示红灯状态。

用LED 灯显示倒计时,并且能实现总体清零功能,计数器由初始状态开始计数,对应状态的显示灯亮。

1.2设计思路和原理本次设计是针对十字路口,进行南北和东西直行情况下交通灯控制。

设定东西方向为主干道方向,根据交通灯的亮的规则,在初始状态下四个方向的都为红灯亮启,进入正常工作状态后,当主干道上绿灯亮时,支干道上红灯亮,持续35S 后,主干道和支干道上的黄灯都亮启,持续5S 后,主干道上红灯亮启,支干道上绿灯亮启持续25S ,之后主干道和支干道上的黄灯都亮启5s ,一个循环完成。

循环往复的直行这个过程。

其过程如下图所示:0s30s25s主干道方向支干道方向图1.交通灯点亮时间控制说明1.3实现方法本次采用文本编辑法,即利用Verilog 语言描述交通控制器,通过状态机计数法,实现设计所要求的交通灯控制及时间显示。

设计中用两组红黄绿LED 模拟两个方向上的交通灯,用4个7段数码管分别显示两个方向上的交通灯剩余时间,控制时钟由试验箱上频率信号提供。

第二章 Verilog 程序设计2.1整体设计根据上章设计原理,交通灯控制的关键是各个状态之间的转换和进行适当的时间延时,根据状态机的设计规范,本次设计了三个状态之间的循环转化,其真值表及状态转化图如下所示:状状状状状状状状状状状状00状状10状状11状状01状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状状001100010010001010100010图2.交通灯控制状态转化说明:该状态图为交通灯在正常情况下的状态转化图,进入控制后,状态00时主干道绿灯及支干道红灯亮起,进入状态01后两路黄灯亮起,状态11时主干道红灯及支干道绿灯亮起。

verilog交通灯设计

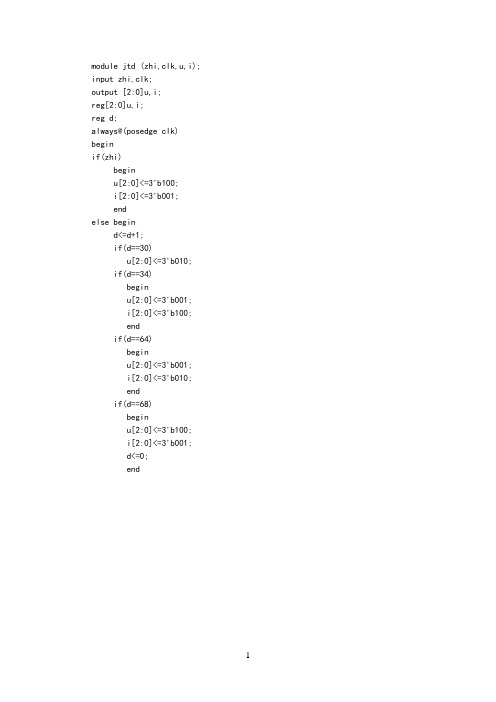

module jtd (zhi,clk,u,i); input zhi,clk;output [2:0]u,i;reg[2:0]u,i;reg d;always@(posedge clk) beginif(zhi)beginu[2:0]<=3'b100;i[2:0]<=3'b001;endelse begind<=d+1;if(d==30)u[2:0]<=3'b010; if(d==34)beginu[2:0]<=3'b001; i[2:0]<=3'b100; endif(d==64)beginu[2:0]<=3'b001; i[2:0]<=3'b010; endif(d==68)beginu[2:0]<=3'b100; i[2:0]<=3'b001; d<=0;endmodule jtd(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [5:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s0;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin u[2:0]<=3'b010;i[2:0]<=3'b001;d=d+1;if(d==4)begin state<=s2;d=0;end else state<=s1;ends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin u[2:0]<=3'b001;i[2:0]<=3'b010;d=d+1;if(d==4)begin state<=s4;d=0;end else state<=s3;enddefault: state<=s4;endcaseendendendmodule黄灯闪module jtde(zhi,u,i,clk,rst);input zhi,clk,rst;output [2:0]u,i;reg [2:0]u,i;reg[4:0]state;reg [6:0]d;initial d=0;parameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:begin u[2:0]<=3'b100;i[2:0]<=3'b001;if(zhi)begin state<=s0;end else state<=s4;ends0:begin u[2:0]<=3'b100;i[2:0]<=3'b001;d=d+1;if(d==30)begin state<=s1;d=0;end else state<=s0;ends1:begin d=d+1;if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s1;endif(d==3)begin u[2:0]<=3'b000;i[2:0]<=3'b001;state<=s1;endif(d==4)begin u[2:0]<=3'b010;i[2:0]<=3'b001;state<=s2;d=0;endends2:begin u[2:0]<=3'b001;i[2:0]<=3'b100;d=d+1;if(d==30) begin state<=s3;d=0;end else state<=s2;ends3:begin d=d+1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d=0;endenddefault: state<=s4;endcaseendend黄灯闪且倒计时module mnb(zhi,u,i,clk,rst,ugx,usx,igx,isx);input zhi,clk,rst;output [2:0]u,i;output [3:0]ugx,usx,igx,isx;reg [2:0]u,i;reg[4:0]state;reg [4:0]ugx,usx,igx,isx;reg [6:0]d,e,f;initialbegin d<=0;e<=30;f<=34;endparameter s0=5'b00001,s1=5'b00010,s2=5'b00100,s3=5'b01000,s4=5'b10000;always@(posedge clk)beginif(!rst) begin state<=s4;u[2:0]<=3'b100;i[2:0]<=3'b001;endelsebegincase(state)s4:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=0;usx<=0;igx<=0;isx<=0;if(zhi)beginstate<=s0;d<=0;e<=30;f<=35;end else state<=s4;ends0:beginu[2:0]<=3'b100;i[2:0]<=3'b001;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30)begin state<=s1;d<=0;e<=4;f<=4;end else state<=s0;ends1:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;e<=e-1;f<=f-1;if(d==0)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==1)begin u[2:0]<=3'b000;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==2)begin u[2:0]<=3'b010;i[2:0]<=3'b001;d<=d+1;state<=s1;end if(d==3)beginu[2:0]<=3'b000;i[2:0]<=3'b001;state<=s2;d<=0;e<=35;f<=30;endends2:beginu[2:0]<=3'b001;i[2:0]<=3'b100;ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e< =e-1;f<=f-1;if(d==30) begin state<=s3;d<=0;e<=4;f<=4;end else state<=s2;ends3:begin ugx<=e%10;usx<=e/10;igx<=f%10;isx<=f/10;d<=d+1;e<=e-1;f<=f-1;if(d==1)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==2)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s3;endif(d==3)begin i[2:0]<=3'b000;u[2:0]<=3'b001;state<=s3;endif(d==4)begin i[2:0]<=3'b010;u[2:0]<=3'b001;state<=s4;d<=0;endenddefault: state<=s4;endcaseendendendmodule黄灯闪。

Verilog代码(计数器、交通灯、串并转换)

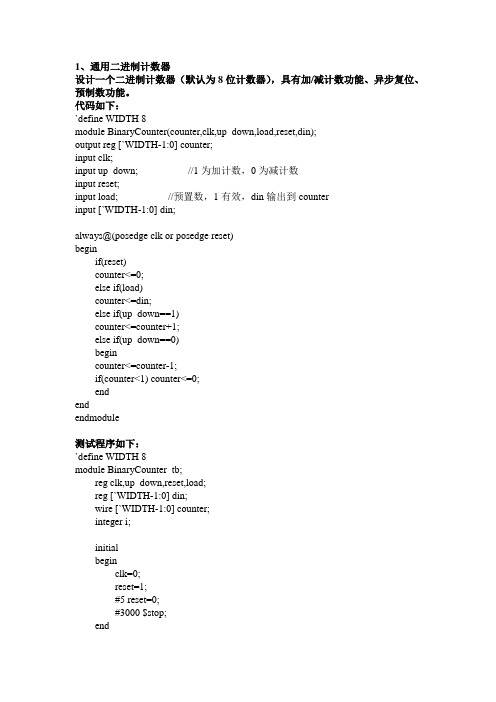

1、通用二进制计数器设计一个二进制计数器(默认为8位计数器),具有加/减计数功能、异步复位、预制数功能。

代码如下:`define WIDTH 8module BinaryCounter(counter,clk,up_down,load,reset,din);output reg [`WIDTH-1:0] counter;input clk;input up_down; //1为加计数,0为减计数input reset;input load; //预置数,1有效,din输出到counterinput [`WIDTH-1:0] din;always@(posedge clk or posedge reset)beginif(reset)counter<=0;else if(load)counter<=din;else if(up_down==1)counter<=counter+1;else if(up_down==0)begincounter<=counter-1;if(counter<1) counter<=0;endendendmodule测试程序如下:`define WIDTH 8module BinaryCounter_tb;reg clk,up_down,reset,load;reg [`WIDTH-1:0] din;wire [`WIDTH-1:0] counter;integer i;initialbeginclk=0;reset=1;#5 reset=0;#3000 $stop;endalways #5 clk=~clk;/*always@(posedge clk)beginup_down={$random}%2;load={$random}%2;din={$random}%256;end*/initialbegin#5;for(i=0;i<256;i=i+3)begindin=i;#10;endendinitialbeginup_down=1;load=1;#20 load=0;#30 load=1;#30 load=0;endalways #200 up_down=~up_down;BinaryCounter bcounter(.counter(counter),.clk(clk),.up_down(up_down),.load(load),.reset(reset),.din(din));endmodule波形图如下:图1 二进制计数器波形图图2 二进制计数器波形图从图像可看出,20s-50s为加计数,50s-80s时load=1,执行置数功能,80s-200s 时up_down=1,为加计数,200s-280s时up_down=0,为减计数。

基于VerilogHDL的通行时间可变的交通灯控制器

通行时间可变的交通灯控制器设计module tr1(ng,clk,reset,resets,emergency,lighta,lightb,seg,select); input ng,clk,reset,emergency,resets;output[6:0]seg;//显示用的output[3:0] lighta,lightb;//a是主干道,b是支干道output [3:0] select;//选择那一个管子进行显示reg clk1,clk2;//clk1要5HZ clk2要几千HZreg [3:0] select;reg tim1,tim2;//这是看你的等有没有变过颜色的控制信号reg [1:0] cont;reg[2:0]state1,state2,ste;两个控制颜色变化状态的信号。

reg[3:0]lighta,lightb;//a是主干道,b是支干道reg[3:0]num;//译码器是根据这个东西来译码的reg [35:0] fout;reg[6:0]seg;//显示reg[7:0] numa,numb;reg[7:0] red1,red2,green1,green2,yellow1,yellow2,left1,left2; always @(ng )if(!ng)begin //设置计数初值green1 <=8'b00110000;//30Sred1 <=8'b01010001;//51Syellow1<=8'b00000011;//3Sleft1 <=8'b00010101; //15Sgreen2 <=8'b00110000;//30Sred2 <=8'b01010001;//51Syellow2<=8'b00000011;//3Sleft2 <=8'b00010101; //15Sendalways @ (posedge clk)beginif (fout==36'b111111111111111111111111111111111111)fout<=0;else begin fout<=fout+1;clk1=fout[23];5HZclk2=fout[13];几千HZendendalways @(posedge clk1 )beginif(reset) //复位与特殊情况控制这是主干道的复位beginlighta<=4'b1000;//lighta是主干道的交通灯,lightb是支干道的交通灯,1000是红灯,0100是直行绿灯,0010是黄灯,0001是左转绿灯numa<=red1; //主干道的数码管从红灯开始记state1<=0;//这时候灯变化的控制信号为0endelse if(emergency)//紧急情况beginlighta<=4'b1000;//主干道红了numa<=red1;//计时也从红灯记endelse if(ng)//这下开始正常工作了begin //使能有效开始控制计数if(!tim1) //你有没有变过颜色啊?没有?那开始变颜色吧。

VerilogHDL编写的交通灯

1. module trafficlight(clk,lx,lx_l,lx_r,ly,ly_l,ly_r,c,done,m);input clk,c;//始终和初始化控制output done;output [5:0]m;//倒计时寄存器output lx,lx_l,lx_r,ly,ly_l,ly_r;//指示灯(分别是X、Y方向的直行、左转和右转)reg lx,lx_l,lx_r,ly,ly_l,ly_r;reg [5:0]m;reg [1:0]state;//状态机reg done;parameters0=2'b00,s1=2'b01,s2=2'b10,s3=2'b11;//-------------------------------------------//状态模块always@(posedge clk)if(c)begin done<=1;state<=2'b00;endelsebegincase(state)s0:if(done)begin m<=6'd44;done<=0;endelse if(m>1) m<=m-1;elsebegin state<=s1;done<=1;m<=0;ends1:if(done)begin m<=6'd24;done<=0;endelse if(m>1) m<=m-1;elsebegin state<=s2;done<=1;m<=0;ends2:if(done)begin m<=6'd29;done<=0;endelse if(m>1) m<=m-1;elsebegin state<=s3;done<=1;m<=0;ends3:if(done)begin m<=6'd14;done<=0;endelse if(m>1) m<=m-1;elsebegin state<=s0;done<=1;m<=0;endendcaseend//-----------------------------------------//输出模块always@(posedge clk)begincase(state)s0:{lx,lx_l,lx_r,ly,ly_l,ly_r}<=6'b101001;s1:{lx,lx_l,lx_r,ly,ly_l,ly_r}<=6'b011001; s2:{lx,lx_l,lx_r,ly,ly_l,ly_r}<=6'b001101; s3:{lx,lx_l,lx_r,ly,ly_l,ly_r}<=6'b001011; endcaseend//-------------------------------------------- endmodule2.生成的状态机3.整体的图,四个状态都包括X方向由直行变左转,符合倒计时的要求。

Verilog语言实现设计交通灯控制器

Verilog语言实现设计交通灯控制器实验模块组成:(计数器+控制器)可以分开实现,最好一起实现避免接口对接时出错译码器实验要求:1.在十字路口两个方向各设一组红、绿、黄灯,显示顺序为:南北方向是绿、黄、红灯;东西方向是红、绿、黄灯。

2.要求红、绿、黄灯的持续时间分别为:10s、7s、3s,东西、南北方向各用一个数码管显示倒计时时间。

3.当任意方向出现特殊情况时,应优先放行,即使各方向均亮红灯,倒计时停止,且显示数字闪烁。

经过规定时间之后,恢复正常运行状态。

//计数器+控制器module ZTJ(clk,s,count1,count2,led);parameter s0=6’b010100,s1=6’b001100,s2=6'b100010,s3=6'b100001,s4=6'b100100;input clk,s;output[3:0]count1;output[3:0]count2;output[5:0]led;reg[3:0]count1;reg[3:0]count2;reg[5:0]led;reg[5:0]st;reg[5:0]jicun;reg[3:0]i;always @(posedge clk)if(s==0 &led==6’b000000)beginled<=s0;st<=s0;count1<=4'b0110;count2〈=4’b1001;endelse if(s==0 & led!=6’b000000)begincase(st)s0:if(count1!=4'b0000) begin led<=s0;count1〈=count1—1;count2<=count2-1;end else begin count1<=4'b0010;st<=s1;ends1:if(count1!=4'b0000)begin led〈=s1;count1〈=count1—1;count2<=count2-1;end else begin count1〈=4’b1001;count2<=4'b0110;st<=s2;ends2:if(count2!=4’b0000) begin led〈=s2;count1<=count1-1;count2〈=count2-1;end else begin count2〈=4’b0010;st〈=s3;ends3:if(count2!=4'b0000)begin led<=s3;count1〈=count1—1;count2〈=count2—1;end else begin count1<=4’b0110;count2〈=4’b1001;st<=s0;enddefault:led<=s4;endcaseendelsebeginjicun<=led;led〈=s4;count1<=count1;count2〈=count2;i<=i+1;if(i==4’b1001)led〈=jicun;endendmodule//译码器module DECL7S(A,LED7S);input [3:0]A;output [6:0]LED7S;reg [6:0]LED7S;always@(A)begincase(A)4’b0000:LED7S<=7'b0111111;4’b0001: LED7S<=7'b0000110;4'b0010: LED7S<=7'b1011011;4'b0011:LED7S〈=7'b1001111;4'b0100:LED7S<=7’b1100110;4’b0101:LED7S<=7’b1101101;4'b0110: LED7S<=7’b1111101;4'b0111:LED7S<=7'b0000111;4’b1000:LED7S<=7'b1111111;4’b1001: LED7S<=7'b1101111;4'b1010: LED7S<=7’b1110111;4’b1011:LED7S〈=7'b1111100;4’b1100: LED7S〈=7'b0111001;4'b1101:LED7S<=7’b1011110;4'b1110: LED7S<=7'b1111001;4’b1111:LED7S〈=7’b1110001;default:LED7S〈=7'b0111111;endcaseendendmodule。

用verilog语言编写交通灯程序

交通灯一、实验目的写一个交通灯,要求:①有东西南北四个方向,两组交通灯轮流交替变换,其中,红灯时间为30个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。

最后用modelsim软件进行仿真。

②要求设计是一个可综合设计。

二、实验原理根据实验要求的逻辑功能描述,可以分析得出原理图如下:控制器即可以设计为一个有限状态机的形式:E-W方向S-N方向状态R Y G R Y G1 0 0 1 0 0 IDLE1 0 0 0 0 1 S11 0 0 0 1 0 S20 0 1 1 0 0 S30 1 0 1 0 0 S4根据实验要求画出控制器的状态转移图如下:三、代码1、源代码(1)控制器模块module traffic_lights(clk,rst,count,ew,sn);input clk,rst;input[5:0] count;output[2:0] ew,sn;reg[2:0] ew,sn;reg[3:0] state;parameter Idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100; always (posedge clk)if(!rst)beginstate<=Idle;endelsecasex(state)Idle: if(rst)beginstate<=s1;ends1: if(count=='d25)beginstate<=s2;ends2: if(count=='d30)beginstate<=s3;ends3: if(count=='d55)beginstate<=s4;ends4: if(count=='d60)beginstate<=s1;endendcasealways (posedge clk)beginif(!rst)beginew<=3'b100;sn<=3'b100;endelsecasex(state)Idle: if(rst)beginew<=3'b100;sn<=3'b001;ends1: if(count=='d25)beginew<=3'b100;sn<=3'b010;ends2: if(count=='d30)beginew<=3'b001;sn<=3'b100;ends3: if(count=='d55)beginew<=3'b010;sn<=3'b100;ends4: if(count=='d60)beginew<=3'b100;sn<=3'b001;enddefault: state<=Idle;endcaseendendmodule(2)计数器模块module counter(en,clk,rst,out);output[5:0]out;input en,clk,rst;reg[5:0] out;always(posedge clk or negedge rst)beginif(!rst)out<='d0;else if(!en&&out<'d60)out<=out+1;elseout<='d1;endendmodule(3)将控制器与计数器进行连接module traffic_lights_top(out,clk,rst,en,ew,sn); input clk,rst,en;output[2:0] ew,sn;output[5:0]out;wire[5:0] out;traffic_lights u1(.clk(clk),.rst(rst),.count(out),.ew(ew),.sn(sn));counter u2(.en(en),.clk(clk),.rst(rst),.out(out));endmodule2、激励`timescale 1ns/100psmodule traffic_lights_tb;reg clk,rst,en;wire[2:0] ew,sn;wire[5:0]out;traffic_lights_top m(.clk(clk),.rst(rst),.en(en),.ew(ew),.sn(sn),.out(out));always#5 clk=~clk;initialen<=1;initialbeginclk<=1;en<=0;rst<=0;#5 rst<=1;endendmodule四、仿真波形(图一)(图二)五、波形说明波形图中,从上至下依次为:时钟信号clk、复位信号rst、计数器使能端en、东西方向上灯的状态ew、南北方向上灯的状态sn、计数器的输出out。

智能交通灯控制器的设计(verilog)

智能交通灯控制器的设计1、实验目的及要求实验目的:通过交通灯的设计与仿真综合,体会复杂时序的实现方法,学会用框图表示程序的设计思想,掌握中小规模集成电路的系统综合设计方法。

实验要求:设计一个交通灯信号控制电路。

具体要求为:输入为50MHz的时钟和复位信号,输出为红、绿、黄三个信号(高电平为亮)。

复位信号(高电平)有效,红、绿、黄灯灭;接着进行如下循环:绿灯亮1分钟,黄灯闪烁10秒,红灯亮1分钟。

在此基础上再加两个数码管,对倒计时的数显示。

2、实验设备(环境)及要求实验EDA工具为:Synplify Pro 9.6.2和ModelSim SE 6.2b。

3、实验内容与步骤3.1设计思路概述总体上分为三个大模块,即:顶层模块、控制模块、译码模块(包括显示模块)。

他们各自的作用分别如下:顶层模块:此模块只做例化,即对底层的控制模块和译码模块进行例化,而不做逻辑设计。

控制模块:此模块是本程序的主体,主要是控制各个灯颜色(此模块并不控制黄灯的闪烁)的转换,以及倒计时时间输出。

首先要对时钟进行分频。

由于系统时钟频率比较大,因此首先分频产生时钟,用于下面的电路的控制;然后是各种颜色之间的转换,在此在添加一个使能端enable ,当使能端enable为0的时候,就开始进行状态循环以及倒计时,然后enable就立即变为1;状态用light_status(分别为0、1、2)表示,开始的时候,如果状态light_status为0,表示此时显示的是绿灯,便把绿灯亮的时间(60s)给统计灯亮时间的变量light_long,并且把显示灯亮的变量light_select赋值100(高电平表示亮),最后把状态标志位light_status赋1,但是此时并不能转向下一个状态(黄),因为绿灯亮的时间还没有控制,接下来会转到倒计时处。

然后,我们这里用了BCD码表示倒计时时间。

灯亮或闪烁时间(绿、黄、红分别为60s、10s、60s)用BCD码表示(分别为60h、10h、60h),倒计时的时候个位和十位分别是BCD码的高四位和低四位,首先是低四位倒数,当倒数到0时,给它重新赋值为9,且高四位减1,如此循环,直到这个数减到0,此时表示某一个灯亮的时间到,接着进行下一个状态,为了能使进入下一个状态,必须在时间减到0的时候,给使能端enable 赋值0;由于用的BCD码,高四位和低四位就分别是我们要在译码模块的要用数码管显示的十位和个位。

基于verilog HDL数字系统设计--交通灯

交通灯控制器-------数字系统设计文档姓名:学号:一.课题简介:我在本课程中所选择的课题是用Verilog HDL 实现的交通灯控制器。

该交通灯控制器处在一个城乡结合处的十字路口,这个十字路口分为主干道和乡村公路,由于主干道的车流量远大于乡村公路的车流量,所以这个交通灯控制器不同于常见的交通灯控制器。

这个交通控制器的功能有如下几点:1.当乡村公路无车时,始终保持乡村公路红灯亮,主干道绿灯亮。

2.当乡村公路有车时,而主干道通车时间已经超过它的最短通车时间时,禁止主干道通行,让乡村公路通行。

主干道最短通车时间为25s 。

3.当乡村公路和主干道都有车时,按主干道通车25s,乡村公路通车16s交替进行。

4.不论主干道情况如何,乡村公路通车最长时间为16s。

5.在每次由绿灯亮变成红灯亮的转换过程中间,要亮5s时间的黄灯作为过渡。

6.用开关代替传感器作为检测车辆是否到来的信号。

用红、绿、黄三种颜色的发光二极管作交通灯。

要求显示时间,倒计时。

二.控制框图和设计流程图:1.这个交通灯控制器由三个主要部分组成---核心控制器以及、译码器、分频器。

2.流程图的内容同上面交通灯的功能,这里不再多做解释。

三.各部分组件的具体实现和分析:1.核心控制器实现基本功能:(1)它的输入端有4个输入信号—C、RST、ST、CLK。

C信号是一个检测信号,检测乡村公路是否有车,C=0示无车,这种情况下乡村公路一直亮红灯,主干道一直亮红灯,并且两个计数器都同步30秒重复计数,直到C=1即乡村公路有车是才跳变到其他情况。

RST信号是复位信号,当RST=0时,这个交通灯控制器才能正常工作。

当RST=1时,所有计数器都立刻赋初值,并且乡村公路和主干道都亮红灯,表示交通灯控制器出了故障,为防止意外发生,禁止通行。

ST信号表示使能信号,当ST=1时,交通灯控制器才能正常工作。

ST=0时,所有计数器都停止计数,并且乡村公路和主干道都亮红灯,表示交通灯控制器出了故障,为防止意外发生,禁止通行。

Verilog HDL基础教程之:实例5 交通灯控制器

Verilog HDL 基础教程之:实例5 交通灯控制器

实例的内容及目标

1.实例的主要训练内容

本实例通过Verilog HDL 语言设计一个简易的交通等控制器,实现一个具有两个方向、共8 个灯并具有时间倒计时功能的交通灯功能。

2.实例目标

通过本实例,读者应达到下面的目标。

掌握Verilog 设计一个交通等控制器的方法。

初步掌握Verilog 语言的设计方法。

原理简介

交通灯是城市交通中不可缺少的重要工具,是城市交通秩序的重要保障。

本实例就是实现一个常见的十字路口交通灯功能。

读者通过学习这个交通灯控制器,可以实现一个更加完整的交通灯。

例如实现实时配置各种灯的时间,手动控制各个灯的状态等。

一个十字路口的交通一般分为两个方向,每个方向具有红灯、绿灯和黄灯3 种,另外每个方向还具有左转灯,因此每个方向具有4 个灯。

这个交通灯还为每一个灯的状态设计了倒计时数码管显示功能。

可以为每一个灯的状态设置一个初始值,灯状态改变后,开始按照这个初始值倒计时。

倒计时归零后,灯的状态将会改变至下一个状态。

值得注意的是,交通灯两个方向的灯的状态是相关的。

也就是说,每个方向的灯的状态影响着另外一个方向的灯的状态,这样才能够协调两个方向的车流。

如果每个方向的灯是独立变化的,那么交通灯就没有了意义。

如表1 所示是两个方向(假设为A,B 方向)灯的状态的对应情况。

用verilog语言编写交通灯程序

交通灯一、实验目的写一个交通灯,要求:①有东西南北四个方向,两组交通灯轮流交替变换,其中,红灯时间为30个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。

最后用modelsim软件进行仿真。

②要求设计是一个可综合设计。

二、实验原理根据实验要求的逻辑功能描述,可以分析得出原理图如下:控制器即可以设计为一个有限状态机的形式:E-W方向S-N方向状态R Y G R Y G1 0 0 1 0 0 IDLE1 0 0 0 0 1 S11 0 0 0 1 0 S20 0 1 1 0 0 S30 1 0 1 0 0 S4根据实验要求画出控制器的状态转移图如下:三、代码1、源代码(1)控制器模块module traffic_lights(clk,rst,count,ew,sn);input clk,rst;input[5:0] count;output[2:0] ew,sn;reg[2:0] ew,sn;reg[3:0] state;parameter Idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100; always @(posedge clk)if(!rst)beginstate<=Idle;endelsecasex(state)Idle: if(rst)beginstate<=s1;ends1: if(count=='d25)beginstate<=s2;ends2: if(count=='d30)beginstate<=s3;ends3: if(count=='d55)beginstate<=s4;ends4: if(count=='d60)beginstate<=s1;endendcasealways @(posedge clk)beginif(!rst)beginew<=3'b100;sn<=3'b100;endelsecasex(state)Idle: if(rst)beginew<=3'b100;sn<=3'b001;ends1: if(count=='d25)beginew<=3'b100;sn<=3'b010;ends2: if(count=='d30)beginew<=3'b001;sn<=3'b100;ends3: if(count=='d55)beginew<=3'b010;sn<=3'b100;ends4: if(count=='d60)beginew<=3'b100;sn<=3'b001;enddefault: state<=Idle;endcaseendendmodule(2)计数器模块module counter(en,clk,rst,out);output[5:0]out;input en,clk,rst;reg[5:0] out;always@(posedge clk or negedge rst)beginif(!rst)out<='d0;else if(!en&&out<'d60)out<=out+1;elseout<='d1;endendmodule(3)将控制器与计数器进行连接module traffic_lights_top(out,clk,rst,en,ew,sn); input clk,rst,en;output[2:0] ew,sn;output[5:0]out;wire[5:0] out;traffic_lights u1(.clk(clk),.rst(rst),.count(out),.ew(ew),.sn(sn));counter u2(.en(en),.clk(clk),.rst(rst),.out(out));endmodule2、激励`timescale 1ns/100psmodule traffic_lights_tb;reg clk,rst,en;wire[2:0] ew,sn;wire[5:0]out;traffic_lights_top m(.clk(clk),.rst(rst),.en(en),.ew(ew),.sn(sn),.out(out));always#5 clk=~clk;initialen<=1;initialbeginclk<=1;en<=0;rst<=0;#5 rst<=1;endendmodule四、仿真波形(图一)(图二)五、波形说明波形图中,从上至下依次为:时钟信号clk、复位信号rst、计数器使能端en、东西方向上灯的状态ew、南北方向上灯的状态sn、计数器的输出out。

verilog简单交通灯实现.pptx

case(data[3:0]) 4'b0000 : seg7_temp[7:0]<=8'b11000000;

5

学海无 涯 4'b0001 : seg7_temp[7:0]<=8'b11111001; 4'b0010 : seg7_temp[7:0]<=8'b10100100; 4'b0011 : seg7_temp[7:0]<=8'b10110000; 4'b0100 : seg7_temp[7:0]<=8'b10011001; 4'b0101 : seg7_temp[7:0]<=8'b10010010; 4'b0110 : seg7_temp[7:0]<=8'b10000010; 4'b0111 : seg7_temp[7:0]<=8'b11111000; 4'b1000 : seg7_temp[7:0]<=8'b10000000; 4'b1001 : seg7_temp[7:0]<=8'b10010000; default : seg7_temp[7:0]<=8'b10000110; endcase end endmodule

end

3

学海无 涯

state2:begin if(jin) begin if(!a) begin qh<='b0010;ql<='b0101;a<=1; r1<=1;y1<=0;g1<=0; r2=0;y2<=0;g2<=1; end else begin if(!qh&&!ql) begin next_state<=state3;a<=0; qh<='b0000;ql<='b0000; end else if(!ql) begin ql<='b1001;qh<=qh-1'b1; end else begin ql<=ql-1'b1; end end end

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

s2:if(count2!=4'b0000) begin led<=s2;count1<=count1-1;count2<=count2-1;end else begin count2<=4'b0010;st<=s3;end

3.当任意方向出现特殊情况时,应优先放行,即使各方向均亮红灯,倒计时停止,且显示数字闪烁。经过规定时间之后,恢复正常运行状态。

//计数器+控制器

module ZTJ(clk,s,count1,count2,led);

parameter s0=6'b010100,s1=6'b001100,s2=6'b100010,s3=6'b100001,s4=6'b100100;

end

else

begin

jicun<=led;

led<=s4;

count1<=count1;

count2<=count2;

i<=i+1;

if(i==4'b1001)

led<=jic译码器

module DECL7S(A,LED7S);

input [3:0] A;

output [6:0] LED7S;

endcase

end

endmodule

4'b1011: LED7S<=7'b1111100;

4'b1100: LED7S<=7'b0111001;

4'b1101: LED7S<=7'b1011110;

4'b1110: LED7S<=7'b1111001;

4'b1111: LED7S<=7'b1110001;

default:LED7S<=7'b0111111;

Ve

实验模块组成:

(计数器+控制器)可以分开实现,最好一起实现避免接口对接时出错

译码器

实验要求:

1.在十字路口两个方向各设一组红、绿、黄灯,显示顺序为:

南北方向是绿、黄、红灯;东西方向是红、绿、黄灯。

2.要求红、绿、黄灯的持续时间分别为:10s、7s、3s,东西、南北方向各用一个数码管显示倒计时时间。

input clk,s;

output[3:0]count1;

output[3:0]count2;

output[5:0]led;

reg[3:0]count1;

reg[3:0]count2;

reg[5:0]led;

reg[5:0]st;

reg[5:0]jicun;

reg[3:0]i;

always @(posedge clk)

if(s==0 & led==6'b000000)

begin

led<=s0;

st<=s0;

count1<=4'b0110;

count2<=4'b1001;

end

else if(s==0 & led!=6'b000000)

begin

case(st)

s0:if(count1!=4'b0000) begin led<=s0;count1<=count1-1;count2<=count2-1;end else begin count1<=4'b0010;st<=s1;end

reg [6:0] LED7S;

always@(A)

begin

case(A)

4'b0000: LED7S<=7'b0111111;

4'b0001: LED7S<=7'b0000110;

4'b0010: LED7S<=7'b1011011;

4'b0011: LED7S<=7'b1001111;

4'b0100: LED7S<=7'b1100110;

4'b0101: LED7S<=7'b1101101;

4'b0110: LED7S<=7'b1111101;

4'b0111: LED7S<=7'b0000111;

4'b1000: LED7S<=7'b1111111;

4'b1001: LED7S<=7'b1101111;

4'b1010: LED7S<=7'b1110111;

s3:if(count2!=4'b0000) begin led<=s3;count1<=count1-1;count2<=count2-1;end else begin count1<=4'b0110;count2<=4'b1001;st<=s0;end

default:led<=s4;

endcase