第三讲、SOPC设计流程和软硬件协同设计方法(精选)

第章sopc技术概述

Nios II /f (快速)

Nios II /s (标准) Nios II /e (经济)

针对最佳性能优化 平衡性能和尺寸 针对逻辑资源占用优化

6级 1 周期 动态 可设置 可设置

5级 3 周期 静态 可设置 无

无 软件仿真实现 无 无 无

256

256

256

1.3 Nios II软核简介

❖ 外设的可定制性

Altera公司NIOS和NIOS II Xilinx的MicroBlaze

1.3 Nios II软核简介

❖ Nios II是Altera公司2004年6月推出的第二代软核处理器。 ❖ 相对于Nios,Nios II 性能更高,占用FPGA的资源更少,

而与之配套的开发环境更先进,有更多的资源可供用户使用。 ❖ Nios II系列32位RISC嵌入式处理器具有超过200 DMIP的性

1.2 基本概念

❖ 软核

IP软核通常是用HDL文本形式提交给用户,它经过 RTL级设计优化和功能验证,但其中不含有任何具 体的物理信息。据此,用户可以综合出正确的门电 路级设计网表,并可以进行后续的结构设计,具有 很大的灵活性,借助于EDA综合工具可以很容易地 与其他外部逻辑电路合成一体,根据各种不同半导 体工艺,设计成具有不同性能的器件。软IP内核也 称为虚拟组件(VC-Virtual Component)。

1.3 Nios II软核简介

定时器/计数器 用户逻辑接口 外部SRAM接口

SDR SDRAM

PCI DDR2 SDRAM

SHA-1

外部三态桥接 EPCS串行闪存控制 器

JTAG UARTC S8900 10Base-T接口

片内ROM

直接存储器通道 (DMA)

SOC的软硬件协同设计方法和技术

SOC的软硬件协同设计方法和技术摘要:随着嵌入式系统与微电子技术的飞速发展,硬件的集成度越来越高,这使得将CPU、存储器和I/O设备集成到一个硅片上成为可能,SOC应运而生,并以其集成度高、可靠性好、产品问世周期短等特点逐步成为当前嵌入式系统设计技术的主流。

传统的嵌入式系统设计开发方法无法满足Soc设计的特殊要求,这给系统设计人员带来了巨大的挑战和机遇,因此针对Soc的设计方法学己经成为当前研究的热点课题。

论文首先分析了嵌入式系统设计的发展趋势,论述了传统设计开发方法和工具的局限性,针对Soc设计技术的特点探究了Soc软硬件协同设计方法的流程,并讨论了目前软硬件协同设计的现状。

关键词: 软硬件协同设计,可重用设计,SOC背景:计算机从1946年诞生以来,经历了一个快速发展的过程,现在的计算机没有变成科幻片电影中那样贪婪、庞大的怪物,而是变得小巧玲珑、无处不在,它们藏身在任何地方,又消失在所有地方,功能强大,却又无影无踪,这就是嵌入式系统。

嵌入式系统是以应用为中心、计算机技术为基础、软件硬件可剪裁、适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

嵌入式系统是将先进的计算机技术、微电子技术和现代电子系统技术与各个行业的具体应用相结合的产物,这一点决定了它必然是一个技术密集、高度分散、不断创新的知识集成系统。

嵌入式系纫‘泛应用于国民经济和国防建设的各个领域,发展非常迅速,调查数据表明,嵌入式系统的增长为每年18%,大约是整个信息技术产业平均增长的两倍[1],目前世界上大约有2亿台通用计算机,而嵌入式处理器大约60亿个,嵌入式系统产业是二十一世纪信息产业的重要增长点。

随着集成电路制造工艺的飞速发展,嵌入式系统硬件的集成度越来越高,这使得将嵌入式微处理器、存储器、I/O设备等硬件组成部件集成到单个芯片上成为可能,片上系统SoC (System on Chip)应运而生[2]。

SOC极大地缩小了系统体积;减少了板级系统SoB(System on Board)中芯片与芯片之间的互连延迟,从而提高了系统的性能; 强调设计重用思想,提高了设计效率,缩短了设计周期,减少了产品的上市时间。

软硬件协同设计

基于底层硬件的软件设计,涉及了设备驱动程序的设计、嵌入式实时操作系统的定制/移植、基于底层硬件的软件体系架构等实用技术。

主要包括两个方面的内容:一是通用计算机在Windows、Linux和VxWorks等常见操作系统下的串/并/网络通信实现和USB、ISA、PCI 设备/板卡的驱动程序设计;二是嵌入式应用体系的直接基本软件架构与基于μC/OS、DSP/BIOS、WinCE/EXP、μCLinux及VxWorks等常见嵌入式实时操作系统下的基本软件架构及各类常见嵌入式软件体系下的UART、SPI、CAN、EMAC、ADC、DAC、存储器件等外设/接口的驱动软件设计。

书中还介绍了如何使用CPLD/FPGA/PAC等器件进行可编程数字/模拟逻辑软件的设计,进而实现所需的特定外设/接口及其连接与FPGASoPC软硬件协同的设计。

请参考《基于底层硬件的软件设计》软硬件协同设计一、软硬件协同设计的定义:软硬件协同设计是指对系统中的软硬件部分使用统一的描述和工具进行集成开发,可完成全系统的设计验证并跨越软硬件界面进行系统优化。

二、软硬件协同设计理论:首先是系统的描述方法。

目前广泛采用的硬件描述语言是否仍然有效?如何来定义一个系统级的软件功能描述或硬件功能描述?迄今为止,尚没有一个大家公认的且可以使用的系统功能描述语言可供设计者使用。

其次是这一全新的设计理论与已有的集成电路设计理论之间的接口。

可以预见,这种全新的设计理论应该是现有集成电路设计理论的完善,是建立在现有理论之上的一个更高层次的设计理论,它与现有理论一起组成了更为完善的理论体系。

在这种假设下,这种设计理论的输出就应该是现有理论的输入。

第三,这种全新的软硬件协同设计理论将如何确定最优性原则。

显然,沿用以往的最优性准则是不够的。

除了芯片设计师们已经熟知的速度、面积等硬件优化指标外,与软件相关的如代码长度、资源利用率、稳定性等指标也必须由设计者认真地加以考虑。

SOC设计领域的核心技术——软硬件协同设计

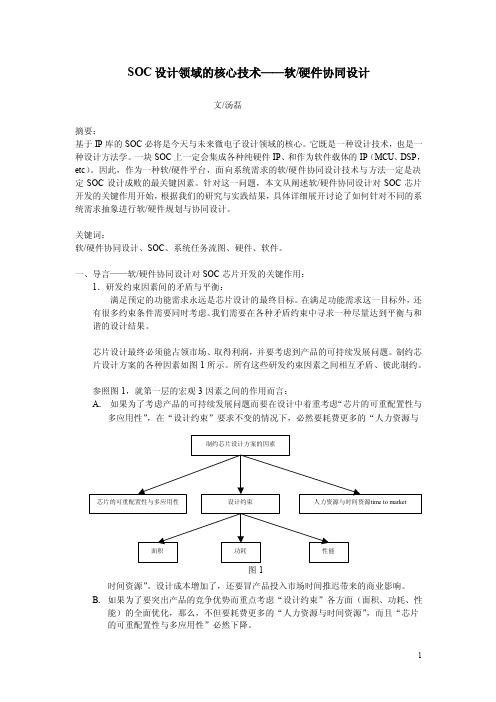

文/汤磊 摘要: 基于 IP 库的 SOC 必将是今天与未来微电子设计领域的核心。它既是一种设计技术,也是一 种设计方法学。 一块 SOC 上一定会集成各种纯硬件 IP、 和作为软件载体的 IP(MCU、 DSP, etc ) 。因此,作为一种软/硬件平台,面向系统需求的软/硬件协同设计技术与方法一定是决 定 SOC 设计成败的最关键因素。针对这一问题,本文从阐述软/硬件协同设计对 SOC 芯片 开发的关键作用开始, 根据我们的研究与实践结果, 具体详细展开讨论了如何针对不同的系 统需求抽象进行软/硬件规划与协同设计。 关键词: 软/硬件协同设计、SOC、系统任务流图、硬件、软件。 一、导言——软/硬件协同设计对 SOC 芯片开发的关键作用: 1.研发约束因素间的矛盾与平衡: 满足预定的功能需求永远是芯片设计的最终目标。 在满足功能需求这一目标外, 还 有很多约束条件需要同时考虑。 我们需要在各种矛盾约束中寻求一种尽量达到平衡与和 谐的设计结果。 芯片设计最终必须能占领市场、取得利润,并要考虑到产品的可持续发展问题。制约芯 片设计方案的各种因素如图 1 所示。所有这些研发约束因素之间相互矛盾、彼此制约。 参照图 1,就第一层的宏观 3 因素之间的作用而言: A. 如果为了考虑产品的可持续发展问题而要在设计中着重考虑 “芯片的可重配置性与 多应用性” ,在“设计约束”要求不变的情况下,必然要耗费更多的“人力资源与

3

列。 如果要在实际设计中强调某一款专用芯片的可重配置性与多应用性,一个最有效的方 法,就是尽可能考虑到各个应用的大体功能需求,即每个单应用的单任务流图形式,然 后将各个单任务流图看作一个彼此互斥的多分支总系统任务流图来进行系统架构规划。 简单举例: TD-SCDMA、GSM、可视电话 3 模合一应用下(下行链路)的多分支系统 任务流图粗框架如图 2 所示: 多分支系统任务流图软/硬件划分原则如下: A. 首先采用算法将不同分支间功能相似的子任务节点尽可能进行一一自动对应。 B. 各个分支间,完全对应相同的子任务节点由硬件完成。 (比如,假设如果 3 个应用模 式下的语音解码协议完全相同,则完全可将语音解码部分做成纯硬件。 ) C. 各个分支间任务有差别的相对应节点由软件完成。 (如:3 种应用下彼此不同的协议 栈处理工作) D. 各个分支间任务不同, 但不适宜由软件完成的工作, 由不同硬件各自单独完成。 (比 如: 对于芯片的 3 模应用, 架构中一定要有 TD-RFIO、 GSM-RFIO、 可视电话 UART 3 个各自独立的对外接口模块,这里暂不讨论软件无线电的可实现性。 ) E. 软件载体(MCU、DSP)的最大处理能力应该由已被划分为软件任务的、各个分支 间任务相似的相对应节点对软件性能需求的最大值来决定。 (如图: 假设可视电话和 TD 的信源解码都要求有语音及图象解码能力,而 GSM 的信源解码只要求有语音解 码能力。则芯片中 DSP 的性能必须具备语音及图象解码能力。 ) 根据研究,对多分支系统任务流图,由于不同分支间的互斥性与分时性,可以将各个分 支进行基于对应节点功能相似度的图形合并,由此生成一张复合任务流图[3,4]。复合 任务流图中的每一个复合节点子任务,由生成该复合节点的原各个分支间相对应节点的 功能集之合集组成。 例如,上述 TD-SCDMA、GSM、可视电话 3 模式应用下的多分支系统任务流图的复合 任务流图粗框架形式如图 2 右所示。也就是说,对于多分支系统任务流图,我们可以通 过图论的方法将各个分支进行任务合并生成一张复合任务流图,当且仅当系统架构能够 胜任复合任务流图的功能及性能需求时,芯片设计能够满足所预定的可重配置性与多应 用性的需要。 (关于“基于节点任务相似度的多图自动化合并算法”可参考[3,4]。 ) 六、并行系统任务流图的软/硬件协同设计方法: 多并行与多分支系统任务的最大区别是各单任务流图在时间上并行因此不能进行合并。 比如对于手机基带芯片的应用而言,通话过程的上行与下行任务之间就可视为并行任 务。而对于手机大多数的其它功能需求,如:发短信、记事本、打游戏、上网、MP3, 等等,它们通常不可能与通话过程同时进行,并且它们彼此之间并行的可能性也不高。 我们可将其相互之间视为多分支系统任务[1]。各个分支任务的多样性适宜由软件来完 成,而软件载体(MCU、DSP)的最大处理能力则由各个分支间相对应各节点对软件性 能需求的最大值来决定。

SOPC开发流程及开发平台简介PPT课件

分配外设地址和中断

生成系统

SOPC Builder GUI

自定义命令

IP

模块

处理器库

外设模块库

硬件开发

Nios II IDE

软件开发

Quartus II

GNU Tools

HDL 源文件 测试台

用户逻辑设计 其它的IP模块 SOPC Builder的 顶层.bdf文件

2.1 SOPC开发流程

软件开发

配置Nios II处理器

选择并配置外设.IP

连接各外设模块

分配外设地址和中断

生成系统

SOPC Builder GUI

自定义命令

IP

模块

处理器库

外设模块库

硬件开发

Nios II IDE

软件开发

Quartus II

GNU Tools

使用SOPC Builder生成系统后,可以直接使用Nios II IDE开始设计C/C++应用程序代码。Altera提供外设驱动程序和硬件抽象层(HAL),使用户能够快速编写与低级硬件细节无关的Nios II程序;

2.1 SOPC开发流程

QuartusII: 用于完成Nios II系统的分析综合、硬件优化、适配、配置文件编程下载以及硬件系统测试等;

SOPC Builder: 它是Nios II软核处理器的开发包,用于实现Nios II系统配置、生成以及与Nios II系统相关的监控和软件调试平台的生成;

Nios II IDE: 用于完成基于Nios II系统的软件开发和调试,并可借助其自带的Flash编程器完成对Flash以及EPCS的编程操作。

2.1 SOPC开发流程

SOC第二章设计流程

• • •

• 3)软、硬件协同设计的流程 软

(1).系统需求说明 系统设计首先从确定所需的 功能开始,包含系统基本输入 和输出及基本算法需求,以及 系统要求的功能、性能、功耗 、成本和开发时间等。在这一 阶段,通常会将用户的需求转 换为用于设计的技术文档,并 初步确定系统的设计流程。

• •

• •

第二章

SoC设计流程 设计流程

Outlines

• 1 软、硬件协同设计方法 • 2 基于标准单元的 芯片设计流程 基于标准单元的SoC芯片设计流程

2.1 软、硬件协同设计

• The hardware and software in an

embedded system work together to solve a problem • How to partition is usually dictated by speed and cost

).高级算法建模与仿真 (2).高级算法建模与仿真 ). 在确定流程后,设计者将使用如C和 在确定流程后,设计者将使用如 和C++等高级语言创建 等高级语言创建 整个系统的高级算法模型和仿真模型。目前,一些EDA工 整个系统的高级算法模型和仿真模型。目前,一些 工 具可以帮助我们完成这一步骤。有了高级算法模型, 具可以帮助我们完成这一步骤。有了高级算法模型,便可 以得到软、硬件协同仿真所需的可执行的说明文档。 以得到软、硬件协同仿真所需的可执行的说明文档。此类 文档会随着设计进程的深入而不断地完善和细化。 文档会随着设计进程的深入而不断地完善和细化。 (3).软、硬件划分过程 ).软 ). 这一环节包括软、硬件划分和任务分配。设计者通过软、 这一环节包括软、硬件划分和任务分配。设计者通过软、 硬件划分来决定哪些功能应该由硬件完成, 硬件划分来决定哪些功能应该由硬件完成,哪些功能应该 由软件来实现。 由软件来实现。软、硬件划分的合理性对系统的实现至关 重要。通常,在复杂的系统中,软件和硬件都比较复杂。 重要。通常,在复杂的系统中,软件和硬件都比较复杂。 有些功能既可以用软件实现也可以用硬件实现,这取决于 有些功能既可以用软件实现也可以用硬件实现, 所要达到的性能指标与实现的复杂程度及成本控制等因素。 所要达到的性能指标与实现的复杂程度及成本控制等因素。 对比而言,两者各有千秋。 对比而言,两者各有千秋。

SOPC方案

SOPC方案引言:在当今数字技术高速发展的时代,各类电子设备的设计与开发成为了不可或缺的一环。

嵌入式系统的设计需求越来越复杂,为了满足这一需求,诞生了SOPC(System on a Programmable Chip)方案。

本文将详细介绍SOPC方案的定义、优势以及应用领域,以便更好地理解和应用该方案。

定义:SOPC是一种将系统级硬件和软件集成在一个可编程芯片上的设计方案。

通过SOPC方案,用户可以根据自己的需求灵活设计硬件系统,并利用编程方式控制系统的功能和性能。

SOPC方案的核心是可编程逻辑器件,如FPGA(Field Programmable Gate Array)。

优势:1. 灵活性:SOPC方案采用可编程芯片,使得系统硬件可以根据需求进行灵活定制。

不同于传统固定功能的硬件电路,SOPC方案可以根据用户的具体需求进行设计和修改,提供更加灵活的解决方案。

2. 可重构性:利用SOPC方案,用户可以通过重新配置硬件逻辑通过编程方式快速修改和调整系统功能。

这种可重配置性使得系统在设计阶段和实际应用中具备更强的适应性和可扩展性。

3. 性能优化:通过SOPC方案,用户可以根据应用的需求和资源限制精确控制系统的功能和性能。

此外,由于硬件和软件的紧密结合,SOPC方案有助于提高系统的运行效率和优化功耗。

4. 开发效率:SOPC方案通过软件和硬件的集成,简化了系统设计的流程。

借助现成的IP核(Intellectual Property Core)和开发工具,开发人员可以快速搭建嵌入式系统,并且可以使用高级编程语言进行开发。

应用领域:1. 通信领域:SOPC方案在通信设备的设计中得到了广泛应用。

通过SOPC方案,通信设备可以适应不同的接口、协议和传输速率,并且可以进行灵活的调试和维护。

2. 工业自动化:SOPC方案可以用于工业自动化控制系统的设计与开发。

通过SOPC方案,工控系统可以根据具体要求进行硬件逻辑的编程,实现自动化控制和数据采集等功能。

基于SOPC的软硬件协同设计平台的研究与实现

软硬件协同设计方法的未来发展 趋势

1、标准化

随着软硬件协同设计方法的逐渐普及,标准化将成为未来发展的重要趋势。 通过制定统一的标准和规范,可以降低设计的复杂度,提高设计的可重复性和可 维护性。

2、智能化

智能化是软硬件协同设计的另一重要趋势。借助人工智能和机器学习等技术, 可以使软硬件协同设计过程更加自动化和智能化,提高设计的效率和准确性。

基于SOPC的软硬件协同设计平 台的研究与实现

01 一、概述

目录

02 二、原理与实现

03 三、优化与改进

04 四、应用与前景

05 参考内容

随着科技的快速发展,嵌入式系统设计面临着越来越高的性能和功能要求。 为了满足这些要求,基于SOPC(System-on-a-Programmable-Chip)的软硬件协 同设计平台逐渐成为研究热点。本次演示将介绍基于SOPC的软硬件协同设计平台 的意义和研究背景,阐述软硬件协同设计平台的原理和实现方法,分析优化与改 进方法,并探讨应用与前景。

感谢观看

随着信息技术的飞速发展,软硬件协同设计方法在信息系统中的重要性日益 凸显。本次演示将深入探讨软硬件协同设计方法的研究现状、关键技术以及未来 发展趋势,分析现有研究的不足之处,并提出未来可能的研究方向。

软硬件协同设计方法的研究现状

软硬件协同设计是指在系统设计过程中,同时考虑硬件和软件的需求、设计 和优化,以达到整个系统的最佳性能。近年来,国内外学者针对软硬件协同设计 方法进行了广泛研究,取得了诸多成果。例如,基于模型的系统工程(MBSE)方 法、基于代理的软硬件协同设计方法等。然而,在实际应用中,软硬件协同设计 方法的普及率并不高,仍存在一些不足之处,如对设计人员技能要求较高,设计 周期较长等。

SOPC设计流程和软硬件协同设计方法

SOPC设计流程

SOPC由于硬件和软件都必须自己设计和定制,它 与传统的嵌入式系统设计流程不同;在传统的嵌入式 系统开发中,其主控芯片一般是专用的集成电路,其 结构是固定的,比如ARM系列的4510、44B0X、2410等 等,这种控制器的外设已经设计好,而且地址都已经 固定,设计人员只要关心PCB设计和软件开发。对于 SOPC的开发,设计人员必须同时关注片内硬件逻辑的

• HDL语言(VHDL 或 Verilog HDL) • 原理图(可移植性差) • 网表 • 符合某种EDA工具的特定格式

2020/8/13

IP Core的分类--SOPC的要素

Vs.ASIC

• 微处理器IP Core

– 8/16/32/64位,如MicroBlaze、Nois、8051

• 处理器外设IP Core

• 由于FPGA密度达到了百万门甚至千万门,越来越多 的设计师倾向于使用IP核来保持和提高产品的产量。

• FPGA的设计成本低廉, 可作为切实可行的生产工具 以及最佳原型设计,从而大大降低了设计门槛。

2020/8/13

IP Core 存在形式

IP分为软IP、固IP和硬IP。 • 软IP是指描述功能块的行为的HDL程序包,它

❖1.基于Altera FPGA的SOPC 设计流程及设计工具

2020/8/13

§ 1.1. EDA技术的发展趋势

3. 可编程器件设计环境

Altera

Xilinx Lattice

MAX+PLUS Ⅱ

支持硬核 ARM922T

QuartusⅡ 支持软核 Nios Ⅱ

Foundation

ISE Platform Studio 硬核PowerPC405 软核 MicroBlaze

SOPC设计

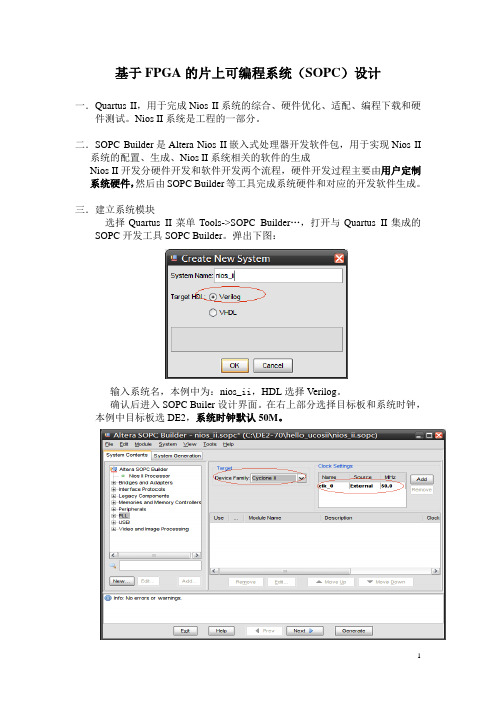

基于FPGA的片上可编程系统(SOPC)设计一.Quartus II,用于完成Nios II系统的综合、硬件优化、适配、编程下载和硬件测试。

Nios II系统是工程的一部分。

二.SOPC Builder是Altera Nios II嵌入式处理器开发软件包,用于实现Nios II 系统的配置、生成、Nios II系统相关的软件的生成Nios II开发分硬件开发和软件开发两个流程,硬件开发过程主要由用户定制系统硬件,然后由SOPC Builder等工具完成系统硬件和对应的开发软件生成。

三.建立系统模块选择Quartus II菜单Tools->SOPC Builder…,打开与Quartus II集成的SOPC开发工具SOPC Builder。

弹出下图:输入系统名,本例中为:nios_ii,HDL选择Verilog。

确认后进入SOPC Builer设计界面。

在右上部分选择目标板和系统时钟,本例中目标板选DE2,系统时钟默认50M。

1.定制Nios 处理器(CPU Core)首先加入的是CPU核,选择组件栏中的Avalon Modules ->Nios II Processor右键点击,选择Add New Nios II Processor Altera Corporation…,打开配置对话框如下图:Nios II提供三个选项,经济、标准、快速的CPU核,我们选经济核。

其他选项表单中都默认,点击Finish完成。

并选择JTAG调试模块,Level1。

2. 加入on_chip_memory使用FPGA内部RAM资源,可以构成RAM或ROM,速度快,特别在调试时因为很少受外部连线等因素的限制很有用。

组件栏中选择Legacy Components->On-Chip Memory打开界面,如下图:定义了4k字节的RAM。

3. 加入JTAG(联合测试行动组)串口JTAG UART在调试中非常有用,在PC主机和FPGA之间进行串行字符流通信。

SOPC系统设计

SOPC系统架构 SOPC系统架构

2. Avalon 总线

Avalon 总线是一种相对简单的总线结构,主要用于 连接片内处理器与外设,以构成片上可编程系统 (SOPC)。它描述了主从构件间的端口连接关系, 以及构件间通讯的时序关系。

SOPC系统架构 SOPC系统架构

Avalon 总线模块框图

SOPC系统架构 SOPC系统架构

3. 外设IP模块

设计者可以添加下列模块到 SOPC Builder 中: • Nios 32 位 CPU • 片上 Boot Monitor ROM • UART(通用异步串行接口) • 定时器 • 按键 PIO(可编程输入输出) • LCD PIO • LED PIO • 七段显示PIO • 外部RAM总线(Avalon三状态桥) • 外部RAM接口 • 外部Flash接口

● 在Quartus

Ⅱ中执行 “Tools>Programmer”命令,将 quartus_nios2_project.sof下载到目标芯 片上。(sof是FPGA下载文件。 )

注意:在将程序下载到 中之前, 注意:在将程序下载到FPGA中之前,首 中之前 先要先将SOF文件下载到 文件下载到FPGA中! 先要先将 文件下载到 中

SOPC系统设计 SOPC系统设计 二、软件设计部分

● 在资源管理器自己的QuartusⅡ工程目录下

创建一个文件夹 ● 启动Nios Ⅱ IDE ● 创建一个Nios Ⅱ IDE工程 ● 设计源代码 ● 编译工程 ● 将程序下载到FPGA中在线运行

SOPC系统设计 SOPC系统设计

软件开发流程

SOPC系统设计 SOPC系统设计 二、软件设计部分

SOPC系统架构 SOPC系统架构

嵌入式技术概述--SOPC硬件开发环境及硬件开发流程介绍 ppt课件

能 模 块

配

置

配 置

件 到

工 程

文 件

SOF

FPGA

•系统所需的计 算性能、带宽、 吞吐量、接口 类型以及多线 程软件支持等。

用户定制指令与外设

•若 需要 , 用

标

户可以定制

准

指令和外设

库 模

逻辑。

块

SOPC硬件设计流程

•当 标 准 库 模 块不能满足设 计 要Ni求osⅡ时内,核和可标准外设 设计定制逻辑 模块。

SOPC硬件设计实例

电子钟设计:2)创建NiosⅡ系统模块

2-2)创建NiosⅡ系统模块: 4) LCD控制器的添加,在Avalon components中的display 库中选择Character LCD(162, Optrex 16027) 。

SOPC硬件设计实例

电子钟设计:2)创建NiosⅡ系统模块

SOPC硬件设计实例

电子钟设计:2)创建NiosⅡ系统模块

2-2)创建NiosⅡ系统模块: 2)定时器的添加,在Avalon components中的other库中选 择Interval Timer。

SOPC硬件设计实例

电子钟设计:2)创建NiosⅡ系统模块

2-2)创建NiosⅡ系统模块: 3) PIO(按键)的添加,在Avalon components中的other 库中选择PIO 。

电子钟设计:2)创建NiosⅡ系统模块

2-1)创建顶层实体:选择FileSave As;确定Add to Current Project选项被选中,点 击“保存”,文件被保存并被加入到工程中。

SOPC硬件设计实例

电子钟设计:2)创建NiosⅡ系统模块

2-2)创建NiosⅡ系统模块:启动SOPC Builder,选择ToolsSOPC Builder,出现 Create New System对话框。

SOPC开发流程及开发平台简介

案例二:智能门禁系统的SOPC开发

要点一

总结词

要点二

详细描述

智能门禁系统是SOPC开发的另一个应用领域,通过集成微 处理器、读卡器、显示屏等模块,实现门禁的智能化管理 。

智能门禁系统SOPC开发同样涉及硬件设计、逻辑设计、 系统集成等多个环节。在硬件设计方面,需要选择合适的 读卡器、显示屏等器件,并设计合理的电路板布局和布线 。在逻辑设计方面,需要编写门禁控制程序和算法,实现 门禁的智能化管理。在系统集成方面,需要将各个模块进 行整合,并进行测试和调试,确保系统的稳定性和可靠性 。

IP核

可重用的硬件模块,用于加速SOPC系统的开发,如处理器核、存储器控制器等。

硬件描述语言

用于描述硬件逻辑的编程语言,如VHDL和Verilog。

软件开发平台

嵌入式操作系统

提供多任务管理和系统资源 管理功能,如Linux、 VxWorks等。

1

开发工具

用于编写、编译和调试应用 程序的软件工具,如Eclipse

IP核

用于设计可复用的硬件模块,如CPU、DSP、GPU等。IP核可以由第三方提供,也可以 自己开发。

软件开发工具

编译器

01

调试器

பைடு நூலகம்02

03

集成开发环境(IDE)

用于将高级语言编写的程序编译 成机器码,常见的编译器有GCC、 Clang等。

用于调试程序,常见的调试器有 GDB、JTAG等。

用于编写、编译、调试程序,常 见的IDE有Eclipse、Visual Studio等。

通信领域

信号处理

SOPC技术在通信领域广泛应用于信号处理,如调制解调、信道编解码等。

高速串行接口

SOPC技术可以实现高速串行接口,如PCI Express、Serial RapidIO等,用于高速数据传输。

嵌入式系统3-嵌入式系统设计-软硬件协同设计技术

嵌入式系统设计嵌入式系统设计过程概念特性,特征硬件/软件划分硬件组成部分软件组成部分Estimation -Exploration硬件软件设计(S yn t he s is,La y ou t,…)设计(C om pi l at i on,…)验证和评估(尺寸, 功耗, 性能, …)传统软件/硬件开发模型面临的问题Break the wall today!传统设计方法存在的问题z缺少统一的软硬件表示方法z划分依靠先验定义z不能够验证整个系统z通过HW/SW 边界时很难发现不兼容问题z缺少成熟的设计流程z上市时间问题z描述更改变得困难发展过程z软硬件协同设计早期–主要是针对一个特定的硬件如何进行软件开发或根据一个已有的软件实现具体的硬件结构。

z前者是一个经典的软件开发问题–软件性能的好坏不仅仅取决于软件开发人员的技术水平,更有赖于所使用的硬件平台;z后者是一个软件固化的问题–实现的途径可以是采用一个与原有软件平台相同的硬件处理器,并将软件代码存储于存储器当中,也可以是在充分理解软件的内在功能之后完全用硬件来实现软件的功能。

软硬件共同设计能带来什么?z缩短开发周期z取得更好的设计效果z满足苛刻的设计限制z这种平台的推出将不仅包含芯片本身,还必须包含完整的开发系统和典型应用实例,而供应商提供的服务和技术支持也当然要成为产品不可分割的一部分。

目标和需求z统一的设计方法z执行独立z设计/执行验证z自动软件,硬件,接口合成商业应用z Research(研究)–CADLab, SIR/CASTLE (Germany), Chinook,COSMOS, COSYMA, CoWare, DICE,COMET, LYCOS (Denmark), POLIS,Ptolemy, Riley, TOSCA, AKKA, CODES,VIOOL, COOL…z Commercial(商业)–ArchGen(Synergy System Design, Inc.),Mentor Graphics, Synopsys, Synthesia->Cadence, Co-design Automation->Synopsys, Celoxica, CoWare, etc.缺点z典型的手动划分(manual Partition )z固定应用领域(carefully very specialized) z逐渐增长的评估需求支持很弱(no abstractmodels)z主要强调性能z模型的连贯性在设计重用中不被支持z商业系统更强调协同验证(co-verification)方面(more achievable goal)软硬件协同设计定义z软硬件协同设计定义–The meeting of system-level objectives byexploiting the trade-offs between hardware and software in a system through their concurrentdesign–软硬件共同设计目的是为硬件和软件的协同描述,验证和综合提供一种集成环境。

SOPC设计流程和软硬件协同设计方法教学案例

– 划分策略 - high level partitioning by hand, automated partitioning using various techniques, etc.

• 软硬件设计(同时进行) • 交互设计 • 设计验证

• 关键技术(如可编程逻辑综合技术、器件接口 和功能模型描述)的进步使得软硬件交互设计 变得简单起来

2020/10/11

Thank you!

2020/10/11

• 因此: – Poor quality designs(设计质量差) – Costly modifications(设计修改难) – Schedule slippages(研制周期不能有效保障)

2020/10/11

软硬件协同设计过程

• 系统定义(需求分析) • 软硬件划分

– 结构规划 – 处理器类型, 软硬件之间的接口类型, 等 .

❖1.基于Altera FPGA的SOPC 设计流程及设计工具

2020/10/11

§ 1.1. EDA技术的发展趋势

3. 可编程器件设计环境

Altera

Xilinx Lattice

MAX+PLUS Ⅱ

支持硬核 ARM922T

QuartusⅡ 支持软核 Nios Ⅱ

Foundation

ISE Platform Studio 硬核PowerPC405 软核 MicroBlaze

2020/10/11

软硬件协同设计定义与主要概念

2020/10/11

传统的嵌入式ห้องสมุดไป่ตู้统设计过程

• 传统软硬件设计过程的基本特征: – 系统在一开始就被划分为软件和硬件两大部分 – 软件和硬件独立进行开发设计 – “Hardware first” approach often adopted

简要叙述软硬件协同设计的基本流程

英文回答:Co—design of software and hardware is an important part of our product design process, which aims to maximize the synergy of hardware and software engineers and to ensure the soundness and efficiency of product functions and structures. Basic processes include four phases of needs analysis, architecture design, interface definition and validation testing. During the needs analysis phase, hardware and software engineers should listen extensively to user needs and ensure that product needs are clear and clear. During the architecture design phase, the software and hardware engineers are required to consult fully to determine the system architecture and division of labour. During the interface definition phase, hardware and software engineers are required to standardize the definition of interface protocols to ensure proper systemmunication. Finally, during the validation testing phase, hardware and software engineers should actively cooperate to ensure the reliability of products. Through this process, our co—engineering of software and hardware can improve the efficiency and quality of product research and development, be in line with the national strategy for science and technology development and promote technological innovation andindustrial upgrading.软硬件协同设计是我国产品设计过程中的重要一环,旨在充分发挥软硬件工程师的协同作用,确保产品功能和架构的合理性和高效性。

简要叙述软硬件协同设计的基本流程

简要叙述软硬件协同设计的基本流程英文回答:Basic Flow of Software-Hardware Co-Design:The basic flow of software-hardware co-design involves the following steps:1. Requirement Analysis and Specification: Determine the system requirements, including both hardware and software components.2. System Architecture Design: Partition the system into hardware and software subsystems, considering performance, cost, and feasibility constraints.3. Hardware Architecture Design: Design the hardware architecture, including processors, memory, and I/O interfaces.4. Software Architecture Design: Design the software architecture, including software components, communication protocols, and data structures.5. Co-Simulation and Validation: Simulate the hardware and software systems together to verify their interaction and functionality.6. Integration and Testing: Integrate the hardware and software components and test their overall performance and compliance with requirements.7. Deployment and Maintenance: Deploy the system and provide ongoing maintenance and updates.中文回答:软硬件协同设计的基本流程:软硬件协同设计的基本流程包括以下步骤:1. 需求分析与规范,明确系统需求,包括硬件和软件组件。

(3)软硬件协同设计技术

2014-7-31

15

软硬件协同设计基本步骤 Specification(设计描述)

List the functions of a system that describe the behavior of an abstraction clearly with out ambiguity. Process of conceptualizing and refining the specifications, and producing a hardware and software model.

CSCI Testing

2014-7-31

5

传统的嵌入式系统设计过程

传统软硬件设计过程的基本特征: 系统在一开始就被划分为软件和硬件两大部分 软件和硬件独立进行开发设计 “Hardware first” approach often adopted 隐含的一些问题: 软硬件之间的交互受到很大限制 软硬件之间的相互性能影响很难评估 系统集成相对滞后,NRE较大 因此: Poor quality designs(设计质量差) Costly modifications(设计修改难) Schedule slippages(研制周期不能有效保障)

18

协同设计中的软硬件划分与调度

A hardware/software partitioning represents a physical partition of system functionality into application-specific hardware and software. Scheduling is to assign an execution start time to each task in a set, where tasks are linked by some relations.