嵌入式硬件开发平台共43页文档

第三章嵌入式硬件平台设计优秀课件

LCD 显 示 及触摸屏

32M字 节 Flash(BIOS)

64MB SDRAM 系统内存

16M字 节 NAND FLASH

基 于 ARM920T的 32位 微 处 理 器

35

电源电路-参考电路

36

时钟电路

时钟电路用于向CPU及其它电路提供工作时钟,S3C2410使用无 源晶振,晶振的接法如下图所示

1、主时钟电路 2、RTC时钟电路 3、主时钟及USB时钟滤波

主时钟 电路

RTC时钟 电路

主时钟及USB 时钟滤波

37

时钟电路

1、S32410有两个锁相环,一个用于FCLK、HCLK和 PCLK,另一个专门用于USB模块

S3C2410扩展系统

S3C2410最小系统 + SDRAM + FLASH电路可构成一个完全的 嵌入式系统

可运行于SDRAM中的程序,也可以运行FLASH中的程序

程序大小可以很大,如果将程序保存到FLASH中,掉电后不 会丢失,因此,既可以通过JTAG接口调试程序,也可以将程序 烧写到FLASH,然后运行FLASH中的程序

33

电源电路-需求分析

1、一般是多电源系统,I/O一般为3.3V供电,内核为2.5V (S3C44B0)、 1.8V(S3C2410)供电,有可能还包含 5V或12V等电源; 2、 一般将数字电源和模拟电源分别供电; 3、要求电源纹波比较小,一般采用LDO(low dropout regulator,低压差线性稳压器 )供电;

38

复位电路

由RC电路及施密特触发器组成:

39

JTAG调试接口电路

嵌入式系统开发平台

辽宁工程技术大学上机实验报告

实验内容一、实验内容

1.建立一个工程文件。

2.建立一个汇编程序,实现数据段大量数据的复制功能,并添加到工程中。

3.设置编译连接控制选项

4.编译连接工程

5.使用AXD调试工程,方法可以采用

(1)模拟指令集形式

(2)下载到SDRAM或FLASH中硬件调试。

二、实验原理

1. H-JTAG软件是免费JTAG调试和Flasher擦写软件,通过并口线连接目标板。

此软件针对EEliod开发平台和XSBASE 270-S开发板(或其它PXA270的开发板),需要进行配置才能正常工作。

2. ADS 是ARM 系统的一个集成开发环境,提供程序编写、编译、连接、生成映像的功能,可以用来调试PXA270开发板

三、实验步骤

1.配置实验环境

(1)建立工作文档

复制选中的两个文件夹并且粘贴至C盘根目录下

导入ADS许可证

(2)连接开发板和电脑

2.调试软件环境

(1)打开H-JTAG软件,显示出开发板的CPU型号为PXA270,说明电脑与开发板连接

成功。

(2)配置ADS软件。

3.将程序传送到开发板

实验分析调试方法和运行结果

1.编译并运行程序

2 .观察开发板

开发板的8个发光二极管从左到右依次发光,说明程序正确运行。

3.修改源程序,再次运行。

开发板的8个发光二极管从右到左依次发光,修改后的程序运行正确。

嵌入式系统(第章 嵌入式系统硬件平台与接口设计)ppt课件

Bank5:RTL8019AS,ISA总线兼容的10M以太网( PHY+MAC层)控制芯片。占用系统外部中断1,16位 数据总线;扩展IO口

Bank6:SDRAM,起始地址为0xC000000。在 SDRAM中,前512Kbyte的空间划分出来,作为系统 的LCD显示缓冲区使用(更新其中的数据,就可以更新 LCD的显示)。系统的程序存储空间从0xC080000开 始。也就是,引导系统的时候,需要把system.bin文件 复制到0xC080000开始的地址空间,把PC指针指向 0xC080000。

9

详细设计阶段-硬件设计

1. 设计硬件子系统:top-down方法 1. 分成模块 2. 设计框图 3. 例:CPU子系统、存储器子系统等

2. 定义硬件接口 1. I/O端口 2. 硬件寄存器 3. 共享内存 4. 硬件中断 5. 存储器空间分配 6. 处理器的运行速度

10

详细设计阶段-软件设计

29

3) Boot Loader的任务

Boot Loader是系统加电后首先运行的一段代码,完成 整个系统的加载启动任务。它首先完成系统硬件的初始 化,包括时钟的设置、存储器的映射等。并设置堆栈指 针,然后跳转到操作系统内核入口,如系统在加电或复 位时通常从地址0x00000000处开始执行,而在这个地 址处安排的通常就是系统的Boot Loader程序。

7

2)体系结构设计

决定因素

1. 系统是硬实时系统还是软实时系统 2. 操作系统是否需要嵌入 3. 物理系统的成本、尺寸和耗电量是否是产

品成功的关键因素 4. 选择处理器和相关硬件 5. 其他

8

3)详细设计阶段-硬件与软件划分 决定哪些用硬件实现,哪些用软件实现? 例如:

嵌入式系统硬件平台

✓利用改变内部工作电压,降低芯片功耗。

✓减少芯片对外管脚数,简化制造过程。

✓减少外围驱动接口单元及电路板之间的信号传递, 可以加快微处理器数据处理的速度。

✓内嵌的线路可以避免外部电路板在信号传递时所 造成系统杂讯。

12

嵌入式片上系统(System On Chip)(4)

13

嵌入式硬件开发工具(1)

嵌入式开发需要提供强大的硬件开发工具和软件包 支持。 1.硬件:速度、功能、成本。 更强大的嵌入式处理器如32 位、64位RISC芯片或信 号处理器、DSP 增强处理能力,同时增加功能接口, 如USB,扩展总线类型,如CAN BUS,加强对多媒体、 图形等的处理,逐步实施片上系统(SOC)的概念。

第四章 嵌入式系统硬件平台

嵌入式处理器及其分类 典型的嵌入式处理器 嵌入式系统常见外设

1

嵌入式系统硬件体系结构

2

嵌入式微处理器

3

嵌入式微控制器

典型代表:单片机这种8位的电子器件,目前 在嵌入式设备中仍然有着极其广泛的应用。

单片机芯片内部集成ROM/EPROM 、RAM 、总 线、总线逻辑、定时/计数器、看门狗、I/O 、 串行口、脉宽调制输出、A/D 、D/A 、Flash RAM 、EEPROM 等各种必要功能和外设

常友好的用户界面。手写文字输入、语音拨号上网、收发电

子邮件以及彩色图形、图像都会使使用者获得自由的感受。

17

典型的嵌入式微处理器(1)

1 .ARM/StrongARM

ARM (Advanced RISC Machines )公司是全球领先的16/32 位 RISC 微处理器知识产权设计供应商。ARM 公司通过转让它的 高性能、低成本、功耗低的RISC 微处理器、外围和系统芯片设 计技术给合作伙伴来生产各具特色的芯片。ARM 公司已成为移 动通信、手持设备、多媒体数字消费嵌入式解决方案的RISC 标 准。

嵌入式系统 嵌入式系统硬件平台与接口设计PPT课件

4)系统集成

把系统的软件、硬件和执行装置集成在一起, 进行调试,发现并改进设计过程中的错误。

5)系统测试

对设计好的系统进行测试,看其是否满足给 定的要求。

第12页/共120页

嵌入式系统的硬件体系结构

通用微处理器

可重构计算机

ASIC

应用软件

配置存储器

通用嵌入式 微处理器

可重构 计算部件

第32页/共120页

但在具有MMU的ARM系统中,存储管理 单元MMU主要完成工作: • 虚拟存储空间到物理存储空间的映射。在 ARM中采用了页式虚拟存储管理。 • 存储器访问权限的控制。 • 设置虚拟存储空间的缓冲的特性。

第33页/共120页

2410的UART

• S3C2410A 的UART (Universal Asynchronous Receiver and Transmitter) 提供了三个独立的异步 串行I/O口,每一个都可以工作在中断模式或DMA模式, 即UART可以产生中断或DMA请求以在CPU和UART之 前传送数据,使用系统时钟,UART最高可以支持 230.4K bps 的位传输率。

第5页/共120页

需求分析-罗列用户的需求

(11)系统的响应时间是多少? (12)需要什么安全措施? (13)系统在什么样的环境下运行? (14)外部存储媒介和内存需要多大? (15)系统的可拆装性,可靠性和牢固性的期望值是什么 (16)如何给系统供电? (17)系统如何向用户通报故障? (18)是否需要任何手动或机械代用装置? (19)系统是否将具有远程诊断或更正问题的功能? (20)其他问题

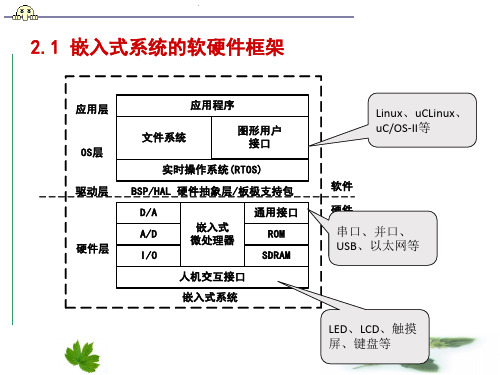

嵌入式系统的软/硬件框架

驱动器1 驱动器2

...... 驱动器N

嵌入式系统原理与开发(第三版)课件:嵌入式硬件平台

嵌入式硬件平台

嵌入式硬件平台

嵌入式硬件平台

3.1 引言 3.2 嵌入式硬件平台概述 3.3 总线 3.4 存储设备 3.5 I/O设备 3.6 通信设备 3.7 其他 思考与练习题

嵌入式硬件平台

3.1 引 言

嵌入式系统的硬件除了核心部件——嵌入式处理器外, 还包括存储器系统、外围接口部件以及连接各种设备的总线 系统。其中,存储器是嵌入式系统存放数据和程序的功能部 件,而外围设备则决定了应用于不同领域的嵌入式系统的独 特功能。

嵌入式硬件平台

2.总线读/写 微处理器总线在握手基础上为CPU和系统其他部分建立 通信。基本的总线操作包括读和写。图3-3说明了一个支持 读和写的典型总线结构。

嵌入式硬件平台 图3-3 典型的微处理器总线

嵌入式硬件平台

➢ Clock提供总线组件各部分的同步。 ➢ 当总线读时,R/W‘ 为1;当总线写时,R/W’ 为0。 ➢ Address是一个a位信号束,为访问提供地址。 ➢ Data是一个n位信号束,它可以从CPU得到数据或向 CPU传送数据。 ➢ 当数据线上的值合法时,Data ready' 发信号。

嵌入式硬件平台

总线行为经常用时序图来说明,时序图表示了总线上的 信号如何随时间变化。图3-4所示为某总线的时序图,包括 读和写两部分。由于读不改变设备和存储器的任何状态,因 此总线通常处于读状态。CPU可以忽略数据线直到它要使用 读操作的结果为止。此外,还要注意在双向线路上数据的传 输方向并未在时序图中指定。在读过程中,外设或存储器在 数据线上发送数据;而在写过程中,CPU控制数据线。

嵌入式系统硬件平台ppt

嵌入式片上系统(System On Chip)(1)

▪SoC 就是System on Chip ,SoC 嵌入式系统微处理器就是一

种电路系统。

▪它结合了许多功能区块,将功能做在一个芯片上,像是ARM

RISC 、MIPS RISC 、DSP 或是其他的微处理器核心,加上通信 的接口单元,像是万用串行端口(USB )、TCP/IP 通信单元、 GPRS通信接口、GSM 通信接口、IEEE1394 、蓝牙模块接口等 等,这些单元以往都是依照各单元的功能做成一个个独立的处理 芯片。

嵌入式硬件开发工具(2)

2.工具:三星在推广Arm7 ,Arm9 芯片的同 时还提供开发板和板级支持包(BSP ),而 WindowCE 在主推系统时也提供Embedded VC ++作为开发工具,还有Vxworks 的 Tonado 开发环境,DeltaOS 的Limda 编译环 境等等。

嵌入式硬件开发工具(3)

服务特 权

共享文档下载特权

VIP用户有效期内可使用共享文档下载特权下载任意下载券标价的文档(不含付费文档和VIP专享文档),每下载一篇共享文

档消耗一个共享文档下载特权。

年VIP

月VIP

连续包月VIP

享受100次共享文档下载特权,一次 发放,全年内有效

赠每的送次VI的发P类共放型的享决特文定权档。有下效载期特为权1自个V月IP,生发效放起数每量月由发您放购一买次,赠 V不 我I送 清 的P生每 零 设效月 。 置起1自 随5每动 时次月续 取共发费 消享放, 。文一前档次往下,我载持的特续账权有号,效-自

与计算机处理器不同的是,在实际嵌入式应用中,只保 留和嵌入式应用紧密相关的功能硬件,去除其他的冗余 功能部分,这样就以最低的功耗和资源实现嵌入式应用 的特殊要求。

IAC-RK3568-Kit嵌入式开发板硬件说明书

IAC-RK3568-Kit 嵌入式开发板硬件说明书版本号:V 2.02022年08月浙江启扬智能科技有限公司版权所有QIYANG TECHNOLOGY Co., LtdCopyright Reserved有任何技术问题或需要帮助,请联系:***********************第2页 共48页 购买产品,请联系销售:********************更多信息请访问:技术支持如果您对文档有疑问,可在办公时间(周一至周五 8:30-12:00,13:30-17:30),通过以下方式联系我们:技术邮箱:***********************技术支持电话:*************-805官网:(中文)/(英文)资料更新与获取1、资料的更新产品相关资料会不断完善更新;当您在使用这些内容时,请确保其为最新状态。

2、更新通知启扬智能产品资料更新通过微信公众号进行推送通知,敬请关注!3、资料如何获取产品购买后,请联系我公司相关销售人员获取。

有任何技术问题或需要帮助,请联系:*********************** 第3页 共48页 购买产品,请联系销售:********************更多信息请访问:版本更新记录目录阅读前须知:本手册主要介绍该开发板的硬件接口 (5)一、前言 (5)1.1、公司简介 (5)1.2、IAC-RK3568-KIT 开发/评估板的使用建议 (6)二、系统组成 (7)2.1、芯片概述 (7)2.2、开发板资源 (12)2.3、核心板资源 (15)三、底板接口功能 (16)3.1、基本接口功用说明 (18)3.2、接口引脚定义 (20)四、尺寸结构图 (40)4.1、核心板尺寸 (40)4.2、底板尺寸 (42)五、器件连接示图 (44)六、电气特性 (45)六、软件描述 (46)七、附注 (47)有任何技术问题或需要帮助,请联系:***********************第4页共48页购买产品,请联系销售:********************阅读前须知:本手册主要介绍该开发板的硬件接口一、前言1.1、公司简介浙江启扬智能科技有限公司2007年成立于杭州,是一家专注于ARM嵌入式产品研发、生产与销售的国家高新技术企业。

嵌入式硬件平台

应答 等待

等待

CPU

设备

3.3 总线

➢ 3.3.1 总线协议 ➢ 3.3.2 DMA ➢ 3.3.3 总线配置 ➢ 3.3.4 总线实例

3.3 总线

3.3.2 DMA

标准总线事务要求CPU在每个读写事务中间,解决 了CPU与其他设备的信息交换问题。

存在的问题 某些数据传输不需要CPU介入,如I/O设备和存储

第三章 嵌入式硬件平台

3.1 引言 3.2 嵌入式硬件平台概述 3.3 总线 3.4 存储设备 3.5 I/O设备 3.6 通信设备 3.7 其它

3.3 总线

➢ 3.3.1 总线协议 ➢ 3.3.2 DMA ➢ 3.3.3 总线配置 ➢ 3.3.4 总线实例

3.3 总线

3.3.1 总线协议

1. 握手协议 2. 总线读写

高速总线通常提供较宽的数据连接。 高速总线通常要更昂贵的电路和连接器,可以通过 使用较慢的、比较便宜的总线来降低低速设备成本。 桥允许总线独立操作,因此可以在I/O操作中提供 并行性。

3.3 总线

➢ 3.3.1 总线协议 ➢ 3.3.2 DMA ➢ 3.3.3 总线配置 ➢ 3.3.4 总线实例

Address Data ready’

Data

数据1

数据2

数据3

数据4

时间

1.2.2嵌入式系统的特点

2.总线读写

获 数总取 据 线事务的完成状态机是对时序发 数送 据图的有效释 应补放 答充。

当CPU决定地址执行起一始个位置读事务,它转换地到址新状起态始位,置 并转分 应发 换析 答 给 图让 捕设 获备 了正它确这工一作端的的总总线线应答信协号议; 状而 态设 。备状态

3.2 嵌入式硬件平台概述

第二章嵌入式系统硬件平台

NOR Flash 和NAND Flash的对比

2、接口对比 NOR Flash带有SRAM接口,有足够的地址引脚来寻

址,可以很容易地存取其内部的每一个字节。 NAND Flash地址、数据和命令共用8位总线/16位总

线,每次读写都要使用复杂的I/O接口串行地存取 数据,8位总线/16位总线用来传送控制、地址和 资料信息。

S2层为芯片外的高速缓存(SRAM、DRAM、 DDRAM)

S3层为主存储器(Flash、PROM、EPROM、 EEPROM)

S4层为外部存储器(磁盘、光盘、CF、SD 卡)

S5层为远程二级存储(分布式文件系统、 Web服务器)

2.3.2 嵌入式系统存储设备分类

1.按在系统中的地位分类

主存:在系统中,存储器可分为主存储器(Main Memory简称 内存,内存是计算机主机的一个组成部分,一般都用快速存储 器件来构成,内存的存取速度很快,但内存空间的大小受到地 址总线位数的限制。内存通常用来容纳当前正在使用的或要经 常使用的程序和数据,CPU可以直接对内存进行访问。

ARM生产模式-Chipless:ARM公司的成功经验 80年代末90年代初半导体行业产业链刚刚出现

分工,台积电,联电等半导体代工厂正悄悄崛起, 美国硅谷中的一些Fabless公司也如雨后春笋一样涌 现出来,所谓的Fabless公司自己设计芯片,但是生 产过程则包给台积电等代工厂生产。而ARM更是为 天下先,12年前首创了Chipless的生产模式,即该公 司既不生产芯片,也不设计芯片,而是设计出高效 的IP内核,授权给半导体公司使用,半导体公司在 ARM技术的基础上添加自己的设计并推出芯片产品, 最后由OEM客户采用这些芯片来构建基于ARM技 术的系统产品。

嵌入式linux开发平台

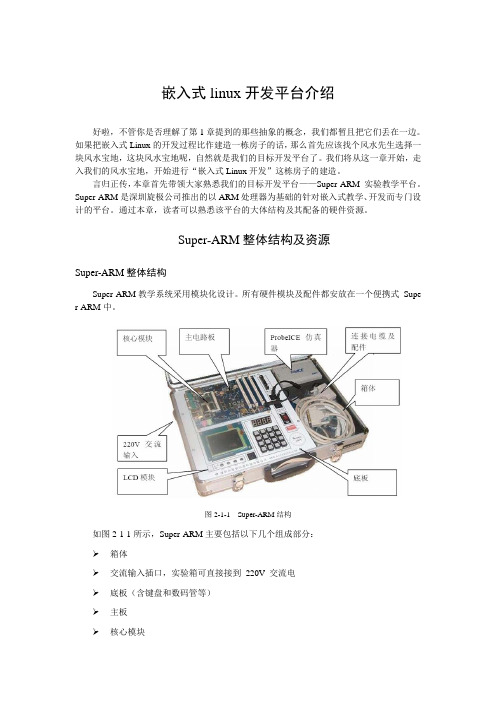

嵌入式linux开发平台介绍好啦,不管你是否理解了第1章提到的那些抽象的概念,我们都暂且把它们丢在一边。

如果把嵌入式Linux的开发过程比作建造一栋房子的话,那么首先应该找个风水先生选择一块风水宝地,这块风水宝地呢,自然就是我们的目标开发平台了。

我们将从这一章开始,走入我们的风水宝地,开始进行“嵌入式Linux开发”这栋房子的建造。

言归正传,本章首先带领大家熟悉我们的目标开发平台——Super-ARM 实验教学平台。

Super-ARM是深圳旋极公司推出的以ARM处理器为基础的针对嵌入式教学、开发而专门设计的平台。

通过本章,读者可以熟悉该平台的大体结构及其配备的硬件资源。

Super-ARM整体结构及资源Super-ARM整体结构Super-ARM教学系统采用模块化设计。

所有硬件模块及配件都安放在一个便携式Supe r-ARM中。

图2-1-1 Super-ARM结构如图2-1-1所示,Super-ARM主要包括以下几个组成部分:箱体交流输入插口,实验箱可直接接到220V 交流电底板(含键盘和数码管等)主板核心模块LCD 模块扩展板(可选)ProbeICE 仿真器各种连接电缆及配件Super-ARM教学系统主要资源(1)ARM 处理器系统采用三星公司的处理器S3C2410X(ARM9)。

该处理器是基于ARM920T 内核,主频高达203MHz,带MMU(内存管理单元),片上资源丰富,性价比极高,是目前ARM9处理器中,使用较多的一种。

其结构图如图2-1-2所示:图2-1-2 S3C2410处理器结构图S3C2410集成的片上功能如下:内核工作电压为1.8/2.0V、存储器供电电压3.3V、外部I/O设备的供电电压3.3V;16KB的指令Cache和16KB的数据Cache;LCD控制器,最大可支持4K色STN和256色TFT;4通道的DMA请求;3通道的UART(IrDA1.0、16字节TxFIFO、16字节RxFIFO),2通道的SPI接口;2通道的USB(Host/Slave);4路PWM和1个内部时钟控制器;117个通用I/O,24路外部中断;272Pin FBGA封装;16位的看门狗定时器;1通道的IIC/IIS控制器;带有PLL片上时钟发生器;S3C2410 ARM处理器支持大/小端模式存储字数据,其寻址空间可达1GB,每个Bank 为128MB,对于外部I/O设备的数据宽度,可以是8/16/32位,所有的存储器Bank(共有8个)都具有可编程的操作周期,而且支持NOR/NAND Flash、EEPROM等多种ROM引导方式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

• 外部设备也有寄存器,是一种存储单 元,其物理结构跟内存单元不一样,但作 用跟内存单元一样,都能保存信息。

在设计时,给外部设备的每个寄存器 都分配一个地址,CPU可以根据地址访问 某个寄存器,则该寄存器发生相应的动作: 或接收数据总线上的数据(对应于写操 作),或把自己的数据送到数据总线上 (对应于读操作)。当CPU访问某个寄存 器时,同一个外设的其他寄存器和其他外 设的寄存器由于没有CPU的指令不会发生 动作。

• NAND Flash不能直接在Flash内运行应用 程序,需要将数据复制到RAM中运行。

• NAND Flash的特点是容量大。

3、JTAG接口

• JTAG(Joint Test Action Group,联合测 试行动小组)是一种国际标准测试协议 (IEEE 1149.1兼容),主要用于芯片内部 测试。

(2)异步时序协议的握手协议

• 握手协议是总线异步时序的基本构件。 • 握手协议数据传送过程的4个周期:

4、I/O端口

• I/O端口又称为I/O接口,它是微处理器对外 控制和信息交换的必经之路,是CPU与外 部设备连接的桥梁,它在CPU与外部设备 之间起信息转换和匹配的作用。I/O端口有 串行和并行之分,串行I/O端口一次只能传 送一位二进制数信息,而并行I/O端口一次 能传送一组二进制数信息。

• 若希望两边亮,中间暗,则:

PD7 PD6 PD5 PD4 PD3 PD2 PD1

PD0

0 11

1 11 1

0

• 十六进制编码为:7EH。

2.2 嵌入式系统硬件平台

图2.5 嵌入式系统硬件结构

1、嵌入式处理器

• 嵌入式处理器通常包括几个部分:处理器 内核、地址总线、数据总线、控制总线、 片上I/O接口电路及辅助电路(如时钟、复 位电路等)。

• (1)总线时序协议 • (2)异步时序协议的握手协议 • (3)总线仲裁方式 • (4)总线标准

(1)总线时序协议

• 同步时序: • 总线上所有事件共用同一时钟脉

冲进行操作过程的控制,所有事件都 在时钟周期的开始发生。 • 异步时序: • 操作由源或目的模块发出的特定 信号确定。双方相互提供联络信号。

• 嵌入式处理器可以分为3类: 嵌入式微处理器、 嵌入式微控制器、 嵌入式DSP(Digital Signal Processor,

数字信号处理器),

2、嵌入式系统中的存储设备

(1)RAM、SRAM、DRAM

• RAM即是我们通常所说的内存。RAM又可 分为SRAM(静态存储器)和DRAM(动 态存储器)。

• 图2.3 I/O接口电路的位置

• CPU对外设I/O端口物理地址的编址方式有 两种:

• 一种是I/O映射方式(I/O-mapped);

• 另一种是内存映射方式(Memory- mapped)。

• 具体采用哪一种则取决于CPU的体系结构。

5、中断

• 中断方式是指,当外部设备准备与CPU进 行数据传输时,外部设备首先向CPU发出 中断请求,CPU接收到中断请求并在一定 条件下,暂时停止原来的程序并执行中断 服务处理程序,执行完毕以后再返回原来 的程序继续执行。

图2.4 中断处理的各个阶段

6、数据编码

• 设用微处理器控制一串彩灯(发光二极管) 的亮灭。如图2.4所示。

• 我们设不发光的口线(高电平)为1,发 光的口线(低电平)为0。

• 当彩灯L1发光时,PD0口线为低电平, 而其余口线均为高电平。

则可以表示为以下对应值:

PD7 PD6 PD5 PD4 PD3 PD2 PD1 PD0

(2)Flash

• Flash是一种非易失闪存,它具有和ROM 一样掉电后数据不会丢失的特性。Flash是 目前嵌入式系统中广泛采用的主流存储器, 它的主要特点是按整体/扇区擦除和按字节 编程,具有低功耗、高密度、小体积等优 点。

Flash分为 NOR Flash、NAND Flash两种。

• NOR Flash的特点是在芯片内执行,可以 直接读取芯片内储存的数据,因而速度比 较快。应用程序直接在Flash内运行,不必 把代码读到系统RAM中运行。

2、寄存器

• 所谓寄存器(register),是CPU内部 用来存放数据的一些小型存储区域, 用于暂时存放参与运算的数据ห้องสมุดไป่ตู้运算 结果。

• 寄存器是一种时序逻辑电路,但这种时 序逻辑电路只包含存储电路。寄存器的存 储电路是由锁存器或触发器构成的,因为 一个锁存器或触发器能存储1位二进制数, 所以由N个锁存器或触发器可以构成N位寄 存器。寄存器是CPU内部的元件,寄存器 拥有非常高的读写速度,所以在寄存器之 间的数据传送非常快。

本章要点

学习完本章读者将掌握如下内容: • 1、嵌入式硬件的相关基础知识 • 2、嵌入式硬件平台基本组成 • 3、ARM系列微处理器简介 • 4、S3C2410及PXA270微处理器的结构

2.1 相关基础知识

1、微处理器

• 中央微处理器,简称CPU,它是计算机中 最重要的一个部分,它决定嵌入式系统的 主要功能特性。CPU又由运算器和控制器 两大部分组成。

• 我们经常用简易 JTAG接口直接烧写 嵌入式系统Flash存 储器。这种烧写方式

是通过一根并口电缆

和一块信号转换集成 电路板以建立PC机与 开发板之间的通信。

3、总线

• 总线(BUS)是接口电路与CPU或者接口 电路与I/O外部设备之间连接的主要形式, 是各功能部件之间传送信息的公共通路。

• 采用一组公共的信号线作为嵌入式系统各 部件之间的通信线,这组公共信号线就称 为总线。

通信协议

• 通信协议是指通信双方的一种约定。约定 包括对数据格式、同步方式、传送速度、 传送步骤等问题做出统一规定,通信双方 必须共同遵守。

1 11

1 11 1

0

用二进制数表示为:11111110。 用十六进制编码 ,其值为:FEH 。

• 再如,要彩灯L8发光,其余均不发光,则 有:

则可以表示为以下对应值:

PD7 PD6 PD5 PD4 PD3 PD2 PD1

PD0

0 11

1 11 1 1

• 用二进制数表示为:01111111。 • 十六进制编码为:7FH。