NTP网络授时系统设计与实现——NTP网络授时系统服务器硬件设计

NTP协议介绍及实现方案(服务器端和客户端)

NTP协议介绍及实现方案1 NTP协议简介 (2)2 NTP协议实现原理 (2)2.1 NTP协议的分层结构 (2)2.2 NTP协议的对时方式 (3)2.3 NTP协议的工作模式 (4)3 NTP报文格式 (4)4 NTP实现方案 (7)4.1 服务器端实现方案 (9)4.2 客户端实现方案 (11)5 遗留问题 (12)6 参考文献 (12)1 NTP协议简介NTP(Network Time Protocol,网络时间协议)是由RFC1305定义的时间同步协议,用来在分布时间服务器和客户端之间进行时钟同步,同时也是一个因特网标准,它采用应用层同步方法将计算机时钟和UTC时间(格林尼治时间)进行同步,因此时间精度不高,一般在10ms到100ms之间。

NTP协议属于应用层协议,定义了协议实现过程中所使用的结构、算法、实体和协议,它是基于IP和UDP的,也可以被其它协议组使用。

NTP协议时OSI参考模型的最高层协议,符合UDP传输协议格式,拥有专用端口123。

NTP协议是OSI参考模型的高层协议,符合UDP传输协议格式,拥有专用端口123,在嵌入式linux系统中,采用Server/Cilent的模式来实现网络通信,客户端主动提出申请,而服务器端被动打开。

又由于使用UDP套接字建立连接的好处在于,只有被该套接字指定为远程地址的计算机端口才能向该套接字发送数据,如果没有建立连接,任何IP地址和端口都能将数据发送到这个UDP套接字上。

所以采用建立连接的UDP套接字来传输时间信息。

2 NTP协议实现原理2.1 NTP协议的分层结构NTP采用分层的方法来定义时钟的准确性,可分为从0~15共16个级别,级别编码越低,精确度和重要性越高。

第0级设备是时间同步网络的基准时间参考源,位于同步子网络的顶端,目前普遍采用全球卫星定位系统,即由GPS播出的UTC时间代码。

级别(n+1)从级别n获取时间。

图1 NTP协议分层结构图子网络中的设备可以扮演多重角色,可以做客户机、服务器,也可以做对等机。

ntp校时服务器解决方案

ntp校时服务器解决方案ntp校时服务器解决方案1. 引言在现代科技社会中,时间同步对于许多应用和系统来说至关重要。

通过确保各种设备和计算机之间的时间一致性,我们能够避免许多问题,例如数据不一致、安全漏洞以及网络流量管理等。

而NTP(Network Time Protocol)就是一种常用的时间同步协议,用于确保各种设备之间的时间同步。

2. NTP简介NTP是一种用于时间同步的协议,其主要目标是通过在计算机网络中提供精确、一致的时间。

它基于客户-服务器模型,其中时间服务器被称为NTP服务器,而需要同步时间的设备则被称为NTP客户端。

NTP服务器通过参考一些准确的时间源(例如原子钟或GPS)来提供时间信息。

3. NTP校时服务器的重要性NTP校时服务器在许多领域和应用中扮演着至关重要的角色。

无论是企业网络、云计算环境还是地理分布广泛的系统,NTP校时服务器都是确保时间同步的关键组件。

它们不仅用于同步计算机系统的时间,还用于网络设备、服务器、工业控制系统等各种设备的时间同步。

4. NTP校时服务器解决方案(1)硬件解决方案:硬件NTP校时服务器通常是专门的硬件设备,其内置NTP软件和时间源。

这种解决方案具有高度可靠性和稳定性,并且能够提供高准确度的时间同步。

硬件NTP校时服务器通常具有多个网络接口,可以同时为多个客户端提供时间同步服务。

(2)软件解决方案:软件NTP校时服务器是在一台普通计算机上安装NTP软件,并将其配置为NTP服务器。

这种解决方案相对便宜且灵活,适用于小规模网络或测试环境。

然而,软件解决方案可能会受到计算机性能、网络延迟等因素的影响,对于对时间同步要求更高的环境可能不够理想。

5. NTP校时服务器的配置和管理配置和管理NTP校时服务器是确保时间同步正常运行的关键。

以下是一些常见的配置和管理注意事项:(1)选择时间源:NTP校时服务器的时间源应该是准确可靠的,例如原子钟、GPS或其他参考时间源。

基于龙芯1C的NTP时间服务器设计与实现

[9-11]

。

NTP 校时是通过 NTP 报文在客户端与服务端之

- 26 -

接收处理模块实现授时时统 UTC 的时间溯源,并进

控制器。主控制器模块以龙芯 1C300B 处理器为核

心,存储单元包含 SDRAM、NAND Flash、SD 卡等;网

籍明慧,

等

基于龙芯 1C 的 NTP 时间服务器设计与实现

摘要:信息处理网络化和工业控制自动化的快速发展,对同一网络系统下设备的时间同步提出了

更高的要求。提出了基于北斗卫星导航系统(BDS)与 NTP 的软硬件混合时间同步设计方案,介绍

了其相关原理,并且进行了软硬件的实现。主控板处理器采用国产处理器龙芯 1C300B,搭配嵌入

式 Linux 系统部署 NTP 服务,核心芯片采用国产芯片,整个软硬件设计契合自主国产化思想。经测

精 度 已 经 达 到 了 毫 秒 级 ,且 在 实 际 部 署 上 较 为 简

单。李培基等 [4] 对 NTP、PTP(Precise Time Protocol)及

作者简介:籍明慧(1997—),男,山西忻州人,硕士研究生。研究方向:主板设计。

- 25 -

《电子设计工程》2021 年第 7 期

的计算能力 [15]。

系统总体由北斗时间接收处理模块、处理器模

模 式 ,客 户 端 借 助 NTP 协 议 从 服 务 器 获 取 准 确 的

块、电源模块以及显示模块等部分组成。北斗时间

端双向信息传输持续跟踪时间变化并自动进行

行处理之后通过串口将精确的时钟信息传送给主

时 间 ,在 校 时 的 同 时 ,NTP 能 够 通 过 主 机 与 客 户

作性和灵活性。

其中,T/RXCLK、T/RXD[0:3]引脚分别实现发送/

网络时间校准服务器

网络时间校准服务器摘要:网络时间校准服务器是一种用于同步网络设备的时间的服务器。

本文将介绍网络时间校准服务器的基本原理、作用、常见的实现方式,以及它在各个行业的重要性和应用场景。

1. 简介网络时间校准服务器(Network Time Protocol Server,简称NTP Server)是一种用于同步网络设备的时间的服务器。

它主要通过发送时间信号并接收应答来保持网络设备的时间同步。

网络时间校准服务器通过确定网络上的主时钟并在各个设备之间进行时间同步,确保所有连接到网络的设备具有相同的时间。

2. 基本原理网络时间校准服务器通过使用网络时间协议(Network Time Protocol,简称NTP)来同步网络设备的时间。

NTP是一种用于分布式计算机系统中的时间同步协议,它通过将一个计算机作为服务器提供时间,其他计算机可以通过网络连接到该服务器并校准自己的时间。

NTP服务器通常与GPS接收器或原子钟等高精度时间源连接,以提供准确可靠的时间校准。

3. 作用网络时间校准服务器在网络中的作用非常重要。

它不仅可以确保网络设备的时间同步,还可以提供时间戳用于日志记录、数据同步、安全验证等操作。

时间同步对于许多网络应用来说至关重要,比如金融交易、科学实验、航空航天等领域都需要高度精确的时间同步。

4. 实现方式网络时间校准服务器可以使用不同的实现方式。

常见的实现方式包括:4.1. 基于软件的NTP服务器:这种实现方式使用计算机上的软件作为NTP服务器,通过网络连接到外部时间源获取时间信号。

4.2. 基于硬件的NTP服务器:这种实现方式使用专门的硬件设备作为NTP服务器,通常与GPS接收器或原子钟等高精度时间源连接。

4.3. 基于云的NTP服务器:这种实现方式使用云服务提供商的服务器作为NTP服务器,通过互联网连接到时间源获取时间信号。

5. 重要性和应用场景网络时间校准服务器在各个行业都具有重要性和广泛的应用场景。

网络授时服务器

网络授时服务器什么是网络授时服务器网络授时服务器是一种基于网络时间协议(NTP)的服务器,可以提供高精度的时间同步服务,用来让计算机之间的系统时间保持一致。

当多台计算机之间存在时间误差时,就可以使用网络授时服务器来对它们进行同步。

网络授时服务器的工作原理网络授时服务器的工作原理主要分为两部分:首先,授时服务器需要从参考时钟源获取准确的时间授时服务器需要借助参考时间源来获取准确的时间,这个时间源可以是计算机的时钟、GPS卫星信号等。

如果一个授时服务器想要提供较高精度的时间同步服务,那么它需要从多个参考时钟源获取准确时间,计算得出平均值。

同时,授时服务器还需要定期对参考时钟源进行校准,以确保它们的时间准确无误。

接着,授时服务器需要将准确的时间信息传输给客户端授时服务器通过NTP协议将准确的时间信息传输给客户端。

客户端请求授时服务器提供时间信息,并在收到时间信息后,进行本地时间的校准。

NTP协议使用了一些优秀的算法,可以在网络延迟较大的情况下,保证高精度时间同步。

网络授时服务器的作用和应用场景网络授时服务器的主要作用是保证多台计算机的时间同步,避免不同计算机时间的误差导致网络应用的故障。

它在很多网络应用场景中都起到了关键的作用,这些场景包括:金融交易在金融交易中,时间精度是极为重要的,时间误差可能导致交易数据无法同步或交易结果无法被验算。

因此,金融交易通常会使用高精度的网络授时服务器来确保所有系统参与者的系统时间是同步的。

通信系统在通信系统中,计算机之间需要准确的交换数据,但如果它们的时间不同步,数据交换就可能出现错误。

为了保证通信系统的正常运行,网络授时服务器被广泛应用于通信系统中。

安全系统安全系统需要精确的时间戳来记录和验证操作时间。

如果时间戳不准确,不仅会给系统的安全性带来威胁,还会阻碍应用程序的正常运行。

在安全系统中,网络授时服务器可以提供高精度时间戳,确保操作时间的准确性。

总结网络授时服务器是一种重要的网络基础设施,可以帮助多个计算机系统保持高精度的时间同步。

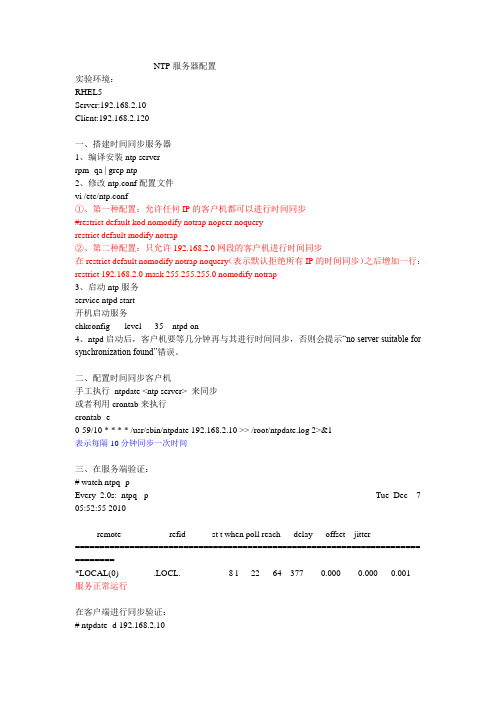

NTP时间服务器配置

NTP服务器配置实验环境:RHEL5Server:192.168.2.10Client:192.168.2.120一、搭建时间同步服务器1、编译安装ntp serverrpm -qa | grep ntp2、修改ntp.conf配置文件vi /etc/ntp.conf①、第一种配置:允许任何IP的客户机都可以进行时间同步#restrict default kod nomodify notrap nopeer noqueryrestrict default modify notrap②、第二种配置:只允许192.168.2.0网段的客户机进行时间同步在restrict default nomodify notrap noquery(表示默认拒绝所有IP的时间同步)之后增加一行:restrict 192.168.2.0 mask 255.255.255.0 nomodify notrap3、启动ntp服务service ntpd start开机启动服务chkconfig --level 35 ntpd on4、ntpd启动后,客户机要等几分钟再与其进行时间同步,否则会提示“no server suitable for synchronization found”错误。

二、配置时间同步客户机手工执行ntpdate <ntp server> 来同步或者利用crontab来执行crontab -e0-59/10 * * * * /usr/sbin/ntpdate 192.168.2.10 >> /root/ntpdate.log 2>&1表示每隔10分钟同步一次时间三、在服务端验证:# watch ntpq -pEvery 2.0s: ntpq -p Tue Dec 7 05:52:55 2010remote refid st t when poll reach delay offset jitter====================================================================== ========*LOCAL(0) .LOCL. 8 l 22 64 377 0.000 0.000 0.001服务正常运行在客户端进行同步验证:# ntpdate -d 192.168.2.107 Dec 05:54:42 ntpdate[3627]: ntpdate 4.2.2p1@1.1570-o Thu Nov 26 11:35:07 UTC 2009 (1) Looking for host 192.168.2.10 and service ntphost found : 192.168.2.10transmit(192.168.2.10)receive(192.168.2.10)transmit(192.168.2.10)receive(192.168.2.10)transmit(192.168.2.10)receive(192.168.2.10)transmit(192.168.2.10)receive(192.168.2.10)transmit(192.168.2.10)server 192.168.2.10, port 123stratum 9, precision -20, leap 00, trust 000refid [192.168.2.10], delay 0.02632, dispersion 0.00061transmitted 4, in filter 4reference time: d0a890f1.b4d040ff Tue, Dec 7 2010 5:54:41.706originate timestamp: d0a89102.09318178 Tue, Dec 7 2010 5:54:58.035transmit timestamp: d0a890f2.3c8effe2 Tue, Dec 7 2010 5:54:42.236filter delay: 0.02910 0.02632 0.02808 0.026410.00000 0.00000 0.00000 0.00000filter offset: 15.80026 15.79880 15.79793 15.798370.000000 0.000000 0.000000 0.000000delay 0.02632, dispersion 0.00061offset 15.7988017 Dec 05:54:42 ntpdate[3627]: step time server 192.168.2.10 offset 15.798801 sec附:当用ntpdate -d 来查询时会发现导致no server suitable for synchronization found 的错误的信息有以下2个:错误1.Server dropped: Strata too high在ntp客户端运行ntpdate serverIP,出现no server suitable for synchronization found的错误。

NTP网络时间服务器概述

NTP网络时间服务器概述NTP(Network Time Protocol)是一种用于同步计算机网络中设备时钟的协议。

它允许网络中的设备通过连接到一个或多个NTP服务器来获取准确的时间。

NTP基于一种分层体系结构,其中主服务器从时间源获得时间,并将其传播到网络中的其他设备。

在这篇文章中,我们将概述NTP网络时间服务器及其工作原理。

NTP网络时间服务器的概述NTP网络时间服务器是运行NTP协议的服务器,用于提供准确的时间服务给其他设备。

这些服务器通常由专门的机构或组织维护,例如国家实验室、大型公司或网络服务提供商。

NTP 服务器通常连接到一个或多个时间源,如原子钟、GPS系统或其他准确的时间提供者。

它们通过使用NTP协议与其他设备进行通信,以同步其时钟。

NTP网络时间服务器的工作原理NTP网络时间服务器的工作原理可以简单地分为两个主要步骤:时间同步和时间传播。

时间同步是指获取准确时间并将其应用于服务器本地的时钟。

NTP服务器通常与原子钟或其他准确时间源进行联系,以获取高精度的时间信息。

服务器将此时间信息与本地时钟进行比较,并校准本地时钟,以保证其与时间源保持同步。

NTP协议还针对网络延迟和时钟变化进行调整,以确保准确的时间同步。

时间传播是指在网络中传播已经同步的时间信息。

一旦NTP服务器与时间源同步,它将以最高精度提供准确时间。

其他设备可以通过连接到NTP服务器并使用NTP协议来获取这个准确时间。

NTP服务器使用一种层级结构,其中较高级别的服务器从更准确的时间源获取时间,并将其传播到较低级别的服务器。

这种传播过程将准确时间逐渐传送到整个网络中的设备上。

NTP协议的特点NTP协议具有以下几个特点:1. 网络层级结构:NTP协议使用一种分层结构,其中高级别的服务器从准确的时间源获取时间,并将其传播到较低级别的服务器。

这种层级结构允许时间信息在网络中传播并保持同步。

2. 精确的时间同步:NTP协议通过校准本地时钟与准确时间源同步以实现精确的时间同步。

一种NTP系统设计与实现

NTP服务器配置范例及学习总结

NTP服务器配置范例及学习总结NTP(网络时间协议)是常用的网络时间同步协议,通过NTP服务器可以将计算机的系统时间同步到全球的标准时间,以确保计算机之间的时间一致性。

下面将介绍一个NTP服务器的配置范例,并总结学习经验。

一、NTP服务器的配置范例假设我们有一个Linux服务器,需要将其配置为一个NTP服务器,供其他计算机同步时间。

以下是一个简单的NTP服务器配置范例:1.安装NTP软件首先需要安装NTP软件包。

以Ubuntu为例,可以通过以下命令安装NTP:```sudo apt-get install ntp```2.配置NTP服务器```sudo vi /etc/ntp.conf```在文件中添加以下内容:```#使用本地时钟作为参考时间源server 127.127.1.0fudge 127.127.1.0 stratum 10#使用NTP服务器同步时间server iburstserver iburst#允许其他计算机同步时间restrict default nomodify notrap```3.启动NTP服务器```sudo service ntp start```4.验证NTP服务器通过以下命令验证NTP服务器是否正常工作:```ntpq -p```如果看到输出中包含一些服务器的IP地址和相关信息,则表示NTP 服务器已成功配置和启动。

二、学习总结学习和配置NTP服务器涉及以下几个方面的知识:1.NTP协议:了解NTP协议的基本原理和工作方式,以及NTP服务器的作用和功能。

2.NTP服务器的选择:选择合适的NTP服务器来同步时间,可以从互联网上的公共NTP服务器中选择,也可以使用其他可靠的时间源。

3.NTP服务器的配置:了解NTP服务器的配置文件,明确要配置的参数和选项,并进行相应的配置。

4.NTP服务器的验证:验证配置是否正确,包括启动NTP服务器、查看NTP服务器的状态和信息,确保NTP服务器正常工作。

NTP时间服务器

NTP时间服务器NTP:Network Time Protocol,⽹络时间协议。

它是⽤来使⽹络中的各个计算机时间同步的⼀种协议。

它的⽤途是把计算机的时钟同步到UTC(世界协调时钟),其精度在局域⽹内可达0.1ms,在互联⽹上绝⼤多数的地⽅其精度可以达到1-50ms。

NTP时间服务器就是利⽤NTP协议提供时间同步服务的。

注意: 在CentOS8.0中默认不再⽀持ntp软件包,时间同步将由chrony来实现。

NTP时间服务器搭建1. 安装NTP软件包(1)查看本机系统版本# cat /etc/cent0s-release(2)安装ntp软件包# yum install ntp -y(3) 查看ntp安装后⽣成哪些⽂件# rpm -ql ntp主配置⽂件: /etc/ntp.conf2. 配置NTP Server(1)⾸先我们要在互联⽹上找到给我们提供同步服务的NTP Server⽐如我找了这两个节点58.220.133.132114.67.103.73(2)在打开NTP服务器之前先和这些服务器做⼀个同步,使得我们机器的时间尽量接近标准时间. 这⾥我们可以⽤ntpdate命令⼿动更新时间假如你的时间差的很离谱的话第⼀次会看到调整的幅度⽐较⼤,所以保险起见可以运⾏两次. 那么为什么在打开NTP服务之前先要⼿动运⾏同步呢? 1. 因为根据NTP的设置,如果你的系统时间⽐正确时间要快的话,那么NTP是不会帮你调整的,所以要么你把时间设置回去,要么先做⼀个⼿动同步 2. 当你的时间设置和NTP服务器的时间相差很⼤的时候,NTP会花上较长⼀段时间进⾏调整.所以⼿动同步可以减少这段时间那我们先⼿动同步时间:# ntpdate 58.220.133.132# ntpdate 114.67.103.73(3)配置和运⾏NTP Server 现在我们就来创建NTP的配置⽂件了, 它就是 /etc/ntp.conf.。

ntp校时服务器方案

NTP校时服务器方案目标本方案旨在设计和实施一个高效可靠的NTP(Network Time Protocol)校时服务器,确保网络中的设备具有准确的时间同步,提供可靠的时间参考,并满足以下目标:1.提供高精度的时间同步服务,确保网络设备的时间准确性;2.支持大规模的设备接入,能够同时为多个客户端提供时间服务;3.具备高可用性和容错能力,能够处理故障和负载均衡;4.提供安全的时间同步服务,防止时间劫持和篡改;5.提供详尽的日志和监控功能,便于故障排查和性能优化。

实施步骤步骤一:硬件和网络设施准备1.选择合适的硬件设备作为NTP服务器,建议选择高性能的服务器设备,具备较大的存储容量和高速的网络接口;2.部署服务器设备在稳定可靠的机房环境中,确保供电和网络连接的稳定性;3.配置服务器设备的操作系统和网络环境,确保服务器能够正常运行,并与其他网络设备通信。

步骤二:NTP软件配置和安装1.选择合适的NTP软件,如NTPd、Chrony等,并根据操作系统选择相应的版本;2.安装NTP软件并进行基本配置,包括选择合适的时间源、配置服务器参数和权限控制;3.配置NTP软件的日志和监控功能,确保能够记录和监控服务器的状态和性能。

步骤三:时间源选择和配置1.选择合适的时间源,如公共NTP服务器、GPS时间源、本地时钟等;2.配置时间源的连接参数和优先级,确保服务器能够获取到准确的时间信息;3.配置时间源的冗余和负载均衡策略,确保在某个时间源故障时能够切换到其他可用的时间源。

步骤四:安全性配置和防御措施1.配置NTP服务器的安全性参数,如限制客户端访问、加密通信、防止时间劫持等;2.配置防火墙和访问控制列表,限制对NTP服务器的非授权访问;3.定期更新NTP软件和操作系统的补丁,确保安全漏洞得到及时修复。

步骤五:性能优化和监控1.配置NTP服务器的性能参数,如调整时间同步间隔、优化资源消耗等;2.配置监控工具,如Zabbix、Nagios等,对NTP服务器进行实时监控,包括服务器状态、时间同步情况、资源利用率等;3.配置日志分析工具,对NTP服务器的日志进行分析和统计,及时发现和解决潜在问题。

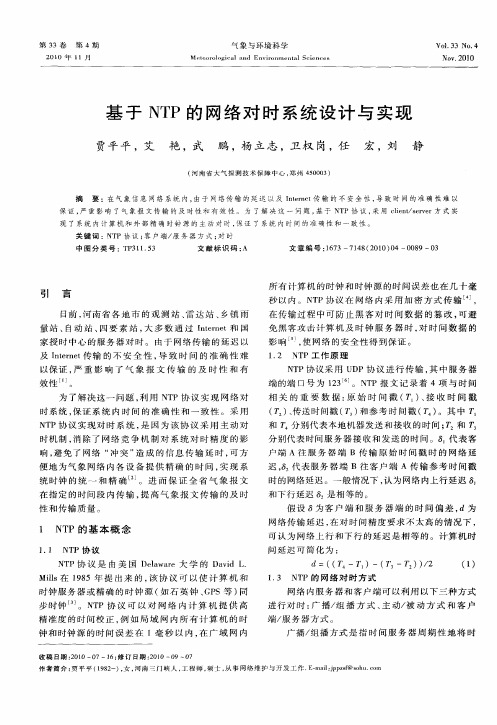

基于NTP的网络对时系统设计与实现

1 2 N P工 作 原 理 . T

及 It nt 输 的不 安 全 性 , 致 时 间 的 准 确 性 难 ne e 传 r 导 以保 证 , 重 影 响 了 气 象 报 文 传 输 的及 时 性 和 有 严

效 性 。 为 了 解 决 这 一 问 题 , 用 N P协 议 实 现 网 络 对 利 T 时 系 统 , 证 系 统 内 时 间 的 准 确 性 和 一 致 性 。 采 用 保 N P协 议 实 现 对 时 系 统 , 因 为 该 协 议 采 用 主 动 对 T 是 时 机 制 , 除 了 网 络 竞 争 机 制 对 系 统 对 时 精 度 的 影 消

N P协议 采用 U P协议 进 行 传 输 , 中服 务器 T D 其

端 的 端 口号 为 136。 N P报 文 记 录 着 4项 与 时 间 2[ T 3

相 关 的 重 要 数 据 : 始 时 间 戳 ( ) 接 收 时 间 戳 原 . 、 ( ) 传送 时间戳 ( ) 参 考 时 间戳 ( 4 。其 中 、 和 T) 和 分别代表 本地机器 发送 和接 收的 时间 ; 2 T 和

所有 计算 机 的时钟 和 时钟 源 的时 间误差也 在 几十 毫 秒 以内 。N P协议 在 网络 内采 用 加 密方 式 传 输 , T

在传 输过 程 中可 防 止黑 容 对 时 间数 据 的篡 改 , 可避 免黑 客攻 击计 算 机及 时钟 服 务 器 时 , 时 间 数 据 的 对

收 稿 日期 :0 0—0 21 7—1 ; 订 日期 : 0 0— 9~ 7 6修 21 0 0

() 1

网 络 内服 务 器 和 客 户 端 可 以 利 用 以 下 三 种 方 式

基于NTP协议的网络时间服务系统的实现

用。它是 目 前最准确的基本物理量 , 具有 良好 的传

递性 , 且 与人 民大众 的 日常生 活 密切 相 关 。随着 并

电子信息技术 和 Itre 的迅猛发展 , nent 电子商务、

I pl m e a i n o t r i e s r e y t m s d o m e nt to f ne wo k tm e v r s s e ba e n NTP

Z a j ,Z a gAi n NigD y h oKe a h n mi , n a u i

电子 政 务等 高 时 间约 来自 业 务 对 整个 社 会 的 时 间

E EC丁 L Q 【 c弧五 嚣n

维普资讯

2o o8

De i & Re e r h sgn s ac

设计 , 由时问协议 (mepooo)IMP时间戳 消息 t rtc1、C i

( MP t tmp mesg ) I I C i s me a sae 及 P时 问 戳 选 项 (P I

b s d o h e u t f a a s a itc a e n t e r s lso t t ts i.Th e h d wh c Su e o d a t h r b e ea — d em t o ih i s d t e l wi t ep o l msr l t h

me h d o u l i g n t r i e v r a d t e p o e s o e i n n i a i r t n s fwa e t o fb i n e wo k tme s r e n h r c s fd sg i g tme c l a i o t r d b o

局域网搭建NTP时间服务器及配置

一、局域网内由于时间不同步造成的问题作为网络管理员,既要保证网络设备的稳定运行,又要及时处理网络中随时出现的故障,而如果无法实现时间同步,就会增加处理故障的难度,比如:(一)有时候需要重启CISCO交换机,但每次重启后以后,交换机的时间又变回默认的1994年了。

(二)局域内有几十台交换机,虽然大多可以实现远程网管,但由于时间不一致,造成无法准备网络故障发生的确切时间。

(三)单位使用刷卡考勤,不准确的局域网时间往往造成考勤时间差异。

(四)公司各业务系统需要定时后台传输数据,也因为时间不一致导致传输不准时,甚至传输失败。

二、局域网内架设时间服务器1.局域网内需要同步的设备:Windows2003服务器AIX服务器Linux服务器WindowsXP桌面电脑CISCO路由器、交换机2.时间服务器方案选择如果要做成能够使CISCO路由器、交换机跟随进行时间同步的时间服务器,只有两个方案,一个是选择第三方专业的NTP软件,另一个就是利用LINUX系统作一台NTP服务器,考虑到时间服务器还必须访问外网来实现自身的时间同步,而我们有一台现成的windows2003代理服务器。

我们选择了方案一,在windows2003平台上使用专业的NTP服务器。

专业的NTP软件就叫NTP,它的WINDOWS版本(下载地址为http://www.meinberg.de/download/ntp/windows/ntp-4.2.4p7@copenhagen-o-win32-setup.exe)3.时间服务器安装1) 安装时一切配置都按默认的即可,但是在选择安装程序时,有一个安装第三方软件的那个(即openssl的不必选),一路点下一步进行即可,当然这样做完以后,十次有九次会提示NTP服务没有启动成功。

2) 查看和修改配置文件打开配置文件,即“Edit NTP Configuration”这一项,里面有一点需要记住的地方,即“driftfile "C:\ProgramFiles\NTP0606\etc\ntp.drift"”这一条,也就是说我们要在对应的目录下创建一个名为“ntp.drift”的文件,文件的内容为“0.000”,然后再把server 127.127.1.0fudge 127.127.1.0 stratum 12这两行配置文件前面的“#”去掉。

Window搭建局域网NTP服务器

Window搭建局域网NTP服务器在局域网环境中,搭建一个可靠和准确的NTP(Network Time Protocol)服务器对于网络管理和时间同步非常重要。

本文将介绍如何在Windows操作系统下搭建一个局域网NTP服务器,确保网络中各设备的时间同步。

一、背景介绍网络中的设备通常需要准确同步时间,以确保各个设备之间的时间一致性。

NTP服务器通过向客户端提供准确的时间信息,实现网络中所有设备的时间同步。

二、准备工作在搭建局域网NTP服务器之前,需要确保以下准备工作已经完成:1. Windows操作系统:本文以Windows Server 2016为例进行介绍,但其他版本也可以进行类似操作。

2. 确保网络连接正常:确保服务器连接到局域网,并具备访问互联网的能力。

3. 管理员权限:在Windows Server上进行配置需要管理员权限。

三、安装和配置NTP服务器1. 安装NTP服务器软件:从可靠的来源下载并安装NTP服务器软件,如“Meinberg NTP”或“Symmetricom NTP”等。

2. 配置服务端:打开NTP服务器软件的配置文件,根据软件提供的说明进行相关配置。

常见的配置项包括服务器的地址、使用的NTP协议版本等。

3. 启动NTP服务器:保存配置文件并启动NTP服务器服务。

四、防火墙配置1. 开放NTP服务器端口:为了使局域网中的客户端能够与NTP服务器进行通信,需要在防火墙中开放NTP服务器的端口。

默认情况下,NTP服务器使用UDP 123端口。

2. 配置防火墙规则:打开防火墙设置,添加一个规则,允许流量通过NTP服务器的端口。

五、验证NTP服务器1. 客户端配置:在局域网中的某个客户端上配置NTP服务器信息,包括服务器的IP地址或域名。

2. 同步时间:客户端通过与NTP服务器进行通信,同步服务器时间。

3. 验证同步:验证客户端的时间是否与NTP服务器的时间一致。

可以使用命令行工具或者图形界面工具进行验证。

NTP服务器的配置

NTP服务器的配置2008-01-31 09:51:10本文介绍了时间服务器常用的二种协议:SNTP和TIME,并就局域网环境下各种系统(Linux、Windows98、2000、XP)时间服务的设置分别进行了说明,最终实现整个局域网环境下所有电脑时钟的同步与校准。

一、什么是网络时间服务网络时间服务Net Time Service与网络文件下载服务FTP、网络浏览服务WWW等一样,是一种网络服务,提供网络时间服务的电脑叫网络时间服务器。

当然有些时间服务器是纯硬件结构的,通过GP S卫星信息来获取时间,其外观与一台交换机相似,不在文本介绍之列。

本文主要介绍一台电脑如何通过网络获取上级时间服务器提供的标准时间,再服务于本单位的局域网,使一个单位的所有电脑都能与标准时间保持同步,时间误差一般小于0.5秒。

TCP/IP协议中,用于同步时间的协议为NTP协议,它是由美国德拉瓦大学的David L. Mills教授于1985年提出,除了可以估算封包在网络上的往返延迟外,还可独立地估算计算机时钟偏差,从而实现在网络上的高精准度计算机校时,它是设计用来在Internet上使不同的机器能维持相同时间的一种通讯协议。

时间服务器(time server)是利用NTP的一种服务器,通过它可以使网络中的电脑保持时间同步。

NTP是一个跨越广域网或局域网的复杂的同步时间协议,它通常可获得毫秒级的精度。

SNTP(Simple Netw ork Time P rotocol)是NTP的一个子集,目的是为了那些不需要NTP实现复杂性网络时间同步的主机。

通常用于局域网上的若干台主机通过互联网与其他的NTP主机同步时钟,接着再向局域网内其他客户端提供时间同步服务。

SNTP一般使用UDP的123端号,Linux系统和Windows系统都支持它,是现在架设网络时间服务器的主流协议。

Time P rotocol (RFC-868)协议是一种较简单的协议。

NTP(时间同步服务器)配置

NTP(时间同步服务器)配置NTP(网络时间协议)是一种用于网络中计算机时间同步的协议。

它通过一组服务器,称为时间同步服务器,将准确的时间信息传递给其他计算机,以确保整个网络中的时间一致性。

配置NTP服务器是很重要的,本文将介绍如何进行NTP服务器的配置。

首先,安装并配置NTP服务器软件。

在大多数Linux发行版中,可以使用以下命令来安装NTP服务器软件:```sudo apt-get install ntp```1.配置服务器的参考时间源。

NTP服务器需要一个可靠的时间源来同步时间。

可以从多个公共NTP服务器选择一个参考时间源。

可以在配置文件中添加以下行来指定参考时间源:``````2.配置其他NTP服务器。

可以选择指定其他NTP服务器作为备用时间源。

这些服务器将在参考时间源不可用时使用。

可以添加以下行来指定其他NTP服务器:``````3. 配置允许访问NTP服务器的客户端。

可以通过使用`restrict`命令来限制可以访问NTP服务器的客户端。

可以添加以下行来指定允许访问的客户端:```restrict 192.168.0.0 mask 255.255.255.0 nomodify notrap```其中,`192.168.0.0`应替换为允许访问的客户端的IP地址范围。

4.配置NTP服务器的日志记录。

可以通过添加以下行来配置NTP服务器的日志记录:```logfile /var/log/ntp.log```这将指定日志文件的路径和文件名。

5.配置时间同步频率。

可以通过添加以下行来配置时间同步的频率:```minpoll 4maxpoll 6```其中,`minpoll`表示最小的间隔时间单位,`maxpoll`表示最大的间隔时间单位。

较小的值表示更频繁的时间同步。

6.配置NTP服务器的启动选项。

可以通过添加以下行来配置NTP服务器的启动选项:```#启用NTP服务器server 127.127.1.0fudge 127.127.1.0 stratum 10```这将启用本地计算机作为NTP服务器以提供时间同步服务。

局域网搭建NTP时间服务器及配置

局域网搭建NTP时间服务器及配置局域网中搭建NTP(Network Time Protocol)时间服务器可以确保网络中的所有设备都能够同步时间,提高网络的稳定性和安全性。

本文将介绍搭建NTP时间服务器的步骤以及配置方法。

1.确认网络拓扑结构:在搭建NTP时间服务器之前,需要明确网络的拓扑结构。

通常情况下,一个局域网中至少会有一台用作时间服务器的设备,并且所有其他设备都要能够直接或间接地访问到时间服务器。

2.选择合适的硬件设备:搭建NTP时间服务器所需的硬件设备可以是一台独立的物理服务器,也可以是一台虚拟机。

确保服务器的资源足够满足网络中所有设备的时间同步需求。

3. 安装操作系统:根据服务器的硬件要求,选择合适的操作系统。

常见的选择包括Windows Server、Linux等。

安装操作系统之后,确保服务器的网络配置正确,可以正确地与局域网中的其他设备通信。

4. 安装NTP软件:根据选择的操作系统,安装相应的NTP软件。

如果是Windows Server,可以安装Meinberg NTP等软件;如果是Linux,可以安装NTPd等软件。

安装软件的过程会涉及到配置文件的设置,其中包括时间服务器的相关参数,例如时间源、时间同步方式等。

5.配置NTP服务器:根据实际需求,配置NTP服务器的参数。

例如,指定时间源服务器的IP地址或域名,设置时间同步的方式(一般采用时钟同步或频率同步),调整时间服务器的时钟精度等。

6.配置网络设备:在局域网中的其他设备上进行NTP配置,使其能够与时间服务器进行时间同步。

具体的配置方法会因设备的型号和操作系统而有所不同,可以参考设备的文档或官方网站进行配置。

7.测试同步效果:在完成NTP服务器和网络设备的配置后,进行时间同步的测试。

可以通过在各个设备上查看时间,确认它们是否与时间服务器的时间保持一致。

如果存在差异,可以检查配置文件和参数,或者检查网络的连接和延迟。

8.定期维护和监控:建议定期对NTP时间服务器进行维护和监控。

NTP协议介绍及实现方案

NTP协议介绍及实现方案NTP(Network Time Protocol,网络时间协议)是一种用于计算机网络中精确同步时间的协议。

它的发展旨在解决网络中计算机时钟不同步的问题,确保网络上的所有设备拥有相同的时间。

NTP协议采用客户端-服务器模型,其中服务器负责提供精确时间参考,而客户端设备通过与服务器相同的协议进行时间同步。

一.服务端的实现方案:1.获得精确时间源:NTP服务器需连接外部的精确时间源,例如GPS 卫星或国家时间标准台,以获取准确的时间信息。

2. 安装和配置NTP服务器软件:在服务器上安装和配置NTP服务器软件,如OpenNTPD、Chrony或NTPd等。

3.配置时间源:将精确时间源的信息输入到NTP服务器软件的配置文件中,以便服务器可以获取精确的时间同步信息。

4.启动NTP服务器:启动NTP服务器软件,让其开始运行。

NTP服务器将监听网络上的时间请求,并根据配置的时间源提供准确时间信息。

5.配置防火墙:如果服务器使用防火墙,需要配置防火墙允许外部设备通过NTP协议与服务器进行通信。

二.客户端的实现方案:1.获取NTP服务器信息:通过网络查找可用的NTP服务器列表。

2. 安装和配置NTP客户端软件:在客户端设备上安装合适的NTP客户端软件,如Chrony或NTPd。

3.配置NTP服务器:将NTP服务器的信息输入到NTP客户端的配置文件中,以便客户端可以与指定的NTP服务器进行时间同步。

4.启动NTP客户端:启动NTP客户端软件,让其开始运行。

NTP客户端将向指定的NTP服务器发送时间同步请求,并同步客户端设备的时间。

5.配置定时同步:通过配置NTP客户端软件的参数,可以设置定时同步的间隔和频率。

NTP协议的工作原理是通过精确时间源和时间同步算法来保持网络中设备的时间同步。

NTP客户端通过向NTP服务器发送时间同步请求,服务器将返回当前的准确时间信息。

根据返回的时间信息和本地设备的时间,客户端设备会做出调整,使本地时间与服务器时间保持同步。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第3章NTP网络授时系统服务器硬件设计3.1 服务器端硬件系统结构图NTP服务器的硬件设计,按照最小设计的原则,以保证整个硬件的尺寸符合要求,只提供系统所必须的功能,如串口、以太网口等。

系统结构如图3-1所示:图3-1 NTP服务器硬件实现框图3.2 系统硬件选型3.2.1 芯片选型根据前面的需求分析和硬件总体设计,结合实际应用和实现的需要,选择以下硬件芯片,如表3-1所示。

表3-1 NTP服务器芯片选型3.2.2 S3C4510B简介本系统选择了ARM架构的Samsung的S3C4510B处理器作为整个服务器硬件的核心。

ARM(Advanced RISC Machines)架构是面向低预算市场设计的第一款RISC 微处理器,除了RISC的一些特点外,ARM体系结构还采用了一些特别的技术,在保证提高性能的前提下尽量缩小芯片的面积,并降低功耗。

ARM微处理器具有体积小、低功耗、低成本、高性能的特点,支持Thumb(16位)/ARM(32位)双指令集,大量使用存储器而使指令执行速度更快,寻址方式灵活简单,执行效率高,指令长度固定等优点,主要应用在工业控制、无线通讯、网络应用、消费电子、成像产品、安全产品、存储产品、汽车行业等领域[10]。

S3C4510B是Samsung公司生产的基于以太网应用的高性价比16/32位RISC 微控制器,内含一个由ARM公司设计的16/32位ARM7TDMI RISC处理器核[11]。

另外,S3C4510B的片内外围功能模块主要包括:——2个带缓冲描述符(Buffer Descriptor)的HDLC通道——2个UART通道——2个GDMA通道——2个32位定时器——18个可编程的I/O口S3C4510B的片内逻辑电路包括:——中断控制器——DRAM/SDRAM控制器——系统管理器——ROM/SRAM和FLASH控制器——一个内部32位系统总线仲裁器——一个外部存储器控制器S3C4510B的结构框图如下图所示。

图3-2 S3C4510B结构框图[11] S3C4510B的引脚分布如下图所示:图3-3 S3C4510B引脚分布图[11]S3C4510B共有208只引脚,采用QFP封装,其主要控制信号如下:LITTLE(pin49):大小端模式选择。

1=小端模式,0=大端模式。

该引脚片内下拉默认大端模式,在实际系统中常用小端模式,因此该引脚应该上拉或接电源。

FILTER(Pin55):若使用PLL倍频电路,应在该引脚和地之间接820pF的陶瓷电容。

实际应用中一般使用PLL电路,因此应该用该电容连接。

TCK/TMS/TDI/TDO/nTRST(Pin58~62):JTAG接口引脚。

根据IEEE标准,TCK应该下拉,TMS、TDI、nTRST应上拉,S3C4510B已经按此标准在片内连接,只需与JTAG插座直接相连即可。

TMODE(pin63):测试模式。

1=芯片测试模式,0=正常工作模式。

用户一般不使用测试模式,该引脚一般下拉或接地。

nEWAIT(pin71):外部等待请求信号,该引脚应上拉。

B0SIZE[1:0](pin74,73):BANK0数据宽度选择。

01=8位,10=16位,11=32位,00=系统保留CLKOEN(pin76):时钟输出允许、禁止,1=允许,0=禁止。

一些外围器件入SDRAM需要CPU的时钟输出作为自身的时钟源,该引脚一般接高电平使得时钟输出为允许。

XCLK(pin80):系统时钟源,接有源晶振的输出。

nRESET(pin82):系统复位引脚,低电平复位,系统正常工作时该引脚处于高电平。

CLKSEL(pin83):时钟选择。

1=XCLK直接作为系统的工作时钟,0=XCLK经过PLL电路倍频后作为系统的工作时钟。

ExtMREQ(pin108):外部主机总线请求信号,该引脚应该下拉。

S3C4510B其余引脚为电源线、地线、数据总线、地址总线及其他功能模块的输入输出线,对CPU自身的运行影响相对较小,其连接方式也比较简单。

3.3 部分硬件单元设计基于嵌入式的NTP服务器硬件设计主要包括以下几部分:串口电路设计、存储器接口设计、复位电路设计、网络接口设计、IIC接口、JTAG接口电路设计等。

3.3.1 复位电路在系统中,复位电路主要完成系统的上电复位和系统在运行时用户的按键复位功能。

复位电路可由简单的RC电路构成,也可使用其他的相对较复杂,但功能更完善的电路。

本系统复位电路设计较为简单,其实现原理图如图3-4 所示。

当上电初始化时,按RESET 处于断开状态,电容C13 通过电阻R3 充电,此时第一个驱动门IC11A 输出高复位电平,第二个驱动门IC11B 输出低复位电平,复位时间由电阻和电容的时间常数确定。

待电容充电完成,IC11A 输出低电平而IC11B 输出高电平。

当按键闭合时,电容开始放电,两个驱动门回到复位状态。

74HC14 门电路在于提高复位电平的负载能力和增强按键的去抖动能力,使复位操作能够正确无误地执行。

图3-4 复位电路3.3.2 10/100M以太网接口电路S3C4510B内嵌一个以太网控制器,支持媒体独立接口(Media Independent Interface,MII)和带缓冲DMA接口(Buffered DMA Interface,BDI)。

可在半双工或全双工模式下提供10M/100Mbps的以太网接入。

在半双工模式下,控制器支持CSMA/CD协议,在全双工模式下支持IEEE802.3 MAC控制层协议。

因此,S3C4510B内部实际上已包含了以太网MAC控制,但并未提供物理层接口,需外接一片物理层芯片以提供以太网的接入通道。

常用的单10M/100Mbps高速以太网物理层接口器件主要有RTL8201、DM9161等,均提供MII接口和传统7线制网络接口,可方便的与S3C4510B接口。

以太网物理层接口器件主要功能一般包括:物理编码子层、物理媒体附件、双绞线物理媒体子层、10/100BASE-TX编码/解码器和双绞线媒体访问单元等。

在该系统中,使用RTL8201[12]作为以太网的物理层接口。

以下分别为RTL8201的引脚分布图和相关引脚功能描述,表中仅列出芯片在100Mbps MII 接口方式下的引脚定义,当工作于7线制网络接口方式,部分引脚定义不同。

更具体的内容和使用方法可参考RTL8201的用户手册。

图3-5 RTL8201引脚分布图[12]表3-2 RTL8201引脚功能描述表3-2 RTL8201引脚功能描述(续表)由于S3C4510B片内已有带MII接口的MAC控制器,而RTL8201也提供了MII接口,各种信号的定义也很明确,因此RTL8201与S3C4510B地连接比较简单。

实际应用电路图见下图。

图3-6 10/100M以太网接口电路S3C4510B 的MAC控制器可通过MDC/MDIO管理接口控制多达31个RTL8201,每个RTL8201应有不同的PHY地址(可从00001B到11111B)。

当系统复位时,RTL8201锁存引脚9,10,12,13,15的初始状态作为与S3C4510B 管理接口通信的PHY地址,但该地址不能设为00000B,否则RTL8201进入掉电模式。

信号的发送和接收端应通过网络隔离变压器和RJ45接口接入传输媒体,其实际应用电路见下图。

图3-7 RTL8201与网络隔离变压器及RJ45的连接图3.3.3 存储器接口设计ARM 处理芯片大多不具有存储功能,它所需要的ROM 和RAM 都要扩展外部存储器而得到,ARM 芯片提供专门的数据接口与存储器的连接。

为了完成最小系统的设计,本课题的ROM 存储器采用HYUNDAI 公司生产的HY29LV160 FLASH 存储器,而RAM 采用该公司生产的HY57V641620 SDRAM 存储器,以此构建2MB 的代码存储系统和16MB 的随机存取系统。

HY29LV160[13]是一款单片容量为16Mb(2MB),工作电压为2.7V-3.6V,采用TSOP管脚封装,16 位数据宽度。

该芯片仅需3V电压即可完成在系统编程操作。

考虑到容量问题和成本问题,本课题采用该芯片构建16 位的FLASH 存储器,其管脚连接接口电路如图3-8所示。

图3-8 FLASH接口电路其中S3C4510B 芯片的20 位地址线与FLASH 的地址线相对应连接,前16位数据线与flash 的数据线相连接,再加上读写控制信号构成16位数据存储方式。

57V641620[14]是一款性价比较高的SDRAM存储器,其存储容量为4组×16Mb(8MB),工作电压3.3V,54脚TSOP封装。

它可支持自动刷新和自刷新,具有16位数据宽度,从速度和容量方面考虑,本课题采用两片57V641620构造32位RAM存储系统,具体接口电路如图3-9 所示。

图3-9 SDRAM存储器接口电路3.3.4 IIC接口电路设计IIC 总线是一种用于IC 器件之间连接的二进制总线。

他通过SDA(串行数据线)及SCL(串行时钟线)两线在连接到总线上的器件之间传递信息,并跟据地址来识别器件。

通常,这种接口的器件结构紧凑,修改和可宽展性好,广泛地使用在板级器件间的信息交换上。

S3C4510B内含一个IIC总线主控器,可方便地与各种带有IIC接口的器件相连。

本系统采用带有IIC 接口电路的EEPROM 存储器A T24C01[15]与S3C4510B 相连接作为IIC存储器。

AT24C01提供128 字节的存储空间用于存放网络接口的物理地址等需要掉电保护的数据。

图3-10 为A T24C01的接口电路。

图3-10 A T24C01接口电路图3.3.5 JTAG接口电路设计JTAG(Joint Test Action Group,联合测试行动小组)是一种国际标准测试协议,JTAG电路主要用于芯片内部测试及对系统进行仿真、调试,为软件的开发和测试提供了一种简便的方法。

JTAG技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路TAP(Test Access Port,测试访问接口),通过专用的JTAG测试工具对内部节点进行测试。

通常,可以通过JTAG 口外加仿真器对开发的程序的有效性进行简单仿真,也可用于系统编程。

JTAG 接口一般有两种标准即双列14 针和20 针,本系统采用20 针的JTAG 标准,其管脚定义和接口如表3-2 所示表3-3 20针JTAG接口定义3.3.6 RS232串行接口电路几乎所有的微控制器、PC都提供串行接口,使用电子工业协会(EIA)推荐的RS-232-C标准,这是一种很常用的串行数据传输总线标准。

早期它被应用于计算机和终端通过电话线和MODEM进行远距离的数据传输,随着微型计算机和微控制器的发展,不仅远距离,近距离也采用该通信方式。