Verilog教程夏宇闻PPT课件

天津大学 Verilog 课件 第一讲概述

44

Verilog与C语言的关系

算法的描述和验证常用C语言来完成。

Verilog用于行为级和RTL级描述。 C语言与Verilog HDL可以配合使用。

C语言与Verilog HDL的语法很像,许多关键字

相同。

45

世界上第一个晶体管是1947年由肖克利和他的两助手布拉顿、巴丁在贝尔实验室工作 时发明的,为此,肖克利三人于1956年获得诺贝尔物理学奖。用晶体管代替电子管制 造电脑,在电脑史上是一次突破性技术飞跃。 1954年,贝尔实验室使用800支晶体管组装成功人类有史以来第一台晶体管计算机 TRADIC

25

45nm四核Core 2 Quad Q9650

3.0GHz时钟频率;NL则代表2 x 6MB共12MB的二级缓存容量 , Yorkfield内核四核心处理器拥有8.2亿个晶体管,这比Kentsfield内核的 5.82亿个晶体管足足多出了2.38亿个之多。其中,50%的二级缓存容量增 长约占据了1.92亿个晶体管,而余下的部分则分别由新增的SSE4多媒体 指令运算单元以及微架构的改良部分所占据。

TJIC

超大规模集成电路设计专用语言

1

选用教材

Verilog 数字系统设计 教程 作者: 夏宇闻编 出版社:北京航空航 天大学出版社 出版日期:2003-7-1 ISBN:7-81077-302-X 定价:38.00元

2

参考资料(一) 参考资料

<<VERILOG HDL硬件描述 语言 >>

37

集成电路的设计流程(1)

TJU. ASIC Center---verilog2008秋

38

集成电路的设计流程(2)

verilog数字系统设计教程PPT课件

• 复杂数字系统的构成; • 基本电路和 Verilog 的对应关系; • 同步有限状态机在电路中的作用; • 时钟树与自动综合技术

数字逻辑电路的构成

- 组合逻辑:输出只是输入逻辑电平的函

数(有延时),与电路的原始状态无关。

• 时序逻辑:输出不只是输入的逻辑电

平的函数,还与电路所处的状态有关。

8 ‘ d 31

8‘d

t

out[15:0]

202

16 ‘ d

16‘ d

t

Sn 开

93

606

t 关

全局时钟网和平衡树结构

触发器1

全局时钟网络 触发器 图1 全局时钟网示意图

缓冲器

触发器n

图2 平衡树结构示意图

避免冒险和竞争

• 由于组合逻辑和布线的延迟引起

a

c

b

a

b

t

c

t

clock

避免冒险和竞争与流水线

t

t

带寄存器的八位数据通路控制器的波形

ControlSwitch

in[7]

out[7]

CLOCK

out[7]

D Q[7]

ControlSwitch

in[0]

out[0]

CLOCK

out[0]

D Q[0]

带寄存器的八位数据通路控制器的Verilog描述

`define ON 1 ‘b 1 `define OFF 1 ‘b 0 wire ControlSwitch; wire clock wire [7:0] out, in;

ControlSwitch in[7]

out[7]

…... …...

in[0]

Verilog数字系统设计教程[夏宇闻]PPT课件

![Verilog数字系统设计教程[夏宇闻]PPT课件](https://img.taocdn.com/s3/m/4645846c58fafab069dc0258.png)

设计示例四(续) 用激励信号对进位计数器进行测试

module stimulus; reg clk; reg reset; wire[3:0] q; // instantiate the design block ripple_carry_counter r1(q, clk, reset); // Control the clk signal that drives the design block. initial clk = 1'b0; always #5 clk = ~clk;

设计示例四 带异步复位端的 D 触发器

module DFF(q, d, clk, reset); output q; input d, clk, reset; reg q; always @(posedge reset or negedge clk) if (reset) q <= 1'b0; else q <= d; endmodule

设计示例二

由已设计的模块来构成高一级的模块

q3

q2

q1

q0

d

q

d

f4

clk clr

f3

clk clr

q

d

f2

clk clr

q

d

f1

clk clr

q

clrb

clk

d3

d2

d1

d0

四位寄存器电路结构图

设计示例二 `include “ flop.v ” module hardreg(d,clk,clrb,q); input clk,clrb; input[3:0] d; output[3:0] q; flop f1(d[0],clk,clrb,q[0],), f2(d[1],clk,clrb,q[1],), f3(d[2],clk,clrb,q[2],), f4(d[3],clk,clrb,q[3],); endmodule

2Verilog语言快速入门专题培训课件

(3) 关系运算符

> 大于 < 小于 >= 大于等于 <= 小于等于

例: Y=(3>2) Y=(3<2); Y=(3>=2); Y=(3<=2); Y=(3<=1’bx);

结果为1 结果为0 结果为1 结果为0

结果为x

说明 关系运算的结果可能是1(逻辑真)、0(逻辑假)、x(不确定);

2Verilog语言快速入门

Verilog模块结构

module 模块名 ([端口列表]); [端口信号声明;] [参数声明;]

内部信号声明

assign语句

底层模块或门原语 调用(包括生成块)

Initial或always 语句块

任务和函数定义 specify 块(路径延迟)

模块说明部分

说明: 浅色部分用得较少; 常用语句只有三种:

赋值目标必须是wire型的,wire表示电路间的连线。

8

2. assign语句

例:assign M=B|C;

assign Y=A&M;

M

M和Y都必须是wire型的

9

2. assign语句 详见夏宇闻教材第6章,自学。

Verilog具有丰富的表达式运算功能,可用于assign语句

10

(1) 算术型

参数声明要说明参数的名称和初值

6

例: module full_adder (A,B,CIN,S,COUT); input [3:0] A,B; input CIN; output reg [3:0] S; output COUT;

位宽如果不做说明的话,默认是1位; 数据类型不做说明的话,默认是wire型的。

Verilog教程-夏宇闻(共178张)

第13页,共178页。

3.2 Verilog HDL基本(jīběn)结构

二、Verilog HDL模块的结构

▪ Verilog的基本设计单元是“模块 (block) ” 。 ▪ Verilog 模块的结构由在module和endmodule关键词

之间的4个主要部分组成:

1 端口定义 2 I/O说明

(3)用 “always” 块语句 结构说明语句

always @(posedge clk) // 每当时钟上升沿到来时执行一遍块内语句

begin

if(load)

out = data; // 同步预置数据 else

out = data + 1 + cin; // 加1计数

end

❖注1:“always” 块语句常用于描述时序逻辑,也可 描述组合逻辑。

3.12 不同抽象级别的Verilog HDL模型

1

3.13 设计技巧

第1页,共178页。

引言 3.1

(yǐnyán)

内容概要

一、什么是Verilog HDL 二、Verilog HDL的发展历史 三、不同层次的Verilog HDL抽象

四、Verilog HDL的特点

2

第2页,共178页。

3.1 引言(yǐnyán)

❖ Verilog HDL模块的模板(仅考虑用于逻辑综合的部分)

module <顶层模块名> (< 输入输出端口列表>) ;

output 输出端口列表;

input 输入端口列表;

//(1)使用assign语句定义逻辑功能

wire 结果信号名;

assign <结果信号名> = 表达式 ;

【课件】Verilog教程清华微电所精编版

VERILOG HDL的设计流程

自顶向下(Top-Down)设计 一个系统由总设计师先进行系统描述

(Spec),将系统划分为若干模块,编写 模块模型(一般为行为级),仿真验证后, 再把这些模块分配给下一层的设计师, 由他们完成模块的具体设计,而总设计 师负责各模块的接口定义

VERILOG教程(1)

清华大学微电子学研究所 2003年9月

提纲

Verilog概述 Verilog程序的基本结构 Verilog上机环境及工具

Verilog概述 Verilog程序的基本结构 Verilog上机环境及工具

VERILOG概述

什么是Verilog HDL? Verilog HDL(Hardware Discription Language)是一种硬件描述语言,用于从 算法级、门级到开关级的多种抽象设计 层次的数字系统建模。

VERILOG HDL与 C语言

虽然Verilog的某些语法与C语言接近,但存在 本质上的区别

Verilog是一种硬件语言,最终是为了产生实际的硬 件电路或对硬件电路进行仿真

C语言是一种软件语言,是控制硬件来实现某些功 能

利用Verilog编程时,要时刻记得Verilog是硬件语 言,要时刻将Verilog与硬件电路对应起来

数据流方式 行为方式 结构方式 上述方式的混合

模块

简单的例子(数据流方式) module HalfAdder(A, B, Sum, Carry);

input A, B; output Sum, Carry;

assign #2 Sum=A^B; assign #5 Carry=A&B; endmodule

北航 夏宇闻 Verilog HDL语法详细讲解

简单ROM建模

my_rom_data myrom.v 0000 `timescale 1ns/10ps 0101 module myrom(read_data,addr,read_en_); 1100 input read_en_; 0011 input [3:0] addr; 1101 output [3:0] read_data; 0010 reg [3:0] read_data; 0011 1111 reg [3:0] mem [0:15]; 1000 initial 1001 $readmemb(“my_rom_data”,mem); 1000 always @ (addr or read_en_) 0001 if(!read_en_) ROM的数据存储在另外 1101 read_data=mem[addr]; 的一个独立的文件中 1010 endmodule 0001

语法详细讲解

怎样使用任务

endmodule 在测试模块中使用任务可以提高程序代码的效率,可以进行多次 重复操作。 cpu_data clk data_valid data_read read_cpu_state

wait wait data1 data2 wait data3 data4 wait

语法详细讲解

建立时钟 建立时钟

[例3]. 带延迟、头一个脉冲不规则的、占空比不为1的时钟:

reg clk; initial begin #(period+1) clk=1; #(period/2-1) forever begin #(period/4) clk=0; #(3*period/4) clk=1; end end reg go; wire clk; nand ul(clk,clk,go); initial begin #(period/4+1) go=0; #(5*period/4-1) go=1; end

北航夏宇闻verilog讲稿ppt语法入门.pptx

▪ 通过简单的例子了解Verilog模块的基本构成 ▪ 了解Verilog模块的层次结构和行为模块 ▪ 了解Verilog模块的测试

简单的 Verilog HDL 模块

下面先介绍几个简单的Verilog HDL程序,然后从中分 析Verilog HDL程序的特性。

例[2.1.1]: module adder ( count,sum,a,b,cin ); input [2:0] a,b; input cin; output count; output [2:0] sum; assign {count,sum}=a+b+cin; endmodule

转换为门级电路互连的电路结构(综合)。 ▪ 需要对已经转换为门级电路结构的逻辑

进行测试(门级电路仿真)。 ▪ 需要对布局布线后的电路结构进行测试。

(布局布线后仿真)。

模块的测试

激励和控 制信号

被测模块

输出响应 和验证

பைடு நூலகம்

模块的测试

测试模块常见的形式:

module t; reg …; //被测模块输入/输出变量类型定义 wire…; //被测模块输入/输出变量类型定义 initial begin …; …; …; end … …//产生测试信号 always #delay begin …; end … …//产生测试信号

endmodule

简单的 Verilog HDL 模块

上述程序例子通过另一种方法描述了一个三态 门。

在这个例子中存在着两个模块:模块trist1 调用模块 mytri 的实例元件 tri_inst。

模块 trist1 是上层模块。模块 mytri 则被称 为子模块。

通过这种结构性模块构造可构成特大型模块。

systemVerilog快速入门PPT

// 4态,Verilog-2001(位宽可变)数据类型 //4态,Verilog-2001(32位)有符号数据类型 //4态,(位宽可变) 0,1,x,或者 z //2态,(位宽可变) 1位 0 或 1 //2态,(8位)有符号整型数 //2态,(16位)有符号整型数 //2态,(32位)有符号整型数 //2态,(64位)有符号整型数

极大地提高了仿真速度

仅一种语言就能解决设计和测试问题

Co-sim HDL Simultion Overhead

testbench

使得我们有可能使用更 高速度的仿真工具,加 速了设计的完成

SystemVerilog

testbench

设计和验证语言的统一提高了设计效率,学习周期 设计和验证语言的统一提高了设计效率, 很短,设计和验证人员都乐意采用: 很短,设计和验证人员都乐意采用: 可自动生成高级的受约束-随机测试信号语句, - 可自动生成高级的受约束-随机测试信号语句,大 大降低了设计和验证的复杂度; 大降低了设计和验证的复杂度; - 完整的统一的断言技术改善了设计小组和验证小 组之间的交流。 组之间的交流。

SystemVerilog 是Verilog-2001扩展后的超集 扩展后的超集

---------------------------------- Verilog -2001 -------------------------------

ANSI C style ports standard file I/O (* attributes *) generate $value$plusargs configurations localparam `ifndef `elsif `line memory part selects constant functions @* variable part select

verilog之一讲资料

2、成为IC设计的一项独立技术,成为实现SoC设计 的技术支撑以及ASIC设计方法学中的学科分支。

从设计来源上说,单纯靠Foundry设计IP模块已远不能 满足系统设计师的要求。IP库需要广开设计源头,汇纳 优秀模块。不论出自谁家,只要是优化的设计,与同类 模块相比达到芯片面积更小、运行速度更快、功率消耗 更低、工艺容差更大,就自然会有人愿意花钱使用这个 模块的“版权”,因此也就可以纳入IP库,成为IP的一 员。

原理图输入方式的基本思路是从元件库中选取 所需的元器件符号,或自行创建的新元器件,然 后按照设计要求进行连线。

文本编辑输入方式与传统的计算机软件语言编 辑输入基本一致。就是将使用了某种硬件描述语 言(HDL)的电路设计文本,如VHDL或Verilog的 源程序,进行编辑输入。

文本输入方式可以克服原理图输入方式存在的 弊端,为EDA技术的应用和发展打开了一个广阔 的天地。

Verilog HDL 的抽象级别

语言本身提供了各种层次抽象的表述,可以用详细 程度有很大差别的的多层次模块组合来描述一个电路 系统。

行为级:技术指标和算法的Verilog描述 RTL级:逻辑功能的Verilog描述 门级 :逻辑结构的Verilog描述 开关级:具体的晶体管物理器件的描述

Verilog HDL 的抽象级别

固IP是完成了综合的功能块。它有较大的设计深度,以网 表文件的形式提交客户使用。优点成功率高。缺点:只 能库调用

硬IP提供设计的最终阶段产品:掩膜。随着设计深度的提 高,后续工序所需要做的事情就越少,当然,灵活性也 就越小。

IP库简介

8051和ARM7、PowerPC等微处理器、320C30等数字信号 处理器、MPEGII等数字信息压缩/解压器在内的大规 模IC模块。曾是IC产品,曾广泛用来与其他功能器件一 起,在PCB上构成系统主板。

北航 夏宇闻 Verilog HDL语法具体讲解

语法详细讲解

载入存储设备

可以通过使用一个循环或系统任务来载入存有数据的整个存储 器。

ata ,,,,,,,,,,,,,,,0 000 ,,,,,,,,,,,,,,,0 101

reg [3:0] mem [0:15];

,,,,,,,,,,,,,,,1

initial

100

$readmemb(“my_rom_data”,mem); always @ (addr or read_en_)

,,,,,,,,,,,,,,,0

的节点或测试模块中在多个地方被赋值的信号)进行赋值。 initial begin

#10 assign top.dut.fsml.state_reg = `init_state;

语字语强语强法符法制法制详串详详激激,细,细,细励励,,讲讲,讲,,解,解,解

#20 deassign top.dut.fsml.state_reg; end force 和 release 用于寄存器类型和网络连接类型(例如:门级扫 描寄存器的输出)的强制赋值,强制改写其它地方的赋值。

语法详细讲解

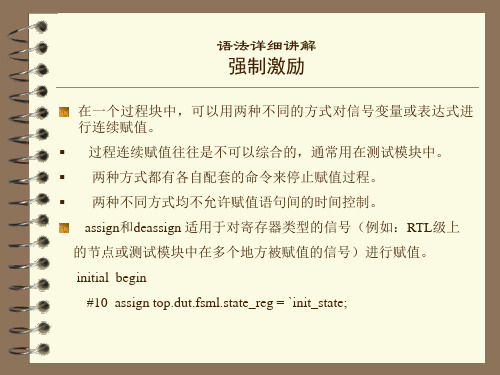

强制激励

在一个过程块中,可以用两种不同的方式对信号变量或表达式进 行连续赋值。 ▪ 过程连续赋值往往是不可以综合的,通常用在测试模块中。 ▪ 两种方式都有各自配套的命令来停止赋值过程。 ▪ 两种不同方式均不允许赋值语句间的时间控制。 assign和deassign 适用于对寄存器类型的信号(例如:RTL级上

,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,

,,k注延,,,,,,,,:迟,,,,,,,,这期,,,#,,(两间,p,,e,个一,r,i,o,时直,d,,/,2钟 是,,),,,模低,,,,,,,,型电,c,l,k,有平,=,,,!些,,c,,l,不而同门,级行描为述描的述模的型模开型始

夏宇文 第八章

第八章可综合的VerilogHDL设计实例---简化的RISC CPU设计简介---前言:在前面七章里我们已经学习了VerilogHDL的基本语法、简单组合逻辑和简单时序逻辑模块的编写、Top-Down设计方法、还学习了可综合风格的有限状态机的设计,其中EEPROM读写器的设计实质上是一个较复杂的嵌套的有限状态机的设计,它是根据我们完成的实际工程项目设计为教学目的改写而来的,可以说已是真实的设计。

在这一章里, 我们将通过一个经过简化的用于教学目的的 RISC_CPU 的设计过程,来说明这种新设计方法的潜力。

这个模型实质上是第四章的RISC_CPU模型的改进。

第四章中的RISC_CPU模型是一个仿真模型,它关心的只是总体设计的合理性,它的模块中有许多是不可综合的,只可以进行仿真。

而本章中构成RISC_CPU的每一个模块不仅是可仿真的也都是可综合的,因为他们符合可综合风格的要求。

为了能在这个虚拟的CPU上运行较为复杂的程序并进行仿真, 因而把寻址空间扩大到8K(即15位地址线)。

下面让我们一步一步地来设计这样一个CPU,并进行仿真和综合,从中我们可以体会到这种设计方法的魅力。

本章中的VerilogHDL程序都是我们自己为教学目的而编写的,全部程序在CADENCE公司的LWB (Logic Work Bench)环境下和 Mentor 公司的ModelSim 环境下用Verilog语言进行了仿真, 通过了运行测试,并分别用Synergy和Synplify综合器针对不同的FPGA进行了综合。

分别用Xilinx和Altera公司的的布局布线工具在Xilinx3098上和Altera Flex10K10实现了布线。

顺利通过综合前仿真、门级结构仿真以及布线后的门级仿真。

这个CPU 模型只是一个教学模型, 设计也不一定合理, 只是从原理上说明了一个简单的RISC _CPU的构成。

我们在这里介绍它的目的是想说明:Verilog HDL 仿真和综合工具的潜力和本文介绍的设计方法对软硬件联合设计是有重要意义的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

endmodule

缩减运算符

位运算符

3.2 Verilog HDL基本结构

[例3.2.3] 2位比较器

module compare2 ( equal,a,b);

output equal; input [1:0] a,b;

条件运算符

assign equal = ( a = = b ) ? 1:0;

连续赋值语句

3.13 设计技巧

3.1 引言

内容概要

一、什么是Verilog HDL 二、Verilog HDL的发展历史 三、不同层次的Verilog HDL抽象 四、Verilog HDL的特点

3.1 引言

一、什么是Verilog HDL

▪ Verilog HDL是一种用于数字逻辑电路设计的硬件描述 语言(Hradware Description Language ),可以用来进 行数字电路的仿真验证、时序分析、逻辑综合。 ➢ 用Verilog HDL描述的电路设计就是该电路的 Verilog HDL模型。 ➢ Verilog HDL 既是一种行为描述语言也是一种结构描述 语言。

1995标准; ▪ 1999年,模拟和数字电路都适用的Verilog标准公开

发表

3.1 引言

三、不同层次的Verilog HDL抽象

▪ Verilog HDL模型可以是实际电路的不同级别的抽象。 抽象级别可分为五级:

➢ 系统级(system level): 用高级语言结构(如case语句)

实现的设计模块外部性能的模型;

// 输入端口声明

input cin;

assign {cout,sum}=a+b+cin;

功能描述

endmodule

assign语句:无论右边表达式操作数何时发生变化,右边表达式都 会重新计算,并且个Verilog HDL程序嵌套在module和endmodule声明语句中。 ➢ 每条语句相对module和endmodule最好缩进2格或4格! ➢ // …… 表示注释部分,一般只占据一行。对编译不起作用!

的抽象模型来描述; ➢ 基本逻辑门、开关级结构模型均内置于语言中,可直接调

用; ➢ 易创建用户定义原语(UDP,User Designed Primitive) 。

▪ 易学易用,功能强

3.2 Verilog HDL基本结构

内容概要

一、简单的Verilog HDL例子 二、Verilog HDL模块的结构 三、逻辑功能定义 四、关键字 五、标识符 六、编写Verilog HDL源代码的标准

信号类型声明

always @(posedge clk)

begin

if(load) out <= data;

// 同步预置数据 功能描述

else out < = out + 1 + cin; // 加1计数

end assign cout = &out & cin; //若out为8‘hFF,cin为1,则cout为1

单行注释符

3.2 Verilog HDL基本结构

[例3.2.2] 8位计数器

module counter8 ( out,cout,data,load, cin,clk ); 端口定义

output [7:0] out;

output cout; input [7:0] data;

I/O说明

input load, cin,clk ; reg[7:0] out;

➢ 算法级(algorithmic level): 用高级语言结构实现的设

计算法模型(写出逻辑表达式);

➢ RTL级(register transfer level): 描述数据在寄存器

之间流动和如何处理这些数据的模型;

➢ 门级(gate level): 描述逻辑门(如与门、非门、或门、

与非门、三态门等)以及逻辑门之间连接的模型;

▪ 既可以用电路的功能描述,也可以用元器件及其之间的 连接来建立Verilog HDL模型。

3.1 引言

二、Verilog HDL的发展历史

▪ 1983年,由GDA(GateWay Design Automation)公 司的Phil Moorby首创;

▪ 1989年,Cadence公司收购了GDA公司; ▪ 1990年, Cadence公司公开发表Verilog HDL; ▪ 1995 年 , IEEE 制 定 并 公 开 发 表 Verilog HDL1364-

/ * 如果a等于b,则equal 为1,否则为0 * /

endmodule

“<=”非阻塞过程性赋值:将想要赋给左式的值安排在未来时刻。不等上一个赋值 完成执行下个赋值语句。

“=” 阻塞过程性赋值:按照顺序执行,前一个赋值结束才执行下边的赋值语句。

➢ / * …… * /内表示注释部分,一般可占据多行。 对编译不起作用!

➢ 开关级(switch level): 描述器件中三极管和储存节点

及其之间连接的模型。

返回3.12

3.1 引言

四、Verilog HDL的特点

▪ 语法结构上的主要特点:

➢ 形式化地表示电路的行为和结构; ➢ 借用C语言的结构和语句; ➢ 可在多个层次上对所设计的系统加以描述,语言对设计规

模不加任何限制; ➢ 具有混合建模能力:一个设计中的各子模块可用不同级别

3.2 Verilog HDL基本结构

一、简单的Verilog HDL例子

[例3.2.1] 8位全加器 模块名(文件名)

module adder8 ( cout,sum,a,b,cin ); 端口定义

output cout; output [7:0] sum;

// 输出端口声明

I/O说明

input [7:0] a,b;

多行注释符

3.2 Verilog HDL基本结构

[例3.2.4] 三态驱动器

门元件关键字

module trist2(out,in,enable); output out; input in, enable; bufif1 mybuf(out,in,enable);

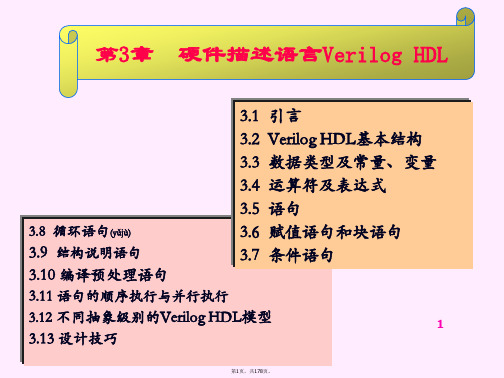

第3章 硬件描述语言Verilog HDL

3.1 引言

3.2 Verilog HDL基本结构

3.3 数据类型及常量、变量

3.4 运算符及表达式

3.5 语句

3.8 循环语句

3.6 赋值语句和块语句

3.9 结构说明语句

3.7 条件语句

3.10 编译预处理语句

3.11 语句的顺序执行与并行执行

3.12 不同抽象级别的Verilog HDL模型