Cyclone V 器件数据表

Cyclone II器件中文资料

一、外文资料译文:Cyclone II器件系列简介关键词:cyclone II器件;特点;简介;在非常成功的第一代Cyclone器件系列之后,Altera的Cyclone II FPGA系列扩大低成本的FPGA的密度,最多达68,416个逻辑单元(LE),提供622个可用的输入/输出引脚和1.1M比特的嵌入式寄存器。

Cyclone II器件的制造基于300毫米晶圆,采用台积电90nm、低K值电介质工艺,这种工艺技术是使用低绝缘体过程以确保了快速有效性和低成本。

通过使硅片面积最小化,Cyclone II器件可以在单芯片上支持复杂的数字系统,而在成本上则可以和ASIC竞争。

不像其他用电力功耗和性能来换取低成本的FPGA卖主,Altera 最新一代低价位的FPGA——cyclone II FPGA系列,和同类90nmFPGA器件相比,它提高了百分之六十的性能和降低了一半的功耗。

低成本和优化特征使Cyclone II FPGA系列为各种各样的汽车、消费、通讯、视频处理、测试与测量、和其他最终市场提供理想的解决方案。

在参考设计、系统图,和IP,使用cyclone II FPGA系列可以帮助你迅速实现最总市场方案开发。

低成本的嵌入式解决方案Cyclone II 器件支持Nio s II 嵌入式处理器,能够自己完成自定义的嵌入式处理器。

Cyclone II器件还能够扩展各种外部存储器和I/O口或者嵌入式处理器的性能。

单个或多个NiosII嵌入式系统中嵌入式处理器也可以设计成cyclone II设备以提供一些额外的同时处理的能力或者甚至取代已经在你的系统中存在的嵌入式处理器。

使用cyclone II和nios II 能够拥有成本低和高性能处理方案的共同特点,和普通的产品相比,这个特点能够延长你的产品的生命周期,提高产品进入市场的时间。

低成本DSP方案单独使用cycloneII FPGA 系列或者或者作为数字信号处理(DSP)协处理器以提高数字信号处理(DSP)应用的性价比。

EP4CE15E22C9L中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

Cyclone IV器件在商业,工业,延伸产业和汽车级版本. Cyclone IV E器件提供-6(最快 ),-7,-8,-8L和-9L速度等级的商用设备,-8L速度等级为工业设备,以及用于扩展工业和汽 车设备-7速度等级. Cyclone IV GX器件提供-6(最快),-7和-8速度等级的商用设备和 -7为工业设备的速度等级.

条件( V)

过冲持续时间为%高时间

Unit

交流输入

Vi

电压

VI = 4.20 VI = 4.25 VI = 4.30 VI = 4.35 VI = 4.40 VI = 4.45 VI = 4.50 VI = 4.55 VI = 4.60

100

%

98

%

65

%

43

%

29

%

20

%

13

%

9

%

6

%

图1-1

示出的方法来确定过冲持续时间.该

芯片中文手册,看全文,戳

1–2

第 1章: Cyclone IV器件手册

运行条件

1

Cyclone IV E工业设备I7提供具有扩展的工作温度范围.

绝对最大额定值

绝对最大额定值规定的最大工作条件Cyclone IV器件.该值是基于与所述设备和击穿和损伤 机理理论模型进行的实验.该装置的功能操作不在这些条件暗示.

从的Cyclone IV E和Cyclone IV GX器件的预期值.所有物资必须是没有高原严格单调.

表 1-3.推荐工作条件 Cyclone IV E器件

符

参数

VCCINT (3) VCCIO (3), (4) VCCA (3)

电源电压为内部逻辑, 1.2-V操作

cyclonev GIC

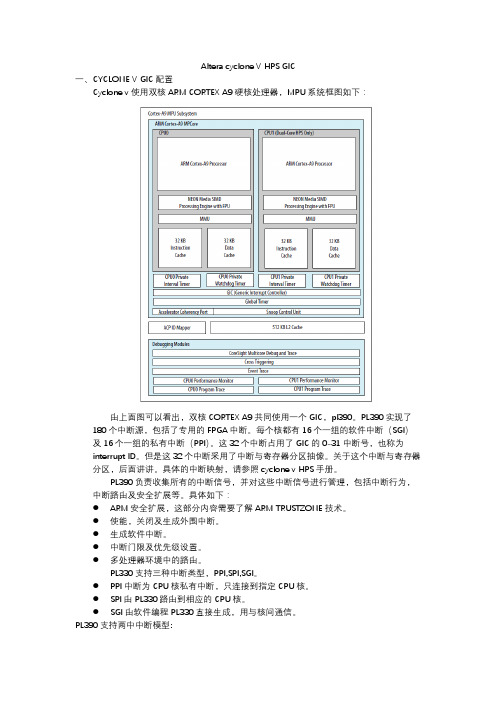

Altera cyclone V HPS GIC一、CYCLONE V GIC配置Cyclone v使用双核ARM CORTEX A9硬核处理器,MPU系统框图如下:由上面图可以看出,双核CORTEX A9共同使用一个GIC,pl390。

PL390实现了180个中断源,包括了专用的FPGA中断。

每个核都有16个一组的软件中断(SGI)及16个一组的私有中断(PPI)。

这32个中断占用了GIC的0-31中断号,也称为interrupt ID。

但是这32个中断采用了中断与寄存器分区抽像。

关于这个中断与寄存器分区,后面讲讲。

具体的中断映射,请参照cyclone v HPS手册。

PL390负责收集所有的中断信号,并对这些中断信号进行管理,包括中断行为,中断路由及安全扩展等。

具体如下:●ARM安全扩展,这部分内容需要了解ARM TRUSTZONE技术。

●使能,关闭及生成外围中断。

●生成软件中断。

●中断门限及优先级设置。

●多处理器环境中的路由。

PL330支持三种中断类型,PPI,SPI,SGI。

●PPI中断为CPU核私有中断,只连接到指定CPU核。

●SPI由PL330路由到相应的CPU核。

●SGI由软件编程PL330直接生成,用与核间通信。

PL390支持两中中断模型:●1:N:只让一个CPU核处理中断。

软件通过系统编程GIC实现中断路由,让指定CPU核处理该中断。

●N:N:每个处理器都会收到中断,它们独立处理这些中断。

这种方式在SGI上使用,用于CPU核间通信。

二、MPU GICPL390提供一个AMBA总线接口给SOC系统访问其内部寄存器,可以进行可寻址配置及访问,同时还可以提供最多8个CPU接口,也就是说可以最多为8个CPU提供中断服务。

整个GIC被分成两个部分,distributor(中断分配器)与多个CPU接口。

再看下面一张图。

这张图中,红色箭头直接穿过distributor,分配到FIQ与IRQ,这就是bypass模式,也称为旁路模式,这种模式下,所有中断被直接分配到了相应的CPU核。

Cyclone IV 器件中的存储器模块

4096 × 2

2048 × 4

1024 × 8

配置 ( 深度 × 宽度 )

1024 × 9

512 × 16

512 × 18

256 × 32

256 × 36

奇偶校验位

v

字节使能

v

Packed 模式

ห้องสมุดไป่ตู้

v

地址时钟使能

v

单端口模式

v

简单双端口模式

v

真双端口模式

v

嵌入式移位寄存器模式 ( 注释 1)

v

ROM 模式

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at /common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

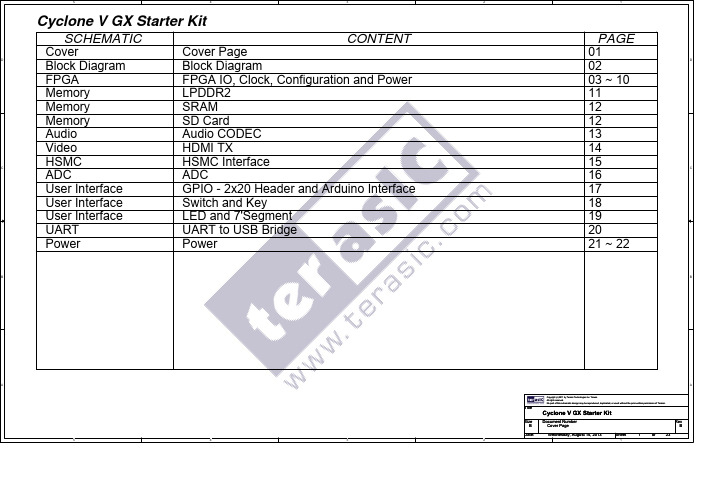

Cyclone V GX 开发板原理图 (5CGXFC5C6F27)

SRAMSD CardAudio CODECHDMI TXHSMC InterfaceADCGPIO - 2x20 Header and Arduino InterfaceSwitch and KeyLED and 7'SegmentUART to USB BridgePowerCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.All rights reserved.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.Title5432TitleSize Document Number Date:Copyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.Block DiagramCyclone V GX Starter KitB Friday, November 15, 2013SWITCH7-SEGMENTADC InterfaceDDR2LP_DQ7DDR2LP_DM0DDR2LP_DQ4DDR2LP_DQ5DDR2LP_DQ14DDR2LP_DQ15DDR2LP_CKE0DDR2LP_DM1DDR2LP_DQ12DDR2LP_DQ13DDR2LP_DQ11DDR2LP_CKE1DDR2LP_DQS_n1DDR2LP_DQS_p1DDR2LP_DQ8DDR2LP_DQ9GNDDDR2LP_DQ10DDR2LP_CA0DDR2LP_CA1SW[9..0]HEX0_D[6..0]HEX1_D[6..0]ADC_CONVST ADC_SCK ADC_SDO ADC_SDITitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.IO_4A/DIFFIO_RX_B30N/DQ4B/B_DQ_4Y13IO_4A/DIFFIO_RX_B30P/DQ4B/B_DQ_5W12IO_4A/DIFFIO_TX_B32N/DQ4B/B_DQ_7AF12IO_4A/DIFFIO_TX_B32P/DQ4B/B_DM_0AF11IO_4A/DIFFIO_TX_B33N/GND AC13IO_4A/DIFFIO_RX_B34N/DQ5B/B_DQ_8AC15IO_4A/DIFFIO_TX_B33P/DQ5B/B_DQ_10AC14IO_4A/DIFFIO_RX_B34P/DQ5B/B_DQ_9AB15IO_4A/DIFFIO_RX_B35N/DQSN5B/B_DQSN_1V14IO_4A/DIFFIO_TX_B36N/DQ5B/B_DQ_11AF13IO_4A/DIFFIO_RX_B35P/DQS5B/B_DQS_1U14IO_4A/DIFFIO_TX_B36P/B_CKE_1AE13IO_4A/DIFFIO_TX_B37N/DQ5B/B_CKE_0AF14IO_4A/DIFFIO_RX_B38N/DQ5B/B_DQ_12AB16IO_4A/DIFFIO_TX_B37P/DQ5B/B_DQ_14AE14IO_4A/DIFFIO_RX_B38P/DQ5B/B_DQ_13AA16IO_4A/DIFFIO_TX_B40N/DQ5B/B_DQ_15AF18IO_4A/DIFFIO_TX_B40P/DQ5B/B_DM_1AE18IO_4A/DIFFIO_RX_B46N/DQ6B/B_DQ_20IO_4A/DIFFIO_RX_B46P/DQ6B/B_DQ_21IO_4A/DIFFIO_TX_B48N/DQ6B/B_DQ_23IO_4A/DIFFIO_TX_B48P/DQ6B/B_DM_2IO_4A/DIFFIO_RX_B50N/DQ7B/B_DQ_24IO_4A/DIFFIO_TX_B49P/DQ7B/B_DQ_26IO_4A/DIFFIO_RX_B50P/DQ7B/B_DQ_25IO_4A/DIFFIO_RX_B51N/DQSN7B/B_DQSN_3IO_4A/DIFFIO_TX_B52N/DQ7B/B_DQ_27IO_4A/DIFFIO_RX_B51P/DQS7B/B_DQS_3IO_4A/DIFFIO_RX_B54N/DQ7B/B_DQ_28IO_4A/DIFFIO_TX_B53P/DQ7B/B_DQ_30IO_4A/DIFFIO_RX_B54P/DQ7B/B_DQ_29IO_4A/DIFFIO_TX_B56N/DQ7B/B_DQ_31IO_4A/DIFFIO_TX_B56P/DQ7B/B_DM_3IO_4A/DIFFIO_RX_B58N/DQ8B/B_DQ_32IO_4A/DIFFIO_TX_B57P/DQ8B/B_DQ_34IO_4A/DIFFIO_RX_B58P/DQ8B/B_DQ_33IO_4A/DIFFIO_RX_B59N/DQSN8B/B_DQSN_4IO_4A/DIFFIO_TX_B60N/DQ8B/B_DQ_35IO_4A/DIFFIO_RX_B59P/DQS8B/B_DQS_4IO_4A/DIFFIO_RX_B62N/DQ8B/B_DQ_36IO_4A/DIFFIO_TX_B61P/DQ8B/B_DQ_38IO_4A/DIFFIO_RX_B62P/DQ8B/B_DQ_37IO_4A/DIFFIO_TX_B64N/DQ8B/B_DQ_39IO_4A/DIFFIO_TX_B64P/DQ8B/B_DM_4IO_3B/DIFFIO_TX_B24N/DQ3B/B_CA_1AF6IO_3B/DIFFIO_TX_B24P/DQ3B/B_CA_0AE6SRAM_D0SRAM_D1SRAM_D2SRAM_D3SRAM_D4SRAM_D5SRAM_D6SRAM_D7SRAM_D8SRAM_D9SRAM_D10SRAM_D11SRAM_D12SRAM_D13SRAM_D14SRAM_D15HDMI_TX_VS HDMI_TX_HSHDMI_TX_D19HDMI_TX_D1HDMI_TX_D2HDMI_TX_D3HDMI_TX_D5HDMI_TX_D6HDMI_TX_D9HDMI_TX_D11HDMI_TX_D18HDMI_TX_D17HDMI_TX_D16HDMI_TX_D15HDMI_TX_D12HDMI_TX_D14TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NIO_6A/DIFFIO_TX_R34P/DQ5R E24IO_6A/DIFFIO_TX_R34N/DQ5R E25IO_6A/DIFFIO_RX_R35P/DQ5R K24IO_6A/DIFFIO_TX_R36P/DQ5R F24IO_6A/DIFFIO_RX_R35N/DQ5R K23IO_6A/DIFFIO_TX_R36N/DQ5R G24IO_6A/DIFFIO_RX_R37P/DQS5R L23IO_6A/DIFFIO_TX_R38PH23IO_6A/DIFFIO_RX_R37N/DQSN5R L24IO_6A/DIFFIO_TX_R38N/DQ5R H24IO_6A/DIFFIO_RX_R39P/DQ5R H22IO_6A/DIFFIO_TX_R40P/DQ5R F23IO_6A/DIFFIO_RX_R39N/DQ5R J23IO_6A/DIFFIO_TX_R40N G22IO_6A/DIFFIO_RX_R41P L22IO_6A/DIFFIO_RX_R41NK21IO_5B/DIFFIO_RX_R15P/DQ2R R24IO_5B/DIFFIO_TX_R16P/DQ2RU24IO_5B/DIFFIO_RX_R15N/DQ2R R25IO_5B/DIFFIO_TX_R16NV25IO_5B/DIFFIO_TX_R18P/DQ3R AB26IO_5B/DIFFIO_TX_R18N/DQ3R AA26IO_5B/DIFFIO_RX_R19P/DQ3R T26IO_5B/DIFFIO_RX_R19N/DQ3RR26IO_5B/DIFFIO_RX_R21P/DQS3R P21IO_5B/DIFFIO_TX_R22PW25IO_5B/DIFFIO_RX_R21N/DQSN3RP22IO_5B/DIFFIO_TX_R22N/DQ3R W26IO_5B/DIFFIO_RX_R23P/DQ3R N25IO_5B/DIFFIO_TX_R24P/DQ3RU25IO_5B/DIFFIO_RX_R23N/DQ3R P26IO_5B/DIFFIO_TX_R24NU26Audio CODECHSMC_D0HSMC_RX_n0HSMC_RX_p0HSMC_RX_n10HSMC_RX_p10HSMC_RX_p9HSMC_RX_n9HSMC_RX_p11HSMC_RX_n11HSMC_RX_n12HSMC_RX_p12HSMC_RX_p1HSMC_RX_n1HSMC_RX_n7HSMC_RX_p7HSMC_TX_n8HSMC_TX_p8HSMC_TX_p9HSMC_TX_n9HSMC_TX_p10HSMC_TX_n10HSMC_TX_p0HSMC_TX_n0HSMC_TX_p2HSMC_TX_n2HSMC_TX_n1HSMC_TX_p1HSMC_TX_n4HSMC_TX_p4HSMC_TX_n3HSMC_TX_p3HSMC_TX_n6HSMC_TX_p6AUD_XCK 13AUD_DACDAT 13AUD_ADCDAT 13AUD_DACLRCK 13AUD_ADCLRCK13AUD_BCLK 13TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NIO_7A/DIFFIO_TX_T6N/DQ1T/T_DQ_35IO_7A/DIFFIO_RX_T7P/DQ1T/T_DQ_33IO_7A/DIFFIO_TX_T8P/DQ1T/T_DQ_34IO_7A/DIFFIO_RX_T7N/DQ1T/T_DQ_32IO_7A/DIFFIO_TX_T10P/DQ2T/T_DM_3IO_7A/DIFFIO_TX_T10N/DQ2T/T_DQ_31IO_7A/DIFFIO_RX_T11P/DQ2T/T_DQ_29IO_7A/DIFFIO_TX_T12P/DQ2T/T_DQ_30IO_7A/DIFFIO_RX_T11N/DQ2T/T_DQ_28IO_7A/DIFFIO_RX_T13P/DQS2T/T_DQS_3IO_7A/DIFFIO_RX_T13N/DQSN2T/T_DQSN_3IO_7A/DIFFIO_TX_T14N/DQ2T/T_DQ_27IO_7A/DIFFIO_RX_T15P/DQ2T/T_DQ_25IO_7A/DIFFIO_TX_T16P/DQ2T/T_DQ_26IO_7A/DIFFIO_RX_T15N/DQ2T/T_DQ_24IO_7A/DIFFIO_TX_T22P/T_RESETN B15IO_7A/DIFFIO_TX_T22N/DQ3T/T_DQ_19C15IO_7A/DIFFIO_RX_T23P/DQ3T/T_DQ_17C14IO_7A/DIFFIO_TX_T24P/DQ3T/T_DQ_18A8IO_7A/DIFFIO_RX_T23N/DQ3T/T_DQ_16D15IO_7A/DIFFIO_TX_T24N/GNDA9IO_7A/DIFFIO_TX_T26P/DQ4T/T_DM_1C9IO_7A/DIFFIO_TX_T26N/DQ4T/T_DQ_15B9IO_7A/DIFFIO_RX_T27P/DQ4T/T_DQ_13E16IO_7A/DIFFIO_TX_T28P/DQ4T/T_DQ_14D10IO_7A/DIFFIO_RX_T27N/DQ4T/T_DQ_12D16IO_7A/DIFFIO_TX_T28N/DQ4T/T_CKE_0C10IO_7A/DIFFIO_RX_T29P/DQS4T/T_DQS_1N12IO_7A/DIFFIO_TX_T30P/T_CKE_1B10IO_7A/DIFFIO_RX_T29N/DQSN4T/T_DQSN_1M12IO_7A/DIFFIO_TX_T30N/DQ4T/T_DQ_11A11IO_7A/DIFFIO_RX_T31P/DQ4T/T_DQ_9F16IO_7A/DIFFIO_TX_T32P/DQ4T/T_DQ_10E10IO_7A/DIFFIO_RX_T31N/DQ4T/T_DQ_8E15IO_7A/DIFFIO_TX_T32N/GNDE11IO_7A/DIFFIO_TX_T34P/DQ5T/T_DM_0B12IO_7A/DIFFIO_TX_T34N/DQ5T/T_DQ_7A13IO_7A/DIFFIO_RX_T35P/DQ5T/T_DQ_5G12IO_7A/DIFFIO_TX_T36P/DQ5T/T_DQ_6A12IO_7A/DIFFIO_RX_T35N/DQ5T/T_DQ_4F12IO_7A/DIFFIO_TX_T36N/DQ5T/T_ODT_1B11IO_7A/DIFFIO_RX_T37P/DQS5T/T_DQS_0M11IO_7A/DIFFIO_TX_T38P/T_ODT_0C13IO_7A/DIFFIO_RX_T37N/DQSN5T/T_DQSN_0L11IO_7A/DIFFIO_TX_T38N/DQ5T/T_DQ_3C12IO_7A/DIFFIO_RX_T39P/DQ5T/T_DQ_1E13IO_7A/DIFFIO_TX_T40P/DQ5T/T_DQ_2D11IO_7A/DIFFIO_RX_T39N/DQ5T/T_DQ_0D13GXB L2 is C7 FPGA onlyHSMC_GXB_RX_p3HSMC_GXB_RX_n3HSMC_GXB_TX_p3HSMC_GXB_TX_n3SMA_GXB_TX_pSMA_GXB_RX_pREFCLK_p1REFCLK_n1SMA_GXB_RX_p SMA_GXB_RX_nSMA_GXB_TX_p SMA_GXB_TX_n TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.GXB_L1GXB_L25CGXFC5C6F27C7NREFCLK1LNP6REFCLK1LP N7GXB_TX_L5NK1GXB_TX_L5P K2GXB_RX_L5P,GXB_REFCLK_L5P M2GXB_RX_L5N,GXB_REFCLK_L5N M1GXB_TX_L4N P1GXB_TX_L4P P2GXB_RX_L4P,GXB_REFCLK_L4P T2GXB_RX_L4N,GXB_REFCLK_L4N T1GXB_TX_L3N W3GXB_TX_L3P W4GXB_RX_L3P,GXB_REFCLK_L3P V2GXB_RX_L3N,GXB_REFCLK_L3N V1RREF_TLB1GXB_RX_L8n,GXB_REFCLK_L8n D1GXB_RX_L8p,GXB_REFCLK_L8p D2GXB_RX_L7n,GXB_REFCLK_L7n F1GXB_RX_L7p,GXB_REFCLK_L7p F2GXB_RX_L6n,GXB_REFCLK_L6n H1GXB_RX_L6p,GXB_REFCLK_L6p H2GXB_TX_L6p G4GXB_TX_L6n G3GXB_TX_L7p E4GXB_TX_L7n E3GXB_TX_L8p C4GXB_TX_L8nC3REFCLK2Lp M6REFCLK2LnL5R1990R2042KJ12J7R1980C1360.01uVCCIO = 3.3VVCCIO = 3.3VVCCIO = 2.5VVCCIO = 2.5VHSMC_CLKIN_p1HSMC_CLKIN_n1CLOCK_50_B7A HSMC_CLKIN_n1HSMC_CLKIN_n2CLOCK_50_B5B CLOCK_50_B6A GPIO0GPIO2I2C_SDACLOCK_125_n GPIO8GPIO7GPIO6GPIO4CLOCK_50_B8A HSMC_CLKIN0HSMC_CLKIN_p2HSMC_CLKIN_n2VCC2P5VCC2P5VCC2P5VCC3P3VCC2P5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C2690.1u 10V C2680.1u 10VC1110.1u 10VR188100R197100R200100R11220KC2670.1u 10V Bank 5BBank 6ABank 7ABank 8A5CGXFC5C6F27C7NIO_5B/CLK7P,FPLL_BR_FBP/DIFFIO_RX_R9P T21IO_5B/CLK7N,FPLL_BR_FBN/DIFFIO_RX_R9NT22IO_5B/CLK6P/DIFFIO_RX_R17P R20IO_5B/CLK6N/DIFFIO_RX_R17NP20IO_5B/FPLL_BR_CLKOUT0,FPLL_BR_CLKOUTP,FPLL_BR_FB/DIFFIO_TX_R20P/DQ3RIO_5B/FPLL_BR_CLKOUT1,FPLL_BR_CLKOUTN/DIFFIO_TX_R20N/DQ3RIO_6A/CLK5P/DIFFIO_RX_R25P N20IO_6A/CLK5N/DIFFIO_RX_R25NM21IO_6A/FPLL_TR_CLKOUT0,FPLL_TR_CLKOUTP,FPLL_TR_FB/DIFFIO_TX_R28P/DQ4RIO_6A/FPLL_TR_CLKOUT1,FPLL_TR_CLKOUTN/DIFFIO_TX_R28N/DQ4RIO_6A/CLK4P,FPLL_TR_FBP/DIFFIO_RX_R33P K25IO_6A/CLK4N,FPLL_TR_FBN/DIFFIO_RX_R33NK26IO_7A/CLK11P/DIFFIO_RX_T25P G15IO_7A/CLK11N/DIFFIO_RX_T25NG14IO_7A/CLK10P/DIFFIO_RX_T33P H12IO_7A/CLK10N/DIFFIO_RX_T33N G11IO_8A/CLK9P/DIFFIO_RX_T41P N9IO_8A/CLK9N/DIFFIO_RX_T41NM10IO_8A/FPLL_TL_CLKOUT0,FPLL_TL_CLKOUTP,FPLL_TL_FB/DIFFIO_TX_T44P/DQ6T/T_CA_2IO_8A/FPLL_TL_CLKOUT1,FPLL_TL_CLKOUTN/DIFFIO_TX_T44N/DQ6T/T_CA_3IO_8A/CLK8P,FPLL_TL_FBP/DIFFIO_RX_T49P L8IO_8A/CLK8N,FPLL_TL_FBN/DIFFIO_RX_T49N K9U20MSEL Settings : MSEL[4:0] = 10010 Active serial (AS)(x1 and x4),no compression, no security, fast PORFPGAHSMCSD_DAT0SD_DAT1SD_DAT2SD_DAT3SD_CMD SD_CLK MSEL0MSEL1MSEL3MSEL2MSEL4BST_TDI BST_TDO JTAG_FPGA_TDI FPGA_CONF_DONE FPGA_nSTATUS FPGA_nCONFIGHSMC_JTAG_TDI HSMC_JTAG_TDO JTAG_FPGA_TDO FPGA_nCEGPIO34GPIO11GPIO23GPIO22GPIO21GPIO20GPIO19GPIO17GPIO15GPIO14GPIO13GPIO12GPIO31VCC3P3VCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R1730DNI R520R1770DNI RN2210K12345678Bank 9A5CGXFC5C6F27C7NIO_3A/DATA6/DIFFIO_RX_B1N/DQ1B T7IO_3A/DATA5/DIFFIO_TX_B2NU7IO_3A/DATA8/DIFFIO_RX_B1P/DQ1B T8IO_3A/DATA7/DIFFIO_TX_B2P/DQ1B V8IO_3A/DATA10/DIFFIO_RX_B3N/DQSN1B W8IO_3A/DATA9/DIFFIO_TX_B4N/DQ1BAB6IO_3A/DATA12/DIFFIO_RX_B3P/DQS1B Y9IO_3A/DATA11/DIFFIO_TX_B4PAA6IO_3A/DATA14/DIFFIO_RX_B5N/DQ1B R10IO_3A/DATA13/DIFFIO_TX_B6N/DQ1B AA7IO_3A/CLKUSR/DIFFIO_RX_B5P/DQ1B R9IO_3A/DATA15/DIFFIO_TX_B6P/DQ1B Y8IO_5A/PR_REQUEST/DIFFIO_TX_R1N/DQ1RAC23IO_5A/CVP_CONFDONE/DIFFIO_TX_R3N/DQ1RAA23IO_5A/nPERSTL1/DIFFIO_RX_R6N/DQSN1R U22MSEL0M7CONF_DONE A6MSEL1L6nSTATUS B5nCED5MSEL2A2MSEL3K5nCONFIG F5MSEL4J5IO_3A/PR_DONE/DIFFIO_RX_B7NR8IO_3A/PR_READY/DIFFIO_TX_B8N/DQ1BAD6IO_3A/PR_ERROR/DIFFIO_RX_B7P P8IO_3A/DIFFIO_TX_B8P/DQ1BAD7R530VCCAUX_VCCA_FPLLVCC2P5VCC3P3VREF_3P3_VCCIOTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NVCC VCC VCC VCC VCC VCCVCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCCPGM AA9VCCPGM W22VCCPGM F8VCCBATVCCPD5B R21VCCPD6A J22VCCPD6A L21VCCPD7A8AF19VCCPD7A8A F17VCCPD7A8A F13VCCPD7A8A F11VCCPD7A8A F9VCCA_FPLL W7VCCA_FPLL J6VCCA_FPLLY21VCCA_FPLL G21VCC_AUX G9VCC_AUX E14VCC_AUX G19VCC_AUXAB20VCC_AUX AB14VCC_AUX AA85CGXFC5C6F27C7NVCCIO4A U18VCCIO4A AE22VCCIO4A AA20VCCIO4A AD19VCCIO4A Y17VCCIO4A W14VCCIO4A AC16VCCIO4A AF15VCCIO4A AB13VCCIO4A AE12VCCIO5A V21VCCIO5A AB23VCCIO5B N26VCCIO5B T25VCCIO5B W24VCCIO5B R22VREFB4AN0AD15VREFB5AN0W23VREFB5BN0P25CYCLONE V GX XCVR PowerU14-122.5V2.5Vfor VCCIO_VCCPD 2.5Vfor VCCIO_VCCPD 3.3Vfor VCCIO 1.2VVCCH_GXBL VCCAUX_VCCA_FPLLVCC1P2VCC3P3VCC2P5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C2204.7n 50VC25522n 16VC1674.7u 6.3VC2510.01u 50VC1830.01u 50VC2320.47u 10VC1804.7n 50VC1782.2n 50VC1940.01u 50VC1701u 10VC1720.47u 10VC2504.7n 50VC1764.7u 6.3VC10510u 6.3VC2492.2n 50VC1910.01u 50VC1044.7u 6.3VC1820.1u 10VC2460.01u 50VC1900.1u 10VC25322n 16VC1851u 10VC2590.1u 10VC2130.01u 50VC25247n 25VNote:Place decoupling caps near LPDDR2 power pins place close to DDR2 chipDDR2LP_CKE0DDR2LP_CS_n0DDR2LP_DM0DDR2LP_DM1DDR2LP_DQ2DDR2LP_DQ3DDR2LP_DQ4DDR2LP_DQ5DDR2LP_DQ6DDR2LP_DQ7DDR2LP_DQ8DDR2LP_DQ9DDR2LP_DQ10DDR2LP_DQ11DDR2LP_DQ12DDR2LP_DQ13DDR2LP_DQ14DDR2LP_DQ15DDR2LP_DM3DDR2LP_DQ31DDR2LP_DQ24DDR2LP_DQ25DDR2LP_DQ26DDR2LP_DQ27DDR2LP_DQ28DDR2LP_DQ29DDR2LP_DQ30DDR2LP_DM2DDR2LP_DQ16DDR2LP_DQ17DDR2LP_DQ19DDR2LP_DQ18DDR2LP_DQ20DDR2LP_DQ22DDR2LP_DQ21DDR2LP_DQ23DDR2LP_ZQ0DDR2LP_ZQ1DDR2LP_CKE1DDR2LP_CS_n1DDR2LP_CK_nVCC1P2TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C1450.1u 10V240DNIC1580.1u 10VR169 4.7K R1684.7K DNIC15510u 10VDNU0A1DNU1A2NC0A3NC1A4NC2A5NC3A6NC4A7NC5A8NC6A9NC7A10DNU2A22DNU3A23DM2AB20DNU10AB22DNU8AB1DNU9AB2CS#0AB3CS#1AB4NC/ZQ AC11CKE0AC3CKE1AC4DNU4B1DNU5B2DM3B20DNU6B22DNU7B23NC8B4NC9B6NC10B7NC11B9NC12D1NC13D2NC14E1NC15E2NC16F1NC17G1NC18G2NC19H1NC20H2NC21J1NC22K1NC23K2NC24L1DM1L23DM0N23ZQ P1DQ30A13DQ29A14DQ26A16DQ25A17DQ16AB12DQ18AB14DQ20AB15DQ22AB17DQ17AC13DQ19AC14DQ21AC16DQ23AC17DQ31B12DQ28B14DQ27B15DQ24B17DQ15C22DQ14D23DQ12E22DQ13E23DQ11F22DQ10G23DQ8H22DQ9H23DQ6T22DQ7T23DQ5U22DQ4V23DQ2W22DQ3W23240C4010u 10VC14622n 16VMT42L128M32D1LF-25WTVSS A21VSS AA1VDD2AA2VDD2AB10VSS AB11VDD2AB21VSS AC21VSS AC5VSS/NC AC9VSS B10VDD2B21VSS/NC B5VSS/NC B8VSS C1VDD2C2VSS/NC F2VSS/NCJ2VDD2L22VSS M2VSS M23VSS R1VDD2R2VSSQ A12VSSQ A15VSSQ A18VDDQ AA22VDDQ AB13VDDQ AB16VDDQ AB19VSSCA AB7VSSQ AC12VSSQ AC15VSSQAC18VSSQ C23VDDQ D22VSSQ F23VDDQ G22VSSQ J23VDDQ K22VSSQ P23VDDQ R22VSSQ U23VSSCA V1VDDQ V22VSSQ Y23C1594.7u 6.3VC16222n 16VC1530.1u 10VSD_DAT1SD_DAT0SD_DAT3SD_DAT2SD_CMDSD_DAT2SD_DAT3SD_CMD SRAM_CE_n SRAM_OE_n SRAM_WE_n SRAM_LB_n SRAM_UB_nSRAM_D11SRAM_D12SRAM_D15SRAM_D13SRAM_D9SRAM_D10SRAM_D14SRAM_CE_nSRAM_A14SRAM_A16SRAM_A15SRAM_A17SRAM_A13VCC3P3_SDVCC3P3_SDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R185RN1010K 12345678L2130ohm, 3ASRAM 256Kx16nCE 6G N D 12nWE 17A1326A1427A1828D930D1031D1132G N D34D1235D1336D1437D1538nLB 39nUB40nOE 41A1542A1643A1744123J6c k e tDAT3CMD DAT2R11710KDefault :I2C Address 0x34/35AUD_XCKAUD_BCLKAUD_DACDAT AUD_DACLRCK AUD_ADCDATAUD_ADCLRCK I2C_SDA_3P3I2C_SCL_3P3AUD_MUTEAUD_CSBAUD_I2C_SDAT AUD_I2C_SCLK AGND AGNDVCC_AUDDVCC_AUDDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R18680R1502K DNIC22100u C13410u 6.3VU7SSM2603BCLK 7H P V D D 12XTO 2D C V D D 3MICBIAS21MICIN22RLINEIN 23LLINEIN24MUTE25CSB26SDIN27SCLK28ROUT 17A V D D18A G N D19VMID 20LOUT16P G N D 15RHPOUT 14LHPOUT13XTI/MCLK 1D G N D4RECLRC11RECDAT 10D B V D D5CLKOUT6PBDAT 8PBLRCK 9E P _G N D 29C1390.1u 10V DNIR2822R20330R3022R1512K DNIR174.7KC151u 10VDefault :I2C Address 0x72/0x73Pull-high to FPGA bank I/O powerNote:Place Capacitor near ADV7513 DVDD pinsHDMI_TX_CLK HDMI_TX_DE HDMI_TX_VS HDMI_TX_HS HDMI_HPD CEC_CLKHDMI_SPDIF HDMI_MCLK HDMI_I2S0HDMI_I2S1HDMI_I2S2HDMI_I2S3HDMI_SCLK HDMI_LRCLKHDMI_TX_D17HDMI_TX_D18HDMI_TX_D19HDMI_TX_D20HDMI_TX_D21HDMI_TX_D22HDMI_TX_D23CLK_12MHz VCC1P8VCC1P8_DVDDVCC1P8VCC1P8_AVDDVCC1P8_DVDDVCC1P8_PVDDVCC1P8_AVDDVCC3P3_DVDD VCC3P3_DVDDVCC1P8_AVDDVCC1P2VCC1P8_DVDDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C3510u 6.3VR15349.9DNI R12822DNIR1242K X312MHZDNIVCC 4OUT 3GND2EN1C1490.1u 10VL910uH74479887310AC1520.1u 10VC1380.1u 10VR129R1252K DNIC1290.1u 10VDNIC1300.1u 10VL410uHR80R138887ADV7513BSWZD1743D1842D1941D2040D2139D2238D2337CLK 53DE63HSYNC 64VSYNC 2R_EXT 14HPD 16SPDIF 3MCLK 4I2S05I2S16I2S27I2S38SCLK 9LRCLK 10PD22DVDD_3V 29DVDD11DVDD211DVDD331DVDD451PVDD 12BGVDD 13AVDD115AVDD219AVDD325EPAD_GND65R130R127TX_n TX_p RX_p RX_nDefaultJumper OpenHSMC_RX_p5HSMC_RX_n5HSMC_TX_p5HSMC_TX_n5HSMC_CLKIN_p1HSMC_CLKIN_n1NET_HSMC_GXB_TX_p0NET_HSMC_GXB_TX_n0HSMC_TX_n0HSMC_CLKOUT_n1HSMC_CLKOUT_p1HSMC_RX_p6HSMC_RX_n6HSMC_TX_n6HSMC_TX_p6HSMC_RX_n1HSMC_RX_p1HSMC_RX_p7HSMC_RX_n7HSMC_TX_p7HSMC_TX_n7HSMC_TX_p1HSMC_TX_n1HSMC_RX_p2HSMC_RX_n2HSMC_CLKOUT0HSMC_JTAG_TCKHSMC_CLKIN0HSMC_JTAG_TDI HSMC_JTAG_TMS HSMC_JTAG_TDO HSMC_D1HSMC_TX_p2HSMC_TX_n2HSMC_GXB_TX_p0HSMC_GXB_TX_n0HSMC_D2HSMC_RX_p3HSMC_RX_n3HSMC_RX_p0HSMC_GXB_RX_n0HSMC_GXB_RX_p0HSMC_RX_n0HSMC_TX_n3HSMC_TX_p3HSMC_D3HSMC_RX_n4HSMC_RX_p4HSMC_TX_p4HSMC_TX_n4HSMC_TX_p0HSMC_D0HSMC_SDAHSMC_SCLI2C_SDA I2C_SCLHSMC_SDA HSMC_SCLVCC12_HSMCVCC12_HSMCVCC3P3_HSMCVCC3P3_HSMCVCC12_HSMCVCC3P3VCC3P3_HSMCTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R460C12010u 35V C2650.1u 25VTP1Dummy PinC2660.1u 25V R18722R49JP13HEADER 212C11510u 6.3V C24822u 25V 116416816516616729293131333335353737393930303232343436363838404041414343454547474949515153535555575759596161636365656767696971717373757577777979818183838585878789899191939395959797999942424444464648485050525254545656585860606262646466666868707072727474767678788080828284848686888890909292949496969898100100161161162162163163164164R18622XJ1Jumper-2.54mmVREF ADC_IN1ADC_IN2ADC_IN3ADC_IN5ADC_IN6ADC_IN7ADC_IN0ADC_IN4ex_ADC_SDO ADC_VREFADC_REFCOMP ex_ADC_CONVST ex_ADC_SDIex_ADC_SCK TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C7810u 10V C800.1u 10VCH0CH1CH2CH3CH4CH5CH6CH7COMG N DG N D G N DG N DG N D G N DVREFREFCOMP SDISCKSDOCONVD V D DO V D DA V D D 1A V D D 1U17LTC2308CUF22232412345625910112018781516171412131921C1021n 50VC981n 50V C8210u 10VC991n 50V C1001n 50V TP13TP_YELLOWC790.1u 10VR8649.9C872.2u 10VC1011n 50V C840.1u 10VGPIO_D0GPIO_D2GPIO_D4GPIO_D6GPIO_D8GPIO_D1GPIO_D3GPIO_D5GPIO_D7GPIO_D9GPIO_D14GPIO_D12GPIO_D10GPIO_D18GPIO_D16GPIO_D22GPIO_D20GPIO_D24GPIO_D15GPIO_D13GPIO_D11GPIO_D19GPIO_D17GPIO_D23GPIO_D21GPIO_D25GPIO_D26GPIO_D28GPIO_D30GPIO_D32GPIO_D34GPIO_D33GPIO_D31GPIO_D29GPIO_D27GPIO_D35GPIO_D7GPIO_D11GPIO_D15GPIO_D19GPIO_D23GPIO_D27GPIO3GPIO20GPIO_D20Arduino_IO0CPU_RESET_n Arduino_Reset_nAnalog_In1Analog_In2Analog_In3Arduino_Reset_nAnalog_In0Arduino_AD4_IO14Arduino_AD5_IO15Analog_In6Analog_In7Arduino_IO11Arduino_IO12Arduino_IO13Arduino_Reset_nArduino_IO15Arduino_IO14GNDVCC5VCC12VCC3P3VCC3P3VCC5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.BAT54S D15BAT54S123JP14HEADER 2x3123456D38BAT54S123BAT54S D13BAT54S123R22222R2242.2K DNIRN418BAT54S BAT54S RN1118BAT54S D45BAT54S123BAT54S 3BAT54S R2252.2K DNID43BAT54S123JP9BOX Header 2X20M 12345678910111312141618202224262715171921232528293133353739303234363840Reserved 6x6mm tact switchSW1SW0SW2SW3BTN3BTN1BTN2BTN0VCC1P2VCC1P2TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.RN2318BUTTON1TACT SW DNI4321SW0SLIDE SW12345BUTTON3TACT SW DNI4321SW2SLIDE SW12345SW1SLIDE SW12345RN311RN2610K12345678BUTTON2TACT SW DNI4321RN2412012345678B2A2E1G0F0E0B1C1D1F1G1C0B0A0D0A1C2D2E2F2HEX0_D0HEX0_D1HEX0_D2HEX0_D3HEX0_D4HEX0_D5HEX0_D6HEX1_D0HEX1_D1HEX1_D3HEX1_D4HEX1_D2HEX1_D5HEX1_D6HEX2_D0HEX2_D1HEX2_D2HEX2_D3HEX2_D4HEX2_D5GPIO22GPIO23GPIO24GPIO25GPIO26GPIO27GPIO28GPIO30GPIO29HEX2_D0HEX3_D0HEX2_D1HEX3_D1HEX2_D2HEX2_D3HEX2_D4HEX2_D5HEX2_D6LEDR0LEDG1LEDG2LEDG3LEDG4LEDG5LEDG6LEDG7LEDR1LEDR2LEDR3LEDR4LEDR5LEDR6LEDR7VCC_HEX2VCC_HEXVCC_HEXVCC_HEX2VCC_HEXTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.e d dpc g b f a CA1CA2HEX07Segment Display12345610987ON1S2121615RN1868012345678e d c b f a CA1CA2HEX2124561098RN1668012345678RN1568012345678ON1S1SW DIP-812345678161514131211109RN1912345678e d dpc g b f a CA1CA2HEX17Segment Display12345610987R2010R20510kRN1768012345678Self Powered and Internal OSCUSB to UARTUART_CTSRX_LEDTX_LEDUART_RTSFT232_DP FT232_DM UART_RX UART_TX UART_RESET_nUART_RXLED UART_TXLED UART_CTS UART_RTSUART_CTSUART_RTSUART_PW_ENVCC5_UARTVCC3P3_UARTVCC5_UARTVCC5_USB_UARTVCCIO_UART VCC2P5VCC5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.DNITP_YELLOWU4FT232R VCC19VCCIO 1G N D 4RESET 183V3OUT16USBDP 14USBDM15TXD 30RXD 2CTS#8RTS#32DSR#6DTR#31DCD#7RI#3CBUS022NC15A G N D 24NC212NC313NC525NC629NC423OSCI 27OSCO 28G N D 17G N D 20TEST26CBUS121CBUS311CBUS210CBUS49E P _G N D33R71M R14310kC140.1u 25VTPD2E001DRLRU2VCC 1NC2IO13GND4IO25D9LEDR21R220DNIC314.7u 6.3VL24321R142 4.7K C60.1u 25VR23R15733C330.1u 25VC80.1u 25V DNITP_YELLOWD8LEDG21R15633C254.7u 6.3VC270.1u 25VL2230ohm, 3A10kC184.7u 6.3VRamp TimeTsoft-start = 0.99 msec3.3V / 5AVCC1P1_PGOOD VCC3P3_PGOOD VCC3P3_INTVCCVCC3P3_INTVCCVCC12VCC1P1_INTVCCVCC3P3_INTVCCTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.LTC3605EUF#PBFITH 6CLKIN24S G N D22P G N D 110E P _P G N D 225SW616FB4RT 1CLKOUT23R66316K R6910KC623.3n 50VR471050VU11PHMODE 2MODE 3TRACK/SS 5P V I N 117P V I N 218BOOST20PGOOD8SW111SW212SW313SW414SW515SW616RUN 7VON 9SVIN19I N T V C C21C4822u 25V C570.1u 25VD12CMDSH-3C17339p 50V 12.4K DNIC721n 50VR182100K+C656.3V330u 1239p 50V DNIR1940DNIPOWER SWC5022u 25VXJ3Jumper-2.54mmC58 2.2u 6.3VC7168p 50V2.5VTantalum330u 2L121uH 744311100R6715KR18411.5K DNIC510.1u 25VRamp Time = 1.2 msecVCC3P3VCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R109200KC561u 10VC532.2u 10VLT3080-1U10OUT11OUT22OUT33SET 4IN28IN17NC6V_CONTROL 5OUT49DNIC494.7n 50VC521u 10VR44180KC5422u 6.3VC1124.7n 50V6.3VXJ6Jumper-2.54mmGND13URXFOSC_24BST_TMS URD UTXE UWR URXFSI_WU UD7EEPDATA EEPCSEEPCLK USB_RESETnBST_TDI BST_TDO ISP_TCK ISP_TMS ISP_TDI ISP_TDOUSB_RESETn TRGNST TRGNCSO TRGASDO TRGDCLK TRGNCE TRGTDO TRGTMSTRGOE TRGOEFPGA_nCEUART_RESET_nPWRONPWRON BST_TCK VCC5_USBVCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.FT245BLLQFP-32TEST31RXF#12EEDATA 2XTIN 27XTOUT 28G N D17D718RD#16WR 15TXE#14A G N D 29EECS 32EESK 1RESET#4SI/WU 11PWREN#10USBDM 8G N D 9R14110KR2070DNIR13310KR1480DNIC14347p 50VBAT54SDW 123R13027EPM240M100C4N IO-B1-10G1IO-B1-11G2IO-B1-12F3IO-B1-13H1IO-B1-14H3IO-B1-15H2IO-B1-16L1IO-B1-17L2IO-B1-18K3IO-B1-19L3IO-B1-20K4IO-B1-21L4IO-B1-22K5IO-B1-23L5IO-B1-24L6IO-B1-25K6IO-B1-26J6IO-B1-27L7IO-B1-28K7IO-B1-29/DEV_OE L8IO-B1-30/DEV_CLRn K8IO-B1-31L9IO-B1-32K9IO-B1-33L10IO-B1-34K10IO-B1-35L11IO-B1-8/GCLK1E1IO-B1-9F1TCK K1TDI J2TDO K2TMS J1G N D I N TG 4G N D I N T E 8IO-B1-36J5IO-B1-37J7R14422。

Cyclone IV Device Datasheet(cyiv-53001)

1

© July 2010

Altera Corporation

Cyclone IV Device Handbook, Volume 3

1–2

Chapter 1: Cyclone IV Device Datasheet Operating Conditions

Absolute Maximum Ratings

1. Cyclone IV Device Datasheet

CYIV-53001-1.3

This chapter describes the electrical and switching characteristics for Cyclone IV devices. Electrical characteristics include operating conditions and power consumption. Switching characteristics include transceiver specifications, core, and periphery performance. This chapter also describes I/O timing, including programmable I/O element (IOE) delay and programmable output buffer delay. This chapter includes the following sections:

Cyclone IV Device Handbook, Volume 3

© July 2010 Altera Corporation

Chapter 1: Cyclone IV Device Datasheet Operating Conditions

恒星IV(Cyclone IV)产品文档指南说明书

Cyclone® IV Featured Documentation - Quick Links GuideOnline Version Send Feedback 7678452023.07.27Contents ContentsCyclone® IV Featured Documentation - Quick Links (3)IV Featured Documentation - Quick Links Guide Send FeedbackCyclone®2Cyclone ® IV Featured Documentation - Quick LinksThis page provides links to some of the key Cyclone ® IV documentation, organized by focused subject areas.Featured Documents Design guidelinesDevice overview Datasheet Errata sheetCyclone IV Device Handbook Cyclone IV FPGAs Family Overview Product Table Package and Thermal specifications Device pin-outs Pin connection guidelinesSee All Cyclone IV Resources and DocumentationDevice Handbook Sections1.Volume 1 - Cyclone IV Device Handbook•Section I. Device Core—Chapter 1. Cyclone IV FPGA Device Family Overview —Chapter 2. Logic Elements and Logic Array Blocks in Cyclone IV Devices —Chapter 3. Memory Blocks in Cyclone IV Devices —Chapter 4. Embedded Multipliers in Cyclone IV Devices —Chapter 5. Clock Networks and PLLs in Cyclone IV Devices •Section II. I/O Interfaces —Chapter 6. I/O Features in Cyclone IV Devices —Chapter 7. External Memory Interfaces in Cyclone IV Devices •Section III. System Integration—Chapter 8. Configuration and Remote System Upgrades in Cyclone IV Devices —Chapter 9. SEU Mitigation in Cyclone IV Devices —Chapter 10. JTAG Boundary-Scan Testing for Cyclone IV Devices —Chapter 11. Power Requirements for Cyclone IV Devices 2.Volume 2 - Cyclone IV Device Handbook •Section I. Transceivers—Chapter 1. Cyclone IV Transceivers Architecture —Chapter 2. Cyclone IV Reset Control and Power Down —Chapter 3. Cyclone IV Dynamic Reconfiguration3.Volume 3 - Cyclone IV Device Handbook767845 | 2023.07.27Send FeedbackIntel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.*Other names and brands may be claimed as the property of others.ISO 9001:2015Registered•Section I. Device Datasheet—Chapter 1. Cyclone IV Device Datasheet —Cyclone IV I/O timing spreadsheetPower and Thermal Management•PowerPlay Early Power Estimator User Guide •Cyclone IV and Cyclone V PowerPlay Early Power Estimator •Device-Specific Power Delivery Network (PDN) Tool 2.0 User Guide •Power Delivery Network (PDN) Tool 2.0 for Stratix V , Arria V , Arria II GZ, Cyclone V , and Cyclone IV DevicesExternal Memory Interfaces•External Memory Interfaces in Cyclone IV DevicesDesign Guidelines•AN 592: Cyclone IV Design Guidelines •Cyclone IV Device Family Pin Connection GuidelinesDevelopment Kits•Cyclone IV GX Transceiver Starter Board Reference Manual •Cyclone IV GX FPGA Development Board Reference Manual •Cyclone IV GX FPGA Development Kit User Guide •Cyclone IV GX Transceiver Starter Kit User Guide •USB-Blaster Download Cable User Guide •Cyclone IV BoardsSoftware Documentation•Intel Quartus Prime Standard Edition User Guides - Combined PDFIP Documentation•ALTLVDS IP Core User Guide •ALTPLL IP Core User Guide •Clock Control Block (ALTCLKCTRL) IP Core User Guide •PCI Express* Compiler User Guide •Phase-Locked Loop Reconfiguration (ALTPLL_RECONFIG) IP Core User Guide •RAM Megafunction User Guide •Remote Update Intel FPGA IP User Guide •SCFIFO and DCFIFO IP Cores User Guide •All Cyclone IV Related IP DocumentationCyclone ® IV Featured Documentation - Quick Links767845 | 2023.07.27Cyclone ®IV Featured Documentation - Quick Links GuideSend Feedback4Application Notes•A Flexible Solution for Industrial Ethernet •AN 425: Using the Command-Line Jam STAPL Solution for Device Programming •AN 717: Nios II Gen2 Hardware Development Tutorial •Designing Basestation Channel Cards with FPGAs •Driving Innovative Industrial Solutions •Enabling Low-Power EO/IR System Development with FPGAs and Image- and Sensor-Processing IP •Lowering the Total Cost of Ownership for Industrial Applications •All Cyclone IV Related Application NotesCyclone ® IV Featured Documentation - Quick Links767845 | 2023.07.27Send Feedback Cyclone ® IV Featured Documentation - Quick Links Guide5。

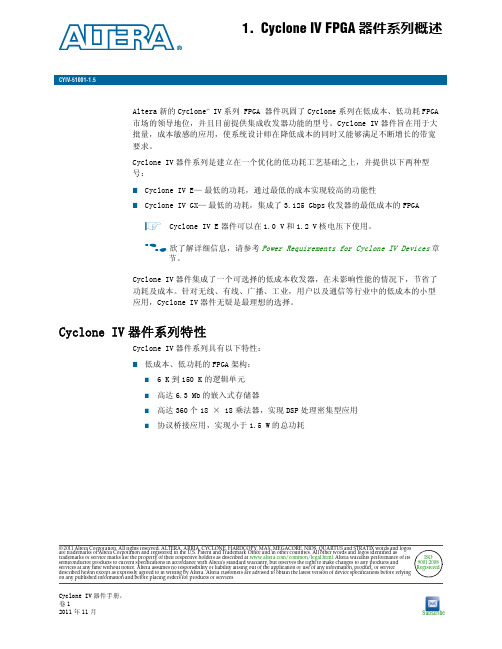

Cyclone IV FPGA 器件系列概述

30

高速收发器 ( 注释 6)

2

4

4

4

8

8

8

8

收发器最大数据速率 (Gbps)

2.5

2.5

2.5

3.125

3.125

3.125

3.125

3.125

PCIe(PIPE) 硬核 IP 模 块

1

1

1

1

1

1

1

1

用户 I/O 块

9

9

9

11

11

11

11

11

( 注释 7) ( 注释 7) ( 注释 7) ( 注释 8) ( 注释 8) ( 注释 8) ( 注释 8) ( 注释 8)

? 1?:Cyclone IV FPGA 器件系列概述

封装矩阵

Altera 公司 2011 年 11 月

封装矩阵

表 1-3 列出了 Cyclone IV E 器件封装产品。

表 1-3. Cyclone IV E 器件系列的封装产品 ( 注释 1)

封装

E144

M164

尺寸 ( 毫米 )

22 × 22

资源

逻辑单元 (LE)

6,272 10,320 15,408 22,320 28,848 39,600 55,856 75,408 114,480

嵌入式存储器 (Kbits)

270

414

504

594

594 1,134 2,340 2,745 3,888

嵌入式 18 × 18 乘法器 15

23

56

66

ISO 9001:2008 Registered

Cyclone IV 器件手册, 卷1 2011 年 11 月

EP3C25Q240C8N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

手术

—

1.15 1.2 1.25

V

—

3.135 3.3 3.465 V

电源电压为输出缓冲器,3.0-V

手术

—

2.85

3

3.15

V

VCCIO (3), (4)

电源电压为输出缓冲器,2.5-V

手术

电源电压为输出缓冲器,1.8-V

手术

电源电压为输出缓冲器,1.5-V

手术

—

2.375 2.5 2.625 V

(4)所有输入缓冲器由在V驱动

供电.

(5)50-200毫秒之间POR时间标准POR范围.每个单独电源应达到在推荐工作范围 50毫秒.

3-9毫秒(6)POR时间,快速POR范围.每个单独电源应在3毫秒达到推荐工作范围内.

芯片中文手册,看全文,戳

第 1章: Cyclone III器件数据表

表1-2 列出所允许最大输入电压过冲和 过冲电压作为在装置寿命百分比持续时间. 允许最大过冲持续时间被指定为高时间比设备寿命百分比.

Max

Unit

1.8

V

3.9

V

3.75

V

1.8

V

3.95

V

40

mA

±2000

V

±500

V

150

°C

125

°C

表1-2 and

芯片中文手册,看全文,戳

芯片中文手册,看全文,戳

July 2012 CIII52001-3.5

CIII52001-3.5

1.Cyclone III器件数据表

本章介绍电气特性,开关特性,以及I / O

对Cyclone时机

Altera Cyclone芯片分析

摘要Cyclone系列芯片是Altera公司推出的新一代低成本、中等规模的FPGA,其价格仅为Altera现有主流器件的30%~50%。

它通过去掉DSP块,MegaRAM,降低LVDS接口速率等指标后,可适应大多数设计的要求,同时分担用户所面临的成本压力。

本论文的开头部分详细介绍了Cyclone系列芯片的体系结构。

该芯片采用0.13μm,全铜SRAM工艺,1.5v内核,同时还拥有2910个逻辑单元到20060个逻辑单元以及59904位RAM到294912位RAM,这使得它可用于实现多种复杂的功能。

此外,该芯片还提供了用于时钟管理的锁相环和用于连接工业标准外部存储器的专用I/O接口;而且,多种IP核及Altera发布的Nios嵌入式微处理器软核均能在其上实现。

之后,论文对Cyclone系列芯片的配置方法进行了探讨,并着重介绍了低成本的串行配置方案。

接着,论文对此次毕业设计中用到的主要开发工具进行了简要介绍,其中包括Protel 99SE和Quartus II软件。

最后,我们具体实现了一个基于Cyclone FPGA的电子时钟的设计。

可编程器件方面,我们选用的是240管脚PQFP封装的EP1C12器件;配置时则是采用主动串行配置方案下的EPCS1器件。

在此,论文主要讲解了板卡的组成、内部设计及仿真,其中内部实现包括:原理图、PCB图的绘制和VHDL程序的编写。

关键词:Cyclone,逻辑阵列块,逻辑单元,互连,锁相环,I/O元素,串行配置器件,Quartus IIABSTRACTAltera®Cyclone™FPGAs—the lowest-cost FPGAs ever—are half the cost of competing devices. Cyclone FPGAs are the optimal solution for high-volume, price-sensitive applications that previously required the use of fixed solutions such as gate arrays and standard cells.At the beginning of the dissertation, we describes the Cyclone architecture in detail. Cyclone FPGAs are built on a cost-optimized, all-copper 1.5-V SRAM process. With up to 20,060 logic elements (LEs) and 288 Kbits of RAM, Cyclone FPGAs can integrate many complex functions. Cyclone FPGAs offer multiple full-featured phase-locked loops (PLLs) to manage board-level clock networks and dedicated I/O interfaces for interfacing with industry standard external memory devices. Altera's Nios® embedded processor and a full intellectual property (IP) portfolio is available for development with Cyclone FPGAs.Then we discuss the configuration schemes of the Cyclone devices,especially the low-cost active serial configuration scheme.After that, we talk about the tools which we used in this graduation design. These tools contain Potel 99SE and Quartus II .Lastly, we use the EP1C12 device in the 240-pin PQFP package and the EPCS1 device which is used to configure EP1C12 in the active serial configuration scheme to implement an electronic clock. In this part, the thesis mainly explains the composition, internal design (including drawing schematic diagram, drawing PCB diagram and programming in VHDL) and simulation of the board.KEY WORDS: Cyclone, LAB, LE, Interconnect, PLL, IOE, Serial Configuration Device, Quartus II目录第一章绪论 (1)1.1.可编程逻辑与ASIC简介 (1)1.2.课题来源及意义 (1)1.3.作者所做工作 (2)1.4.论文结构安排 (2)第二章Cyclone系列芯片的结构分析 (3)2.1.概述 (3)2.1.1.Cyclone主要特性 (3)2.1.2.功能描述 (4)2.2.逻辑阵列块(LAB) (5)2.2.1. LAB互连 (6)B控制信号 (6)2.2.3.逻辑单元(LE) (7)2.2.4.LUT链和寄存器链 (8)2.2.5.addnsub信号 (8)2.2.6.LE的操作模式 (8)2.2.7.进位选择链 (9)2.2.8.清零/重置逻辑控制 (9)2.3.多通道互连(MultiTrack Interconnect) (9)2.4.嵌入式存储器 (10)2.4.1.存储模式 (11)2.4.2.支持奇偶校验位 (11)2.4.3.支持移位寄存器 (12)2.4.4.存储器的配置大小 (12)2.4.5.字节使能 (13)2.4.6.独立时钟模式 (13)2.4.7.输入/输出时钟模式 (13)2.4.8.读/写时钟模式 (13)2.4.9.单端口模式: (14)2.5.全局时钟网络和锁相环 (14)2.5.1.全局时钟网络 (14)2.5.2.双效时钟管脚 (15)2.5.4.锁相环(PLLs) (15)2.6.I/O结构 (16)第三章Cyclone系列芯片的主动串行配置方法 (19)3.1.Cyclone系列芯片主要配置方法简介 (19)3.2.串行配置的实现 (20)3.2.1.配置多个层叠状态的器件 (21)3.2.2.对串行配置器件进行编程 (22)3.2.3.串行配置器件的管脚描述 (22)第四章Protel 99SE及Quartus II软件简介 (23)4.1.Protel电子电路设计软件 (23)4.2.Quartus II开发工具 (24)4.2.1.Quartus II概述 (24)4.2.2.Quartus II的功能 (24)第五章基于Cyclone系列芯片的简单应用 (27)5.1.板卡的组成及结构图 (27)5.2.板卡的逻辑设计 (29)5.2.1.七段显示器模块的逻辑设计 (29)5.2.2.电子时钟时间计数模块的逻辑设计 (32)5.2.4.弹跳消除电路模块的逻辑设计 (34)5.2.3.电子时钟时间设定及其时间显示模块的逻辑设计 (36)附录一消除弹跳电路及微分电路组合模块的程序代码 (41)附录二自由计数器模块及状态转换模块的程序模块 (43)结束语 (45)致谢 (46)参考文献 (47)第一章绪论1.1.可编程逻辑与ASIC简介可编程逻辑器件(PLD)是由用户编程实现所需要逻辑功能的数字集成电路。

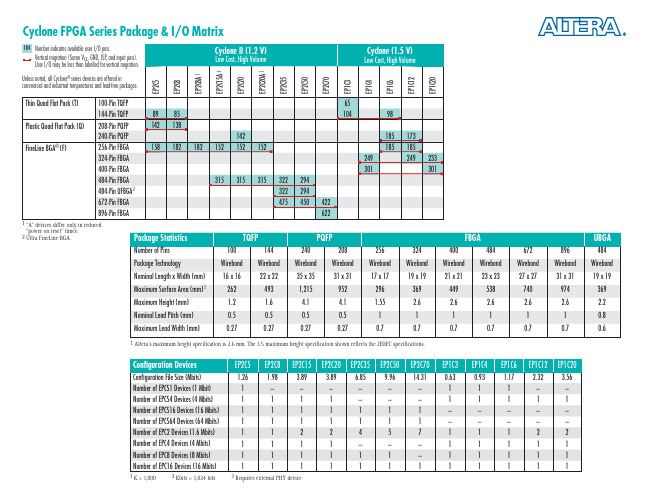

Cyclone系列FPGA选型表

TQFP

100 Wirebond 16 x 16 262 1.2 0.5 0.27 144 Wirebond 22 x 22 493 1.6 0.5 0.27 240

PQFP

208 Wirebond 31 x 31 952 4.1 0.5 0.27 256 Wirebond 17 x 17 296 1.55 1 0.7 324 Wirebond 19 x 19 369 2.6 1 0.7 400 Wirebond 21 x 21 449 2.6 1 0.7 Wirebond 35 x 35 1,215 4.1 0.5 0.27

1 K = 1,00 2 Kbits = 1,024 bits 3 Requires external PHY device

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. This document is subject to change without notice. July 2006

Volume 1 :Chapter 5. Cyclone V器件中的IO特性

相关链接 Cyclone V器件手册: 已知问题 列出了计划更新的 Cyclone V器件手册章节。

Cyclone V器件中每个封装的I/O资源

以下不同的Cyclone V器件系列中的封装计划表列出了每个封装中可用的最大化I/O资源。

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at /common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Volume1:Chapter6.CycloneV器件中的外部存储器接口

6Cyclone V 器件中的外部存储器接口Cyclone ®V 器件提供了一种高效的体系结构,能够适配广泛的外部存储器接口以支持小模块化I/O bank 结构中的高水平系统带宽。

I/O 被设计用于对现有的和新兴的外部存储器标准提供高性能的支持。

表6-1:Cyclone V 器件中所支持的外部存储器标准软核储存控制器硬核储存控制器存储器标准半速率全速率DDR3SDRAM 半速率全速率DDR2SDRAM 半速率全速率LPDDR2SDRAM相关链接•外部存储器接口指标估算器要估算外部存储器系统性能的指标,请使用外部存储器接口指标估算器。

•外部存储器接口手册提供了有关所支持的存储器类型、电路板设计指南、时序分析、仿真和调试的详细信息。

•Cyclone V 器件手册:已知问题列出了对Cyclone V 器件手册章节所规划的更新。

外部存储器性能表6-2:Cyclone V 器件中的外部存储器接口性能最大和最小的操作频率取决于存储器接口标准以及器件数据表中所列出的支持的延迟锁相环(DLL)频率。

最小频率(MHz)最大频率(MHz)电压(V)接口软核控制器硬核控制器3003004001.5DDR3SDRAM3003004001.35ISO 9001:2008Registered©2013Altera Corporation.All rights reserved.ALTERA,ARRIA,CYCLONE,HARDCOPY,MAX,MEGACORE,NIOS,QUARTUS and STRATIX wordsand logos are trademarks of Altera Corporation and registered in the U.S.Patent and Trademark Office and in other countries.All other words and logos identified as trademarks or service marks are the property of their respective holders as described at /common/legal.html .Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty,but reserves the right to make changes to any products and services at any time without notice.Altera assumes no responsibility or liability arising out of the application or use of any information,product,or service described herein except as expressly agreed to in writing by Altera.Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products orservices.1673004001.8DDR2SDRAM 1673003331.2LPDDR2SDRAM相关链接Cyclone V 器件手册HPS 外部存储器性能表6-3:HPS 外部存储器接口性能硬核处理器系统(HPS)仅适用于Cyclone V SoC FPGA 器件。

cyclone4简介

Cyclone IV 器件手册, 卷1

Altera 公司 2011 年 11 月

第 1 章 :Cyclone IV FPGA 器件系列概述

1–3

器件资源

■ 高达 532 个用户 I/O ■ 高达 840 Mbps 发送器 (Tx), 875 Mbps Rx 的 LVDS 接口 ■ 支持高达 200 MHz 的 DDR2 SDRAM 接口 ■ 支持高达 167 MHz 的 QDRII SRAM 和 DDR SDRAM

? 1?:Cyclone IV FPGA 器件系列概述

封装矩阵

Altera 公司 2011 年 11 月

封装矩阵

表 1-3 列出了 Cyclone IV E 器件封装产品。

表 1-3. Cyclone IV E 器件系列的封装产品 ( 注释 1)

封装

E144

M164

尺寸 ( 毫米 )

22 × 22

最大用户 I/O ( 注释 9)

72

150

150

290

310

310

475

475

表 1-2 注释:

(1) 应用于 F169 和 F324 封装。

(2) 应用于 F484 封装。

(3) 仅有两个多用途 PLL 可应用于 F484 封装。 (4) 其中两个通用 PLL 可以支持收发器时钟。欲了解详细信息,请参阅 Clock Networks and PLLs in Cyclone IV Devices

ISO 9001:2008 Registered

Cyclone IV 器件手册, 卷1 2011 年 11 月

Subscribe

1–2

第 1 章 :Cyclone IV FPGA 器件系列概述

EP1C12Q240I7N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

400-Pin FineLine

BGA

1.0 441 21 × 21

1–3

初稿

芯片中文手册,看全文,戳

第一节气旋FPGA

系列数据表

修订记录

本节为设计师提供数据表规格

Cyclone器件.该章节包含内部功能定义 架构,配置和JTAG边界扫描测试信息, DC操作条件下,AC时序参数,一提到功耗和订购信息Cyclone器件.

本节包含以下章节:

■ 简介 ■ 旋风架构

配置与测试直流和开

表4-19.

对于EP1C3定稿定时信息和

EP1C12器件.更新时间信息

inTables 4–25 通过 4–26 and 表4-30

通过 4–51.

更新PLL规范

表4-52.

更新时间信息.时间最终确定 EP1C6和EP1C20器件.更新 性能信息.添加 部分.

"PLL时序"

添加文件到Cyclone器件手册.

运行条件 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1 能量消耗 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8 时序模型. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

× 36位) (1)

注意 表 1-1: (1) 该参数包括全局时钟引脚.

EP1C3 2,910

13 59,904

1 104

EP1C4 4,000

低成本低功耗CycloneIVFPGA

【】 晓 明 , 岩 . 线 传 感 器 网络 研 究现 状 与 应 用 【. 京 工 3杜 陈 无 J北 】

商 大 学 学报 ,0 8 2 ( ) l4 . 2 0 ,6 1 :4 - 3 【】 自力 . 4邝 无线 传 感 器 网络 及 其 应 用[ . 代 电 子 技 术 ,06 J现 】 20

( 2 :0 3 . 2 ) 3 - 3

医 疗研 究 、 理 领 域 也 大展 身 手 。 主 要 的 应 用 包 括 远 程 健康 护 管理 、 症 病 人 或 老 龄 人 看 护 、 活 支 持 设 备 、 理 数 据 实 时 重 生 病

研究和 应用前景 。 参 考 文献 :

4 W S 的 应 用领 域 N

1 军 事应 用 ) WS 具 有 可 快 速 部 署 、 自组 织 、 蔽 性 N 可 隐 强 和 高 容 错 性 的 特 点 , 因 此 非 常 适 合 在 军 事 上 应 用 。 利 用

WS 能 够 实 现 对 敌 军 兵 力 和 装 备 的 监 控 、 场 的 实 时 监 视 、 N 战

统 中的 应 用【. 计 算 机 信 息 ,0 6 9 2 )15 16 J微 】 20 ,(5 :7 - 7 .

低 成 本 低 功 耗 Cy ln P c e I F GA o V

A ea 司 ( L R) 开始 批 量 发 售 C co eI P A。公 司还 宣布 开始 提 供 基 于 C c n V G 的 收 发 器 入 门开 发 套 件 。 hr公 A T y ln F G V y l eI X o

Cyclone FPGA系列简介

Cyclone FPGA系列简介Altera®Cyclone™ FPGA是目前市场上性价比最优且价格最低的FPGA(1)。

Cyclone器件具有为大批量价格敏感应用优化的功能集,这些应用市场包括消费类、工业类、汽车业、计算机和通信类。

Cyclone器件现正在发售中。

器件基于成本优化的全铜1.5V SRAM工艺,容量从2910至20060个逻辑单元,具有多达294912bit嵌入RAM,见表1。

Cyclone FPGA支持各种单端I/O标准如LVTTL、LVCMOS、PCI和SSTL-2/3,通过LVDS和RSDS标准提供多达129个通道的差分I/O支持。

每个LVDS通道高达640Mbps。

Cyclone器件具有双数据速率(DDR) SDRAM和FCRAM接口的专用电路。

Cyclone FPGA中有两个锁相环(PLLs)提供六个输出和层次时钟结构,以及复杂设计的时钟管理电路。

这些业界最高效架构特性的组合使得FPGA系列成为ASIC最灵活和最合算的替代方案。

注释:1. Cyclone FPGA是现今成本最低和经成品认证的FPGA。

表1归纳了Cyclone FPGA系列产品、性能及供货情况注释:2. 有关这些器件供货的详细情况,请和当地Altera销售代表处联系。

表2是Cyclone器件封装和I/O管脚数注释:3. TQFP = 薄四方扁平封装4. PQFP = 四方扁平封装5. BGA = 球栅阵列表3是Cyclone开发包和供货情况。

表4是合适Cyclone器件的配置器件。

联系AlteraAltera只通过销售代表处和分销商销售可编程逻辑器件(PLD)。

如您需要购买Altera产品,请与我们的销售代表处和分销商联系。

Cyclone IV 器件中的SEU 缓解

Altera 公司 2010 年 2 月 Cyclone IV 器件手册, 卷 1

9–4

第 9 章 : Cyclone IV 器件中的 SEU 缓解

Cyclone IV 器件中的错误检测电路使用 32 bit CRC IEEE 802 标准和一个 32 bit 多项 式作为 CRC 发生器。因此,器件只执行一个 32 bit CRC 计算。如果没有出现软错误, 则产生的 32 bit 签名值为 0x00000000, 这将在 CRC_ERROR 输出信号上产生一个 0。如 果在器件中出现软错误,则产生的签名值是一个非零值,并且 CRC_ERROR 输出信号为 1。

错误检测模块

f Altera®网站上的Cyclone IV Devices Pin-Outs对Cyclone IV器件的CRC_ERROR管脚信 息作了详细的报告。

1 WYSIWYG(所见即所得)是一种优化技术,在Quartus II软件中对VQM (Verilog Quartus 映射 ) 网表进行优化。

表 9-1 说明了 CHANGE_EDREG JTAG 指令。

表 9-1. CHANGE_EDREG JTAG Instruction

JTAG 指令 CHANGE_EDREG

指令代码 00 0001 0101

说明

该指令连接 TDI 与 TDO 之间的 32 bit CRC 存储寄存器。所有预计算出的 CRC 值均加载 到 CRC 存储寄存器,以测试 CRC_ERROR 管脚上的错误检测 CRC 电路的操作。

这种错误检测功能会根据器件内容不断计算已配置 CRAM 位的 CRC 值,并且与配置最后 所得到的预计算出的 CRC 值进行比较。如果 CRC 值匹配,则在当前配置 CRAM 位中没有 错误。错误检测过程继续,直到器件被重置 ( 将 nCONFIG 设置为低电平 )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3.135 2.85 2.375 1.71 1.425 1.283 1.19 1.14 3.135 2.85 2.375 1.71 2.375 1.2

3.3 3.0 2.5 1.8 1.5 1.35 1.25 1.2 3.3 3.0 2.5 1.8 2.5 —

3.465 3.15 2.625 1.89 1.575 1.418 1.31 1.26 3.465 3.15 2.625 1.89 2.625 3.0

V V V V V V V V V V V V V V

PLL 模拟电压调节器电源 电池后备电源 (对于设计安全易失性密钥寄存器) DC 输入电压 输出电压 操作结温

— —

VI VO TJ

— — 商业 工业 汽车

–0.5 0 0 –40 –40

— — — — —

3.6 VCCIO 85 100 125

© 2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent

Cyclone V 器件数据表 反馈

Altera 公司

CV-51002 2015.06.12

建议的操作条件

5

符号

说明

条件

最小值 (2)

典型

最大值(2)

单位

3.3 V 3.0 V 2.5 V VCCIO I/O 缓冲电源 1.8 V 1.5 V 1.35 V 1.25 V 1.2 V 3.3 V VCCPGM 配置管脚电源 3.0 V 2.5 V 1.8 V VCCA_FPLL (5) VCCBAT

V V V V V V V V V V V V V V V V V mA °C °C

(1)

VCC_AUX_SHARED 必须与 Cyclone V SX C5、C6、D5 和 D6 器件以及 Cyclone V SE A5 和 A6 器件的 VCC_AUX 的相同源供电。

Cyclone V 器件数据表 反馈

ISO 9001:2008 Registered

101 Innovation Drive, San Jose, CA 95134

2

绝对最大额定值

CV-51002 2015.06.12

表 1: Cyclone V 器件的绝对最大额定值

符号 说明 最小值 最大值 单位

VCC VCCPGM VCC_AUX VCCBAT VCCPD VCCIO VCCA_FPLL VCCH_GXB VCCE_GXB VCCL_GXB VI VCC_HPS VCCPD_HPS VCCIO_HPS VCCRSTCLK_HPS VCCPLL_HPS VCC_AUX_SHARED (1) IOUT TJ TSTG

V V °C °C °C

(2) (5) (6)

电源值介绍了 DC(静态)电源容限的预算,并不包括动态容限要求。有关动态容限要求的额外预算,请参考 PDN 工具。 PLL 数字电压由 VCCA_FPLL 监管。 如果不使用 Cyclone V 器件中的设计安全功能,则需要将 VCCBAT 连接到 1.5-V、2.5-V 或 3.0-V 电源。 Cyclone V 上电复位(POR)电路监测 VCCBAT。如果 VCCBAT 没有上电,那么 Cyclone V 器件不会退出 POR。

(2) (7)

(8) (9)

(10)

电源值介绍了 DC(静态)电源容限的预算,并不包括动态容限要求。有关动态容限要求的额外预算,请参考 PDN 工具。 这也适用于 HPS 电源。对于 HPS 电源,当 HPS_PORSEL = 0 时,有关标准 POR 的信息,请参考 tRAMP 规范;当 HPS_PORSEL = 1 时,有关快 速 POR 的信息,当请参考 tRAMP 规范。 电源值介绍了 DC(静态)电源容限的预算,并不包括动态容限要求。有关动态容限要求的额外预算,请参考 PDN 工具。 对于要求完全符合 PCIe Gen2 发送器抖动规范的 Cyclone V GT 和 ST FPGA 系统,Altera 建议将 VCCE_GXBL 和 VCCL_GXBL 的典型值从 1.1 V 增加至 1.2 V。有关这一条件下 Cyclone V GT 和 ST 器件所建议的最大全双工通道的更多信息,请参考 Cyclone V 器件的收发器协议配置 章节。 对于完全符合 CPRI 发送器抖动规范,4.9152 Gbps ( Cyclone V GT 和 ST 器件)以及 6.144Gbps(仅 Cyclone V GT 和 ST 器件),Altera 建议将 VCCE_GXBL 和 VCCL_GXBL 的典型值从 1.1 V 增加至 1.2 V。有关 Cyclone V GT 和 ST 器件的 CPRI 6.144 Gbps 所建议的最大全双工通道的更多 信息,请参考 Cyclone V 器件的收发器协议配置章节。

内核电压和外围电路电源 配置管脚电源 辅助电源 设计安全易失的密钥寄存器的电池后备电源 I/O 预驱动器电源 I/O 电源 锁相环(PLL)模拟电源 收发器高电压电源 收发器电源 收发器时钟网络电源 DC 输入电压 HPS 内核电压和外围电路电源 HPS I/O 预驱动器电源 HPS I/O 电源 HPS 复位和时钟输入管脚电源 HPS PLL 模拟电源 HPS 辅助电源 每个管脚的 DC 输出电流 操作结温 存储温度 (无偏差)

2.625 1.13/1.23 1.13/1.23

V V V

• PCIe 支持的配置和布局指南 提供有关 Cyclone V GT 和 ST 器件(要求完全符合 PCIe Gen2 发送器抖动规范)所建议的最大化全双工通道的更多信息。 • Cyclone V GT 器件中的 6.144-Gbps 支持功能 提供有关 Cyclone V GT 和 ST 器件所建议的 CPRI 6.144 Gbps 的最大化全双工通道的更多信息。

Altera 公司

Cyclone V 器件数据表 反馈

6

收发器电源操作条件

CV-51002 2015.06.12

符号

说明

条件

最小值 (2)

典型

最大值(2)

单位

tRAMP (7)

电源斜坡时间

标准 POR 快速 POR

200µs 200µs

— —

100ms 4ms

— —

收发器电源操作条件 表 4: Cyclone V GX、GT、SX 和 ST 器件的收发器电源操作条件

Altera 公司

CV-51002 2015.06.12

所允许的最大过冲和下冲电压

3

所允许的最大过冲和下冲电压

在跳变过程中,输入信号可能会过冲下表列出的电压,对输入电流小于 100 mA 和周期少于 20 ns 下冲至–2.0 V。 允许的最大过冲的持续时间被指定为器件寿命的高时钟百分比。一个 DC 信号等于 100%占空比。 例如:过冲至 4.00 V 的信号仅能在 4.00 V 的器件寿命的~15%;如果器件寿命为 10 年,则是 1.5 年。 表 2: Cyclone V 器件跳变过程所允许的最大允许 该表列出了允许的最大输入过冲电压以及过冲电压的持续时间,以器件寿命的百分比表示。

1.07 1.12 2.375 3.135 2.85 2.375

1.1 1.15 2.5 3.3 3.0 2.5

1.13 1.18 2.625 3.465 3.15 2.625

V V V 态)电源容限的预算,并不包括动态容限要求。有关动态容限要求的额外预算,请参考 PDN 工具。 SEU 内部刷新功能适用于部件编号含有"SC"后缀的 Cyclone V E、GX、SE 和 SX 器件。有关器件的可用性和订购信息,请联系当地的 Altera 销售代表。 当 VCCIO 为 2.5、1.8、1.5、1.35、1.25 或 1.2 V 时,VCCPD 必须是 2.5 V。当 VCCIO 为 3.0 V 时,VCCPD 必须是 3.0 V。当 VCCIO 为 3.3 V 时,VCCPD 必须是 3.3 V。

绝对最大额定值

这一部分定义了 Cyclone V 器件的最大操作条件。该值是基于与所述器件进行的实验以及故障和损伤机理的理论模型而定的。 器件的功能性操作没有隐含这些条件。 警告: 下表中列出的范围以外的条件可能导致器件永久性损坏。此外,若器件长时间在绝对最大定额值运行,则可能会对器件产生不良 影响。

符号 说明 条件 (V) 高时间%的过冲持续时间 单位

3.8 3.85 3.9 3.95 4 4.05 4.1 4.15 Vi (AC) AC 输入电压 4.2 4.25 4.3 4.35 4.4 4.45 4.5 4.55 4.6

100 68 45 28 15 13 11 9 8 7 5.4 3.2 1.9 1.1 0.6 0.4 0.2

符号 说明 条件 最小值 (2) 典型 最大值(2) 单位

VCC VCC_AUX VCCPD (4)

内核电压、外围电路电源、收发器物 理编码子层(PCS)电源和收发器 PCI Express® (PCIe®)硬核 IP 数字电源 辅助电源 I/O 预驱动器电源

没有内部刷新功能的 器件 含有内部刷新功能的 器件(含有 SC 后缀) (3) — 3.3 V 3.0 V 2.5 V

2015.06.12

Cyclone V 器件数据表

订阅 反馈

CV-51002

该数据表描述了 Cyclone® V 器件的电气特性、开关特性、配置规格和 I/O 时序。 Cyclone V 器件支持商业与工业等级。商业器件支持–C6 (最快速度)、–C7 和–C8 的速度等级。工业等级器件支持–I7 速度等级。汽 车器件支持–A7 速度等级。