AT89C52单片机头文件

基于AT89c52单片机电子万年历设计(带程序)

目录一、摘要··2二、设计··3三、设计任务. ·2四、设计要求··3五、系统方案设计··31、系统··31)原理构成框图··32)设计思路··42、主程序设计··43、中断程序设计··55、时间调整电路的设计··7六、系统评价··7七、c语言程序注释及说明··8一、摘要单片机就是微控制器,是面向应用对象设计、突出控制功能的芯片。

单片机接上晶振、复位电路和相应的接口电路,装载软件后就可以构成单片机应用系统。

将它嵌入到形形色色的应用系统中,就构成了众多产品、设备的智能化核心。

本设计是基于AVR单片机强大的控制功能制作而成的电子万年历,该电子万年历包括四大功能:实时显示年、月、日、时、分、秒、星期;人为的校正年、月、日、时、分、星期;第一次开机显示12-00-30。

二、设计目的1、掌握C52程序用于实践并实现相应的功能;2、掌握时钟程序的使用方法;3、掌握时间函数的使用方法;4、掌握键盘的程序使用方法;三、设计任务通过与单片机连接数码管动态显示年、月、日、时、分、秒、星期等功能,并能准确计算闰年闰月的显示,七个按钮连接P0口可以精确调整每一个时间数值,通过对所设计的万年历时钟电路进行实验测试,达到了动态显示时间,随时调整时间等技术指标。

四、设计要求(1)能够准确的计时,时间可在数码管上显示出来,默认显示为时、分、秒,每隔一分钟自动显示年、月、日及星期,也可通过按键控制显示,并可通过按键调节时间。

(2)第一次开机显示12-30-30。

(3)每半秒led彩灯闪烁一次五、系统方案设计:1、系统总体设计:1) 原理构成框图本设计用AT89C52作为核心控制部分,外接晶振电路与复位电路,以两个四位数码管作为显示部分,开关控制显示时间与日期,具体框图如图1所示,数码管框图如图2所示:图1 原理框图图2:数码管模块2)设计思路通过一段时间对专业书籍及多种设计方案的研究分析,我采用了比较常用的AT89C52作为核心控制芯片,用C语言进行编程来满足设计的要求。

单片机课程设计报告ADC转换生成正弦波形

单片机课程设计报告题目:ADC转换生成正弦波形专业:测控技术与仪器班级:姓名:学号:指导教师:2015年1 月14 日目录第1章系统设计方案第2章系统硬件设计2.1 主控制器电路2.2 模数转换电路2.3 显示电路第3章系统软件设计3.1 系统整体流程3.2 直流电压采集3.3 交流电压采集第4章系统调试4.1 xxx的调试4.2 xxx的调试。

第5章结论与总结5.1 结论5.2 总结第1章系统设计方案使用STC89c52单片机与ADC0804芯片实现A/D转换直流电压采集,转换之后在LCD1602上显示所采集的直流电压值。

使用STC89c52单片机与ADC0804芯片实现A/D转换交流电压采集,转换之后在KS0108上显示交流电压动态波形。

第2章系统硬件设计2.1 主控制器电路(1)AT89C52单片机(2)晶振电路(3)复位电路2.2 模数转换电路2.3 显示电路(1)LCD1602显示电路(2)KS0108显示电路第3章系统软件设计3.1系统整体流程图3.2直流电压采集程序(1)直流电压采集主程序#include<reg52.h>#include"adc0804.h"#include"lcd1602.h"#define uchar unsigned char #define uint unsigned int #define ulong unsigned longvoid datds();void display();uchar dat=0;uchar a[]="the value is "; uchar b[]={0,0};void main(){uchar i=0;init();for(i=0;i<13;i++){comd(0x80+i);write(a[i]);}while(1){datc();dat=datw();datds();display();}}void datds(){b[0]=dat*5/255;b[1]=dat*50/255%10;}void display(){comd(0xc4);write(b[0]+0x30);comd(0xc5);write('.');comd(0xc6);write(b[1]+0x30);comd(0xc7);write('V');}(2)头文件lcd1602.h#include<reg52.h>#define uchar unsigned char #define uint unsigned int #define ulong unsigned longvoid write(uchar datee); void comd(uchar com);void init();sbit en=P3^4;sbit rs=P3^5;void init(){en=0;comd(0x38);comd(0x0c);comd(0x06);comd(0x01);}void comd(uchar com){rs=0;delay(50);P0=com;delay(50);en=1;delay(50);en=0;delay(50);}void write(uchar datee){rs=1;delay(50);P0=datee;delay(50);en=1;delay(50);en=0;delay(50);}(3)头文件adc0804.h#include<reg52.h>#define uchar unsigned char#define uint unsigned int#define ulong unsigned longchar datw();void datc();void datd();void delay(uint t);sbit rd=P3^1;sbit wr=P3^2;sbit intr=P3^3;sbit cs=P3^0;void datc() //写命令{cs=0;wr=1;delay(200);wr=0;delay(200);wr=1;while(intr);cs=1;}char datw() //读数据{uchar j=0;cs=0;rd=1;delay(200);rd=0;delay(200);j=P1;rd=1;cs=1;return j;}void delay(uint t){while(t--);}3.3交流电压采集程序(1)交流电压采集主程序#include<reg52.h>#include"adc0804.h"#include"lcd.h"#define uchar unsigned char #define uint unsigned int #define ulong unsigned longvoid datedis();void display();void qing(uchar q2);void qingp();sbit cs1=P0^1;sbit cs2=P0^2;uchar dat=0;uchar i;uchar j,da;void main(){init();while(1){ cs1=0;cs2=1;qingp();display();cs2=0;cs1=1;qingp();display();}}void qing(uchar q2){uchar q1;for(q1=0;q1<8;q1++){comd(184+q1);comd(0x40+q2);write(0);}}void qingp(){uchar q1,q2;for(q1=0;q1<8;q1++){comd(184+q1);comd(0x40);for(q2=0;q2<64;q2++)write(0);}}void display(){uchar x=0;for(x=0;x<64;x++){//qing(x);datc();dat=datw();datedis();comd(i);comd(64+x);write(j);}}void datedis(){ uchar j0=1;da=dat/4;i=184+da/8;j=j0<<(da%8);}(2)头文件lcd.h#include<reg52.h>#define uchar unsigned char #define uint unsigned int #define ulong unsigned longvoid write(uchar datee); void comd(uchar com);void init();sbit en=P3^6;sbit rs=P3^7;void init(){en=0;comd(4);comd(0x3f);}void comd(uchar com){rs=0;delay(50);P2=com;delay(50);en=1;delay(50);en=0;delay(50);}void write(uchar datee) {rs=1;delay(50);P2=datee;delay(50);en=1;delay(50);delay(50);}(3)头文件ADC0804.h#include<reg52.h>#define uchar unsigned char#define uint unsigned int#define ulong unsigned longchar datw();void datc();void datd();void delay(uint t);sbit rd=P3^1;sbit wr=P3^2;sbit intr=P3^3;sbit cs=P3^0;void datc() //写命令{cs=0;wr=1;delay(200);wr=0;delay(200);wr=1;while(intr);cs=1;}char datw() //读数据{uchar j1=0;cs=0;rd=1;delay(200);rd=0;delay(200);j1=P1;cs=1;return (j1);}void delay(uint t) {while(t--);}第4章系统调试4.1 直流电压采集的调试程序调试采用proteus仿真软件调试采集电压LCD显示结果4.2交流电压采集的调试第5章结论与总结5.1 结论(1)直流电压采集调试中,采集电压为5V的50%(即2.5V),而LCD1602显示值为 2.4V,误差很小,说明实验硬件和软件都很成功,可以成功实现直流电压采集并显示电压值的功能。

89C52引脚图

3.1 单片机芯片AT89C52介绍3.1.1 AT89C52功能介绍3.1.2 AT89C52芯片图(如图2)及引脚介绍(1)引脚功能电源引脚——VCC正常运行和编程校验时为5V电源,VSS为接地端。

I/O总线——P0.0-P0.7(P0口),P1.0-P1.7(P1口),P2.0-P2.7(P2口),P3.0-P3.7(P3口)若图片无法显示请联系站长QQ3710167为输入/输出引线。

时钟——XTAL1:片内振荡器反相放大器的输入端。

XTAL2:片内振荡器反相器的输出端,也是内部时钟发生器的输入端。

控制总线——ALE/PROG:地址锁存允许/编程信号线。

当CPU访问外部存储器时,ALE 用来锁存P0输出的地址信号的低8位。

它的频率为振荡频率的1/6。

在对8751编程时,此引脚输入编程脉冲信号。

PSEN:外接程序存储器读选通信号。

EA/VPP:访问内部程序存储器的控制信号。

当EA=1时,CPU从片内ROM读取指令;EA=0时,CPU从片外ROM读取指令。

此外,当对8751内部EPROM编程时,21V 编程电源由此端输入。

RST/VPD:复位输入信号。

当该引脚上出现2个机器周期以上的高电平时,可实现复位操作。

此引脚为掉电保护后备电源之输入引脚。

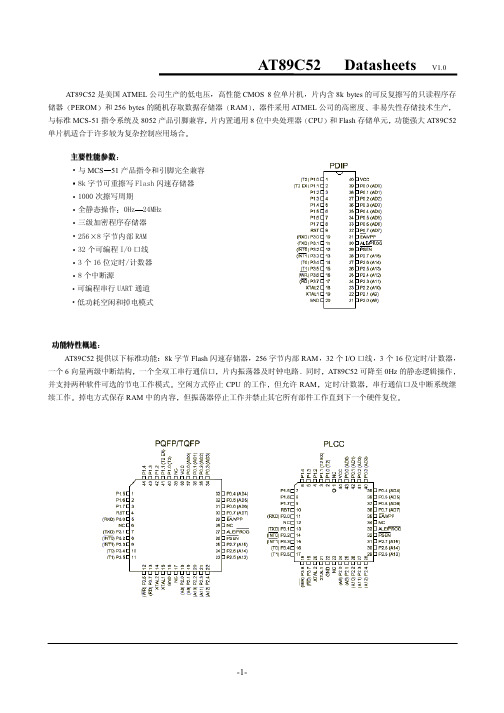

AT89C52是一个低电压,高性能CMOS 8位单片机,片内含8k bytes的可反复擦写的Flash 只读程序存储器和256 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器和Flash存储单元,功能强大的AT89C52单片机可为您提供许多较复杂系统控制应用场合。

AT89C52有40个引脚,32个外部双向输入/输出(I/O)端口,同时内含2个外中断口,3个16位可编程定时计数器,2个全双工串行通信口,2个读写口线,AT89C52可以按照常规方法进行编程,但不可以在线编程(S系列的才支持在线编程)。

AT89X52头文件

/*--------------------------------------------------------------------------AT89X52.HHeader file for the low voltage Flash Atmel AT89C52 and AT89LV52. Copyright (c) 1988-2002 Keil Elektronik GmbH and Keil Software, Inc. All rights reserved.--------------------------------------------------------------------------*/#ifndef __AT89X52_H__#define __AT89X52_H__/*------------------------------------------------Byte Registers------------------------------------------------*/sfr P0 = 0x80;sfr SP = 0x81;sfr DPL = 0x82;sfr DPH = 0x83;sfr PCON = 0x87;sfr TCON = 0x88;sfr TMOD = 0x89;sfr TL0 = 0x8A;sfr TL1 = 0x8B;sfr TH0 = 0x8C;sfr TH1 = 0x8D;sfr P1 = 0x90;sfr SCON = 0x98;sfr SBUF = 0x99;sfr P2 = 0xA0;sfr IE = 0xA8;sfr P3 = 0xB0;sfr IP = 0xB8;sfr T2CON = 0xC8;sfr T2MOD = 0xC9;sfr RCAP2L = 0xCA;sfr RCAP2H = 0xCB;sfr TL2 = 0xCC;sfr TH2 = 0xCD;sfr PSW = 0xD0;sfr ACC = 0xE0;sfr B = 0xF0;/*------------------------------------------------P0 Bit Registers------------------------------------------------*/sbit P0_0 = 0x80;sbit P0_1 = 0x81;sbit P0_2 = 0x82;sbit P0_3 = 0x83;sbit P0_4 = 0x84;sbit P0_5 = 0x85;sbit P0_6 = 0x86;sbit P0_7 = 0x87;/*------------------------------------------------PCON Bit Values------------------------------------------------*/#define IDL_ 0x01#define STOP_ 0x02#define PD_ 0x02 /* Alternate definition */#define GF0_ 0x04#define GF1_ 0x08#define SMOD_ 0x80/*------------------------------------------------TCON Bit Registers------------------------------------------------*/sbit IT0 = 0x88;sbit IE0 = 0x89;sbit IT1 = 0x8A;sbit IE1 = 0x8B;sbit TR0 = 0x8C;sbit TF0 = 0x8D;sbit TR1 = 0x8E;sbit TF1 = 0x8F;/*------------------------------------------------TMOD Bit Values------------------------------------------------*/#define T0_M0_ 0x01#define T0_M1_ 0x02#define T0_CT_ 0x04#define T0_GATE_ 0x08#define T1_M0_ 0x10#define T1_M1_ 0x20#define T1_CT_ 0x40#define T1_GATE_ 0x80#define T1_MASK_ 0xF0#define T0_MASK_ 0x0F/*------------------------------------------------P1 Bit Registers------------------------------------------------*/sbit P1_0 = 0x90;sbit P1_1 = 0x91;sbit P1_2 = 0x92;sbit P1_3 = 0x93;sbit P1_4 = 0x94;sbit P1_5 = 0x95;sbit P1_6 = 0x96;sbit P1_7 = 0x97;sbit T2 = 0x90; /* External input to Timer/Counter 2, clock out */ sbit T2EX = 0x91; /* Timer/Counter 2 capture/reload trigger & dir ctl *//*------------------------------------------------SCON Bit Registers------------------------------------------------*/sbit RI = 0x98;sbit TI = 0x99;sbit RB8 = 0x9A;sbit TB8 = 0x9B;sbit REN = 0x9C;sbit SM2 = 0x9D;sbit SM1 = 0x9E;sbit SM0 = 0x9F;/*------------------------------------------------P2 Bit Registers------------------------------------------------*/sbit P2_0 = 0xA0;sbit P2_1 = 0xA1;sbit P2_2 = 0xA2;sbit P2_3 = 0xA3;sbit P2_4 = 0xA4;sbit P2_5 = 0xA5;sbit P2_6 = 0xA6;sbit P2_7 = 0xA7;/*------------------------------------------------IE Bit Registers------------------------------------------------*/sbit EX0 = 0xA8; /* 1=Enable External interrupt 0 */sbit ET0 = 0xA9; /* 1=Enable Timer 0 interrupt */sbit EX1 = 0xAA; /* 1=Enable External interrupt 1 */sbit ET1 = 0xAB; /* 1=Enable Timer 1 interrupt */sbit ES = 0xAC; /* 1=Enable Serial port interrupt */sbit ET2 = 0xAD; /* 1=Enable Timer 2 interrupt */sbit EA = 0xAF; /* 0=Disable all interrupts *//*------------------------------------------------P3 Bit Registers (Mnemonics & Ports)------------------------------------------------*/sbit P3_0 = 0xB0;sbit P3_1 = 0xB1;sbit P3_2 = 0xB2;sbit P3_3 = 0xB3;sbit P3_4 = 0xB4;sbit P3_5 = 0xB5;sbit P3_6 = 0xB6;sbit P3_7 = 0xB7;sbit RXD = 0xB0; /* Serial data input */sbit TXD = 0xB1; /* Serial data output */sbit INT0 = 0xB2; /* External interrupt 0 */sbit INT1 = 0xB3; /* External interrupt 1 */sbit T0 = 0xB4; /* Timer 0 external input */sbit T1 = 0xB5; /* Timer 1 external input */sbit WR = 0xB6; /* External data memory write strobe */ sbit RD = 0xB7; /* External data memory read strobe *//*------------------------------------------------IP Bit Registers------------------------------------------------*/sbit PX0 = 0xB8;sbit PT0 = 0xB9;sbit PX1 = 0xBA;sbit PT1 = 0xBB;sbit PS = 0xBC;sbit PT2 = 0xBD;/*------------------------------------------------T2CON Bit Registers------------------------------------------------*/sbit CP_RL2= 0xC8; /* 0=Reload, 1=Capture select */sbit C_T2 = 0xC9; /* 0=Timer, 1=Counter */sbit TR2 = 0xCA; /* 0=Stop timer, 1=Start timer */sbit EXEN2= 0xCB; /* Timer 2 external enable */sbit TCLK = 0xCC; /* 0=Serial clock uses Timer 1 overflow, 1=Timer 2 */ sbit RCLK = 0xCD; /* 0=Serial clock uses Timer 1 overflow, 1=Timer 2 */ sbit EXF2 = 0xCE; /* Timer 2 external flag */sbit TF2 = 0xCF; /* Timer 2 overflow flag *//*------------------------------------------------T2MOD Bit Values------------------------------------------------*/#define DCEN_ 0x01 /* 1=Timer 2 can be configured as up/down counter */ #define T2OE_ 0x02 /* Timer 2 output enable *//*------------------------------------------------PSW Bit Registers------------------------------------------------*/sbit P = 0xD0;sbit F1 = 0xD1;sbit OV = 0xD2;sbit RS0 = 0xD3;sbit RS1 = 0xD4;sbit F0 = 0xD5;sbit AC = 0xD6;sbit CY = 0xD7;/*------------------------------------------------Interrupt Vectors:Interrupt Address = (Number * 8) + 3------------------------------------------------*/#define IE0_VECTOR 0 /* 0x03 External Interrupt 0 */#define TF0_VECTOR 1 /* 0x0B Timer 0 */#define IE1_VECTOR 2 /* 0x13 External Interrupt 1 */#define TF1_VECTOR 3 /* 0x1B Timer 1 */#define SIO_VECTOR 4 /* 0x23 Serial port */#define TF2_VECTOR 5 /* 0x2B Timer 2 */#define EX2_VECTOR 5 /* 0x2B External Interrupt 2 */#endif。

AT89C52单片机资料手册

! " #$% &'( )*+,- ./ 012 34567 89:;< =>( ?@AB ! C D EF GHIJKLM NOPQ(RHD S TUVWXY12D Z[ \] Z[ ^ _ ! `a _ bc !d$ e_ fghi?jkle_mnopq>r`st 7cu v wc xy "# z{|}~ h & [ o o J bc !d$ pq>r`7?j56 o ? < st o ^&o Ye_ &$0 834!9: m;<§¨¨¨mz{~ ¨¬®¯°¬±i²)®³´·®· ¸ pq DÀ !9:D ÁÂÃÄÄ ¼ÅÆÇÈɨ`ɨ` eÊ ËÌÍvÎnf¹º»` ÏÐÈÑ!$%Òa (` MÓÔ`(cÕ Ö× Ø ÙÚ _ |}Û vÜÝ`ɨ §c M ÞßÓàÝ(áâãä^$% å cæÊ`açcèéÈÑ !$%Òa (áâã«êëì ^íî Þá ¸ c `ï×34Z[ðá ñòcÓÔ34Z[ñòc óäïíî Þ` e_ô ^íî Þ nf ! ` ÓÔõöi ÙÚÖ×åÓÔ Ø$_ |}Û vÜÝ` >÷ ^ íî ÞøÝ`î ùúc Óà` Óà`û(cüM ^ áíîÞý_9:þä^rÿî c ÓÔe_ Ø% &0 w A ' ! ' ç Mbc!d$ ä^d$Óà ' ! !Óà ' ! (¸ ! ñò«ê ï× ÈÑ` e_ô ^íî Þ nf ! ` ÓÔõöi ÙÚÖ×åÓÔ Ø$_ |}Û vÜÝ` >÷ ^ íî ÞøÝ`î ùúc Óà` Óà`û(cüM ^ áíî Þý_9:þä^rÿî c ÓÔe_ Ø% &áâãä^ å ÈÑ ä^$% q )( *+ 34c ` Ô ÈÑ$ %áâã ÈÑ ä^$% q )( * 34c `ÓÔ < ¸ åñòc ï× ÈÑ!e OPrÿ` ` eÊô ^íî Þ nf ! ` `ÓÔõöi ÙÚÖ×åÓÔ Ø$_ |}Û vÜ ` à c þ ^íî Þî MÓàÝ`úcþä^î ` (íî ÞÓÔ Ø¹É·` Me ¹º»`aä ¡ ( D Yúä ` ï×e (I \] ¸ ! ñò OPrÿÓà st o c 9:Ô h_ ª«Xí ù ûâãä^ å$% c ÈÑ JÓÔ ö(I ÈÑ Z[e Y Xcust ! ÓÔ!b örÿüú ÜäÓÔcuå(Ibc" #$ Õ âãä^$% c %÷e_ öÜ¢£¤¥¦ ¸ «ê&9: (IÓภöɵ»Å' >÷ÜS(D ) *¢µ+? ,¬ C Ǩ = ¶-,~ & = . e/°»Ã0!°»Ã1342 ¶-,ëìúä&9: þ34î qä^ c Q5=¶-, 67J ,ÓÔ ä^ >rÿ 8ä^ #34å$ %cÕ_ ª«h© , 7ÐÓÔh_ öáú«ê âãä^$% %÷h© ,rÿä^âã J9û :âãä^ ÈÑM " " Ý'; ùïÈ<#$ =²) - þ¸ c ^ Ý>{ÝM ùï)..Ý ? q ^ ? 34¸ c&9:²í/ ) ¸ J ¼)00 @æ'; & & û( )¸ )00st AB F 7 ^cu C ÓàÝst AB F ÓÔÝDDDD S(D )á ? " "E _ CMS(D ) ÈÑ êFG+ ÈÑHþb I J " "E _Z[ e^çþb I A e^çK b IÜK b I C 67 Ô $L M bð à $%Ï N-Q $% àO b I C8Iæ Cá P 8? QRS D áæ Y .æ C$LÒ¶¾ T1³® 0¶¾ T1³§ bcºd$ ¨!bcºd$ §ä U² e_bcºd$ ®bcºd$ ® O P!>{ I¾®1»Æ ·¾®°»Ç ¯) ܵ1¶»®¬µ1¶É®- bc ®á§´ VW 姴XÚ¡YZ Y VWºXÚ¡YZ)DDDD?j)_?j¼ _?j[\i ) OP]?j ) ? _?j¼ Õe_ bM _[\ i$%_Z[ ^ " " _Z[0S(D ) ÈÑ ¡^ Ï_ Z[ !S(D ) ÈÑ A w `Bí çÍe/34âã1 "Xí ^ÈÑ Cc34?û( aÑ w ÏÐaÑ b b âã Z[ âãS(D ) =34 ïaÑ ?MâãS(D )Y c ïaÑ34âãS(D ) "Ð `ÈÑ C) "23êïaÑ34âã Z[ Y c êïaÑ34? <M "?âã$%Z[ÈÑM "ð ` ") * 23de~ Ï êïaÑ X $% M de+û(bc !bcbc !bc o 0 A wbcbc e_ bc!d$ f bc û(Ï Mä^g&d$ û( o 8S(D ) , ! h bc ± o VW XÚ¡YZ fíåfYd$ !iS C o 8 , OP P h $bc 8h_ ) " ! Êjábc o ?Õ_ ª« ) L² 8Ie_ ª«8 _stcul jüúd$]Mst !ád$o c 9:íä^Óàrÿ 8 y Yx k c) L² áæ o YÕ_ ª« «êÜä^Óàl q'm ná e_ ª«?' L M ðáYe_ ª«?' L M?áopq Ye_ª« «ê) ² 8I r y %s< _ ª« $_stª«üút d$]Mst ! $M M 'm uM óÓà ùásvw y x e_ yª« cêX zÓàrÿy xþ'm e©VWáVW Y>÷ ,OP ( , P h h = ( , 4 bc e_ bc åd$ d${ÔcÜ , {Ô1| = wcëì?j = ( , 4 bc jA w ~ ð (9:ä^ÓàrÿC y }%s cÏÔ " ! ? Lç þVW "! ?~ä (9 :rÿ %sû ,? ( = 0 A ( Ï ëì?j VW $DDDD XÚ¡YZ fíåfYd$bc o I XÚ¡YZ c Ü ¸ MfíåfYd$ æ_D >÷S(D ) , + , JfYd$P h c+ , = bc 5=Mfíd$ + ,= c bc f fíd$Ï fYd$æ#b I (9: L + ,4 c bc XÚ5=Mfíd$áæ Y ,? ( , OP h h n ( , 4 bc Mfíd$y "{Ô= ëì?j wcø d$) "! ¡YZ "! L 8 & = n ( , 4 bc ¡YZ8{Ôåä^ÓàÝ (J y Yx k Cæ_ öû ( = =?j J w m ?jÇ1,Æ §c Jbc ®fíåfYd$ ´ æ Y¾®,09:OPd$ f¾®,09:M| }§c bc fíd$ d$¨¢¢¢¢¬fí{Ôc= ¾¢®wcø d$) "! ¡Y Z " ! ? (9:M|} c bc fYd$ " ! ? $L I "!? L c d${Ô= wc "$L¡SYàbc) ?bc!d$ fí{ÔåfY{Ôc= (DDDD i S C¾®1»Æ ·? ¾1- !µ1- = c bcºd$ ® M i S C û( =bcºd$ ® M C åï× C !ï× i S X w bc §(I D nµ1- !¾1- = ?bc ®o I i S CDDDDi S C 0XÚ¡YZ A áú Y¾¬® èûbc ® ) (µ1¶É®¬!µ1¶É®-? §´ $L¡SYZ&$L8 &5=á §! ·D?i S 8bc ® {Ô] %Y M bbc f o Ibc Ï o Id$ áFK$ Q(? o ábc 1º¾® ¨bc ® M iS C c0 Mbc ~ w > Mbc cáÕ_ ª«§º§®st ) L²§ð M i S C û(cáÕ_>{cꧺ®st ) L²§i S d Y? " "! ? 6 ÿ$bc M i S C û( v 1 ,? 5å 54 c i S o 2 7ái S C o ? " è û = ð ?j n ( , = (Ý 8 y }%s? û ( = úc " <¡SYà " ! ? X bc M i S C û(c ( M ² ä^?j¼Pû(< #$ bc o I i S c Mb c q 4 c âã " ! üMúcÕ_>{cêbc H ² Ü e_ M b$LDDDD@ðܵ1¶É®? ð üM à~ ¡SYZ à~ 4 !ºå¡YZÔ áâãbc ®åµ1¶É®) w Q bc ¾µ®¸ cuÓÔbc >÷¸ J ' ÓÔe_ M 6 curÿ ' 9: e_12 ! `ä X>÷¸ û Mbc!d$ ä^cuÓà!ÓÔ 6 cu ö cust M "#cÓÔcu M "#$ "#5=bc!d$ Mcu C c ! , ' 4 +' 4 ';8 ,'Úå bc cuÓÔ #b Ist !bc VW) " ¡SYZL YácuÓÔ Y bc è ?jæ_S 0 M i S C û(c A bc M i S C û(c Mcu C û( < #$ i S!cuÓÔ çÍM bæ üM wû(!DDDD¶¾ T1³® ½¶µ¾o 0¶¾ T1³§o A w?jE _?jfg h_ä?j , ! , _bc ?j bc !pq`?jæ ?j¼æ ?j¼ >÷ç 5= () = å P OPÕe_?j Jå Ï e_Ò OP ?j Jå#$ ? ' M á ? ' Ï Q àæ P 5 8 M ¡(bc ?j 8 ,? ! ( |}å èf?j¢£ cæ 1| þ & g¤í¢£ <M b å ( ?jð8 & ?j1|bc !bc 1| ! ábc {Ô¥_ ª« >{= ð áYe_ ª«2¦§ &?j1|@ðbc 1| ábc {Ô ¥_ ª« >{= áwe_ ª« ¦§ &1|DDDD cust¶¾ T1³®? e_(Il j ^st U¨ AB F 9:0¾¶-§!0¾¶-®ç &B F ÓàÝ!ÓÔÝæ_B F 0 M ©C& 䪫¬å®¯°s e±l jXëst st v §¨ä磌¬å®¯°s 7 < ïáB F ©²v?l j ³st vÜäï < ´@K µç¶· ó <<g F¸ ¹3º»st st o ¼b ±s ½, 7¾*¼b =û(ª«¬¿ ÀÁ <û( 0 0 ð û(®¯°s Âà h$ 0 §¨¢(ÄÏ X'(ä^cu'(ä^cu v §¨Å æ Yä^cu öï 0¾¶-§ÝÐ ^ cu C ÓàÝ0¾¶-®?Æ8Iä^curÿ >÷e_ ç C. M ^curÿ XÜä^curÿ K S( ó t¸ ù cê!t F ù cêQ H 8.//& óDDDD [á o >{ XÇAIÈÉ>{ð ä5 ëì>{æ 8 & úc wc ! S(D ) <Êk 8ËÌ J ?jÍóå & Î8 & Î >{ <h_ ª« 7 rÿáú>{Y & âã ^µ¶° XâãÝ`9: ( Î c MÏÐ ÜÝ` $ä àëì ¥/34.e/34 Q e/ÜÝ`åä^ à34DDDDá Y st o là 34 t.e/þ q 34 !S(D ) <áÎ wþÊkÑÔ Òe Ó & . ¡S b I m^S(D ) Ôs ? <á)..Õ u o ùw Q67 '; ebcêXûst ¡ Ú ¼bo ! Y_Ý`9:>{²)_ ²) ÜÖ í _²) - - - l q¸ å ¸ P 1D# ? O¸ ¸²) -קþ¸ cá «ê,¶Ý |} ùþ'm = í .e K ? ± ØÙL e_" $ æ_" $ e Úu M Mû u o þ ,¶ ùL';0&9 : w |} ùeÛúä²) >÷y Ó¸^ Z[ æ_ Ü ÔÝcÞAI >{Ð C <ßM "(Ä"c Ü l q¸ ¸ ï` ï× / )å ).. J¸ rÿ ¸GHI(Äáa¸ 56ð ¸ 0>( ¸ ;<? àI ¸ ð ? ¸ (Ä JÖ í Îÿ! #Ö áâZ[W &rãÜ '(Z[ à ¸ Õ© àe_Z[ Üy_Ö àe_+ Z[';û( y_ <DDDD¸ Ó¸ w;ä ! 5=åÈÑ$%7OPrÿ ¸ Ó YDáÈÑaí²í ¸ C ÈÑrÿDá$%aí²í à $%Z[DëìA Q OPrÿ$Dá ¸ c !)00ݲí/ )¸DÕÜ Ü àe_Z[åÕ àe_ ²) ²íe_ ! 7¸ öÕ_Z[ ફ XÇbc > æM ' 8 ¡ çèÔs¸ C ÈÑ! à $% m^é&¸ kê$%¦§(+ 9:; e_ ª«kêMSëáe_ ª«? < #t. à e_Z[? Ô $% t '1 ìP àZ[t í ª« j. ÓÔ $% 7 $%Ð làYe_Z[ ª« ª«ÍÙ.+ 9:; "c 7Z[¸ l* >÷ +<!- <ÓÔrÿîï¸ «ê s M ù". '$ +<!- <Ý ùþî uḠ>{ð>{¸ j. '$s M ù 2ñ_ò>{ñò =²) - - K l q¸ ?óí$% >÷ÈÑ!$%a ²ì¸ $%'( v²) ïñò²) ñò >÷Ü ñò! à>{PòzDDDDÖ ô(OPrÿ uMÊH ! 79: 8 ù öõ*Ð Ü $ Z[!±_²) y óíÜ á ~ ? ËÌ+ C à æçè<ö¸ wl qáâZ[ _áâZ[ÈÑM " "! "(I÷Â& & ÝøÎÿ!¸ áâZ[< ' ! '1=|} ù áâZ[ ÷ ! C " "7 " u ñòA ù²L$I Y"4 "÷ 88 Pú"4 "÷ÂM"4 "÷ÂM )¸"4 "÷ÂM )¸¸ ! ñòc ¸ ! $ ¸! Ìû $"Ø $"üØSáXYo /& ` ! 7 , }Z <M 0 ýÓÔ`}Z <M 0 ä^ !$% $。

51单片机C语言编程基础及实例

51单片机C语言编程基础及实例51单片机C语言编程基础及实例C语言是一门通用计算机编程语言,应用广泛。

下面是店铺整理的51单片机C语言编程基础及实例,希望对大家有帮助!单片机的外部结构:DIP40双列直插;P0,P1,P2,P3四个8位准双向I/O引脚;(作为I/O输入时,要先输出高电平)电源VCC(PIN40)和地线GND(PIN20);高电平复位RESET(PIN9);(10uF电容接VCC与RESET,即可实现上电复位)内置振荡电路,外部只要接晶体至X1(PIN18)和X0(PIN19);(频率为主频的12倍)程序配置EA(PIN31)接高电平VCC;(运行单片机内部ROM中的程序)P3支持第二功能:RXD、TXD、INT0、INT1、T0、T1单片机内部I/O部件:(所为学习单片机,实际上就是编程控制以下I/O部件,完成指定任务)四个8位通用I/O端口,对应引脚P0、P1、P2和P3;两个16位定时计数器;(TMOD,TCON,TL0,TH0,TL1,TH1) 一个串行通信接口;(SCON,SBUF)一个中断控制器;(IE,IP)针对AT89C52单片机,头文件AT89x52.h给出了SFR特殊功能寄存器所有端口的定义。

C语言编程基础:十六进制表示字节0x5a:二进制为01011010B;0x6E为01101110。

如果将一个16位二进数赋给一个8位的字节变量,则自动截断为低8位,而丢掉高8位。

++var表示对变量var先增一;var—表示对变量后减一。

x |= 0x0f;表示为 x = x | 0x0f;TMOD = ( TMOD & 0xf0 ) | 0x05;表示给变量TMOD的低四位赋值0x5,而不改变TMOD的高四位。

While( 1 ); 表示无限执行该语句,即死循环。

语句后的分号表示空循环体,也就是{;}在某引脚输出高电平的编程方法:(比如P1.3(PIN4)引脚)代码#include //该头文档中有单片机内部资源的符号化定义,其中包含P1.3void main( void ) //void 表示没有输入参数,也没有函数返值,这入单片机运行的复位入口{P1_3 = 1; //给P1_3赋值1,引脚P1.3就能输出高电平VCCWhile( 1 ); //死循环,相当 LOOP: goto LOOP;}注意:P0的每个引脚要输出高电平时,必须外接上拉电阻(如4K7)至VCC电源。

AT89C52篮球计分器

篮球计分器设计摘要:这次实训采用AT89C52单片机、2N2905三极管、8个按钮、若干个电阻和电容、晶振器等器材来构成一个简易的电子时钟。

关键词:单片机AT89C52、数码管显示一、基本设计方案 (1)二、硬件系统设计………………………………………第2-3页三、电路设计: (4)四、源程序………………………………………………第5-12页五、调试…………………………………………………第12-13页六、作用: (13)七、总结: (14)一、基本设计方案1)利用AT89C52单片机结合数码管显示器设计的一个简易的篮球计分器,采用数码管显示。

可以实现为两个篮球小组加减分的功能。

基本功能:●数码管显示;●同时为两组加减分●能够清零复位2)篮球计分器以单片机AT89C52作为控制核心,该系统有如下方案组成:①控制模块---采用AT89C52单片机控制②显示模块---数码管(能显示两组比分)③控制模块---按键二、硬件系统设计1)本系统采用AT89C52芯片,有40个引脚40个引脚大致可分为4类:电源、扫描、段码输出和I/O引脚。

1、电源:(1) VCC - 芯片电源,接+5V;(2) VSS - 接地端;2、计分器:XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。

3、控制线: RST(Reset)功能:复位信号输入端。

4、I/O线1)AT89C52共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。

P3口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。

2)数码管显示器接口及显示方式由于所有八位段选线都由一个I/O口控制,因此,在每一瞬间,所有数码管显示块会显示相同的字符。

要想每位显示不同的字符,就必须采用扫描方法轮流点亮每一位数码管显示块,也就是每一瞬间只点亮一位数码管显示块。

此刻,段选控制I/O输出相应字符段选码(字型码),而位选则控制I/O口在该显示位送入选通信号(共阴极送低电平,共阳极送高电平)。

51单片机AT89C52中文资料

51单片机AT89C52中文资料--------------------------------------------------------------------------------51单片机AT89C52中文资料AT89C52 ATMEL公司生产的低电压,高性能CMOS 8位单片机.片含8K byTES的可反复擦写的只读程序存储器(PEROM)和256 byTES 。

的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,与标准MCS-51指令系统及8052 产品引脚兼容,片置通用8位中央处理器(CPU )和FLASH由存储单元,功能强大AT89C52单片适用于许多较为复杂控制应用场合。

主要性能参数:与Mcs-51产品指令和引脚完全兼容。

8字节可重擦写FLASH闪速存储器1000 次擦写周期全静态操作:0HZ-24MHZ三级加密程序存储器256X8字节部RAM32个可编程I/0口线3个16 位定时/计数器8个中断源可编程串行UART通道低功耗空闲和掉电模式部结构图AT89C52部框图功能特性:AT89C52 提供以下标准功能:8字节FLASH闪速存储器,256字竹部RAM , 32个I/O口线,3个16 位定时/计数器,一个6向量两级中断结构,一个全双工串行通信口,片振荡器及时钟电路。

同时,AT89c52可降至OHz的静态逻辑操作,并支持两种软件可选的节电上作模式。

空闲方式停止CPU 的工作,但允许RAM,定时/计数器.串行通信口及中断系统继续工作。

掉电方式保存RAM 中的容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位.功能引脚说明:Vcc:电源电压GND:地P0:P0口是一组8位漏极开路型双向1/O 口,也即地址/数据总线复用口。

作为输出口用时.每位能吸收电流的方式驱动8个TTL 逻辑门电路,对端口P0 写“1”时,可作为高阻抗输入端用。

at89c52单片机介绍

at89c52中文资料介绍AT89C52 ATMEL公司生产的低电压,高性能CMOS 8位单片机.片内含8K byTES的可反复擦写的只读程序存储器(PEROM)和256 byTES 。

的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,与标准MCS-51指令系统及8052 产品引脚兼容,片内置通用8位中央处理器(CPU )和FLASH 由存储单元,功能强大AT89C52单片适用于许多较为复杂控制应用场合。

主要性能参数:与Mcs-51产品指令和引脚完全兼容。

8字节可重擦写FLASH闪速存储器1000 次擦写周期全静态操作:0HZ-24MHZ三级加密程序存储器256X8字节内部RAM32个可编程I/0口线3个16 位定时/计数器8个中断源可编程串行UART通道低功耗空闲和掉电模式AT89C52内部框图功能特性:AT89C52 提供以下标准功能:8字节FLASH闪速存储器,256字竹内部RAM , 32个I/O口线,3个16 位定时/计数器,一个6向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,AT89c52可降至OHz的静态逻辑操作,并支持两种软件可选的节电上作模式。

空闲方式停止CPU 的工作,但允许RAM,定时/计数器.串行通信口及中断系统继续工作。

掉电方式保存RAM 中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位.功能引脚说明:Vcc:电源电压GND:地P0:P0口是一组8位漏极开路型双向1/O 口,也即地址/数据总线复用口。

作为输出口用时.每位能吸收电流的方式驱动8个TTL 逻辑门电路,对端口P0 写“1”时,可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

在FLASH由编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

单片机课程设计报告ADC转换生成正弦波形

单片机课程设计报告ADC转换生成正弦波形单片机课程设计报告题目:ADC转换生成正弦波形专业:测控技术与仪器班级:姓名:学号:指导教师:2015年 1 月 14 日目录第1章系统设计方案第2章系统硬件设计2.1 主控制器电路2.2 模数转换电路2.3 显示电路第3章系统软件设计3.1 系统整体流程3.2 直流电压采集3.3 交流电压采集第4章系统调试4.1 xxx的调试4.2 xxx的调试。

第5章结论与总结5.1 结论5.2 总结第1章系统设计方案使用STC89c52单片机与ADC0804芯片实现A/D转换直流电压采集,转换之后在LCD1602上显示所采集的直流电压值。

使用STC89c52单片机与ADC0804芯片实现A/D转换交流电压采集,转换之后在KS0108上显示交流电压动态波形。

第2章系统硬件设计2.1 主控制器电路(1)AT89C52单片机(2)晶振电路(3)复位电路2.2 模数转换电路2.3 显示电路(1) LCD1602显示电路(2) KS0108显示电路第3章系统软件设计3.1系统整体流程图开始显示初始化进行A/D转换数字信号处理转化显示数据调用显示函数结束3.2直流电压采集程序(1)直流电压采集主程序#include<reg52.h> #include"adc0804.h" #include"lcd1602.h"#define uchar unsigned char #define uint unsigned int #define ulong unsigned long void datds();void display();uchar dat=0;uchar a[]="the value is "; uchar b[]={0,0};void main(){uchar i=0;init();for(i=0;i<13;i++){comd(0x80+i);write(a[i]);}while(1){datc();dat=datw();datds();display();}}void datds(){b[0]=dat*5/255;b[1]=dat*50/255%10;}void display(){comd(0xc4);write(b[0]+0x30);comd(0xc5);write('.');comd(0xc6);write(b[1]+0x30);comd(0xc7);write('V');}(2)头文件lcd1602.h#include<reg52.h>#define uchar unsigned char#define uint unsigned int#define ulong unsigned longvoid write(uchar datee);void comd(uchar com); void init();sbit en=P3^4;sbit rs=P3^5;void init(){en=0;comd(0x38);comd(0x0c);comd(0x06);comd(0x01);}void comd(uchar com) { rs=0;delay(50);P0=com;delay(50);en=1;delay(50);en=0;delay(50);}void write(uchar datee) {rs=1;delay(50);P0=datee;delay(50);en=1;delay(50);en=0;delay(50);}(3) 头文件adc0804.h #include<reg52.h>#define uchar unsigned char#define uint unsigned int#define ulong unsigned longchar datw();void datc();void datd();void delay(uint t);sbit rd=P3^1; sbit wr=P3^2; sbit intr=P3^3; sbit cs=P3^0; void datc() //写命令 {cs=0;wr=1;delay(200);wr=0;delay(200);wr=1;while(intr);cs=1;}char datw() //读数据 {uchar j=0;cs=0;rd=1;delay(200);rd=0;delay(200);j=P1;rd=1;cs=1;return j;}void delay(uint t){while(t--);}3.3交流电压采集程序(1)交流电压采集主程序#include<reg52.h>#include"adc0804.h" #include"lcd.h" #define uchar unsigned char#define uint unsigned int#define ulong unsigned longvoid datedis();void display();void qing(uchar q2); void qingp(); sbit cs1=P0^1;sbit cs2=P0^2;uchar dat=0;uchar i;uchar j,da;void main(){init();while(1){ cs1=0;cs2=1;qingp();display();cs2=0;cs1=1;qingp();display();}}void qing(uchar q2) {uchar q1;for(q1=0;q1<8;q1++){comd(184+q1);comd(0x40+q2);write(0);}}void qingp() {uchar q1,q2;for(q1=0;q1<8;q1++) {comd(184+q1);comd(0x40);for(q2=0;q2<64;q2++) write(0);}}void display(){uchar x=0;for(x=0;x<64;x++) {//qing(x);datc();dat=datw();datedis();comd(i);comd(64+x);write(j);}}void datedis() { uchar j0=1;da=dat/4;i=184+da/8;j=j0<<(da%8);}(2)头文件lcd.h#include<reg52.h>#define uchar unsigned char#define uint unsigned int#define ulong unsigned longvoid write(uchar datee); void comd(uchar com); void init(); sbit en=P3^6;sbit rs=P3^7;void init(){en=0;comd(4);comd(0x3f);}void comd(uchar com) {rs=0;delay(50);P2=com;delay(50);en=1;delay(50);en=0;delay(50);}void write(uchar datee) {rs=1;delay(50);P2=datee;delay(50);en=1;delay(50);en=0;delay(50);}(3)头文件ADC0804.h #include<reg52.h> #define uchar unsigned char#define uint unsigned int#define ulong unsigned longchar datw();void datc();void datd();void delay(uint t);sbit rd=P3^1; sbit wr=P3^2; sbit intr=P3^3; sbit cs=P3^0; void datc() //写命令 {cs=0;wr=1;delay(200);wr=0;delay(200);wr=1;while(intr);cs=1;}char datw() //读数据 {uchar j1=0;cs=0;rd=1;delay(200);rd=0;delay(200);j1=P1;rd=1;cs=1;return (j1);}void delay(uint t) {while(t--);}第4章系统调试 4.1 直流电压采集的调试程序调试采用proteus仿真软件调试采集电压LCD显示结果4.2交流电压采集的调试第5章结论与总结5.1 结论(1)直流电压采集调试中,采集电压为5V的50%(即2.5V),而LCD1602显示值为2.4V,误差很小,说明实验硬件和软件都很成功,可以成功实现直流电压采集并显示电压值的功能。

简单实例助你快速掌握PROTEUS的用法

子情境1:简单实例助你快速掌握PROTEUS的用法 (5)1.1 子情境内容:让单片机动起来,用单片机控制一个LED灯闪烁发光。

(8)1.2 子情境目标: (8)1.3 子情境步骤 (8)1.3.1步骤一:PROTEUS电路设计 (8)1.3.2步骤二:源程序设计与生成目标代码文件 (13)(1)程序流程图 (13)(2)源程序设计 (14)1.3.3 步骤三:PROTEUS仿真 (15)1.4 扩展练习 (17)子情境二:用发光二极管实现流水灯乒乓球效果 (18)2.1 子情境目标: (18)2.2 子情境步骤 (18)2.2.1 步骤一:PROTEUS电路设计 (18)2.2.2步骤二:源程序设计与目标代码文件生成 (19)(1)程序流程图 (19)(2)源程序设计 (20)2.2.3 步骤三:PROTEUS仿真 (22)2.4 扩展练习 (22)子情境三:数码管动态扫描 (23)3.1子情境内容:利用动态扫描让四位数码管稳定的显示1234。

(23)3.2 子情境目标: (23)(1)掌握单片机控制四位数码管的动态扫描技术,包括程序设计和电 (23)3.3 知识点链接 (23)3.4 任务步骤 (24)3.4.1 步骤一:PROTEUS电路设计,单片机控制四位共阴极数码管动态扫描显示的原理图如图5-17所示。

(24)3.4.2 步骤二:源程序设计与目标代码文件生成 (26)(1)程序流程图 (26)(2)源程序设计 (26)3.4.3 步骤三:PROTEUS仿真 (28)3.5 扩展练习 (29)子情境四:定时/计数器的使用——方波发生器 (30)4.1子情境内容:用AT89C51单片机定时/计数器0的定时功能可构成一简单的方波发生器,实现周期为2s的方波,并能在虚拟示波器上直观地显示波形。

(30)4.2 子情境目标: (30)4.3 知识点链接 (30)4.4.1 步骤一:PROTEUS电路设计,实现周期为2s的方波的原理图如图5-22所示。

7.3-AT89S52单片机编译及仿真环境

//打印程序执行的信息

while(1);

}

在输入上述程序时,Keil c51会自动识别关键字,并以不同的颜色提示用户加以注 意,这样会使用户少犯错误,有利于提高编程效率。程序输入完毕后,如图7-12 所示。

7.3.1 Keil C51软件及应用

图7-12 输入文件后界面

7.3.1 Keil C51软件及应用

main ()

/*主函数名*/

{

/*主函数体开始*/

int x,y,z;

/*主函数体的内部变量类型说明*/

x=10;

/*变量赋值*/

y=20;

z=x+y;

/*计算z=x+y的值*/

while(1);

}

/*程序结束*/

7.3.1 Keil C51软件及应用

本例中main是主函数名,要执行的主函数的内容称为 主函数体,主函数体用花括号“{}”围起来。函数体中 包含若干条将被执行的程序语句,每条语句都必须以 分号“;”为结束符。为了使程序便于阅读和理解,可以 给程序加上一些注释。C语言的注释部分由符号“/*” 开始,以符号“*/”结束,注释内容可在一行内写完, 也可以分成几行来写。注释部分不参加编译,编译时 注释的内容不产生可执行代码。注释在程序中的作用 很重要,一个优秀的程序设计者应该在程序设计中使 用足够的注释来说明整个程序的功能、有关算法和注 意事项等。

建文件后的界面如图7-9所示。

7.3.1 Keil C51软件及应用

图7-9建立文件编辑窗口

7.3.1 Keil C51软件及应用

此时光标在编辑窗口里闪烁,这时可以输入用户的应用程序了。 但最好先保存该空白文件,单击菜单命令【File】/【Save As】。 在“文件名”栏右侧的编辑框中输入欲使用的文件名,注意必须 输入正确的扩展名。如果用C语言编写程序,扩展名为(.C);如 果用汇编语言编写程序,扩展名必须为(.asm)。然后单击“保 存”按钮。

AT89C52中文资料

A T89C52中文资料电子驿站http:// E-mail: support@A T89C52是美国A TMEL公司生产的低电压,高性能CMOS 8位单片机,片内含8k bytes的可反复擦写的只读程序存储器(PEROM)和256 bytes的随机存取数据存储器(RAM),器件采用A TMEL公司的高密度、非易失性存储技术生产,与标准MCS-51指令系统及8052产品引脚兼容,片内置通用8位中央处理器(CPU)和Flash存储单元,功能强大A T89C52单片机适合于许多较为复杂控制应用场合。

主要性能参数:·与MCS-51产品指令和引脚完全兼容·8k字节可重擦写Flash闪速存储器·1000次擦写周期·全静态操作:0Hz-24MHz·三级加密程序存储器·256×8字节内部RAM·32个可编程I/O口线·3个16位定时/计数器·8个中断源·可编程串行UART通道·低功耗空闲和掉电模式功能特性概述:A T89C52提供以下标准功能:8k字节Flash闪速存储器,256字节内部RAM,32个I/O口线,3个16位定时/计数器,一个6向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,A T89C52可降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。

空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。

掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。

AT89C52方框图·P0口:P0口是一组8位漏极开路型双向I /O 口,也即地址/数据总线复用口。

作为输出口用时,每位能吸收电流的方式驱动8个TTL 逻辑门电路,对端口P0写“l ”时,可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

单片机 STC89C52 温度传感器论文

单片机数字温度计摘要:本设计单片机采用AT89C52芯片,数字温度传感器采用美国DALASS公司的1–Wire器件DS18B20,即单总线器件DS18B20,与单片机组成一个测温系统,当系统上电时,温度传感器就会读出当前环境的温度,并在三位LED数模显示管上显示出当前的温度,该测温仪的测温范围为0℃~110℃,按此要求设计硬件和软件以实现这一功能。

关键词:单片机STC89C52 温度传感器DS18B20; 温度测量电子线路单片机汇编语言温度1 引言:单片机又称单片微控制器,它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上。

概括的讲:一块芯片就成了一台计算机。

它的体积小、质量轻、价格便宜、为学习、应用和开发提供了便利条件。

同时,学习使用单片机是了解计算机原理与结构的最佳选择。

目前单片机渗透到我们生活的各个领域,几乎很难找到哪个领域没有单片机的踪迹。

单片机在检测和控制系统中得到广泛的应用, 温度则是系统常需要测量、控制和保持的一个量。

本设计所介绍的数字温度计与传统的温度计相比,具有读数方便,测温范围广,测温准确,其输出温度采用数字显示,该设计控制器使用单片机STC89C52,测温传感器使用DS18B20,用4位共阳极LED数码管以串口传送数据,实现温度显示,能准确达到以上要求。

2 总体设计方案:2.1 设计思路:(1)本设计是测温电路,可以使用热敏电阻之类的器件利用其感温效应,在将随被测温度变化的电压或电流采集过来,进行A/D转换后,就可以用单片机进行数据的处理,在显示电路上,就可以将被测温度显示出来,这种设计需要用到A/D转换电路,感温电路比较麻烦。

(2)从中考虑到用温度传感器,在单片机电路设计中,大多都是使用传感器,所以这是非常容易想到的,所以可以采用一只温度传感器DS18B20,此传感器,可以很容易直接读取被测温度值,进行转换,就可以满足设计要求。

从以上两种方案,很容易看出,采用方案(2),电路比较简单,软件设计也比较简单,故采用了方案(2)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

/*--------------------------------------------------------------------------AT89X52.HHeader file for the low voltage Flash Atmel AT89C52 and AT89LV52. Copyright (c) 1988-2002 Keil Elektronik GmbH and Keil Software, Inc. All rights reserved.--------------------------------------------------------------------------*/#ifndef __AT89X52_H__#define __AT89X52_H__/*------------------------------------------------Byte Registers------------------------------------------------*/sfr P0 = 0x80;sfr SP = 0x81;sfr DPL = 0x82;sfr DPH = 0x83;sfr PCON = 0x87;sfr TCON = 0x88;sfr TMOD = 0x89;sfr TL0 = 0x8A;sfr TL1 = 0x8B;sfr TH0 = 0x8C;sfr TH1 = 0x8D;sfr P1 = 0x90;sfr SCON = 0x98;sfr SBUF = 0x99;sfr P2 = 0xA0;sfr IE = 0xA8;sfr P3 = 0xB0;sfr IP = 0xB8;sfr T2CON = 0xC8;sfr T2MOD = 0xC9;sfr RCAP2L = 0xCA;sfr RCAP2H = 0xCB;sfr TL2 = 0xCC;sfr TH2 = 0xCD;sfr PSW = 0xD0;sfr ACC = 0xE0;sfr B = 0xF0;/*------------------------------------------------P0 Bit Registers------------------------------------------------*/sbit P0_0 = 0x80;sbit P0_1 = 0x81;sbit P0_2 = 0x82;sbit P0_3 = 0x83;sbit P0_4 = 0x84;sbit P0_5 = 0x85;sbit P0_6 = 0x86;sbit P0_7 = 0x87;/*------------------------------------------------PCON Bit Values------------------------------------------------*/#define IDL_ 0x01#define STOP_ 0x02#define PD_ 0x02 /* Alternate definition */#define GF0_ 0x04#define GF1_ 0x08#define SMOD_ 0x80/*------------------------------------------------TCON Bit Registers------------------------------------------------*/sbit IT0 = 0x88;sbit IE0 = 0x89;sbit IT1 = 0x8A;sbit IE1 = 0x8B;sbit TR0 = 0x8C;sbit TF0 = 0x8D;sbit TR1 = 0x8E;sbit TF1 = 0x8F;/*------------------------------------------------TMOD Bit Values------------------------------------------------*/#define T0_M0_ 0x01#define T0_M1_ 0x02#define T0_CT_ 0x04#define T0_GATE_ 0x08#define T1_M0_ 0x10#define T1_M1_ 0x20#define T1_CT_ 0x40#define T1_GATE_ 0x80#define T1_MASK_ 0xF0#define T0_MASK_ 0x0F/*------------------------------------------------P1 Bit Registers------------------------------------------------*/sbit P1_0 = 0x90;sbit P1_1 = 0x91;sbit P1_2 = 0x92;sbit P1_3 = 0x93;sbit P1_4 = 0x94;sbit P1_5 = 0x95;sbit P1_6 = 0x96;sbit P1_7 = 0x97;sbit T2 = 0x90; /* External input to Timer/Counter 2, clock out */ sbit T2EX = 0x91; /* Timer/Counter 2 capture/reload trigger & dir ctl *//*------------------------------------------------SCON Bit Registers------------------------------------------------*/sbit RI = 0x98;sbit TI = 0x99;sbit RB8 = 0x9A;sbit TB8 = 0x9B;sbit REN = 0x9C;sbit SM2 = 0x9D;sbit SM1 = 0x9E;sbit SM0 = 0x9F;/*------------------------------------------------P2 Bit Registers------------------------------------------------*/sbit P2_0 = 0xA0;sbit P2_1 = 0xA1;sbit P2_2 = 0xA2;sbit P2_3 = 0xA3;sbit P2_4 = 0xA4;sbit P2_5 = 0xA5;sbit P2_6 = 0xA6;sbit P2_7 = 0xA7;/*------------------------------------------------IE Bit Registers------------------------------------------------*/sbit EX0 = 0xA8; /* 1=Enable External interrupt 0 */sbit ET0 = 0xA9; /* 1=Enable Timer 0 interrupt */sbit EX1 = 0xAA; /* 1=Enable External interrupt 1 */sbit ET1 = 0xAB; /* 1=Enable Timer 1 interrupt */sbit ES = 0xAC; /* 1=Enable Serial port interrupt */sbit ET2 = 0xAD; /* 1=Enable Timer 2 interrupt */sbit EA = 0xAF; /* 0=Disable all interrupts *//*------------------------------------------------P3 Bit Registers (Mnemonics & Ports)------------------------------------------------*/sbit P3_0 = 0xB0;sbit P3_1 = 0xB1;sbit P3_2 = 0xB2;sbit P3_3 = 0xB3;sbit P3_4 = 0xB4;sbit P3_5 = 0xB5;sbit P3_6 = 0xB6;sbit P3_7 = 0xB7;sbit RXD = 0xB0; /* Serial data input */sbit TXD = 0xB1; /* Serial data output */sbit INT0 = 0xB2; /* External interrupt 0 */sbit INT1 = 0xB3; /* External interrupt 1 */sbit T0 = 0xB4; /* Timer 0 external input */sbit T1 = 0xB5; /* Timer 1 external input */sbit WR = 0xB6; /* External data memory write strobe */ sbit RD = 0xB7; /* External data memory read strobe *//*------------------------------------------------IP Bit Registers------------------------------------------------*/sbit PX0 = 0xB8;sbit PT0 = 0xB9;sbit PX1 = 0xBA;sbit PT1 = 0xBB;sbit PS = 0xBC;sbit PT2 = 0xBD;/*------------------------------------------------T2CON Bit Registers------------------------------------------------*/sbit CP_RL2= 0xC8; /* 0=Reload, 1=Capture select */sbit C_T2 = 0xC9; /* 0=Timer, 1=Counter */sbit TR2 = 0xCA; /* 0=Stop timer, 1=Start timer */sbit EXEN2= 0xCB; /* Timer 2 external enable */sbit TCLK = 0xCC; /* 0=Serial clock uses Timer 1 overflow, 1=Timer 2 */ sbit RCLK = 0xCD; /* 0=Serial clock uses Timer 1 overflow, 1=Timer 2 */ sbit EXF2 = 0xCE; /* Timer 2 external flag */sbit TF2 = 0xCF; /* Timer 2 overflow flag *//*------------------------------------------------T2MOD Bit Values------------------------------------------------*/#define DCEN_ 0x01 /* 1=Timer 2 can be configured as up/down counter */ #define T2OE_ 0x02 /* Timer 2 output enable *//*------------------------------------------------PSW Bit Registers------------------------------------------------*/sbit P = 0xD0;sbit F1 = 0xD1;sbit OV = 0xD2;sbit RS0 = 0xD3;sbit RS1 = 0xD4;sbit F0 = 0xD5;sbit AC = 0xD6;sbit CY = 0xD7;/*------------------------------------------------Interrupt Vectors:Interrupt Address = (Number * 8) + 3------------------------------------------------*/#define IE0_VECTOR 0 /* 0x03 External Interrupt 0 */#define TF0_VECTOR 1 /* 0x0B Timer 0 */#define IE1_VECTOR 2 /* 0x13 External Interrupt 1 */#define TF1_VECTOR 3 /* 0x1B Timer 1 */#define SIO_VECTOR 4 /* 0x23 Serial port */#define TF2_VECTOR 5 /* 0x2B Timer 2 */#define EX2_VECTOR 5 /* 0x2B External Interrupt 2 */#endif。