单片机AT89C52中文资料

AT89C52中文资料

AT89C52中文资料AT89C52的中文资料AT89C52是美国Atmel公司生产的低电压、高性能CMOS 8位单片机,片内含8KB的可反复檫写的程序存储器和12B的随机存取数据存储器(RAM),器件采用Atmel公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内配置通用8位中央处理器(CPU)和Flash存储单元,功能强大的AT89C52单片机可灵活应用于各种控制领域。

AT89C52单片机属于AT89C51单片机的增强型,与Intel 公司的80C52在引脚排列、硬件组成、工作特点和指令系统等方面兼容。

其主要工作特性是:片内程序存储器内含8KB的Flash程序存储器,可擦写寿命为1000次;片内数据存储器内含256字节的RAM;具有32根可编程I/O口线;具有3个可编程定时器;中断系统是具有8个中断源、6个中断矢量、2个级优先权的中断结构;串行口是具有一个全双工的可编程串行通信口;具有一个数据指针DPTR;低功耗工作模式有空闲模式和掉电模式;具有可编程的3级程序锁定位;AT89C52工作电源电压为5(1+0.2)V,且典型值为5V;AT89C52最高工作频率为24MHz。

单片机正常工作时,都需要有一个时钟电路和一个复位电路。

本设计中选择了内部时钟方式和按键电平复位电路,来构成单片机的最小电路。

如图3.1所示。

功能特性描述AT89S52是一种低功耗、高性能CMOS8位微控制器,具有8K 在系统可编程Flash 存储器。

使用Atmel 公司高密度非易失性存储器技术制造,与工业80C51 产品指令和引脚完全兼容。

片上Flash允许程序存储器在系统可编程,亦适于常规编程器。

在单芯片上,拥有灵巧的8 位CPU 和在系统可编程Flash,使得AT89S52为众多嵌入式控制应用系统提供高灵活、超有效的解决方案。

AT89S52具有以下标准功能:8k字节Flash,256字节RAM,32 位I/O 口线,看门狗定时器,2 个数据指针,三个16 位定时器/计数器,一个6向量2级中断结构,全双工串行口,片内晶振及时钟电路。

AT89C52单片机介绍

AT89C52单片机介绍在众多的单片机系列中,AT89C52是一种低功耗、高性能CMOS8位微控制器,具有8K在系列可编程Flash存储器。

使用Atmel公司高密度非易失性存储器技术制造,与工业80C51产品指令和引脚完全兼容。

片上Flash允许程序存储器在系统可编程,也适用于常规编程。

在单芯片上,拥有灵巧的8位CPU和在系统可编程Flash,使得AT89C52为众多嵌入式控制应用系统提供高灵活、超高效的解决方案。

AT89C52具有以下标准功能:8K字节Flash,256字节RAM,32位I/O口线,3个16位定时器/计数器,一个响亮2级中断结构,全双工串行口,片内晶振及时钟电路。

另外,AT89C52可降至0HZ静态逻辑操作,支持2种软件可选择节电模式。

空闲模式下,CPU停止工作,允许RAM、定时器/计数器、串口、中断继续工作。

掉电保护方式下,RAM内容被保存,振荡器被冻结,单片机一切工作停止,直到下一个中断或硬件复位为止。

AT89C52单片机为很多嵌入式控制系统提供了一种灵活性高且廉价的方案。

故此选用AT89C52单片机。

1 AT89C52单片机1.1 AT89C52单片机的硬件结构如图3-1所示,为AT89C52的硬件结构图。

AT89C52单片机的内部结构与MCS-51系列单片机的构成基本相同。

CPU是由运算器和控制器所构成的。

运算器主要用来对操作数进行算术、逻辑运算和位操作的。

控制器是单片机的指挥控制部件,主要任务的识别指令,并根据指令的性质控制单片机各功能部件,从而保证单片机各部分能自动而协调地工作。

它的程序存储器为8K字节可重擦写Flash闪速存储器,闪烁存储器允许在线+5V电擦除、电写入或使用编程器对其重复编程。

数据存储器比51系列的单片机相比大了许多为256字节RAM。

AT89C52单片机的指令系统和引脚功能与MCS-51的完全兼容。

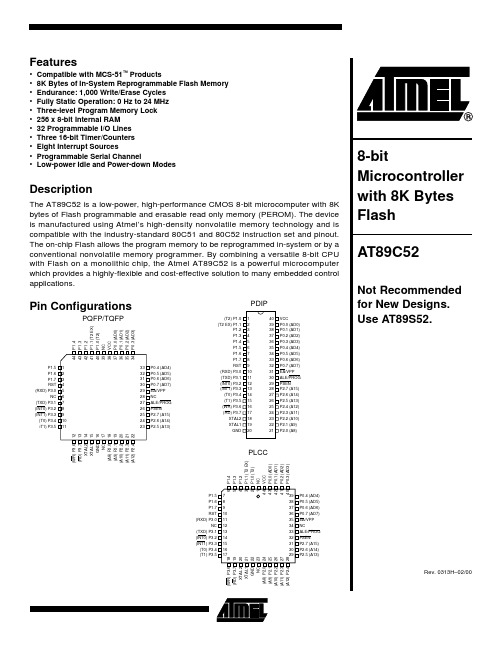

图 3-1 单片机89C52结构框图1.2 主要性能参数• 8K字节可重擦写Flash闪速存储器• 1000次可擦写周期•全静态操作:0Hz-24MHz•三级加密程序存储器• 256×8字节内部RAM• 32个可编程I/O口线• 3个16位定时/计数器• 8个中断源•可编程串行UART通道•低功耗空闲和掉电模式图 3-2 AT89C52外部引脚图1.3 AT89C52管脚说明VCC:电源GND:接地P0口:P0口是一个8位漏级开路的双向I/O口。

AT89C52单片机介绍

AT89C52单片机介绍在众多的单片机系列中,AT89C52是一种低功耗、高性能CMOS8位微控制器,具有8K在系列可编程Flash存储器。

使用Atmel公司高密度非易失性存储器技术制造,与工业80C51产品指令和引脚完全兼容。

片上Flash允许程序存储器在系统可编程,也适用于常规编程。

在单芯片上,拥有灵巧的8位CPU和在系统可编程Flash,使得AT89C52为众多嵌入式控制应用系统提供高灵活、超高效的解决方案。

AT89C52具有以下标准功能:8K字节Flash,256字节RAM,32位I/O口线,3个16位定时器/计数器,一个响亮2级中断结构,全双工串行口,片内晶振及时钟电路。

另外,AT89C52可降至0HZ静态逻辑操作,支持2种软件可选择节电模式。

空闲模式下,CPU停止工作,允许RAM、定时器/计数器、串口、中断继续工作。

掉电保护方式下,RAM内容被保存,振荡器被冻结,单片机一切工作停止,直到下一个中断或硬件复位为止。

AT89C52单片机为很多嵌入式控制系统提供了一种灵活性高且廉价的方案。

故此选用AT89C52单片机。

1 AT89C52单片机1.1 AT89C52单片机的硬件结构如图3-1所示,为AT89C52的硬件结构图。

AT89C52单片机的内部结构与MCS-51系列单片机的构成基本相同。

CPU是由运算器和控制器所构成的。

运算器主要用来对操作数进行算术、逻辑运算和位操作的。

控制器是单片机的指挥控制部件,主要任务的识别指令,并根据指令的性质控制单片机各功能部件,从而保证单片机各部分能自动而协调地工作。

它的程序存储器为8K字节可重擦写Flash闪速存储器,闪烁存储器允许在线+5V电擦除、电写入或使用编程器对其重复编程。

数据存储器比51系列的单片机相比大了许多为256字节RAM。

AT89C52单片机的指令系统和引脚功能与MCS-51的完全兼容。

图3-1 单片机89C52结构框图1.2 主要性能参数•8K字节可重擦写Flash闪速存储器•1000次可擦写周期•全静态操作:0Hz-24MHz•三级加密程序存储器•256×8字节内部RAM•32个可编程I/O口线•3个16位定时/计数器•8个中断源•可编程串行UART通道•低功耗空闲和掉电模式图3-2 AT89C52外部引脚图1.3 AT89C52管脚说明VCC:电源GND:接地P0口:P0口是一个8位漏级开路的双向I/O口。

at89c52

AT89C52概述AT89C52是一款高性能的8位单片机,由Atmel公司生产。

它是AT89系列单片机中的一员,采用MCS-51指令集架构,并使用快速闪存储存程序。

AT89C52具有丰富的外设,包括多个输入输出引脚、计时器、串口通信接口等,广泛应用于嵌入式系统、通信设备、工业控制等领域。

主要特性•采用CMOS技术,工作电压范围广泛(2.4V至5.5V)•具有8KB的内部闪存,用于存储程序和数据•提供256字节的内部RAM,可用于数据存储•包含三个计时器/计数器,可用于定时/计数功能•集成两个串口通信接口,方便与外部设备进行数据交互•支持多种中断方式,提供更好的系统响应能力•可编程输入/输出引脚,可用于连接外部设备引脚描述AT89C52具有40个引脚,以下是一些重要引脚的描述:1.P1.0至P1.7: 8位并行输入/输出引脚,可根据需要进行配置。

在配置为输入时,可以连接外部设备并读取输入值;在配置为输出时,可以向外部设备发送数据。

2.P2.0至P2.7: 8位并行输入/输出引脚,也可以根据需要进行配置。

3.P3.0至P3.7: 8位并行输入/输出引脚,同时具有更多功能,包括与外部存储器的数据和地址传输,以及与LCD显示器的连接等。

4.RST: 复位引脚,将其拉低时可以重启单片机。

5.EA/VPP: 外部访问使能/编程电压引脚,可用于提供外部程序存储器的访问或编程电压。

6.XTAL1/XTAL2: 外部晶振引脚,接入适当的晶振电路以提供时钟信号。

闪存编程AT89C52的程序存储在内部闪存中。

要编程AT89C52,可以使用专用的编程器,通过并行端口或串行端口将目标程序下载到芯片中。

编程AT89C52的一般步骤如下:1.选择所需的编程器,并连接到AT89C52的编程接口。

2.打开编程器软件,并选择正确的单片机型号。

3.导入目标程序文件,该文件应该是以二进制格式存储的。

4.配置编程器选项,包括芯片复位方式、编程电压等。

AT89C52中文资料_参数_电路图

AT89C52为8 位通用微处理器,采用工业标准的C51内核,在内部功能及管脚排布上与通用的8xc52 相同,其主要用于会聚调整时的功能控制。

功能包括对会聚主IC 内部寄存器、数据RAM及外部接口等功能部件的初始化,会聚调整控制,会聚测试图控制,红外遥控信号IR的接收解码及与主板CPU通信等。

主要管脚有:XTAL1(19 脚)和XTAL2(18 脚)为振荡器输入输出端口,外接12MHz 晶振。

RST/Vpd(9 脚)为复位输入端口,外接电阻电容组成的复位电路。

VCC(40 脚)和VSS(20 脚)为供电端口,分别接+5V电源的正负端。

P0~P3 为可编程通用I/O 脚,其功能用途由软件定义,在本设计中,P0 端口(32~39 脚)被定义为N1 功能控制端口,分别与N1的相应功能管脚相连接,13 脚定义为IR输入端,10 脚和11脚定义为I2C总线控制端口,分别连接N1的SDAS(18脚)和SCLS(19脚)端口,12 脚、27 脚及28 脚定义为握手信号功能端口,连接主板CPU 的相应功能端,用于当前制式的检测及会聚调整状态进入的控制功能。

P0 口P0 口是一组8 位漏极开路型双向I/O 口,也即地址/数据总线复用口。

作为输出口用时,每位能吸收电流的方式驱动8 个TTL逻辑门电路,对端口P0 写“1”时,可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8 位)和数据总线复用,在访问期间激活内部上拉电阻。

在Flash编程时,P0 口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

P1 口P1 是一个带内部上拉电阻的8 位双向I/O 口,P1 的输出缓冲级可驱动(吸收或输出电流)4 个TTL 逻辑门电路。

对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口。

作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(IIL)。

AT89C52单片机介绍

AT89C52单片机介绍n to AT89C52 MicrocontrollerAmong the many microcontroller series。

AT89C52 is a low-power。

high-performance CMOS 8-bit microcontroller with 8K programmable Flash memory in the series。

Manufactured using Atmel's high-density non-volatile memory technology。

it is fully compatible with the industrial 80C51 product ns and pins。

The on-chip Flash allows for system programmable memory and is also suitable for nal programming。

With a nimble 8-bit CPU and system programmable Flash on a single chip。

the AT89C52 ___.The AT89C52 has the following standard features: 8K bytes of Flash。

256 bytes of RAM。

32-bit I/O lines。

three 16-bit timers/counters。

a loud 2-level interrupt structure。

full-duplex serial port。

on-chip oscillator and clock circuit。

In n。

theAT89C52 can be ced to 0Hz static logic n and supports two are-selectable power-saving modes。

AT89C52单片机简介

AT89C52是51系列单片机的一个型号,它是ATMEL公司死产的.之阳早格格创做AT89C52是一个矮电压,下本能CMOS 8位单片机,片内含8k bytes的可反复揩写的Flash只读步调死存器战256 bytes的随机存与数据死存器(RAM),器件采与ATMEL公司的下稀度、非易得性死存技能死产,兼容尺度MCS-51指令系统,片内置通用8位中央处理器战Flash死存单元,功能强盛的AT89C52单片机可为您提供许多较搀纯系统统制应用场合.AT89C52有40个引足,32其中部单背输进/输出(I/O)端心,共时内含2其中中断心,3个16位可编程定时计数器,2个齐单工串止通疑心,2个读写心线,AT89C52不妨依照惯例要领举止编程,但是不不妨正在线编程(S系列的才支援正在线编程).其将通用的微处理器战Flash死存器分离正在所有,特天是可反复揩写的Flash死存器可灵验天落矮开垦成本.兼容MCS51指令系统 · 8k可反复揩写(>1000次)Flash ROM· 32个单背I/O心 · 256x8bit里里RAM· 3个16位可编程定时/计数器中断 ·时钟频次0-24MHz· 2个串止中断 ·可编程UART串止通讲· 2其中部中断源 ·共6其中断源· 2个读写中断心线 · 3级加稀位·矮功耗空闲战掉电模式 ·硬件树立睡眠战唤醉功能AT89C52P为40 足单列曲插启拆的8 位通用微处理器,采与工业尺度的C51内核,正在里里功能及管足排布上与通用的8xc52 相共,其主要用于会散安排时的功能统制.功能包罗对于会散主IC 里里寄存器、数据RAM及中部交心等功能部件的初初化,会散安排统制,会散尝试图统制,白中遥控旗号IR的交支解码及与主板CPU通疑等.主要管足有:XTAL1(19 足)战XTAL2(18 足)为振荡器输进输出端心,中交12MHz 晶振.RST/Vpd(9 足)为复位输进端心,中交电阻电容组成的复位电路.VCC(40 足)战VSS(20 足)为供电端心,分别交+5V电源的正背端.P0~P3 为可编程通用I/O 足,其功能用途由硬件定义,正在本安排中,P0 端心(32~39 足)被定义为N1 功能统制端心,分别与N1的相映功能管足贯串交,13 足定义为IR输进端,10 足战11足定义为I2C总线统制端心,分别连交N1的SDAS(18足)战SCLS(19足)端心,12 足、27 足及28 足定义为握脚旗号功能端心,连交主板CPU 的相映功能端,用于目前制式的检测及会散安排状态加进的统制功能.P0 心P0 心是一组8 位漏极开路型单背I/O 心,也即天点/数据总线复用心.动做输出心用时,每位能吸支电流的办法启动8 个TTL逻辑门电路,对于端心P0 写“1”时,可动做下阻抗输进端用.正在考察中部数据死存器或者步调死存器时,那组心线分时变换天点(矮8 位)战数据总线复用,正在考察功夫激活里里上推电阻.正在Flash 编程时,P0 心交支指令字节,而正在步调校验时,输出指令字节,校验时,央供中交上推电阻.P1 心P1 是一个戴里里上推电阻的8 位单背I/O 心, P1 的输出慢冲级可启动(吸支或者输出电流)4 个TTL 逻辑门电路.对于端心写“1”,通过里里的上推电阻把端心推到下电仄,此时可做输出心.做输出心使用时,果为里里存留上推电阻,某个引足被中部旗号推矮时会输出一个电流(IIL).与AT89C51 分歧之处是,P1.0 战P1.1 还可分别动做定时/计数器2 的中部计数输进(P1.0/T2)战输进(P1.1/T2EX),拜睹表1.Flash 编程战步调校验功夫,P1 交支矮8 位天点.P2 心P2 是一个戴有里里上推电阻的8 位单背I/O 心,P2 的输出慢冲级可启动(吸支或者输出电流)4 个TTL 逻辑门电路.对于端心P2 写“1”,通过里里的上推电阻把端心推到下电仄,此时可做输出心,做输出心使用时,果为里里存留上推电阻,某个引足被中部旗号推矮时会输出一个电流(IIL).正在考察中部步调死存器或者16 位天点的中部数据死存器(比圆真止MOVX @DPTR 指令)时,P2 心支出下8 位天点数据.正在考察8 位天点的中部数据死存器(如真止MOVX @RI 指令)时,P2 心输出P2 锁存器的真质.Flash 编程或者校验时,P2亦交支下位天点战一些统制旗号.P3 心P3 心是一组戴有里里上推电阻的8 位单背I/O 心.P3 心输出慢冲级可启动(吸支或者输出电流)4 个TTL 逻辑门电路.对于P3 心写进“1”时,它们被里里上推电阻推下并可动做输进端心.此时,被中部推矮的P3 心将用上推电阻输出电流(IIL).P3 心除了动做普遍的I/O 心线中,更要害的用途是它的第二功能P3 心还交支一些用于Flash 闪速死存器编程战步调校验的统制旗号.RST复位输进.当振荡器处事时,RST引足出现二个呆板周期以上下电仄将使单片机复位.ALE/PROG当考察中部步调死存器或者数据死存器时,ALE(天点锁存允许)输出脉冲用于锁存天点的矮8 位字节.普遍情况下,ALE 仍以时钟振荡频次的1/6 输出牢固的脉冲旗号,果此它可对于中输出时钟或者用于定时脚段.要注意的是:每当考察中部数据死存器时将跳过一个ALE 脉冲.对于Flash 死存器编程功夫,该引足还用于输进编程脉冲(PROG).如有需要,可通过对于特殊功能寄存器(SFR)区中的8EH 单元的D0 位子位,可克制ALE 支配.该位子位后,惟有一条MOVX 战MOVC指令才搞将ALE 激活.别的,该引足会被微小推下,单片机真止中部步调时,应树立ALE 克制位无效.PSEN步调储藏允许(PSEN)输出是中部步调死存器的读选通旗号,当AT89C52 由中部步调死存器与指令(或者数据)时,每个呆板周期二次PSEN 灵验,即输出二个脉冲.正在此功夫,当考察中部数据死存器,将跳过二次PSEN 旗号.EA/VPP中部考察允许.欲使CPU 仅考察中部步调死存器(天点为0000H—FFFFH),EA 端必须脆持矮电仄(交天).需注意的是:如果加稀位LB1 被编程,复位时里里会锁存EA 端状态.如EA端为下电仄(交Vcc端),CPU 则真止里里步调死存器中的指令.Flash 死存器编程时,该引足加上+12V 的编程允许电源Vpp,天然那必须是该器件是使用12V 编程电压Vpp.XTAL1振荡器反相搁大器的及里里时钟爆收器的输进端.XTAL2振荡器反相搁大器的输出端.特殊功能寄存器正在AT89C52 片内死存器中,80H-FFH 共128 个单元为特殊功能寄存器(SFE),SFR 的天点空间映象如表2 所示.并不是所有的天点皆被定义,从80H—FFH 共128 个字节惟有一部分被定义,另有相称一部分不定义.对于不定义的单元读写将是无效的,读出的数值将不决定,而写进的数据也将拾得.不该将数据“1”写进已定义的单元,由于那些单元正在将去的产品中大概给予新的功能,正在那种情况下,复位后那些单元数值经常“0”.AT89C52除了与AT89C51所有的定时/计数器0 战定时/计数器1 中,还减少了一个定时/计数器2.定时/计数器2 的统制战状态位位于T2CON(拜睹表3)T2MOD(拜睹表4),寄存器对于(RCAO2H、RCAP2L)是定时器2 正在16 位捕获办法或者16 位自动沉拆载办法下的捕获/自动沉拆载寄存器.数据死存器AT89C52 有256 个字节的里里RAM,80H-FFH 下128 个字节与特殊功能寄存器(SFR)天点是沉叠的,也便是下128字节的RAM 战特殊功能寄存器的天点是相共的,但是物理上它们是合并的.当一条指令考察7FH 以上的里里天点单元时,指令中使用的觅址办法是分歧的,也即觅址办法决断是考察下128 字节RAM 仍旧考察特殊功能寄存器.如果指令是曲交觅址办法则为考察特殊功能寄存器.比圆,底下的曲交觅址指令考察特殊功能寄存器0A0H(即P2 心)天点单元.MOV 0A0H,#data间交觅址指令考察下128 字节RAM,比圆,底下的间交觅址指令中,R0 的真质为0A0H,则考察数据字节天点为0A0H,而不是P2 心(0A0H).MOV @R0,#data堆栈支配也是间交觅址办法,所以,下128 位数据RAM 亦可动做堆栈区使用.·定时器0战定时器1:AT89C52的定时器0战定时器1 的处事办法与AT89C51 相共.定时器2定时器2 是一个16 位定时/计数器.它既可当定时器使用,也可动做中部事变计数器使用,其处事办法由特殊功能寄存器T2CON(如表3)的C/T2 位采用.定时器2 有三种处事办法:捕获办法,自动沉拆载(进与或者背下计数)办法战波特率爆收器办法,处事办法由T2CON 的统制位去采用.定时器2 由二个8 位寄存器TH2 战TL2 组成,正在定时器处事办法中,每个呆板周期TL2 寄存器的值加1,由于一个机器周期由12 个振荡时钟形成,果此,计数速率为振荡频次的1/12.正在计数处事办法时,当T2 引足上中部输进旗号爆收由1 至0 的下落沿时,寄存器的值加1,正在那种处事办法下,每个呆板周期的5SP2 功夫,对于中部输进举止采样.若正在第一个呆板周期中采到的值为1,而正在下一个呆板周期中采到的值为0,则正在紧跟着的下一个周期的S3P1 功夫寄存器加1.由于辨别1 至0 的跳变需要2 个呆板周期(24 个振荡周期),果此,最下计数速率为振荡频次的1/24.为保证采样的精确性,央供输进的电仄正在变更前起码脆持一个完备周期的时间,以包管输进旗号起码被采样一次.捕获办法正在捕获办法下,通过T2CON 统制位EXEN2 去采用二种办法.如果EXEN2=0,定时器2 是一个16 位定时器或者计数器,计数溢出时,对于T2CON 的溢出标记TF2 置位,共时激活中断.如果EXEN2=1,定时器2 完毕相共的支配,而当T2EX 引足中部输进旗号爆收1 至0 背跳变时,也出现TH2 战TL2 中的值分别被捕获到RCAP2H 战RCAP2L 中.其余,T2EX 引足旗号的跳变使得T2CON 中的EXF2 置位,与TF2 相仿,EXF2 也会激活中断.捕获办法如图4 所示.自动沉拆载(进与或者背下计数器)办法当定时器2处事于16位自动沉拆载办法时,能对于其编程为进与或者背下计数办法,那个功能可通过特殊功能寄存器T2CON(睹表5)的DCEN 位(允许背下计数)去采用的.复位时,DCEN 位子“0”,定时器2 默认树立为进与计数.当DCEN置位时,定时器2 既可进与计数也可背下计数,那与决于T2EX 引足的值,拜睹图5,当DCEN=0 时,定时器2 自动树立为进与计数,正在那种办法下,T2CON 中的EXEN2 统制位有二种采用,若EXEN2=0,定时器2 为进与计数至0FFFFH 溢出,置位TF2 激活中断,共时把16 位计数寄存器RCAP2H 战RCAP2L沉拆载,RCAP2H 战RCAP2L 的值可由硬件预置.若EXEN2=1,定时器2 的16 位沉拆载由溢出或者中部输进端T2EX 从1 至0 的下落沿触收.那个脉冲使EXF2 置位,如果中断允许,共样爆收中断.定时器2 的中断出心天点是:002BH ——0032H .当DCEN=1 时,允许定时器2 进与或者背下计数,如图6 所示.那种办法下,T2EX 引足统制计数器目标.T2EX 引足为逻辑“1”时,定时器进与计数,当计数0FFFFH 进与溢出时,置位TF2,共时把16 位计数寄存器RCAP2H 战RCAP2L 沉拆载到TH2 战TL2 中. T2EX 引足为逻辑“0”时,定时器2 背下计数,当TH2 战TL2 中的数值等于RCAP2H 战RCAP2L中的值时,计数溢出,置位TF2,共时将0FFFFH 数值沉新拆进定时寄存器中.当定时/计数器2 进与溢出或者背下溢出时,置位EXF2 位.波特率爆收器当T2CON(表3)中的TCLK 战RCLK 置位时,定时/计数器2 动做波特率爆收器使用.如果定时/计数器2 动做收支器或者交支器,其收支战交支的波特率不妨是分歧的,定时器1 用于其余功能,如图7 所示.若RCLK 战TCLK 置位,则定时器2处事于波特率爆收器办法.波特率爆收器的办法与自动沉拆载办法相仿,正在此办法下,TH2 翻转使定时器2 的寄存器用RCAP2H 战RCAP2L 中的16位数值沉新拆载,该数值由硬件树立.正在办法1 战办法3 中,波特率由定时器2 的溢出速率根据下式决定:办法1战3的波特率=定时器的溢出率/16定时器既能处事于定时办法也能处事于计数办法,正在大普遍的应用中,是处事正在定时办法(C/T2=0).定时器2 动做波特率爆收器时,与动做定时器的支配是分歧的,常常动做定时器时,正在每个呆板周期(1/12 振荡频次)寄存器的值加1,而动做波特率爆收器使用时,正在每个状态时间(1/2 振荡频次)寄存器的值加1.波特率的估计公式如下:办法1战3的波特率=振荡频次/{32*[65536-(RCP2H,RCP2L)]}式中(RCAP2H,RCAP2L)是RCAP2H 战RCAP2L 中的16 位无标记数.定时器2 动做波特率爆收器使用的电路如图7 所示.T2CON 中的RCLK 或者TCLK=1 时,波特率处事办法才灵验.正在波特率爆收器处事办法中,TH2 翻转不克不迭使TF2 置位,故而不爆收中断.但是若EXEN2 置位,且T2EX 端爆收由1 至0 的背跳变,则会使EXF2 置位,此时本去不克不迭将(RCAP2H,RCAP2L)的真质沉新拆进TH2 战TL2 中.所以,当定时器2 做为波特率爆收器使用时,T2EX 可动做附加的中部中断源去使用.需要注意的是,当定时器2 处事于波特率器时,动做定时器运止(TR2=1)时,本去不克不迭考察TH2 战TL2.果为此时每个状态时间定时器皆市加1,对于其读写将得到一个不决定的数值.然而,对于RCAP2 则可读而不可写,果为写进支配将是沉新拆载,写进支配大概令写战/或者沉拆载堕落.正在考察定时器2或者RCAP2 寄存器之前,应将定时器关关(扫除TR2).可编程时钟输出定时器2 可通过编程从P1.0 输出一个占空比为50%的时钟旗号,如图8 所示.P1.0 引足除了是一个尺度的I/O 心中,还不妨通过编程使其动做定时/计数器2 的中部时钟输进战输出占空比50%的时钟脉冲.当时钟振荡频次为16MHz 时,输出时钟频次范畴为61Hz—4MHz.当树立定时/计数器2 为时钟爆收器时,C/T2(T2CON .1)=0,T2OE (T2MOD.1) =1,必须由TR2(T2CON.2)开用或者停止定时器.时钟输出频次与决于振荡频次战定时器2 捕获寄存器(RCAP2H,RCAP2L)的沉新拆载值,公式如下:输出时钟频次=振荡器频次/{4*[65536-(RCP2H,RCP2L)]}正在时钟输出办法下,定时器2 的翻转不会爆收中断,那个个性与动做波特率爆收器使用时相仿.定时器2 动做波特率爆收器使用时,还可动做时钟爆收器使用,但是需要注意的是波特率战时钟输出频次不克不迭合并决定,那是果为它们共使用RCAP2L战RCAP2L.UART AT89C52的UART 处事办法与AT89C51 处事办法相共.中断AT89C52 公有6 其中断背量:二其中中断(INT0 战INT1),3 个定时器中断(定时器0、1、2)战串止心中断.所有那些中断源如图9 所示.那些中断源可通太过别树立博用寄存器IE 的置位或者浑0 去统制每一其中断的允许或者克制.IE 也有一个总克制位EA,它能统制所有中断的允许或者克制.注意表5 中的IE.6 为死存位,正在AT89C51 中IE.5 也是死存位.步调员不该将“1”写进那些位,它们是将去AT89 系列产品动做扩展用的.定时器2 的中断是由T2CON 中的TF2 战EXF2 逻辑或者爆收的,当转背中断服务步调时,那些标记位不克不迭被硬件扫除,究竟上,服务步调需决定是TF2 或者EXF2 爆收中断,而由硬件扫除中断标记位.定时器0 战定时器1 的标记位TF0 战TF1 正在定时器溢出那个呆板周期的S5P2 状态置位,而会正在下一个呆板周期才查询到该中断标记.然而,定时器2 的标记位TF2 正在定时器溢出的那个呆板周期的S2P2 状态置位,并正在共一个呆板周期内查询到该标记.时钟振荡器AT89C52 中有一个用于形成里里振荡器的下删益反相搁大器,引足XTAL1 战XTAL2 分别是该搁大器的输进端战输出端.那个搁大器与动做反馈元件的片中石英晶体或者陶瓷谐振器所有形成自激振荡器,振荡电路拜睹图10.中交石英晶体(或者陶瓷谐振器)及电容C1、C2 交正在搁大器的反馈回路中形成并联振荡电路.对于中交电容C1、C2 虽然不格中庄重的央供,但是电容容量的大小会沉微做用振荡频次的下矮、振荡器处事的宁静性、起振的易易步调及温度宁静性,如果使用石英晶体,咱们推荐电容使用30pF±10pF,而如使用陶瓷谐振器修议采用40pF±10F.用户也不妨采与中部时钟.采与中部时钟的电路如图10 左图所示.那种情况下,中部时钟脉冲交到XTAL1 端,即里里时钟爆收器的输进端,XTAL2 则悬空.由于中部时钟旗号是通过一个2 分频触收器后动做里里时钟旗号的,所以对于中部时钟旗号的占空比不特殊央供,但是最小下电仄持绝时间战最大的矮电仄持绝时间应切合产品技能条件的央供.空闲节电模式正在空闲处事模式状态, CPU 自己处于睡眠状态而所有片内的中设仍脆持激活状态,那种办法由硬件爆收.此时,共时将片内RAM 战所有特殊功能寄存器的真质冻结.空闲模式可由所有允许的中断哀供或者硬件复位末止.由硬件复位末止空闲状态只需二个呆板周期灵验复位旗号,正在此状态下,片内硬件克制考察里里RAM,但是不妨考察端心引足,当用复位末止空闲办法时,为预防大概对于端心爆收不料写进,激活空闲模式的那条指令后一条指令不该是一条对于端心或者中部死存器的写进指令.掉电模式正在掉电模式下,振荡器停止处事,加进掉电模式的指令是末尾一条被真止的指令,片内RAM 战特殊功能寄存器的真质正在末止掉电模式前被冻结.退出掉电模式的唯一要领是硬件复位,复位后将沉新定义局部特殊功能寄存器,但是不改变RAM中的真质,正在Vcc回复到仄常处事电仄前,复位应无效,且必须脆持一定时间以使振荡器沉开用并宁静处事.步调死存器的加稀AT89C52 有3 个步调加稀位,可对于芯片上的3 个加稀位LB1、LB2、LB3 举止编程(P)或者不编程(U)去得到.当加稀位LB1 被编程时,正在复位功夫,EA 端的逻辑电仄被采样并锁存,如果单片机上电后背去不复位,则锁存起的初初值是一个随机数,且那个随机数会背去死存到真真复位为止.为使单片机能仄常处事,被锁存的EA电仄值必须与该引足目前的逻辑电仄普遍.别的,加稀位只可通过整片揩除的要领扫除.Flash死存器的编程AT89C52单片机里里有8k字节的Flash PEROM,那个Flash 死存阵列出厂时已处于揩除状态(即所有死存单元的真质均为FFH),用户随时可对于其举止编程.编程交心可交支下电压(+12V)或者矮电压(Vcc)的允许编程旗号.矮电压编程模式切合于用户正在线编程系统,而下电压编程模式可与通用EPROM 编程器兼容.AT89C52 单片机中,有些属于矮电压编程办法,而有些则是下电压编程办法,用户可从芯片上的型号战读与芯片内的签字字节赢得该疑息.AT89C52 的步调死存器阵列是采与字节写进办法编程的,屡屡写进一个字节,要对于所有芯片内的PEROM 步调死存器写进一个非空字节,必须使用片揩除的办法将所有死存器的真质扫除.编程要领编程前,须按表9 战图11 所示树立佳天点、数据及统制旗号, AT89C52 编程要领如下:1.正在天点线上加上要编程单元的天点旗号.2.正在数据线上加上要写进的数据字节.3.激活相映的统制旗号.4.正在下电压编程办法时,将EA/Vpp 端加上+12V 编程电压.5.每对于Flash 死存阵列写进一个字节或者每写进一个步调加稀位,加上一个ALE/PROG 编程脉冲.每个字节写进周期是自己定时的,常常约为1.5ms.沉复1—5 步调,改变编程单元的天点战写进的数据,曲到局部文献编程中断.数据查询AT89C52 单片机用Data Palling 表示一个写周期中断为个性,正在一个写周期中,如需读与末尾写进的一个字节,则出的数据的最下位(P0.7)是本去写进字节最下位的反码.写周期完毕后,所输出的数据是灵验的数据,即可加进下一个字节的写周期,写周期开初后,Data Palling 大概随时灵验.Ready/Busy:字节编程的进度可通过“RDY/BSY 输出旗号监测,编程功夫,ALE 形成下电仄“H”后,P3.4(RDY/BSY)端电仄被推矮,表示正正在编程状态(闲状态).编程完毕后,P3.4 形成下电仄表示准备便绪状态.·步调校验:如果加稀位LB1、LB2 不举止编程,则代码数据可通过天点战数据线读回本编写的数据,采与如图12的电路.加稀位不可曲交校验,加稀位的校验可通过对于死存器的校验战写进状态去考证.芯片揩除:利用统制旗号的精确推拢(表6)并脆持ALE/PROG 引足10mS 的矮电仄脉冲宽度即可将PEROM 阵列(4k字节)战三个加稀位整片揩除,代码阵列正在片揩除支配中将所有非空单元写进“1”,那步调需再编程之前举止.·读片内签字字节:AT89C52 单片机内有3 个签字字节,天点为030H、031H 战032H.用于声明该器件的厂商、型号战编程电压.读AT89C52 签字字节需将P3.6 战P3.7 置逻辑矮电仄,读签字字节的历程战单元030H、031H 及032H 的仄常校验相仿,只返回值意思如下:(030H)=1EH 声明产品由ATMEL公司制制.(031H)=52H 声明为AT89C52 单片机.(032H)=FFH 声明为12V 编程电压.(032H)=05H 声明为5V 编程电压.。

AT89C52单片机介绍

AT89C52单片机介绍

AT89C52是Atmel公司生产的一款经典的8位单片机。

它采用MCS-51系列内核,具有高性能、低功耗和强大的外设功能。

AT89C52是AT89C51的改进版本,具有更高的运行速度和更大的存储空间。

首先,AT89C52采用了高性能的CMOS技术,工作频率高达40MHz,可以实现高效的数据处理和实时控制。

与普通的单片机相比,它具有更快的响应速度和更高的运算能力,可以满足复杂控制系统的要求。

其次,AT89C52具有8KB的内部闪存程序存储器,可以存储用户编写的程序代码。

它还具有256字节的RAM内存和128个IO口,可用于连接各种外部设备和传感器。

此外,AT89C52还支持多种通信接口,如UART、SPI和I2C,方便与其他设备进行数据交换和通信。

此外,AT89C52还具有丰富的开发资源和工具支持。

Atmel公司提供了一套完整的开发套件,包括编译器、调试器和仿真器等,为用户提供方便和高效的开发环境。

并且,AT89C52的软件编程接口也非常友好,可以使用C语言或汇编语言进行编程,灵活性很高。

总之,AT89C52是一款功能强大、性能稳定的8位单片机。

它具有高速运算能力、丰富的外设功能和灵活的IO口控制。

它可以广泛应用于各种控制系统、仪器仪表、家电和智能设备等领域。

同时,它的开发环境和编程接口也很友好,为用户提供了方便和高效的开发工具。

AT89C51与AT89C52简介

AT89C51简介AT89C51是一种带4K字节FLASH存储器(FPEROM—Flash Programmable and Erasable Read Only Memory)的低电压、高性能CMOS 8位微处理器,俗称单片机。

AT89C2051是一种带2K字节闪存可编程可擦除只读存储器的单片机。

单片机的可擦除只读存储器可以反复擦除1000次。

该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89C51是一种高效微控制器,AT89C2051是它的一种精简版本。

AT89C单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

外形及引脚排列如图所示主要特性:·与MCS-51 兼容·4K字节可编程FLASH存储器·寿命:1000写/擦循环·数据保留时间:10年·全静态工作:0Hz-24MHz·三级程序存储器锁定·128×8位内部RAM·32可编程I/O线·两个16位定时器/计数器·5个中断源·可编程串行通道·低功耗的闲置和掉电模式·片内振荡器和时钟电路管脚说明:VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P0口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

AT89C52单片机简介

AT89C52单片机简介AT89C52是___生产的51系列单片机之一。

它是一个低电压、高性能的CMOS8位单片机,内置8kbytes可反复擦写的Flash只读程序存储器和256bytes的随机存取数据存储器(RAM)。

该器件采用高密度、非易失性存储技术生产,兼容标准MCS-51指令系统。

AT89C52单片机功能强大,适用于许多较复杂的系统控制应用场合。

该单片机有40个引脚,其中32个是外部双向输入/输出(I/O)端口。

此外,它还内含2个外中断口,3个16位可编程定时计数器,2个全双工串行通信口和2个读写口线。

AT89C52可以按照常规方法进行编程,但不支持在线编程(只有S系列的单片机支持在线编程)。

AT89C52将通用的微处理器和Flash存储器结合在一起,特别是可反复擦写的Flash存储器可有效地降低开发成本。

该单片机兼容MCS51指令系统,具有以下特点:8k可反复擦写(>1000次)FlashROM32个双向I/O口256x8bit内部RAM3个16位可编程定时/计数器中断时钟频率0-24MHz2个串行中断可编程UART串行通道2个外部中断源,共6个中断源2个读写中断口线3级加密位低功耗空闲和掉电模式软件设置睡眠和唤醒功能P2口是一个8位双向I/O口,带有内部上拉电阻。

它的输出缓冲级可以驱动4个TTL逻辑门电路。

当对P2口写入“1”时,内部上拉电阻会将端口拉高,使其可以作为输入口。

当被外部信号拉低时,由于存在上拉电阻,会输出一个电流(IIL)。

在访问外部程序存储器或16位地址的外部数据存储器时,P2口会输出高8位地址数据。

而在访问8位地址的外部数据存储器时,P2口会输出P2锁存器的内容。

此外,P2口还会接收高位地址和一些控制信号,用于Flash编程或校验。

P3口也是一个带有内部上拉电阻的8位双向I/O口。

它的输出缓冲级可以驱动4个TTL逻辑门电路。

当对P3口写入“1”时,内部上拉电阻会将端口拉高,使其可以作为输入端口。

单片机89C52中英文对照翻译(经典版)

AT89C52 internal structure analysis DescriptionThe AT89S52 is a low-power, high-performance CMOS 8-bit microcontroller with 8Kbytes of in-system programmable Flash memory. The device is manufactured using Atmel’s high-density nonvolatile memory technology and is compatible with the industry-standard 80C51 instruction set and pinout. The on-chip Flash allows the programmemory to be reprogrammed in-system or by a conventional nonvolatile memory programmer. By combining a versatile 8-bit CPU with in-system programmable Flash ona monolithic chip, the Atmel AT89S52 is a powerful microcontroller which provides a highly-flexible and cost-effective solution to many embedded control applications. The AT89S52 provides the following standard features: 8K bytes of Flash, 256 bytes of RAM, 32 I/O lines, Watchdog timer, two data pointers, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full duplex serial port, on-chip oscillator,and clock circuitry. In addition, the AT89S52 is designed with static logic for operationdown to zero frequency and supports two software selectable power saving modes.The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, andinterrupt system to continue functioning. The Power-down mode saves the RAM contentsbut freezes the oscillator, disabling all other chip functions until the next interruptor hardware reset.Pin DescriptionVCCSupply voltage.GNDGround.Port 0Port 0 is an 8-bit open drain bidirectional I/O port. As anoutput port, eachpin can sink eight TTL inputs. When 1sare written to port 0 pins, the pins can be used as highimpedanceinputs.Port 0 can also be configured to be the multiplexed loworder address/data bus during accesses to external program and data memory. In this mode, P0 has internal pullups.Port 0 also receives the code bytes during Flash programming and outputs the code bytes during program verification.External pullups are required during program verification.Port 1Port 1 is an 8-bit bidirectional I/O port with internal pullups.The Port 1 output buffers can sink/source four TTL inputs.When 1s are written to Port 1 pins, they are pulled high by the internal pullups and can be used as inputs. As inputs,Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pullups. In addition, P1.0 and P1.1 can be configured to be the timer/counter 2 external count input (P1.0/T2) and the timer/counter 2 trigger input (P1.1/T2EX), respectively, asshown in the following table.Port 1 also receives the low-order address bytes duringFlash programming and verification.Port 2Port 2 is an 8-bit bidirectional I/O port with internal pullups.The Port 2 output buffers can sink/source four TTL inputs.When 1s are written to Port 2 pins, they are pulled high bythe internal pullups and can be used as inputs. As inputs,Port 2 pins that are externally being pulled low will sourcecurrent (IIL) because of the internal pullups.Port 2 emits the high-order address byte during fetchesfrom external program memory and during accesses toexternal data memory that use 16-bit addresses (MOVX @DPTR). In this application, Port 2 uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register. Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.Port 3Port 3 is an 8-bit bidirectional I/O port with internal pullups.The Port 3 output buffers can sink/source four TTL inputs.When 1s are written to Port 3pins, they are pulled high by the internal pullups and can be used as inputs. As inputs,Port 3 pins that are externally being pulled low will source current (IIL) because of the pullups.Port 3 also serves the functions of various special features of the AT89S52, as shown in the following table.Port 3 also receives some control signals for Flash programming and verification.RSTReset input. A high on this pin for two machine cycles while the oscillator is running resets the device. This pin drives High for 96 oscillator periods after the Watchdog times out.The DISRTO bit in SFR AUXR (address 8EH) can be used to disable this feature. In the default state of bit DISRTO,the RESET HIGH out feature is enabled.ALE/PROGAddress Latch Enable (ALE) is an output pulse for latching the low byte of the address during accesses to external memory. This pin is also the program pulse input (PROG) during Flash programming.In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external data memory.If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Otherwise, the pin is weakly pulled high. Setting the ALE-disable bit has noeffect if the microcontroller is in external execution mode.PSENProgram Store Enable (PSEN) is the read strobe to externalprogram memory.When the AT89S52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.EA/VPPExternal Access Enable. EA must be strapped to GND in order to enable the device to fetch code from external program memory locations starting at 0000Hup to FFFFH.Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset.EA should be strapped to VCC for internal program executions.This pin also receives the 12-volt programming enable voltage (VPP) during Flash programming.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting oscillator amplifier.Special Function RegistersA map of the on-chip memory area called the Special FunctionRegister (SFR) space is shown in Table 1.Note that not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip.Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate er software should not write 1s to these unlisted locations,since they may be used in future products to invokenew features. In that case, the reset or inactive values of the new bits will always be 0.Timer 2 Registers:Control and status bits are contained in registers T2CON (shown in Table 2) and T2MOD (shown in Table 3) for Timer 2. The register pair (RCAP2H, RCAP2L) are the Capture/Reload registers for Timer 2 in 16-bit capture mode or 16-bit auto-reload mode.Interrupt Registers:The individual interrupt enable bits are in the IE register. Two priorities can be set for each ofthe six interrupt sources in the IP register.Memory OrganizationMCS-51 devices have a separate address space for Program and Data Memory. Up to 64K bytes each of external Program and Data Memory can be addressed.Program MemoryIf the EA pin is connected to GND, all program fetches are directed toexternal memory.On the AT89S52, if EA is connected to VCC, program fetches to addresses 0000H through 1FFFH are directed to internal memory and fetches to addresses 2000H through FFFFH are to external memory.Data MemoryThe AT89S52 implements 256 bytes of on-chip RAM. The upper 128 bytes occupy a parallel address space to the Special Function Registers. This means that the upper 128 bytes have the same addresses as the SFR space but are physically separate from SFR space. When an instruction accesses an internal location aboveaddress 7FH, the address mode used in the instructionspecifies whether the CPU accesses the upper 128 bytes of RAM or the SFR space. Instructions which use direct addressing access of the SFR space.For example, the following direct addressing instruction accesses the SFR at location 0A0H (which is P2). MOV 0A0H, #dataInstructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 cont ains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).MOV @R0, #dataNote that stack operations are examples of indirectaddressing, so the upper 128 bytes of data RAM are availableas stack space.Watchdog Timer(One-time Enabled with Reset-out)The WDT is intended as a recovery method in situationswhere the CPU may be subjected to software upsets. The WDT consists of a 13-bit counter and the Watchdog Timer Reset (WDTRST) SFR. The WDT is defaulted to disable from exiting reset. To enable the WDT, a user must write01EH and 0E1H in sequence to the WDTRST register (SFR location 0A6H). When the WDT is enabled, it will increment every machine cycle while the oscillator is running. The WDT timeout period is dependent on the external clock frequency. There is no way to disable the WDT except through reset (either hardware reset or WDT overflow reset). When WDT overflows, it will drive anoutput RESET HIGH pulse at the RST pin.Using the WDTTo enable the WDT, a user must write 01EH and 0E1H in sequence to the WDTRST register (SFR location 0A6H).When the WDT is enabled, the user needs to service it by writing 01EH and 0E1H to WDTRST to avoid a WDT overflow.The 13-bit counter overflows when it reaches 8191(1FFFH), and this will reset the device. When the WDT is enabled, it will increment every machine cycle while the oscillator is running. This means the user must reset the WDT at least every 8191 machine cycles. To reset the WDT the user must write 01EH and 0E1H to WDTRST. WDTRST is a write-only register. The WDT counter cannot be read or written. When WDT overflows, it will generate an output RESET pulse at the RST pin. The RESET pulse duration is 96xTOSC, where TOSC=1/FOSC. To make the best use of the WDT, it should be serviced in those sections of code that will periodically be executed within the time required to prevent a WDT reset.WDT During Power-down and IdleIn Power-down mode the oscillator stops, which means the WDT also stops. While in Power-down mode, the user does not need to service the WDT. There are two methods of exiting Power-down mode: by a hardware reset or via a level-activated external interrupt which is enabled prior toentering Power-down mode. When Power-down is exited with hardware reset, servicing the WDT should occur as it normally does whenever the AT89S52 is reset. Exiting Power-down with an interrupt is significantly different. The interrupt is held low long enough for the oscillator to stabilize. When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from resetting the device while the interrupt pin is held low, the WDT is not started until the interrupt is pulled high. It is suggested that the WDT be reset during the interrupt service for the interrupt used to exit Power-down mode.To ensure that the WDT does not overflow within a few states of exiting Power-down, it is best to reset the WDT just before entering Power-down mode. Before going into the IDLE mode, the WDIDLE bit in SFR AUXR is used to determine whether theWDT continues tocount if enabled. The WDT keeps counting during IDLE (WDIDLE bit = 0) as the default state. To prevent the WDT from resetting the AT89S52 while in IDLE mode, the user should always set up a timer that will periodically exit IDLE, service the WDT, and reenter IDLE mode. With WDIDLE bit enabled, the WDT will stop to count in IDLE mode and resumes the count upon exit from IDLE.UARTThe UART in the AT89S52 operates the same way as the UART in the AT89C51 and AT89C52. For further information on the UART operation, refer to the ATMEL Web site (). From the home page, select ‘Products’,then ‘8051-Architecture Flash Microcontroller’, then‘Product Overview’.Timer 0 and 1Timer 0 and Timer 1 in the AT89S52 operate the same wayas Timer 0 and Timer 1 in the AT89C51 and AT89C52. Forfurther information on the timers’ operation, refer to the ATMEL Web site (). From the home page, select ‘Products’, then ‘8051-Architecture Flash Microcontroller’, then ‘Product Overview’.Timer 2Timer 2 is a 16-bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit C/T2 in the SFR T2CON (shown in Table 2). Timer 2 has three operating modes: capture, auto-reload (up or down counting), and baud rate generator. The modes are selected by bits in T2CON, as shown in Table 3. Timer 2 consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.In the Counter function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samplesshow a high in one cycle and a low in the next cycle, thecount is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Sin ce two machine cycles (24 oscillator periods) are required to recognize a 1-to-0 transition, the maximum count rate is 1/24 of the oscillator frequency.To ensure that a given level is sampled at least once before it changes, the level should be held for at leastone full machine cycle.Capture ModeIn the capture mode, two options are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 is a 16-bit timer or counter which upon overflow sets bit TF2 in T2CON.This bit can then be used to generate an interrupt. If EXEN2 = 1, Timer 2 performs the same operation, but a 1- to-0 transition at external input T2EX also causes the current value in TH2 and TL2 to be captured into RCAP2H and RCAP2L, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. The EXF2 bit, like TF2, can generate an interrupt. The capture mode is illustrated in Figure 5.Auto-reload (Up or Down Counter)Timer 2 can be programmed to count up or down when configured in its 16-bit auto-reload mode. This feature is invoked by the DCEN (Down Counter Enable) bit located in the SFR T2MOD (see Table 4). Upon reset, the DCEN bit is set to 0 so that timer 2 will default to count up. When DCEN is set, Timer 2 can count up or down, depending on the value of the T2EX pin.Figure 6 shows Timer 2 automatically counting up when DCEN=0. In this mode, two options are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 counts up to 0FFFFH and then sets the TF2 bit upon overflow. The overflow also causes the timer registers to be reloaded with the 16-bit value in RCAP2H and RCAP2L. The values in Timer in Capture ModeRCAP2H and RCAP2L are preset by software. If EXEN2 = 1, a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at external input T2EX. This transition also sets the EXF2 bit. Both the TF2 and EXF2 bits can generate an interrupt if enabled. Setting the DCEN bit enables Timer 2 to count up or down,as shown in Figure 6. In thismode, the T2EX pin controls the direction of the count. A logic 1 at T2EX makes Timer 2 count up. The timer will overflow at 0FFFFH and set the TF2 bit. This overflow also causes the 16-bit value in RCAP2H and RCAP2L to be reloaded into the timer registers,TH2 and TL2, respectively. A logic 0 at T2EX makes Timer 2 count down. The timer underflows when TH2 and TL2 equal the values stored in RCAP2H and RCAP2L. The underflow sets the TF2 bit and causes 0FFFFH to be reloaded into the timer registers. The EXF2 bit toggles whenever Timer 2 overflows or underflows and can be used as a 17th bit of resolution. In this operating mode, EXF2 does not flag an interrupt.译文:89C52的内部结构分析功能特性描述AT89S52是一种低功耗、高性能CMOS8位微控制器,具有8K 在系统可编程Flash 存储器。

中英文翻译 AT89C52 单片机

AT89C2051AT89C2051 Reference Manual AT89C2051 is made in the ATMEL Corporation, which is the low-voltage, high-performance CMOS8-bit microcontroller.Tablets containing repeated 2k bytes of program memory erasable read-only (PEROM) and random 128bytes data memory (RAM), device using ATMEL's high density, non-volatile memory technology, Compatible with the standard of MCS-51 instruction set, built-chip 8-bit general-purpose central processing unit and repeatedly write the Flash memory, which can effectively reduce the development costs. AT89C2051 features a powerful single-chip can provide cost-effective in many Applications.AT89C2051 MCU MCU is a series of 51 members, is the 8051 version of SCM. Internal comes with a programmable EPROM 2 k bytes of high-performance microcontrollers. With the industry standard MCS-51 orders and pin-compatible, so it is a powerful micro-controllers, many embedded control applications, it provides a highly flexible and effective solutions. AT89C2051 has the following characteristics: 2 k bytes EPROM, 128 bytes RAM, 15 I / O lines, two 16 regular / counter, two five vector interrupt structure, a full two-way serial port, and includes Precision analog comparator and on-chip oscillator, a 4.25 V to 5.5 V voltage scope of work and 12 MHz/24MHz frequency, and also offers the encryption array of two program memory locking, power-down and the clock circuit. In addition, AT89C2051 also supports two kinds of software-selectable power-saving mode power supply. During my free time, CPU stop and let RAM, timing / counter, serial port and interrupt system to continue to work. Power-down can preserve the contents of RAM, but will stop oscillator chip-to prohibit all the other functions until the next hardware reset.AT89C2051 have two 16 time / counter register Timer0t Timer1. As a timer, each machine cycle register an increase, such registers to counting machine cycle. Because a machine cycle is 12 oscillator cycles, the count rate is the frequency oscillator 1 / 12. As a counter, the register in the corresponding external input pin P3.4/T0 and P3.5/T1 emerged from the 1-0 when the changes by 1. Two machine cycle because of the need to identify a 1-0 change, the largest count rate is the frequency oscillator 1 / 24, the external input P3.2/INT0 and P3.3/INT1 programming, for Measuring the pulse width of the door.Therefore, AT89C2051 constitute the SCM system is a simple structure, the costof the cheapest, most efficient micro-control system, eliminating the external RAM, ROM and interface devices, reducing hardware costs, cost savings, improved The cost-effective system.Clock circuitMCU clock signal used to provide various micro-chip microcontroller operation of the benchmark time, the clock signal is usually used by the form of two circuits: the internal and external shocks oscillation. MCS-51 has a microcontroller internal oscillator for a reverse of the high-gain amplifier, pin XTALl and XTAL2 are here to enlarge the electrical inputs and outputs, as in-house approach, a simple circuit, from the clock Signal relatively stable, and actually used often in this way, as shown in Figure 3-1 in its external crystal oscillator (crystal) or ceramic resonator constituted an internal oscillation, on-chip high-gain amplifier and a reverse Feedback components of the chip quartz crystal or ceramic resonator together to form a self oscillator and generate oscillation clock pulse. Figure 3-1 in the external crystal and capacitors C1 and C2 constitute a parallel resonant circuits, their stability from the oscillation frequency, rapid start-up role, and its value are about 33 PF, crystal frequency of elections 12 MHz.Reset CircuitIn order to initialize the internal MCU some special function register to be reset by the way, will reset after the CPU and system components identified in the initial state, and from the initial state began work properly. MCU is reset on the circuit to achieve, in the normal operation of circumstances, as long as the RST-pin on a two machine cycle time over the high, can cause system reset, but if sustained for the RST-pin HIGH, in a circle on the MCU reset state. After the system will reset input / output (I / 0) home port register for the FFH, stack pointer SP home for 07 H, SBUF built-in value for the indefinite, all the rest of the register-0, the status of internal RAM from the impact of reduction, On the system, when the contents of RAM is volatile. Reset operation There are two situations in which a power-on reset and manual (switch) reduction. The system uses a power-on reset mode. Figure 3-1 in the R0 and C0 formed a power-on reset circuit, and its value for R for 8.2 K, C for the 10 uF.Main features:Compatible the MCS51 command system;Contains the 2KB memory re-programming FLASH (1000);2.7 ~ 6V voltage range;the whole Static work: 0Hz ~ 24KHz;Secrets 2 Program Memory Lock128 × 8-bit internal RAM15 programmable I / O linesTwo 16-bit timer / counter6 interrupt sources, two external interrupt sourcesProgrammable Serial ChannelHigh Precision V oltage Comparator (P1.0,P1.1,P3.6);Have the output port of the LED direct driveLow-power idle and power-down modeThe pin Picture of AT89C2051Picture one the pin of AT89C2051AT89C2051’s functional description:VCC: Power Supply V oltageGND: landP1 port: P1 mouth is a group of 8-bit bi-directional I / O interface, P1.2 ~ P1.7 provide internal pull-up resistor,P1.0 and P1.1 internal supreme pull-up resistor. P1 mouth output buffer can absorb the current 20mA and direct-drive LED.When Programming and calibration, P1 mouth as the eighth address receive.P3 mouth: P3 port P3.0 ~ P3.5, P3.7 is the internal pull-up resistor with the seven bi-directional I / O interface. Did not bring out the P3.6,It as a generic I / O port, but can not visit. Can be used as a fixed-chip input comparator output signal. when P3 write 1, they were highed the internal pull-up resistor can be raised as an input port.P3 port special function as shown in table 1:Table 1 P3 mouth’s special featuresPIN functional characteristics20191817161514131211GND P3.5P3.4P3.3P3.2XTAL1XTAL2P3.1P3.0RST P3.7P1.0P1.1P1.2P1.3P1.4P1.5P1.6P1.7VCC 12345678910RST:Reset output. When the oscillator device reset, RST pin to maintain the high level of two machine cycle time.XTAL1: the RP-oscillator amplifier and internal clock generator input.XTAL2: RP-oscillator output amplifier.TimerOverview of the Timer89C2051 single-chip-chip has two 16-bit timer / counter, That is the timer 0 (T0) and Timer 1 (T1). They all have from time to time and event count function, Can be used for timing control, delay of external events, such as counting and testing occasions. Timer’s T0 and T1—— two 16-bit timers in fact is 16-bit counter plus 1. Among them, T0 compositioned by the two 8-bit special function registers TH0 and TL0; T1 posed by the TH1 and TL1. These functions were controled by the special function registers TMOD and TCONWhen set to the work in the timing, Through the pin count of the external pulse signal. When the input pulse signal generated by the falling edge of 1-0, The value of timer plus 1. At of every machine cycle during the S5P2 sampling pin T0 and T1 the input level, if a machine cycle before sample value of 1, The next machine cycle sampling value is 0, The counter plus 1. Since then during S3P1 of the machine cycle, New value will into the counter.so Detection of a 1-0 transition of the two machine cycles,So The maximum count frequency of oscillation frequency of 1 / 24. In addition to the option of work from time to time or count,Each timer / counter have four kinds of work mode, That is, each of timer circuit kinds of four constitute a structural modelTwo low-power modeIdle modeIn idle mode, CPU to maintain sleep and all-chip peripherals remain active, this way generated in Software, At this point, Chip RAM and all the contents of special function registers remain unchanged. Idle mode was terminated by any interrupt request permission to or hardware reset.P1.0 and P1.1 ,in the non-use of external pull-up resistor on the case should be set to "0", Or in the use of pull-up resistor is set to "1."It should be noted that: when uses of hardware reset Termination idle mode, AT89C2051 is usually stopped from the program until the internal reset control of the two machine cycles before the restore procedure Service. In this case the hardware within the prohibition of the reading and writing of internal RAM, However, to allow access to ports, To eliminate the Hardware reset in the idle mode of port accidents may write, In principle, to enter the idle mode of instruction should not be under the command of a pin or an external memory port for a visit.Power-down modeIn power-down mode, the oscillator to stop working, enter the power-down mode ,Instructions, who was the last one, the implementation of the Directive, Chip RAM and all the contents of special function registers the termination of the previous power-down mode be frozen. To withdraw from power-down mode is the only way to reset the hardware, Reset will redefine all the Special Function Registers but Does not change the contents of RAM before the the Vcc work returned to normal levels Shall be null and void and must be reset to maintain a certain period of time in order to restart and oscillator stabilityP1.0 and P1.1 in the non-use of external pull-up resistor on the case should be set to "0", Or in the use of pull-up resistor is set to "1."OscillatorOscillator connected clientXTAL1: RP-oscillator amplifier and internal clock generator inputXTAL2: RP-oscillator amplifier outputCharacteristics of OscillatorXTAL1, XTAL2 ware the RP-chip oscillator amplifier inputs and outputs, Quartzcrystal can be composed of the clock oscillator or ceramic oscillator, For more information from the external input clock driver AT89C2051, XTAL1 input clock signal from, XTAL2 should be left vacant.As the input to the internal circuit is a 2-flip-flop, Therefore, the external clock signal input without special requirements, However, it must comply with the maximum level and minimum norms and timing中文翻译:AT89C2051AT89C2051数据参考手册AT89C2051是美国ATMEL公司生产的低电压、高性能CMOS8位单片机,片内含2k bytes的可反复擦写的只读程序存储器(PEROM)和128bytes的随机数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器和可反复擦写的Flash存储器,可有效地降低开发成本。

51单片机AT89C52中文资料

51单片机AT89C52中文资料--------------------------------------------------------------------------------51单片机AT89C52中文资料AT89C52 ATMEL公司生产的低电压,高性能CMOS 8位单片机.片含8K byTES的可反复擦写的只读程序存储器(PEROM)和256 byTES 。

的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,与标准MCS-51指令系统及8052 产品引脚兼容,片置通用8位中央处理器(CPU )和FLASH由存储单元,功能强大AT89C52单片适用于许多较为复杂控制应用场合。

主要性能参数:与Mcs-51产品指令和引脚完全兼容。

8字节可重擦写FLASH闪速存储器1000 次擦写周期全静态操作:0HZ-24MHZ三级加密程序存储器256X8字节部RAM32个可编程I/0口线3个16 位定时/计数器8个中断源可编程串行UART通道低功耗空闲和掉电模式部结构图AT89C52部框图功能特性:AT89C52 提供以下标准功能:8字节FLASH闪速存储器,256字竹部RAM , 32个I/O口线,3个16 位定时/计数器,一个6向量两级中断结构,一个全双工串行通信口,片振荡器及时钟电路。

同时,AT89c52可降至OHz的静态逻辑操作,并支持两种软件可选的节电上作模式。

空闲方式停止CPU 的工作,但允许RAM,定时/计数器.串行通信口及中断系统继续工作。

掉电方式保存RAM 中的容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位.功能引脚说明:Vcc:电源电压GND:地P0:P0口是一组8位漏极开路型双向1/O 口,也即地址/数据总线复用口。

作为输出口用时.每位能吸收电流的方式驱动8个TTL 逻辑门电路,对端口P0 写“1”时,可作为高阻抗输入端用。

at89c52单片机介绍

at89c52中文资料介绍AT89C52 ATMEL公司生产的低电压,高性能CMOS 8位单片机.片内含8K byTES的可反复擦写的只读程序存储器(PEROM)和256 byTES 。

的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,与标准MCS-51指令系统及8052 产品引脚兼容,片内置通用8位中央处理器(CPU )和FLASH 由存储单元,功能强大AT89C52单片适用于许多较为复杂控制应用场合。

主要性能参数:与Mcs-51产品指令和引脚完全兼容。

8字节可重擦写FLASH闪速存储器1000 次擦写周期全静态操作:0HZ-24MHZ三级加密程序存储器256X8字节内部RAM32个可编程I/0口线3个16 位定时/计数器8个中断源可编程串行UART通道低功耗空闲和掉电模式AT89C52内部框图功能特性:AT89C52 提供以下标准功能:8字节FLASH闪速存储器,256字竹内部RAM , 32个I/O口线,3个16 位定时/计数器,一个6向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,AT89c52可降至OHz的静态逻辑操作,并支持两种软件可选的节电上作模式。

空闲方式停止CPU 的工作,但允许RAM,定时/计数器.串行通信口及中断系统继续工作。

掉电方式保存RAM 中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位.功能引脚说明:Vcc:电源电压GND:地P0:P0口是一组8位漏极开路型双向1/O 口,也即地址/数据总线复用口。

作为输出口用时.每位能吸收电流的方式驱动8个TTL 逻辑门电路,对端口P0 写“1”时,可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

在FLASH由编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

单片机AT89C52简要说明

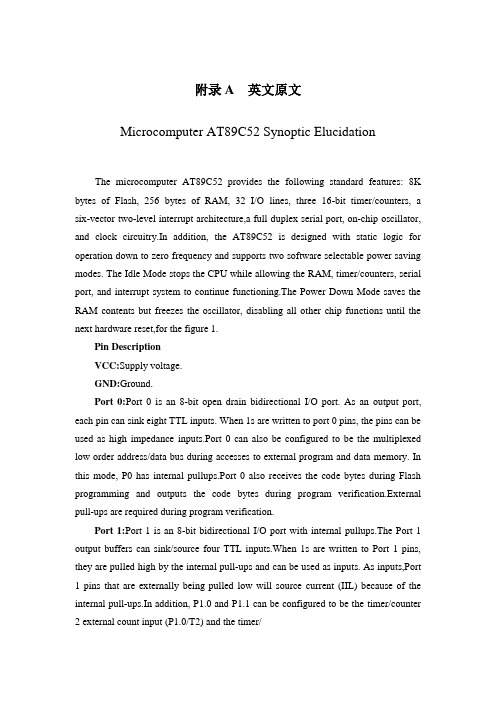

附录A 英文原文Microcomputer AT89C52 Synoptic ElucidationThe microcomputer AT89C52 provides the following standard features: 8K bytes of Flash, 256 bytes of RAM, 32 I/O lines, three 16-bit timer/counters, a six-vector two-level interrupt architecture,a full duplex serial port, on-chip oscillator, and clock circuitry.In addition, the AT89C52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning.The Power Down Mode saves the RAM contents but freezes the oscillator, disabling all other chip functions until the next hardware reset,for the figure 1.Pin DescriptionVCC:Supply voltage.GND:Ground.Port 0:Port 0 is an 8-bit open drain bidirectional I/O port. As an output port, each pin can sink eight TTL inputs. When 1s are written to port 0 pins, the pins can be used as high impedance inputs.Port 0 can also be configured to be the multiplexed low order address/data bus during accesses to external program and data memory. In this mode, P0 has internal pullups.Port 0 also receives the code bytes during Flash programming and outputs the code bytes during program verification.External pull-ups are required during program verification.Port 1:Port 1 is an 8-bit bidirectional I/O port with internal pullups.The Port 1 output buffers can sink/source four TTL inputs.When 1s are written to Port 1 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs,Port 1 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups.In addition, P1.0 and P1.1 can be configured to be the timer/counter 2 external count input (P1.0/T2) and the timer/counter 2 trigger input (P1.1/T2EX), respectively, as shown in the following table.Port 1 also receives the low-order address bytes during Flash programming and verification.Port 2:Port 2 is an 8-bit bidirectional I/O port with internal pullups.The Port 2 output buffers can sink/source four TTL inputs.When 1s are written to Port 2 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (IIL) because of the internal pull-ups. Port 2 emits the high order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR). In this application, Port 2 uses strong internal pull-ups when emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @ RI), Port 2 emits the contents of the P2 Special Function Register.Port 2 also receives the high-order address bits and some control signals during Flash programming and verification.Port 3:Port 3 is an 8-bit bidirectional I/O port with internal pullups.The Port 3 output buffers can sink/source four TTL inputs.When 1s are written to Port 3 pins, they are pulled high by the internal pull-ups and can be used as inputs. As inputs,Port 3 pins that are externally being pulled low will source current (IIL) because of the pullups.Port 3 also serves the functions of various special features of the AT89C51, as shown in the following table.Port 3 also receives some control signals for Flash programming and verification.RST:Reset input. A high on this pin for two machine cycles while the oscillator is running resets the device.ALE/PROG:Address Latch Enable is an output pulse for latching the low byte of the address during accesses to external memory.This pin is also the program pulse input (PROG) during Flash programming.In normal operation, ALE is emitted at a constant rate of 1/6the oscillator frequency and may be used for external timing or clocking purposes. Note, however, that one ALE pulse is skipped during each access to external data memory.If desired, ALE operation can be disabled by setting bit 0 of SFR location 8EH. With the bit set, ALE is active only during a MOVX or MOVC instruction. Other- wise, the pin is weakly pulled high. Setting the ALE-disable bit hasno effect if the microcontroller is in external execution mode.PSEN:Program Store Enable is the read strobe to external program memory.When the AT89C52 is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.EA/VPP:External Access Enable. EA must be strapped to GND in order to enable the图A.1 AT89C52方框图device to fetch code from external program memory locations starting at 0000H up to FFFFH.Note, however, that if lock bit 1 is programmed, EA will be internally latched on reset.EA should be strapped to VCC for internal program executions.This pin also receives the12-volt programming enable voltage(VPP) during Flash programming when 12-volt programming is selected.XTAL1:Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2:Output from the inverting oscillator amplifier.Special Function Registers:Not all of the addresses are occupied, and unoccupied addresses may not be implemented on the chip.Read accesses to these addresses will in general return random data, and write accesses will have an indeterminate er software should not write 1s to these unlisted locations, since they may be used in future products to invoke new features. In that case, the reset or inactive values of the new bits will always be 0.Timer 2 Registers: Control and status bits are contained in registers T2CON and T2MOD for Timer 2. The register pair (RCAP2H,RCAP2L) are the Capture/Reload registers for Timer 2 in 16-bit capture mode or 16-bit auto-reload mode.Interrupt Registers: The individual interrupt enable bits are in the IE register. Two priori- ties can be set for each of the six interrupt sources in the IP register.Data Memory:The AT89C52 implements 256 bytes of on-chip RAM. The upper 128 bytes occupy a parallel address space to the Special Function Registers. That means the upper 128 When an instruction accesses an internal location above address 7FH, the address mode used in the instruction specifies whether the CPU accesses the upper 128 bytes of RAM or the SFR space. Instructions that use direct addressing access SFR space. For example, the following direct addressing instruction accesses the SFR at location 0A0H (which is P2).Instructions that use indirect addressing access the upper 128 bytes of RAM. For example, the following indirect addressing instruction, where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H). Note that stack operations are examples of indirect addressing, so the upper 128 bytes of data RAM are available as stack space.Timer 0 and 1:Timer 0 and Timer 1 in the AT89C52 operate the same way as Timer 0 and Timer 1 in the AT89C51.Timer 2:Timer 2 is a 16-bit Timer/Counter that can operate as either a timer or an event counter. The type of operation is selected by bit C/T2 in the SFR T2CON.Timer 2 has three operating modes: capture, auto-reload(up or down counting), and baud rate generator. The modes are selected by bits in T2CON.Timer 2consists of two 8-bit registers, TH2 and TL2. In the Timer function, the TL2 register is incremented every machine cycle. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency. In the Counter function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since two machine cycles (24 oscillator periods) are required to recognize a 1-to-0 transition,the maxi- mum count rate is 1/24 of the oscillator frequency.To ensure that a given level is sampled at least once before it changes, the level should be held for at least one full machine cycle.Capture Mode:In the capture mode, two options are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 is a 16-bit timer or counter which upon overflow sets bit TF2 in T2CON.This bit can then be used to generate an interrupt. If EXEN2 = 1, Timer 2 performs the same operation, but a 1-to-0 transition at external input T2EX also causes the current value in TH2 and TL2 to be captured into RCAP2H and RCAP2L, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. The EXF2 bit, like TF2, can generate an interrupt.Auto-Reload (Up or Down Counter):Timer 2 can be programmed to count up or down when configured in its 16-bit auto-reload mode. This feature is invoked by the DCEN (Down Counter Enable) bit located in the SFR T2MOD (see Table 4). Upon reset, the DCEN bit is set to 0 so that timer 2 will default to count up. When DCEN is set, Timer 2 can count up or down, depending on the value of the T2EX pin. Timer 2 automatically count up when DCEN = 0. In this mode, two option s are selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 counts up to 0FFFFH and then sets the TF2 bit upon overflow. The overflow also causes the timer registers to be reloaded with the 16-bit value in RCAP2H and RCAP2L. The values in Timer in Capture ModeRCAP2H and RCAP2L are preset by software.If EXEN2 = 1, a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at external input T2EX. This transi- tion also sets the EXF2 bit. Both the TF2 and EXF2 bits cangenerate an interrupt if enabled.Setting the DCEN bit enables Timer 2 to count up or down,as shown in Figure 3. In this mode, the T2EX pin controls the direction of the count. A logic 1 at T2EX makes Timer 2 count up. The timer will overflow at 0FFFFH and set the TF2 bit. This overflow also causes the 16-bit value in RCAP2H and RCAP2L to be reloaded into the timer registers,TH2 and TL2, respect- tively.A logic 0 at T2EX makes Timer 2 count down. The timer underflows when TH2 and TL2 equal the values stored in RCAP2H and RCAP2L. The underflow sets the TF2 bit and causes 0FFFFH to be reloaded into the timer registers.The EXF2 bit toggles whenever Timer 2 overflows or underflows and can be used as a 17th bit of resolution. In this operating mode, EXF2 does not flag an inter- rupt.Baud Rate Generator:Timer 2 is selected as the baud rate generator by setting TCLK and/or RCLK in T2CON (Table 2). Note that the baud rates for transmit and receive can be different if Timer 2 is used for the receiver or trans- mitter and Timer 1 is used for the other function. Setting RCLK and/or TCLK puts Timer 2 into its baud rate generator mode, as shown in Figure 4.The baud rate generator mode is similar to the auto-reload mode, in that a rollover in TH2 causes the Timer 2 registers to be reloaded with the 16-bit value in registers RCAP2H and RCAP2L, which are preset by software.The baud rates in Modes 1 and 3 are determined by Timer2’s overflow rate according to the following (A.1)equation.Modes1 and 3 band rates=Timer 2 Overflow Rate16(A.1)The Timer can be configured for either timer or counter operation. In most applications, it is configured for timer operation (CP/T2 = 0). The timer operation is different for Timer 2 when it is used as a baud rate generator. Normally,as a timer, it increments every machine cycle (at 1/12 the oscillator frequency). As a baud rate generator, however, it increments every state time (at 1/2 the oscillator frequency).The baud rate formula is given below(A.2).modes 1 and 3 band Rate =Oscillator frequency32[65536-(RCAP2H,RCAP2L)](A.2)where (RCAP2H, RCAP2L) is the content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer Timer 2 as a baud rate generator is showed.This figure is valid only if RCLK or TCLK = 1 in T2CON. Note that a rollover in TH2 does not set TF2 and will not generate an interrupt. Note too, that if EXEN2 is set, a 1-to-0 transition in T2EX will set EXF2 but will not cause a reload from (RCAP2H, RCAP2L) to (TH2, TL2). Thus when timer 2 is in use as a baud rate generator, T2EX can be used as an extra external interrupt. Note that when Timer 2 is running (TR2 = 1) as a timer in the baud rate generator mode, TH2 or TL2 should not be read from or written to. Under these conditions, the Timer is incremented every state time, and the results of a read or write may not be accurate. The RCAP2 registers may be read but should not be written to, because a write might overlap a reload and cause write and/or reload errors. The timer should be turned off (clear TR2) before accessing the Timer 2 or RCAP2 registers.附录B 中文翻译单片机AT89C52简要说明AT89C52提供以下标准功能:8k字节Flash闪速存储器,256字节内部RAM,32个I/O口线,3个16位定时/计数器,一个6向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

AT89C52中文资料

A T89C52中文资料电子驿站http:// E-mail: support@A T89C52是美国A TMEL公司生产的低电压,高性能CMOS 8位单片机,片内含8k bytes的可反复擦写的只读程序存储器(PEROM)和256 bytes的随机存取数据存储器(RAM),器件采用A TMEL公司的高密度、非易失性存储技术生产,与标准MCS-51指令系统及8052产品引脚兼容,片内置通用8位中央处理器(CPU)和Flash存储单元,功能强大A T89C52单片机适合于许多较为复杂控制应用场合。

主要性能参数:·与MCS-51产品指令和引脚完全兼容·8k字节可重擦写Flash闪速存储器·1000次擦写周期·全静态操作:0Hz-24MHz·三级加密程序存储器·256×8字节内部RAM·32个可编程I/O口线·3个16位定时/计数器·8个中断源·可编程串行UART通道·低功耗空闲和掉电模式功能特性概述:A T89C52提供以下标准功能:8k字节Flash闪速存储器,256字节内部RAM,32个I/O口线,3个16位定时/计数器,一个6向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,A T89C52可降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。

空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。

掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。

AT89C52方框图·P0口:P0口是一组8位漏极开路型双向I /O 口,也即地址/数据总线复用口。

作为输出口用时,每位能吸收电流的方式驱动8个TTL 逻辑门电路,对端口P0写“l ”时,可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

AT89C52中文原理图规格书

Rev. 0313H–02/00

1

Block Diagram

VCC GND

RAM ADDR. REGISTER

P0.0 - P0.7 PORT 0 DRIVERS

P2.0 - P2.7 PORT 2 DRIVERS

RAM

PORT 0 LATCH

PORT 2 LATCH

QUICK FLASH

PORT 1 LATCH

PORT 3 LATCH

OSC

PORT 1 DRIVERS

PORT 3 DRIVERS

P1.0 - P1.7

P3.0 - P3.7

BUFFER

PC INCREMENTER

PROGRAM COUNTER

DPTR

2

AT89C52

AT89C52

The AT89C52 provides the following standard features: 8K bytes of Flash, 256 bytes of RAM, 32 I/O lines, three 16-bit timer/counters, a six-vector two-level interrupt architecture, a full-duplex serial port, on-chip oscillator, and clock circuitry. In addition, the AT89C52 is designed with static logic for operation down to zero frequency and supports two software selectable power saving modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial port, and interrupt system to continue functioning. The Power-down mode saves the RAM contents but freezes the oscillator, disabling all other chip functions until the next hardware reset.

at89c52单片机中英文资料对照外文翻译文献综述

D.htmlat89c52单片机中英文资料对照外文翻译文献综述at89c52单片机简介中英文资料对照外文翻译文献综述AT89C52 Single-chip microprocessor introductionSelection of Single-chip microprocessor1. Development of Single-chip microprocessorThe main component part of Single-chip microprocessor as a result of by such centralize to be living to obtain on the chip,In immediate future middle processor CPU。

Storage RAM immediately﹑memoy readROM﹑Interrupt system、Timer /'s counter along with I/O's rim electric circuit awaits the main microcomputer section,The lumping is living on the chip。

Although the Single-chip microprocessor r is only a chip,Yet through makes up and the meritorous service be able to on sees,It had haveed the calculating machine system property,calling it for this reason act as Single-chip microprocessor r minisize calculating machine SCMS and abbreviate the Single-chip microprocessor。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

51单片机AT89C52中文资料AT89C52 ATMEL公司生产的低电压,高性能CMOS 8位单片机.片内含8K byTES的可反复擦写的只读程序存储器(PEROM)和256 byTES 。

的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,与标准MCS-51指令系统及8052 产品引脚兼容,片内置通用8位中央处理器(CPU )和FLASH由存储单元,功能强大AT89C52单片适用于许多较为复杂控制应用场合。

主要性能参数:与Mcs-51产品指令和引脚完全兼容。

8字节可重擦写FLASH闪速存储器1000 次擦写周期全静态操作:0HZ-24MHZ三级加密程序存储器256X8字节内部RAM32个可编程I/0口线3个16 位定时/计数器8个中断源可编程串行UART通道低功耗空闲和掉电模式内部结构图AT89C52内部框图功能特性:AT89C52 提供以下标准功能:8字节FLASH闪速存储器,256字竹内部RAM , 32个I/O口线,3个16 位定时/计数器,一个6向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。

同时,A T89c52可降至OHz的静态逻辑操作,并支持两种软件可选的节电上作模式。

空闲方式停止CPU 的工作,但允许RAM,定时/计数器.串行通信口及中断系统继续工作。

掉电方式保存RAM 中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位.功能引脚说明:Vcc:电源电压GND:地P0:P0口是一组8位漏极开路型双向1/O 口,也即地址/数据总线复用口。

作为输出口用时.每位能吸收电流的方式驱动8个TTL 逻辑门电路,对端口P0 写“1”时,可作为高阻抗输入端用。

在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。

在FLASH由编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。

P1口:PI 是一个带内部上拉电阻的8位双向I/O口,Pl的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。

对端口写“1”,通过内部的上拉电阻把端口拉到高电平,此时可作输入口。

作输入口使用时,因为内部存在上拉电阻某个引脚被外部信号拉低时会输出一个电流IIL与A T89C51不同之处是,Pl.0 和P1.1还可分别作为定时/计数器 2 的外部计数输入(Pl.0/T2 )和输入(P1.1/T2EX) ,参见表1FLASH编程和程序校验期间,Pl接收低8位地址。

表1 PI.O 和PI.l 的第二功能口:P2 是一个带有内部上拉电阻的8位双向I/O口,P2的输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑电路。

对端口P2写“l",通过内部的上拉电阻把端口拉到高电平,此时可作输入口,作输入口使用时,因为内部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(llt )。

在访问外部程序存储器或16位地址的外部数据存储器(例如执行MOvx@DPTR 指令)时,P2送出高8 位地址数据。

在访问8位地址的外部数据存储器、如执行MOVX@RI指令)时,P2口输出P2锁存器的内容。

FLASH编程或校验时,P2亦接收高位地址和一些控制信号。

·P3口:P3口是一组带有内部上拉电阻的8位双向I/O口。

P3口输出缓冲级可驱动(吸收或输出电流)4个TTL逻辑门电路。

对P3口写入“1”时,它们被内部上拉电阻拉高并可作为输入端口。

此时,被外部拉低的P3口将用上拉电阻输出电流(IIL) .P3口除了作为一般的I/0口线外,更重要的用途是它的第二功能,如下表所示:端口引脚第二功能P3.0 RXD(串行输入口〕P3.1 TXD(串行输出口〕P3.2 INTO(外中断0〕P3.3 INTO(外中断l)P3.4 TO (定时/计数器0 )P3.5 Tl (定时/计数器l )P3.6 WR(外部数据存储器写选通)P3.7 RD(外部数据存储器读选通)此外,P3口还接收一些用于FLASH闪速存储器编程和程序校验的控制信号。

RST:复位输入。

当振荡器工作时,RST引脚出现两个机器周期以上高电平将使单片机复位。

·ALE/PROG:当访问外部程序存储器或数据存储器时,ALE(地址锁存允许)输出脉冲用于锁存地址的低8位字节.一般情况下,ALE仍以时钟振荡频率的1/6输出固定的脉冲信号,因此它可对外输出时钟或用于定时目的。

要注意的是:每当访问外部数据存储器时将跳过一个ALE脉冲。

对Flash存储器编程期间,该引脚还用于输入编程脉冲(PROG)。

如有必要,可通过对特殊功能寄存器(SFR)区中的8EH单元的D0位置位.可禁止ALE 操作。

该位置位后,只有一条MOVX和MOVC指令才能将ALE激活,此外,该引脚会被微弱拉高,单片机执行外部程序时,应设置ALE禁止位无效。

·PSEN:程序储存允许PSEN输出是外部程序存储器的读选通信号,当A T89C52由外部程序存储器取指令(或数据)时,每个机器周期两次PSEN有效,即输出两个脉冲。

在此期间,当访问外部数据存储器,将跳过两次PSEN信号。

·EA/VPP:外部访问允许。

欲使CPU 仅访问外部程序存储器(地址为0000H-FFFFH ) , EA端必须保持低电平(接地).需注怠的是:如果加密位LBI被编程,复位时内部会锁存EA端状态。

如EA端为高电平(接Vcc端), CPU则执行内部程序存储器中的指令。

flash存储器编程时,该引脚加上+12V的编程允许电源VPP ,当然这必须是该器件是使用12V编程电压VPP 。

·XTAL1:振荡器反相放大器的及内部时钟发生器的输入端.·XTAL1:振荡器反相放大器的输出端。

,特殊功能寄存器:在AT89C52片内存储器中,80H-FFH共128个单元为特殊功能寄存器(SFE ) , SFR的地址空间映象如表2所示。

并非所有的地址都被定义,从80H-FFH共128 个字节只有一部分被定义,还有相当一部分没有定义。

对没有定义的单元读写将是无效的,读出的数位将不确定,而写入的数据也将丢失。

不应将数据"1"写入未定义的单元,由于这些单元在将来的产品中可能赋予新的功能,在这种情况下,复位后这些单元数值总是“0”。

表2 AT89C52 SFR 映象及复位状态AT89C52除了与AT89C51所有的定时/计数器0和定时/计数器1 外,还增加了一个定时/计数器2 .定时/计数器2的控制和状态位位于T2CON (参见表3) T2CON(参见表4) ,寄存器对(RCA02H、RCAP2L)是定时器2在16 位捕获方式或16位自动重装载方式下的捕获/自动重装载寄存器。

表3 定时/计数器2控制寄存器T2CONT2CON地址=OC8H 复位值= 0000 0000B可寻地址TF2 EXF2 RCK TCLK EXEN2 TR2 C/T2 CP/RL27 6 5 4 3 2 1 0符号功能TF2 定时器2溢出标志。

定时器2溢出时,又由硬件置位,必须由软件清0,当RCLK=1或TCLK=1时,定时器2溢出,不对TF2置位。

EXF2 定时器2外部标志。

当EXEN2=1,且当T2EX引脚上出现负跳变而出现捕获或重装载时,EXF2置位,申请中断.此时如果允许定时器2中断,CPU响应中断,执行定时器2中断服务程序,EXF2必须由软件清除。

当定时器2工作在向上或向下计数工作方式时(DCEN=1) , ExF2不能激活中断。

RCLK 接收时钟允许。

RCLK=1时.用定时器2溢出脉冲作为串行口(工作于工作方式1或3时)的接收时钟,RCLK=0,用定时器l的溢出脉冲作为接收时钟。

TCLK 发送时钟允许。

TCLK=1时,用定时器2溢出脉冲作为串行口(工作于工作方式1或3时)的发送时钟,RCLK=0 .用定时器l的溢出脉冲作为发送脉冲。

EXEN2 定时器2外部允许标志。

当EXEN2=1时,如果定时器2未用于作串行口的波特率发生器,在T2EX端出现负跳变脉冲时,激活定时器2 捕获或重装载.EXEN2=0,T2EX 端的外部信号无效.TR2 定时器2启动/停止控制位。

TR2=l时,启动定时器2 。

C/T2 定时器2定时方式或计数方式控制位。

C/T2=0,选择定时方式。

C/T2=1时,选择对外部事件计数方式(下降沿触发)。

CP/RL2 捕获/重装载选择。

CP/RL2=l时,如EXEN2=l.且T2EN双端出现负跳变脉冲时发生捕获操作。

CP/RL2=0时,若定时器2溢出或EXEN2=l条件下,T2EN双端出现负跳变脉冲,都会出现自动重装载操作。

当RCLK=1或TCLK=1时,该位无效,在定时器2溢出时强制其自动重装载。

引脚号功能特性Pl.0 T2 (定时/计数器2外部计数脉冲输入),时钟输出Pl.1 TZEx 定时/计数2捕获/重装载触发和方向控制)中断寄存器:AT89C52有6个中断源,2个中断优先级,lE寄存器控制各中断位,lP寄存器中6个中断源的每一个可定为2个优先级。

数据存储器AT89C52有256个字节的内部RAM , 80H-FFH高128个字节与特殊功能寄存器(SFR)地址是重叠的,也就是高128字竹的RAM和殊功能寄存器的地址是相同的,但物理上它们是分开的。

当一条指令访问7FH以上的内部地址单元时,指令中使用的寻址方式是不同的,也即寻址方式决定是访问高128字节RAM还是访问特殊功能寄存器。

如果指令是直接寻址方式则为访问特殊功能寄存器.例如,下面的直接寻址指令访问特殊功能寄存器0A0H(即P2口)地址单元。

MOV 0A0H ,#data间接寻址指令访问高128字节RAM ,例如下面的间接子址指令中,R0的内容为OAOH ,则访问数据字节地址为0A0H , 而不是P2口(0A0H )。

MOV @RO ,#data堆栈操作也是间接寻址方式,所以,高128位数据RAM亦可作为堆栈区使用。

定时器O和定时器1AT89C52的定时器O和定时器1的工作方式与A T89C51相同。

定时2定时器2是一个16位定时计数器。

它既可当定时器使用,也可作为外部事件计数器使用,其工作方式由特殊功能寄存器T2CON(如表3 )的C/T2位选择。

定时器2有三种工作方式:捕获方式,自动重装载(向上或向下计数)方式和波特率发生器方式,工作方式由T2CON 的控制位来选择,参见表4 。

表4 定时器2 工作方式RCLX + TCLK CP/RL2 TR2 MODE0 O 1 16-bit auto-reload0 1 1 16-bit Capture1 X 1 BaUd Rate GeneratorX X O (off)定时器2由两个8位寄存器TH2和TL2组成,在定时器工作方式中,每个机器周期TL2寄存器的值加1 ,由于一个机器周期由12个振荡时钟构成,因此,计数速率为振荡频率的1/l2 。