组合逻辑电路的设计举例

组合电路的设计方法

A

B

C

Y

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

0

1

0

1

1

1

1

0

1

1

1

1

1

(2)化简得到最简输出逻辑函数

Y ABC ABC ABC AB AC

(3)画逻辑图

B

&

A.

C

&

>=1

Y

2.多输出组合逻辑电路的设计 [例2]设计一个能完成两个一位二进制数相加的

三.组合逻辑电路设计举例

1.单输出组合逻辑电路的设计 [例1]设计一个A、B、C三人表决电路。

当表决某个提案时,多数人同意,提案通过, 同时A具有否决权。用与非门实现。 解:设计步骤 (1)确定输入输出变量,列写真值表

A 同意 “1”,不同意 “0” ;

输入 B 同意 “1”,不同意 “0” ; C 同意 “1”,不同意 “0” ;

组合逻辑电路-半加器。

解:设计步骤 (1)确定输入输出变量,列写真值表

A,B

两个一位二进制数

S

表示二者之和

C进位ABSC0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

(2)化简得到最简输出逻辑函数

S AB AB C AB

(3)画逻辑图

A B

=1

S

&

C

(4)检测此电路,证明逻辑功能符合设计要求

组合逻辑电路的设计方案举例

组合逻辑电路的设计举例例1. 某工厂有A、B、C三个车间和一个自备电站,站内有两台发电机G1和G2。

G1的容量是G2的两倍。

如果一个车间开工,只需G2运行即可满足要求;如果两个车间开工,只需G1运行;如果三个车间同时开工,则G1和 G2均需运行。

试画出控制G1和 G2运行的逻辑图,用与非门实现。

解:(1)根据逻辑要求写出逻辑状态表首先假设逻辑变量取“0”、“1”的含义。

设:A、B、C分别表示三个车间的开工状态:开工为“1”,不开工为“0”;G1和 G2运行为“1”,不运行为“0”。

逻辑状态表ABC G1 G2 0 0 0 00 0 0 1 0 11 0 0 1 0 11 0 1 0 0 01 0 1 1 0 11 0 1 0 1 1 111(2)由逻辑状态表写出逻辑式根据状态表写表达式的一般步骤:①在状态表上找出输出为1的行;②将这一行中所有自变量写成乘积项,当变量的取值为“1”时写为原变量,当变量的取值为“0”时写为原变量的反变量;③将所有乘积项逻辑加,便得到逻辑函数表达式。

这里的乘积项又叫最小项,在最小项里,每个变量都以它的原变量或反变量的形式在乘积项中出现,且仅出现一次。

(3)化简逻辑式(4)用“与非”门构成逻辑电路(5)画出逻辑电路图例2:设计三人表决电路(A、B、C)。

每人一个按键,如果同意则按下,不同意则不按。

结果用指示灯表示,多数同意时指示灯亮,否则不亮。

要求用与非门实现。

解:(1)根据逻辑要求列状态表首先确定逻辑变量取0、1的含义:A、B、C分别表示三人按键的状态,键按下时为“1”,不按时为“0”。

F表示指示灯的亮灭,灯亮为“1”,不亮为“0”。

逻辑要求:两个人(包括两个人)以上同意,指示灯亮。

ABCF 0 0 0 0 0 01 0 0 1 0 01 1 1 1 0 01 0 1 1 1 111111(2)由状态表写出逻辑式并化简、转换(3)实现电路。

数字逻辑4-2组合逻辑电路设计(案例1)

设参加表决的输入变量为A、B、C。 输入为0,表示反对,输入为1,表示 同意。表决的结果用输出变量F表示。 表决的原则是“少数服从多数”,如 多数同意,决议通过,F=1,多数反对, 决议被否决,F=0。

数字逻辑

第4章 组合逻辑电路

组合逻辑电路设计

根据分析,可以很容易列出真值表如下图所示:

A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 F 0 0 0 1 0 1 1 1

由真值表可以直接写出 其最小项表达式:

F

5, 6, 7 m 3,

数字逻辑

第4章 组合逻辑电路

组合逻辑电路设计

选择与非门组成电路,用卡诺图将其化为最简“与-或”式

数字逻辑

第4章 组合逻辑电路

组合逻辑电路设计

2、求出逻辑函数的最简函数表达式

基于小规模集成电路优化设计目标, 要求所设计的电路包含的门电路最少、 引脚之间连线最少,所以,必须将逻 辑函数化简为最简表达式。 3、选择逻辑门类型并进行逻辑函数的变换 4、画出逻辑电路图

数字逻辑 第4章 组合逻辑电路

组合逻辑电路设计

AB C 0 1 00 0 0 01 0 1 11 1 1 10 0 1

F (A ,B ,C ) AB BC AC AB BC AC AB

数字逻辑

BC

辑电路如下图所示

数字逻辑

第4章 组合逻辑电路

本讲小结

4.2 组合电路的设计方法 案例(1)

数字逻辑

章晓卿

上海交通大学继续教育学院

第4章 组合逻辑电路

4.1 组合电路的分析方法 4.2 组合电路的设计方法 4.3 组合电路中的险象问题

实验一组合逻辑电路的设计

实验一组合逻辑电路的设计组合逻辑电路是一种电子电路,由逻辑门组成,用于执行特定的逻辑功能。

在本实验中,我们将设计一个基本的组合逻辑电路以及一些常见的组合逻辑电路,包括加法器、减法器、比较器等。

首先,我们将设计一个基本的组合逻辑电路,该电路由两个输入和一个输出组成。

输入可以是0或1,输出将依据输入的值进行逻辑运算得出。

在这个基本电路中,我们将使用两个逻辑门:与门和或门。

与门的真值表如下:输入1输入2输出000010100111与门的布尔表达式是:输出=输入1AND输入2或门的真值表如下:输入1输入2输出000011101111或门的布尔表达式是:输出=输入1OR输入2基于以上真值表和布尔表达式,我们可以通过逻辑门的连接来设计一个基本的组合逻辑电路。

具体设计步骤如下:1.首先,将两个输入引线分别连接到与门和或门的输入端。

这将确保输入的值能够传递到逻辑门中。

2.将与门和或门的输出引线连接到一个输出引线上,以便能够输出最终的逻辑结果。

3.最后,将逻辑门的电源连接到电路的电源上,以确保逻辑门能正常工作。

通过以上步骤,我们就完成了一个基本的组合逻辑电路的设计。

这个电路可以根据输入产生不同的输出,实现不同的逻辑功能。

除了基本的组合逻辑电路,我们还可以设计一些常见的组合逻辑电路,如加法器、减法器和比较器。

加法器是用来执行数字加法的组合逻辑电路。

在一个二进制加法器中,输入是两个二进制数和一个进位位,输出是一个和输出和一个进位位。

加法器的设计可以通过级联多个全加器来实现。

减法器是用来执行数字减法的组合逻辑电路。

在一个二进制减法器中,输入是两个二进制数和一个借位位,输出是一个差输出和一个借位位。

减法器的设计可以通过级联多个全减法器来实现。

比较器是用来比较两个数字的大小的组合逻辑电路。

比较器的输出取决于输入的大小关系。

如果两个输入相等,则输出为0。

如果第一个输入大于第二个输入,则输出为1、如果第一个输入小于第二个输入,则输出为-1、比较器的设计可以通过使用逻辑门和触发器来实现。

实验五-组合逻辑电路的设计

实验五组合逻辑电路的设计一、试验目的1、掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、熟悉CPLD设计的过程,比较原理图输入和文本输入的优劣。

二、实验的硬件要求1、输入:按键开关(常高)4个;拨码开关4位。

2、输出:LED灯。

3、主芯片:Altera EPM7128SLC84-15。

三、实验内容1、设计一个四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5时,判别电路输出为1,反之为0。

2、设计四个开关控制一盏灯的逻辑电路,要求改变任意开关的状态能够引起灯亮灭状态的改变。

(即任一开关的合断改变原来灯亮灭的状态)3、设计一个优先排队电路,其框图如下:排队顺序:A=1 最高优先级B=1 次高优先级C=1 最低优先级要求输出端最多只能有一端为“1”,即只能是优先级较高的输入端所对应的输出端为“1”。

四、实验连线1、四位拨码开关连D3、D2、D1、D0信号对应的管脚。

OUT输出信号管脚接LED灯。

2、四位按键开关分别连K1、K2、K3、K4信号对应的管脚。

OUT输出信号管脚接LED灯。

3、A、B、C信号对应管脚分别连三个按键开关。

输出A_Out、B_Out、C_Out信号对应的管脚分别连三个LED灯。

(具体管脚参数由底层管脚编辑决定)五、参考原理图1、①原理图,如图5-1所示:②AHDL硬件描述语言输入:SUBDESIGN t5_1(d0,d1,d2,d3:INPUT;out: OUTPUT;)BEGINIF( (d3,d2,d1,d0) >= 5 ) THENout=VCC;ELSEout=GND;END IF;END;2、①原理图,如图5-2所示:②AHDL硬件描述语言输入:SUBDESIGN t5_2(k0,k1,k2,k3:INPUT;out: OUTPUT;)BEGINTABLE(k3,k2,k1,k0) => out;B"0000" => GND;B"0001" => VCC;B"0011" => GND;B"0010" => VCC; 图5-2图5-1B"0110" => GND;B"0111" => VCC;B"0101" => GND;B"0100" => VCC;B"1100" => GND;B"1101" => VCC;B"1111" => GND;B"1110" => VCC;B"1010" => GND;B"1011" => VCC;B"1001" => GND;B"1000" => VCC;END TABLE;END;3、①原理图,如图5-3所示:图5-3②AHDL硬件描述语言输入:SUBDESIGN t5_3(a,b,c : INPUT;a_out,b_out,c_out : OUTPUT;)BEGINIF a THENa_out=VCC; b_out=GND; c_out=GND;ELSIF b THENa_out=GND; b_out=VCC; c_out=GND;ELSIF c THENa_out=GND; b_out=GND; c_out=VCC;ELSEa_out=GND;b_out=GND;c_out=GND;END IF;END;六、实验报告要求1、对于原理图设计要求有设计过程。

组合逻辑电路的设计方法案例分析

组合逻辑电路的设计方法案例分析

与分析过程相反,组合逻辑电路的设计是根据给定的实际逻辑问题,求出实现其逻辑功能的最简逻辑电路。

组合逻辑电路的设计步骤如下。

(1)分析设计要求,设置输入变量和输出变量并逻辑赋值。

(2)列真值表,根据上述分析和赋值情况,将输入变量的所有取值组合和与之相对应的输出函数值列表,即得真值表。

(3)写出逻辑表达式并化简。

(4)画逻辑电路图。

例:设计一个3路判决电路,A 裁判具有否决定权。

解:(1)分析设计要求,设输入、输出变量并逻辑赋值。

输入变量:A 、B 、C 分别为3个裁判。

输出变量:Y 。

逻辑赋值:用1表示肯定,用0表示否定。

(2)列真值表,见表6.6。

(3) 由真值表写出逻辑函数表达式并化简。

C B A C AB ABC Y ++= AC AB AC AB ⋅=+= (4) 画逻辑电路图。

用与非门电路实现,如图6.46所示。

图6.46逻辑电路图

利用分立门电路搭接了具有一定逻辑功能的组合逻辑电路,需要的组合逻辑电路固然能通过刚才的方法利用门电路进行搭接,但缺点是该种电路所需的硬件多、连线多、电路复杂,从而造成功耗、重量及体积增大,同时特性较差,所以可利用现成的集成数字组合逻辑电路来搭接相应的功能电路,接下来介绍常见的集成组合逻辑电路。

组合逻辑电路的设计

0 1 1 0 ×××××

010

0 1 1 1 0 ××××

011

0 1 1 1 1 0 ×××

100

0 1 1 1 1 1 0 ××

101

0 1 1 1 1 1 1 0×

110

0 1 1 1 1 1 1 10

111

出

YEX YS

11 10 01 01 01 01 01 01 01 01

第4章 组合逻辑电路

第4章 组合逻辑电路

Dn An BnCn An BnCn An Bn C n An BnCn An Bn Cn

Cn1 An Bn C n An Bn C n BnCn An (Bn Cn ) BnCn An (Bn Cn ) BnCn

E3 A BC BD A BC BD

E2 BC D BC BD B(C D) B(C D) B (C D)

E1 C D CD C D C D

E0 D

第4章 组合逻辑电路

③ 画逻辑电路。

该电路采用了三种门电路,速度较快,逻辑图如图4.2.4所示。

的输入、输出均为低电平有效,因此给每个输出端加一个

反相器,即可将反码输出的BCD码转换为正常的BCD码。

第4章 组合逻辑电路

图4.3.3 74LS147的逻辑符号

第4章 组合逻辑电路

表4.3.2 74LS147的功能表

I1 I2 I3 I4 I5 I6 I7 I8 I9

111 11 11 11 ××× ×× ×× × 0 ××× ×× ×× 0 1 ××× ×× × 0 1 1 ××× ×× 0 1 1 1 ××× × 0 1 1 1 1 ××× 0 1 1 1 1 1 ×× 0 1 1 1 1 1 1 ×0 1 1 1 1 1 1 1

组合逻辑电路举例

组合逻辑电路举例组合逻辑电路是由逻辑门和逻辑门之间的连接组成的电路,用于实现特定的逻辑功能。

下面列举了十个常见的组合逻辑电路。

1. 与门(AND Gate):与门有两个或多个输入信号和一个输出信号。

当所有输入信号都为高电平时,输出信号为高电平;否则输出信号为低电平。

2. 或门(OR Gate):或门有两个或多个输入信号和一个输出信号。

当任意一个输入信号为高电平时,输出信号为高电平;只有当所有输入信号都为低电平时,输出信号才为低电平。

3. 非门(NOT Gate):非门只有一个输入信号和一个输出信号。

当输入信号为高电平时,输出信号为低电平;当输入信号为低电平时,输出信号为高电平。

4. 与非门(NAND Gate):与非门是与门的输出信号经过非门得到的结果。

当所有输入信号都为高电平时,输出信号为低电平;否则输出信号为高电平。

5. 或非门(NOR Gate):或非门是或门的输出信号经过非门得到的结果。

当任意一个输入信号为高电平时,输出信号为低电平;只有当所有输入信号都为低电平时,输出信号才为高电平。

6. 异或门(XOR Gate):异或门有两个输入信号和一个输出信号。

当两个输入信号相同时,输出信号为低电平;当两个输入信号不同时,输出信号为高电平。

7. 三态门(Tri-state Gate):三态门有一个控制信号和一个数据信号,以及一个输出信号。

当控制信号为高电平时,输出信号等于数据信号;当控制信号为低电平时,输出信号为高阻态。

8. 选择器(Multiplexer):选择器有多个输入信号和一个控制信号,以及一个输出信号。

根据控制信号的不同,将特定的输入信号输出到输出端。

9. 解码器(Decoder):解码器有多个输入信号和多个输出信号。

根据输入信号的不同,将特定的输出信号置为高电平,其余输出信号为低电平。

10. 加法器(Adder):加法器用于实现二进制数字的加法运算。

它有两个输入信号和一个进位输入信号,以及一个输出信号和一个进位输出信号。

实验一组合逻辑电路设计

实验一组合逻辑电路设计一、简介组合逻辑电路是数字电路的一种重要类型,由逻辑门组成,并且没有存储功能。

它的输出只取决于当前的输入状态,与过去的输入状态无关。

本实验旨在设计一组使用逻辑门构成的组合逻辑电路。

二、设计目标本实验的设计目标是实现一个4位2进制加法器电路。

输入为两个4位的二进制数,输出为其和。

为了方便起见,我们假设输入的二进制数已经在输入端以2进制的形式输入。

三、设计思路1.首先,需要设计一个4位的全加器电路,用于对两个位的进位进行处理。

全加器电路由三个输入和两个输出组成。

2.其次,将4个全加器电路组成4位的加法器电路,将各个位的进位进行连接。

3.最后,将输入的两个4位二进制数,以及4个进位信号,分别连接到4个全加器电路的输入端,将各个位的和输出连接到最终的输出端。

四、详细设计1.全加器电路的设计全加器电路有三个输入和两个输出。

其中,三个输入分别为A、B和Cin,分别表示两个相加的输入和进位输入。

两个输出分别为Sum和Cout,分别表示两个输入的和和进位输出。

我们可以使用两个半加器和一个或门来实现全加器电路。

半加器的真值表如下:A B Sum Cout0000011010101101其中,Sum表示两个输入的和,Cout表示两个输入的进位。

将两个半加器按照如下方式连接起来即可构成全加器电路:A --->+------> SumB --->+----------,----> CoutCin --->,--+2.四位加法器电路的设计四位加法器电路由4个全加器电路连接组成。

其中,第一个全加器的输入分别为A0、B0和Cin,输出为S0和C0;第二个全加器的输入分别为A1、B1和C0,输出为S1和C1;依次类推,第三个全加器的输入为A2、B2和C1,输出为S2和C2;第四个全加器的输入为A3、B3和C2,输出为S3和C3将四个全加器按照如下方式连接起来即可构成四位加法器电路:A0--->+---------------->S0B0--->+-------Cin ----,-+-------------------,-------> C0A1---+---->,---------------->S1B1---+---->,-------C0----,--------------,-+---------------,------->C1A2---+------>,---------------->S2B2---+------>,-------C1----,-+---------------->C2A3---+-------+---->,---------------->S3B3---+-----,--------3.输入输出连接将输入的两个4位二进制数依次连接到四位加法器电路的输入端,将四位加法器电路的输出端连接到最终的输出端。

《组合逻辑电路的设计实例》

组合逻辑电路设计实例1. 设计优先编码器设计要求:将Y 0 ~Y 9十个信号编成二进制代码。

其中Y 9的优先级别最高,Y 8次之,依次类推,Y 0优先级别最低。

当有多个信号同时出现在输入端时,要求只对优先级别最高的信号进行编码,且输入、输出都是低电平有效。

(1)分析要求。

Y 0 ~Y 9共十个信号,根据公式2n ≥N =10,取n =4,即取4位二进制码进行编码。

根据设计要求,Y 0 ~Y 9中优先级别高的排斥优先级别低的。

当输入端有多个信号同时存在时,优先级别低的信号无论电平高低,对输出均无影响。

(2)列真值表。

用1表示高电平,用0表示低电平。

由于规定低电平有效,且优先级别高的排斥优先级别低的,被排斥的量用“×”号表示。

输出4位二进制码用DCBA 表示,它们共有16种组合,用来对Y 0 ~Y 9进行编码的方案很多,我们采用其中一种方案。

优先编码器的真值表如表1所示。

表1 优先编码器真值表(3)化简。

因变量太多,用卡诺图化简不方便,可用公式法进行化简。

为便于用与或非门实现该电路,合并使函数值为0的最小项。

先求出反函数的最简与或式,然后再取反求出函数的最简与或非式。

根据真值表写表达式时,因为被排斥的变量对函数值没有影响,所以可以从相应的最小项中去掉,于是可得89899Y Y Y Y Y D +=+= 89Y Y D += 456789567896789789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y C +++=489589689789Y Y Y Y Y Y Y Y Y Y Y Y +++= 489589689789Y Y Y Y Y Y Y Y Y Y Y Y C +++=2345678934567896789789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y B +++=2458934589689789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y +++= 2458934589689789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y B +++=1234567893456789567897899Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y A ++++=124683468568789Y Y Y Y Y Y Y Y Y Y Y Y Y Y Y A ++++=(4)画逻辑图。

组合逻辑电路的设计举例

【例4】某工厂有三条生产线,耗电分别为1号线10kW,2号线 20kW,3号线30kW,生产线的电力由两台发电机组提供,其中1 号机组20kW,2号机组40kW。试设计一个供电控制电路,根据生 产线的开工情况启动发电机,使电力负荷达到最佳配置。

①逻辑抽象,列真值表 输入变量:生产线开工情况 A、B、C表示1、2、3号生产线, 生产线开工为1,停工为0;

1 11 1 1

水面低于检测元件——高电平; 无

水面高于检测元件——低电平; 水泵供水——高电平; 水泵不供水——低电平;

关 项

0 10 1 00

1 01 1 10

(二)写出函数式,同时化简 1、填写卡诺图: BC A 00 01 11 10

00 1 0

1 1

BC MS的卡诺图 A 00 01 11 10

4、将逻辑式化简或作适当变换: ① 使用小规模集成门电路,如不限种类 时,化为最简形式;如限制种类,要 变换成与器件相适应的形式。 ② 使用中规模组件时,将函数式变换成 与组件的逻辑函数相似的形式。

5、画出逻辑电路图。

给定逻辑功能

真值表

逻辑表达式 选定设器件计类型

和数目

表达式化简或 变换

逻辑电路图

二、组合逻辑电路的设计举例

A

1A VCC 1B 4B

1Y 4A

5V 如果要求用0 与非0 门实1 现 1 0 1、将函数式01 化为11 与非11 -与01非形11式

74LS00

B ML

2A 4Y 2B 3B

2Y 3A GND 3Y

C

MS

M S约 A ML束项 B

B0C

1

1

1

0

0

A 0 BC

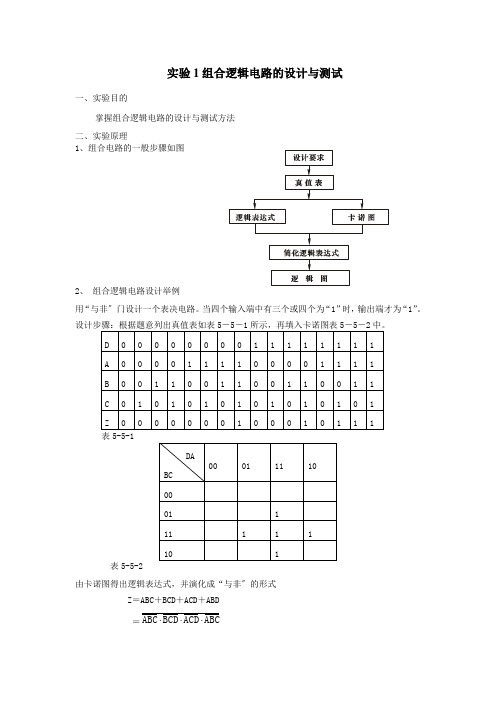

实验1组合逻辑电路的设计与测试

实验

1组合逻辑电路的设计与测试

一、实验目的 掌握组合逻辑电路的设计与测试方法

二、实验原理

1、组合电路的一般步骤如图

2、 组合逻辑电路设计举例

用“与非〞门设计一个表决电路。

当四个输入端中有三个或四个为“1”时,输出端才为“1”。

表5-5-1

表5-5-2

由卡诺图得出逻辑表达式,并演化成“与非〞的形式

Z =ABC +BCD +ACD +ABD

=ABC ACD BCD ABC ⋅⋅⋅

图5-5-1

表决逻辑电路

按图5-5-2接线,输入端A、B、C Z接逻辑电平显示输入插口,按真值表〔自拟〕要求,逐次改变输入变量,测量相应的输出值,验证逻辑功能,与表5-5-1进展比拟,验证所设计的逻辑电路是否符合要求。

三、实验设备与器件

1、+5V直流电源

2、逻辑电平开关

3、逻辑电平显示器

4、直流数字电压表

5、 74LS00 74LS20 cc4070

四、实验内容

1用与非门设计半加器

2用与非和异或门设计半加器

3用与非和异或设计全加器。

组合逻辑电路设计应用举例

目录 检测方案

信号的输入

数据选择器 数据的输出显示源自检测方案• 用数据选择器数据输入端Di作为各盏灯检测信号 的输入端,而选择器最后一级输出端驱动显示器 件,通过显示器的亮、熄区分灯的好坏。

信号的输入

• 在每盏灯的回路串联一采样电阻,并且在电阻两 端并联5V稳压管和限流电阻,由稳压管电压向检 测电路提供检测信号,灯好时检测信号输出5V电 压,灯坏时检测信号输出电压为零。

• 数据选择器地址码为六位“A5A4A3A2A1A0” (26>50) 可由五十进制的计数器输出端提供,计数状态要 用两位数码管显示,经CD4513二—十进制译码 器译码,控制数码管显示器。

总结

检测路灯电路若某路路灯损坏则该输入数据为Di为0, 第一级数据选择器输出W=1,然后再由第二级地址 码A5A4来判断四片十六选一中那一片输出W所对应 灯号,经第二级数据选择器输出Y=1,发光二极管 亮;同时控制二—十进制现在是译码器BI端使数码 管显示损坏的路灯号。反之,若无灯损坏,各路输 入Di均为1,则W=0,Y=0,发光二极管不亮,同时 使BI=0,数码管灭,不显示数字。

十六选一数据选择器

• 因为被检的是50盏灯,所以需要16选1 数据选择器四片其输入地址码均为A3~A0, 四片数据选择器满足了对于这50盏灯的 初级选择。

四选一数据选择器

• 四选一数据选择器其地址码为A5A4, 构成检测电路的第二级用来判断四片 十六选一 数据选择器中那一片输出所 对应灯号。

数据的输出与显示

The end,thank you!

组合逻辑电路的设计举例

C B ML A

ML 0 0 1 1

(二)写出函数式,同时化简 1、填写卡诺图: BC A 00 01 11 10 0 0 1 0 1

BC A 00 0 0 1

(三)选择器件和数目

选用非门、或门和与门各一个

(四)画逻辑图 A MS 1 1 3、列真值表: & B C

逻辑电路图

一、组合逻辑电路的一般设计步骤 1、进行逻辑抽象,列出真值表 ①确定输入、输出信号及其因果关系。 ②设定变量,进行状态赋值(编码)。 ③根据因果关系列真值表。 2、写出逻辑表达式 3、选定器件的类型和数目

门电路; 中规模组件; PLD

给定逻辑功能

真值表 逻辑表达式 设 计 选定器件类型 和数目 表达式化简或 变换 逻辑电路图

≥1

Y1

10

1

1

Y A B BC A B C 1 Y C AB 2

0 0 1 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 0 1 1 1 0 0 1

≥1

0 1 0 Y2 1 0 1 1 1

小结:组合电路的分析和设计方法

得到逻辑功能 一、组合电路的分析方法 给定逻辑图 1、由给定的逻辑图逐级写出逻辑式 2、对逻辑式进行化简或变换 3、列出输出函数的真值表 4、从真值表或函数式规律总结逻辑电路的功能

74LS00

【例 3】人类有 O、 A、 B、 AB4种基本血型,输血者与受血者 的血型必须符合图示原则。试用与非门设计一血型关系检测电 路,用以检测输血者与受血者之间的血型关系是否符合图示关 系,如果符合,输出为1,否则为0。 输血者 受血者 1、进行逻辑抽象,列出真值表 O O A 依题意:输血者的血型和受血者的血型 A 都是输入变量,二者之间的关系是否符 B B 合上述原则为输出函数L。 AB AB 编码:血型有四种取值,要区分开需2位 血 输血者 受血者 二进制编码,则共有4个输入逻辑变量。 型 C D E F 以CD和EF分别代表输血者和受血者 O 0 0 0 0 血型,进行如下编码: A 0 1 0 1 B 1 0 1 0 AB 1 1 1 1

组合逻辑电路设计实例

Y

D7

Y0 Y1

Y

DIN[14:7]

P334 图6-1

DIN[6:0,15] DIN[13:6]

74x151 74x151

DOUT15

DIN[5:0,15,14]

74x151

74x151

DOUT14

DIN[0,15:9]

DIN[8:1] DIN[15:8] DIN[7:0]

74x151 74x151

(注意有效电平)

74x148 EI A2~A0 GS I7~I0 EO

74x138

GI G2A,B CBA Y7~Y0 A[2:0] AVALID

74x148

EI

I7 I0

A2~A0 GS EO

B[2:0] BVALID

R_L[7:0] 最高优先输入为0,其余输入为1

级联比较器

Q[23:0] P[23:0]

双优先级编码器

可以找出最高和第二高优先级的编码器

74x148

EI

如何找第二高优先级?

先“排除”最高优先输入 再用74x148找一次 其他输入不变

A2~A0 GS I7~I0 EO

利用74x148 找出最高优先级 需要2个优先编码器 1个译码器、若干“与门”

强制最高优先输入无效 —— 利用译码器和“与门”实现

如何利用2输入4位多路复用控制移位?

74x157

G S A4~A0 Y4~Y0 B4~B0 基本原理:

DIN[3:0] DIN[2:0,3]

利用多路复用器,

通过控制数据输 入端的连接使输 出产生移位。

当S=0时,Y=A,不移位

当S=1时,Y=B,相当于移动一位

改变A端输入数据的连接顺序 可以使输出:左/右移动一或多位

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

给定逻辑功能

逻辑电路图

一、组合逻辑电路的一般设计步骤 1、进行逻辑抽象,列出真值表 、进行逻辑抽象, 确定输入、输出信号及其因果关系。 ①确定输入、输出信号及其因果关系。 设定变量,进行状态赋值(编码)。 ②设定变量,进行状态赋值(编码)。 根据因果关系列真值表。 ③根据因果关系列真值表。 2、写出逻辑表达式 、 3、选定器件的类型和数目 、

B C

③逻辑电路图

& A 1

10 1

BC A 00 0 1

输入 输出 1 A B C Y1 Y2

真值表 &

0& 1 0 & 1 0 1 0 1

≥1

Y1

Y1 = AB + BC + ABC Y2 = C + AB

0 0 1 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 0 1 1 1 0 0 1

74LS00

【 例 3】人类有 、 A、B、AB4种基本血型 , 输血者与受血者 】 人类有O、 、 、 4 种基本血型, 的血型必须符合图示原则。 的血型必须符合图示原则。试用与非门设计一血型关系检测电 路 , 用以检测输血者与受血者之间的血型关系是否符合图示关 如果符合,输出为1,否则为0。 系,如果符合,输出为 ,否则为 。 输血者 受血者 1、进行逻辑抽象,列出真值表 、进行逻辑抽象, O O A 依题意:输血者的血型和受血者的血型 依题意: A 都是输入变量, 都是输入变量 , 二者之间的关系是否符 B B 合上述原则为输出函数L。 合上述原则为输出函数 。 AB AB 编码:血型有四种取值,要区分开需2位 编码:血型有四种取值,要区分开需 位 血 输血者 受血者 二进制编码,则共有4个输入逻辑变量 个输入逻辑变量。 二进制编码,则共有 个输入逻辑变量。 型 C D E F 以CD和EF分别代表输血者和受血者 和 分别代表输血者和受血者 分别 O 0 0 0 0 血型,进行如下编码: 血型,进行如下编码: A 0 1 0 1 B 1 0 1 0 AB 1 1 1 1

0 0 0 0 1 0 0 1 0 如果要求用与非门实现 0 0 1 1 1 1、将函数式化为与非 与非形式 与非-与非 1 、将函数式化为与非 与非形式 1 1 1 1 0 1 0 × ××1× Nhomakorabea10

MS的卡诺图

01 11 0 1

MS ML ML 0

× ×

×

1

ML的卡诺图

2、化简,得到最简与或式: 、化简,得到最简与或式:

MS = A + BC; M L = B

M S 约 A + BC = A ⋅ B C = × 1 0 0 ML束 B = 1 0 1 × 项 1 1 0 ×

× × ×

2、由上式可知需要4个与非门。 (三)选择器件和数目 、由上式可知需要 个与非门 个与非门。 3、画逻辑图 、 选用非门、 选用非门、或门和与门各一个 A & & MS (四)画逻辑图 B & A & ≥ 1 MS 1 3、列真值表: 、列真值表: & C B ML A B C MS ML C 可选用74LS00实现该逻辑图。 实现该逻辑图。 可选用 实现该逻辑图 ML 0 0 0 0 0 5V 1 0 0 1 0 VCC 1A 如果要求用与非门实现 A 0 0 1 1 1 1B 4B 1、将函数式化为与非 与非形式 与非-与非 1 、将函数式化为与非 与非形式 1 1 1 1 1Y 4A 0 1 MS M 约 A + BC = A 0 BC× × 2A = B 4Y ⋅ S C × × 1 0 0 ML 2B 3B ML束 B 1 0 1 × × = 3A 2Y 项 GND 3Y 1 1 0 × ×

4、画出逻辑图 C D E F & & & & & L & &

2、写出函数式,同时化简 、写出函数式, EF 00 01 11 10 CD 00 1 1 1 受血者 1 输血者 01 0 1 O1 0O A A 11 0 0 B 1 0B 10 0 0 AB 1 1 AB 血 输血者 受血者 L=CD+EF+C E E F+D F 型 C D O 0 0 3、将表达式化为与非式 0 A 0 1 0 L = CD• EF •1C 0 • D F 1 E B AB 1 1 1 0 1 0 1

输入 输出 A B C Y1 Y2

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

0 0 1 1 1 0 0 1

0 1 0 1 0 1 1 1

②写出函数式,同时化简 写出函数式, BC A 00 0 1 1 01 1 1 01 11 1 1 11 1 1 10 1

L1 L2

I2 该电路可以选取四二输入端 真值表 与非门74LS00和六反相器 与非门 和六反相器 I0 I1 74LS04连接构成,2 L0 L1 连接构成, 连接构成 I 也可以用 两片74LS00。 两片 1 。1A × V1 0 × CC 1B 0 1 × 4B 1 0 1Y 0 0 1 4A 0 0 2A 4Y 0 0 0 3B 0 0 2B 3A 2Y GND 3Y

≥1

0 1 0 Y2 1 0 1 1 1

小结: 小结:组合电路的分析和设计方法

得到逻辑功能 一、组合电路的分析方法 给定逻辑图 1、由给定的逻辑图逐级写出逻辑式 、 2、对逻辑式进行化简或变换 、 3、列出输出函数的真值表 、 4、从真值表或函数式规律总结逻辑电路的功能 、

列真值表: 列真值表 输 入 CD EF 00 00 00 01 00 10 00 11 01 01 01 11 10 10 10 11 11 11 … …

输 出 L 1 1 1 1 1 1 1 1 1 0

2、写出函数式,同时化简 、写出函数式, EF 00 01 11 10 CD 00 1 1 1 受血者 1 输血者 01 0 1 O1 0O A A 11 0 0 B 1 0B 10 0 0 AB 1 1 AB 血 输血者 受血者 L=CD+EF+C E E F+D F 型 C D O 0 0 3、将表达式化为与非式 0 A 0 1 0 L = CD• EF •1C 0 • D F 1 E B AB 1 1 1 0 1 0 1

74LS00

L0 = I 0

L1 = I 0 I 1 L2 = I 0 I 1 I 2 = I 0 I 1 ⋅ I 2

L2 0 0 1 0

供水, 【例2】水箱由大小两台水泵 L、MS供水, 】水箱由大小两台水泵M A,B,C为水位检测元件,水位低于检测元件时 为水位检测元件, 为水位检测元件 检测元件给出高电平,否则给出低电平。 检测元件给出高电平,否则给出低电平。 MS

门电路; 中规模组件; 门电路; 中规模组件; PLD

给定逻辑功能 真值表 逻辑表达式 设 计 选定器件类型 和数目 表达式化简或 变换 逻辑电路图

4、将逻辑式化简或作适当变换: 、将逻辑式化简或作适当变换: 使用小规模集成门电路, ① 使用小规模集成门电路,如不限种类 化为最简形式;如限制种类, 时,化为最简形式;如限制种类,要 变换成与器件相适应的形式。 变换成与器件相适应的形式。 使用中规模组件时, ② 使用中规模组件时,将函数式变换成 与组件的逻辑函数相似的形式。 与组件的逻辑函数相似的形式。 5、画出逻辑电路图。 、画出逻辑电路图。

仿真演示

【例4】某工厂有三条生产线,耗电分别为1号线10kW,2号线 某工厂有三条生产线,耗电分别为1号线10kW, 10kW 20kW, 号线30kW 生产线的电力由两台发电机组提供,其中1 30kW, 20kW,3号线30kW,生产线的电力由两台发电机组提供,其中1 号机组20kW 20kW, 号机组40kW 试设计一个供电控制电路, 40kW。 号机组20kW,2号机组40kW。试设计一个供电控制电路,根据生 产线的开工情况启动发电机,使电力负荷达到最佳配置。 产线的开工情况启动发电机,使电力负荷达到最佳配置。 ①逻辑抽象,列真值表 逻辑抽象, 输入变量: 输入变量:生产线开工情况 A、B、C表示 、2、3号生产线, 、 、 表示 表示1、 、 号生产线 号生产线, 生产线开工为1,停工为0; 生产线开工为 ,停工为 ; 输出变量:发电机组工作情况 输出变量: Y1、Y2表示 、2号发电机组, 、 表示 表示1、 号发电机组 号发电机组, 发电机组启动为1,停机为0; 发电机组启动为 ,停机为 ; 真值表

二、组合逻辑电路的设计举例 【例1】火车站有特快、直快和慢车三种列车进出,要求用二输 】火车站有特快、直快和慢车三种列车进出, 入与非门和反相器设计一个指示列车等待进站的逻辑电路。 入与非门和反相器设计一个指示列车等待进站的逻辑电路。 进行逻辑抽象,列出真值表。 1、进行逻辑抽象,列出真值表。 输入信号- 各种列车的进站请求信号: 输入信号- 各种列车的进站请求信号: 设特快、直快和慢车的进站请求信号为: 设特快、直快和慢车的进站请求信号为:I0、I1、I2 规定有请求为1;无请求为0。 规定有请求为 ;无请求为 。 真值表 信号优先顺序: →→I →→I 信号优先顺序:I0→→ 1→→ 2 输出信号- 3个指示灯的状态 个指示灯的状态: 输出信号- 3个指示灯的状态:L0,L1,L2 规定灯亮为1;灯灭为 。 规定灯亮为 ;灯灭为0。 L0亮,指示特快进站 控制关系: 控制关系: L 亮,指示直快进站 1 L2亮,指示慢车进站

C B ML A

ML 0 0 1 1

× × × ×

(二)写出函数式,同时化简 写出函数式, 1、填写卡诺图: 、填写卡诺图: BC A 00 01 11 10 0 0 1 0 × 1 × BC A 00 0 0 1 ×

(三)选择器件和数目 选用非门、 选用非门、或门和与门各一个 (四)画逻辑图 A ≥ 1 MS 1 3、列真值表: 、列真值表: & B C A B C