Integrated_Circuits(集成电路)电子信息类专业英语、计算机类专业英语文章汇编

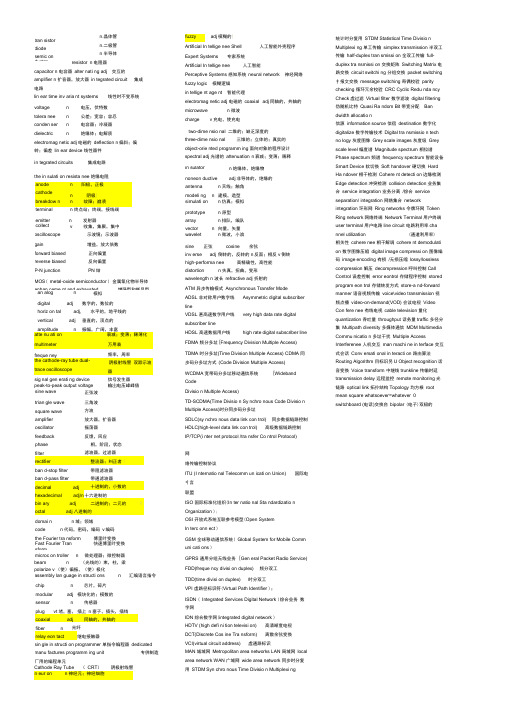

电子信息工程专业英语词汇 专外1

专外VLSI Very large scale integrated circuit 超大规模集成电路IC Integrated circuit 集成电路LSI Large scale integrated 大规模集成MOS Metal-Oxide-Semiconduter金属氧化物半导体CMOS Complementary Metal-Oxide-Semiconduter互补金属氧化物半导体ECL Emitter Coupled Logic射级耦合逻辑UV ultraviolet 紫外线MIPS Million Instruction Per Second百万条指令每秒ALU Arithmetic Logic Unit算术逻辑单元BIOS Base Input Output System基本输入输出系统OA Operation Amplifiers运算放大器GBW Gain*Bandwidth增益带宽积DC Direct Current直流电AC Alternating Current交流电GSM Global System of Mobile communication全球移动通信系统SCR Silicon Controlled Rectifier可控硅整流器TCXO Tempretuer Compensated Crystal Oscillator温度补偿晶体振荡器VCO Voltage Controlled Oscillator压控振荡器PLL Phase Locked Loop锁相环VSWR Voltage Standing Wave Ratio电压驻波比FCC Fedal Communications Commission联邦通信委员会PTT Post Telephone and Telegraph Administration邮电管理局MTSO Mobile Telephone Switching Office移动电话交换局MSC Mobile Switching Center移动交换中心PSTN Public Switching Telephone Network公共交换电话网TDM Time Division Multiplexing时分复用PCM Pulse code Modulation脉冲编码调制PCS Personal Communication Service个人通信业务FDM Frequency Division Multiplexing频分复用CD Compact disc光盘CAD Computer Aided Design计算机辅助设计EDA Electronic Design Automation电子设计自动化HDL Hardware Description Language硬件描述语言ASIC Application Specific Integration Circuit专用集成电路PLD Programmable Logic Device可编程逻辑器件PLA Programmable Logic Array可编程逻辑阵列FPGA Filed Programmable Gate Array现场可编程门阵列RTL Register Transfer level寄存器传递级OTP One-time Programmable一次可编程ISP In-system Programmable在系统可编程ASSP Application-specific Standard Parts专用标准器件SPLD Simple Programmable Logic Device简单可编程逻辑器件CPLD Complex Programmable Logic Device复杂可编程逻辑器件NRE Nonrecurring Engineering一次性工程SDR Software-Defined Radios软件无线电SP Digital Signal Processor数字信号处理器SoC System-on-ChipRC Reconfigurable Computing可重配计算IEEE Institute of Electrical and Electronics Engineers电器与电子工程师学会EPROM Electrically Erasable Programmable Read-Only Memory电可擦除可编程只读存储器DRAM Dynamic Random Access Memory动态随机存取存储器SRAM Static Random Access Memory静态随机存取存储器DAC Digital-to-Analog Converter数字模拟转换器ROM Read Only Memory只读存储器占空比Duty cycle真空电子管Vamcuum tube触发器flip flop品质因数quality factor过采样over-sampling复平面complex plane低通滤波器Low-pass filter软盘Floppy disk地址指针Address pointer接口电路Interface circuitry沟道电容器Trench capacitor三态缓冲器Tri-state buffer引导扇区Boot sector汇编语言Assembly language操作码Operating code传输函数Transfer function数据手册Data sheet入厂检查Incoming inspection线路驱动器line driver电平移动器Level shifter信号调节器Signal conditioner电流源Current source电压源Voltage source一阶滤波First-Order Filters二阶低通滤波器Second-order Low-Pass Filters 复频率变量complex-frequency variable 角频率angular frequency暂态响应transient response阶跃函数step function参考电压reference voltage电源power supply线性稳压器liner regulator负载电流load current反向偏压back bias晶体振荡器crystal oscillator补偿振荡器compensated Oscillator串联谐振series resonant并联谐振parallel resonant谐振频率resonanting frequency反馈元件feedback element鉴相器phase detector鉴频器frequency detector频率合成器frequency synthesizer电荷泵charge pump环路滤波器loop filter死区deadband传播延迟propagation delay时钟抖动clock jitter传输线transmission line电压反射voltage reflection功率损耗power loss接触电阻contact resistance频率响应frequency response电流current flow边缘卡edge card母板motherboard子板daughter board扁平电缆ribbon cable分组交换packet switching无绳电话cordless phone基站base station拨号音dial tone频率重用frequency reuse端局end office增量调制delta modulation预测编码predictive encoding保护时间guard time纠错error correction频率冲突frequency conflict总速率gross rate编码理论coding theory随机噪声random noise二进制反码one’complement扩频通信spread spectrum communication 微弱信号weak signal发射功率transmission power嵌入式系统embedded system模块(构件)building block金属互联metal interconnect设计流程design flow现状present state状态机state machine次态next state数据处理data processing胶连逻辑glue logic测试台test bench高阻high impedance类型转换type conversion学习曲线learning curve。

电子行业转贴电子专业英语

电子行业转贴电子专业英语引言随着电子行业的蓬勃发展,电子专业英语在该行业中变得越来越重要。

掌握电子专业英语不仅有助于从事电子工程相关工作的人员流畅地与国际伙伴交流,还能提高在电子行业中的竞争力。

本文将转贴一些常用的电子专业英语词汇和短语,希望能对电子行业从业人员和学生提供帮助。

1. 电子器件和设备的英语词汇•Semiconductors(半导体)•Resistors(电阻器)•Capacitors(电容器)•Inductors(电感器)•Transistors(晶体管)•Diodes(二极管)•Integrated Circuits(集成电路)•Microcontrollers(微控制器)•Printed Circuit Boards(印刷电路板)•Power Supplies(电源)2. 电子行业的工作职位和专业术语•Electrical Engineer(电气工程师)•Electronics Technician(电子技术员)•Circuit Designer(电路设计师)•Hardware Engineer(硬件工程师)•Analog Design Engineer(模拟设计工程师)•Digital Design Engineer(数字设计工程师)•Quality Control Engineer(质量控制工程师)•Test Engineer(测试工程师)•Firmware Engineer(固件工程师)•Project Manager(项目经理)3. 电子行业常见缩写和首字母缩写•PCB: Printed Circuit Board(印刷电路板)•IC: Integrated Circuit(集成电路)•LED: Light-Emitting Diode(发光二极管)•BOM: Bill of Materials(物料清单)•SMT: Surface Mount Technology(表面贴装技术)•ESD: Electrostatic Discharge(静电放电)•EMC: Electromagnetic Compatibility(电磁兼容性)•PCB: Personal Computer Board(个人电脑板)•ADC: Analog-to-Digital Converter(模数转换器)•DAC: Digital-to-Analog Converter(数模转换器)4. 交流时常用的电子专业英语短语•Can you please expln that in simple terms?(你能简单地解释一下吗?)•I’m sorry, I didn’t understand what you just sd.(对不起,我刚才没听懂你说的话。

电子行业电子工程专业英文词汇

电子行业电子工程专业英文词汇IntroductionIn the rapidly developing field of electronics, it is essential for professionals in the electronic engineering industry to be familiar with the relevant technical terms and vocabulary in the English language. This article ms to provide a comprehensive list of key English terms commonly used in the electronic engineering profession.Key Vocabulary1.Analog Circuit: A circuit that consists of analog electronics components, such as resistors, capacitors, and inductors, to process continuous-time signals.2.Digital Circuit: A circuit that operates using digital logic, utilizing binary digits (bits) to process and transmit information.3.Microcontroller: An integrated circuit that contns a CPU, memory, and input/output peripherals, designed for embedded systems.4.Integrated Circuit (IC): A microelectronic circuit that contns multiple electronic components, such as transistors and resistors, integrated into a single chip.5.Printed Circuit Board (PCB): A flat board made of non-conductive material on which electronic components are mounted and interconnected using conductive tracks.6.Signal Processing: Processing and manipulation of signals to extract relevantinformation or alter the characteristics of the signal.7.Semiconductor: A material with electrical conductivity between a conductor and an insulator, commonly used in electronic components such as diodes and transistors. 8.Transistor: A semiconductor device that amplifies or switches electronic signals and forms a key building block for electronic circuits.9.Resistor: An electronic component that restricts the flow of electric current, typically used to control voltage or current levels.10.C apacitor: An electronic component that stores electrical energy in an electric field and is used to store and release energy in electronic circuits.11.I nductor: An electronic component that stores energy in a magnetic field and is used in circuits for energy storage or filtering.12.D iode: A two-terminal electronic component that conducts current primarily in one direction, commonly used as a rectifier.13.V oltage: The electric potential difference between two points, measured in volts (V). 14.C urrent: The flow of electric charge, measured in amperes (A).15.R esistance: The opposition to the flow of electric current, measured in ohms (Ω).16.P ower: The rate at which work is performed or energy is transferred, measured in watts (W).17.F requency: The number of complete cycles of a periodic waveform that occur per second, measured in hertz (Hz).18.A mplitude: The maximum extent of a vibration or oscillation, measured from the equilibrium position.19.O hm’s Law: A fundamental law in electronics stating that the current flowingthrough a conductor is directly proportional to the voltage across it, and inversely proportional to the resistance.20.K irchhoff’s Laws: A set of f undamentallaws in circuit theory that describe theconservation of electric charge and energy inelectrical circuits.ConclusionThis document provides a comprehensive list of key English terms commonly used in the electronic engineering profession. Familiarity withthese terms is essential for professionals in the electronic industry to effectively communicate and understand the technical aspects of their work. Further research and study of these terms will contribute to a deeper understanding of electronic engineering concepts and principles.。

电子信息工程专业英语词汇汇编

transistor n.晶体管diode n.二极管semiconductor n 半导体resistor n 电阻器capacitor n 电容器alternating adj 交互的amplifier n 扩音器,放大器integrated circuit 集成电路linear time invariant systems 线性时不变系统voltage n 电压,伏特数tolerance n 公差;宽容;容忍condenser n 电容器;冷凝器dielectric n 绝缘体;电解质electromagnetic adj 电磁的deflection n偏斜;偏转;偏差linear device 线性器件the insulation resistance 绝缘电阻anode n 阳极,正极cathode n 阴极breakdown n 故障;崩溃terminal n 终点站;终端,接线端emitter n 发射器collect v 收集,集聚,集中oscilloscope 示波镜;示波器gain 增益,放大倍数forward biased 正向偏置reverse biased 反向偏置P-N junction PN结MOS(metal-oxide semiconductor)金属氧化物半导体enhancement and exhausted 增强型和耗尽型integrated circuits 集成电路analog n 模拟digital adj 数字的,数位的horizontal adj, 水平的,地平线的vertical adj 垂直的,顶点的amplitude n 振幅,广阔,丰富attenuation 衰减;变薄;稀薄化multimeter 万用表frequency 频率,周率the cathode-ray tube 阴极射线管dual-trace oscilloscope 双踪示波器signal generating device 信号发生器peak-to-peak output voltage 输出电压峰峰值sine wave 正弦波triangle wave 三角波square wave 方波amplifier 放大器,扩音器oscillator 振荡器feedback 反馈,回应phase 相,阶段,状态filter 滤波器,过滤器rectifier 整流器;纠正者band-stop filter 带阻滤波器band-pass filter 带通滤波器decimal adj 十进制的,小数的hexadecimal adj/n十六进制的binary adj 二进制的;二元的octal adj 八进制的domain n 域;领域code n代码,密码,编码v编码the Fourier transform 傅里叶变换Fast Fourier Transform 快速傅里叶变换microcontroller n 微处理器;微控制器assembly language instructions n 汇编语言指令chip n 芯片,碎片modular adj 模块化的;模数的sensor n 传感器plug vt堵,塞,插上n塞子,插头,插销coaxial adj 同轴的,共轴的fiber n 光纤relay contact 继电接触器single instruction programmer 单指令编程器dedicated manufactures programming unit 专供制造厂用的编程单元beam n (光线的)束,柱,梁polarize v(使)偏振,(使)极化Cathode Ray Tube(CRT)阴极射线管neuron n神经元;神经细胞fuzzy adj 模糊的Artificial Intelligence Shell 人工智能外壳程序Expert Systems 专家系统Artificial Intelligence 人工智能Perceptive Systems 感知系统neural network 神经网络fuzzy logic 模糊逻辑intelligent agent 智能代理electromagnetic adj 电磁的coaxial adj 同轴的,共轴的microwave n 微波charge v充电,使充电insulator n 绝缘体,绝缘物nonconductive adj非导体的,绝缘的antenna n天线;触角modeling n建模,造型simulation n 仿真;模拟prototype n 原型array n 排队,编队vector n 向量,矢量wavelet n 微波,小浪sine 正弦cosine 余弦inverse adj倒转的,反转的n反面;相反v倒转high-performance 高精确性,高性能two-dimensional 二维的;缺乏深度的three-dimensional 三维的;立体的;真实的object-oriented programming面向对象的程序设计spectral adj 光谱的attenuation n衰减;变薄;稀释distortion n 失真,扭曲,变形wavelength n 波长refractive adj 折射的ATM 异步传输模式Asynchronous Transfer ModeADSL非对称用户数字线Asymmetric digital subscriberlineVDSL甚高速数字用户线very high data rate digitalsubscriber lineHDSL高速数据用户线high rate digital subscriber lineFDMA频分多址(Frequency Division Multiple Access)TDMA时分多址(Time Division Multiple Access)CDMA同步码分多址方式(Code Division MultipleAccess)WCDMA宽带码分多址移动通信系统(Wideband CodeDivision Multiple Access)TD-SCDMA(Time Division Synchronous Code DivisionMultiple Access)时分同步码分多址SDLC(synchronous data link control)同步数据链路控制HDLC(high-level data link control)高级数据链路控制IP/TCP(internet protocol /transfer Control Protocol)网络传输控制协议ITU (International Telecommunication Union)国际电信联盟ISO国际标准化组织(International StandardizationOrganization);OSI开放式系统互联参考模型(Open SystemInterconnect)GSM全球移动通信系统(Global System for MobileCommunications)GPRS通用分组无线业务(General Packet Radio Service)FDD(frequency division duplex)频分双工TDD(time division duplex)时分双工VPI虚路径标识符(Virtual Path Identifier);ISDN(Integrated Services Digital Network)综合业务数字网IDN综合数字网(integrated digital network)HDTV (high definition television)高清晰度电视DCT(Discrete Cosine Transform)离散余弦变换VCI(virtual circuit address)虚通路标识MAN城域网Metropolitan area networksLAN局域网local area networkWAN广域网wide area network同步时分复用STDM Synchronous Time DivisionMultiplexing统计时分复用STDM Statistical Time DivisionMultiplexing单工传输simplex transmission半双工传输half-duplex transmission全双工传输full-duplex transmission交换矩阵Switching Matrix电路交换circuit switching分组交换packet switching报文交换message switching奇偶校验parity checking循环冗余校验CRC Cyclic Redundancy Check虚过滤Virtual filter数字滤波digital filtering伪随机比特Quasi Random Bit带宽分配Bandwidth allocation信源information source信宿destination数字化digitalize数字传输技术Digital transmission technology灰度图像Grey scale images灰度级Grey scale level幅度谱Magnitude spectrum相位谱Phase spectrum频谱frequency spectrum智能设备Smart Device软切换Soft handover硬切换Hard Handover相干检测Coherent detection边缘检测Edge detection冲突检测collision detection业务集合service integration业务分离/综合service separation/ integration网络集合network integration环形网Ring networks令牌环网Token Ring network网络终端Network Terminal用户终端user terminal用户电路line circuit电路利用率channel utilization(通道利用率)相关性coherence相干解调coherent demodulation数字图像压缩digital image compression图像编码image encoding有损/无损压缩lossy/lossless compression解压decompression呼叫控制Call Control误差控制error control存储程序控制stored program control存储转发方式store-and-forward manner语音\视频传输voice\video transmission视频点播video-on-demand(VOD)会议电视Video Conference有线电视cable television量化quantization吞吐量throughput话务量traffic多径分集Multipath diversity多媒体通信MDM Multimedia Communication多址干扰Multiple Access Interference人机交互man machine interface交互式会话Conversational interaction路由算法Routing Algorithm目标识别Object recognition话音变换Voice transform中继线trunk line更多精品文档传输时延transmission delay远程监控remote monitoring光链路optical link拓扑结构Topology均方根root mean squarewhatsoever=whatever 0switchboard (电话)交换台bipolar (电子)双极的premise (复)房屋,前提cursor (计算机尺的)游标,指导的elapse (时间)经过,消失vaporize (使)蒸发subsystem (系统的)分部,子系统,辅助系统metallic (像)金属的,含金属的,(声音)刺耳的dispatch (迅速)派遣,急件consensus (意见)一致,同意deadline (最后)期限,截止时间tomographic X线体层摄像的alas 唉,哎呀cluster 把…集成一束,一组,一簇,一串,一群encyclopedia 百科全书millionfold 百万倍的semiconductor 半导体radius 半径范围,半径,径向射线half-duplex transmission 半双工传输accompaniment 伴随物,附属物reservation 保留,预定quotation 报价单,行情报告,引语memorandum 备忘录redundancy 备用be viewed as 被看作…be regards as 被认为是as such 本身;照此;以这种资格textual 本文的,正文的verge 边界variation 变化,变量conversion 变化,转化identity 标识;标志criterion 标准,准则in parallel on 并联到,合并到juxtapose 并置,并列dialing pulse 拨号脉冲wave-guide 波导wavelength division multiplexed 波分复用baud rate 波特率playback 播放(录音带,唱片)no greater than 不大于update 不断改进,使…适合新的要求,更新asymmetric 不对称的irrespective 不考虑的,不顾的inevitably 不可避免的inevitable 不可避免的,不可逃避的,必定的segment 部分abrasion 擦伤,磨损deploy 采用,利用,推广应用take the form of 采用…的形式parameter 参数,参量layer 层dope 掺杂FET(field effect transistors) 场效应管audio recording 唱片ultra-high-frequency(UHF) 超高频in excess of 超过in excess of 超过hypertext 超文本ingredient 成分,因素ingredient 成分,组成部分,要素metropolitan-area network(WAN) 城域网metropolitan area network(WAN) 城域网,城市网络congestion 充满,拥挤,阻塞collision 冲突extractive 抽出;释放出extract 抽取,取出,分离lease 出租,租约,租界期限,租界物pass on 传递,切换transmission 传输facsimile 传真innovative=innovatory 创新的,富有革新精神的track 磁道impetus 促进,激励cluster 簇stored-program control(SPC) 存储程序控制a large number of 大量的peal 大声响,发出supersede 代替supplant 代替,取代out-of-band signaling 带外信号simplex transmission 单工传输monochromatic 单色的,单色光的,黑白的ballistic 弹道的,射击的,冲击的conductor 导体hierarchy 等级制度,层次infrastructure 底层结构,基础结构geographic 地理的,地区的geographically 地理上GIS(ground instrumentation system) 地面测量系统ground station 地面站earth orbit 地球轨道extraterrestrial 地球外的,地球大气圈外的Land-sat 地球资源卫星rug 地毯,毯子ignite 点火,点燃,使兴奋electromagnetic 电磁的inductive 电感arc 电弧telephony 电话(学),通话dielectric 电介质,绝缘材料;电解质的,绝缘的capacitor 电容telecommunication 电信,无线电通讯scenario 电影剧本,方案modem pool 调制解调器(存储)池superimposing 叠加,重叠pin 钉住,扣住,抓住customize 定做,定制monolithic 独立的,完全统一的aluminize 镀铝strategic 对全局有重要意义的,战略的substantial 多的,大的,实际上的multi-path fading 多径衰落multi-path 多路,多途径;多路的,多途径的multi-access 多路存取,多路进入multiplex 多路复用multiplex 多路复用的degradation 恶化,降级dioxide 二氧化碳LED(light-emitting-diode) 发光二极管evolution 发展,展开,渐进feedback 反馈,回授dimension 范围,方向,维,元scenario 方案scenario 方案,电影剧本amplifer 放大器noninvasive 非侵略的,非侵害的tariff 费率,关税率;对…征税distributed functional plane(DFP) 分布功能平面DQDB(distributed queue dual bus) 分布式队列双总线hierarchy 分层,层次partition 分成segmentation 分割interface 分界面,接口asunder 分开地,分离地detached 分离的,分开的,孤立的dispense 分配allocate 分配,配给;配给物centigrade 分为百度的,百分度的,摄氏温度的fractal 分形molecule 分子,微小,些微cellular 蜂窝状的cellular 蜂窝状的,格形的,多孔的auxiliary storage(also called secondary storage) 辅助存储器decay 腐烂,衰减,衰退negative 负电vicinity 附近,邻近vicinity 附近地区,近处sophisticated 复杂的,高级的,现代化的high-frequency(HF) 高频high definition television 高清晰度电视chromium 铬annotate 给…作注解in terms of 根据,按照disclosure 公布,企业决算公开public network公用网functionality 功能,功能度mercury 汞resonator 共鸣器resonance 共振whimsical 古怪的,反复无常的administration 管理,经营cursor 光标(显示器),游标,指针optical computer 光计算机photoconductor 光敏电阻optical disks 光盘optically 光学地,光地wide-area networks 广域网specification 规范,说明书silicon 硅the international telecommunication union(ITU) 国际电信联盟excess 过剩obsolete 过时的,废弃的maritime 海事的synthetic 合成的,人造的,综合的synthetic 合成的,综合性的rational 合乎理性的rationalization 合理化streamline 合理化,理顺infrared 红外线的,红外线skepticism 怀疑论ring network 环形网hybrid 混合物counterpart 伙伴,副本,对应物electromechanical 机电的,电动机械的Robot 机器人Robotics 机器人技术,机器人学accumulation 积累infrastructure 基础,基础结构substrate 基质,底质upheaval 激变,剧变compact disc 激光磁盘(CD)concentrator 集中器,集线器centrex system 集中式用户交换功能系统converge on 集中于,聚集在…上lumped element 集总元件CAI(computer-aided instruction) 计算机辅助教学computer-integrated manufacturing(CIM) 计算机集成制造computer mediated communication(CMC) 计算机中介通信record 记录register 记录器,寄存器expedite 加快,促进weight 加权accelerate 加速,加快,促进更多精品文档categorize 加以类别,分类in addition 加之,又,另外hypothetical 假设的rigidly 坚硬的,僵硬的compatibility 兼容性,相容性surveillance 监视surveillance 监视retrieval 检索,(可)补救verification 检验simplicity 简单,简明film 胶片,薄膜take over 接管,接任ruggedness 结实threshold 界限,临界值with the aid of 借助于,用,通过wire line 金属线路,有线线路coherent 紧凑的,表达清楚的,粘附的,相干的compact 紧密的approximation 近似undertake 进行,从事transistor 晶体管elaborate 精心制作的,细心完成的,周密安排的vigilant 警戒的,警惕的alcohol 酒精,酒local area networks(LANs) 局域网local-area networks(LANs) 局域网drama 剧本,戏剧,戏剧的演出focus on 聚集在,集中于,注视insulator 绝缘root mean square 均方根uniform 均匀的open-system-interconnection(OSI) 开放系统互连expire 开始无效,满期,终止immunity 抗扰,免除,免疫性take…into account 考虑,重视…programmable industrial automation 可编程工业自动化demountable 可拆卸的tunable 可调的reliable 可靠be likely to 可能,大约,像要videotex video 可视图文电视negligible 可以忽略的aerial 空气的,空中的,无形的,虚幻的;天线broadband 宽(频)带pervasive 扩大的,渗透的tensile 拉力的,张力的romanticism 浪漫精神,浪漫主义discrete 离散,不连续ion 离子force 力量;力stereophonic 立体声的continuum 连续统一体,连续统,闭联集smart 灵巧的;精明的;洒脱的token 令牌on the other hand 另一方面hexagonal 六边形的,六角形的hexagon 六角形,六边形monopoly 垄断,专利video-clip 录像剪辑aluminum 铝pebble 卵石,水晶透镜forum 论坛,讨论会logical relationships 逻辑关系code book 码本pulse code modulation(PCM) 脉冲编码调制roam 漫步,漫游bps(bits per second) 每秒钟传输的比特ZIP codes 美国邮区划分的五位编码susceptible(to) 敏感的,易受…的analog 模拟,模拟量pattern recognition 模式识别bibliographic 目录的,文献的neodymium 钕the european telecommunication standardizationinstitute(ETSI) 欧洲电信标准局coordinate 配合的,协调的;使配合,调整ratify 批准,认可bias 偏差;偏置deviate 偏离,与…不同spectrum 频谱come into play 其作用entrepreneurial 企业的heuristic methods 启发式方法play a …role(part) 起…作用stem from 起源于;由…发生organic器官的,有机的,组织的hypothesis 前提front-end 前置,前级potential 潜势的,潜力的intensity 强度coincidence 巧合,吻合,一致scalpel 轻便小刀,解剖刀inventory 清单,报表spherical 球的,球形的distinguish 区别,辨别succumb 屈服,屈从,死global functional plane(GFP) 全局功能平面full-duplex transmission 全双工传输hologram 全息照相,全息图deficiency 缺乏thermonuclear 热核的artifact 人工制品AI(artificial intelligence) 人工智能fusion 熔解,熔化diskettes(also called floppy disk) 软盘sector 扇区entropy 熵uplink 上行链路arsenic 砷neural network 神经网络very-high-frequency(VHF) 甚高频upgrade 升级distortion 失真,畸变identification 识别,鉴定,验明pragmatic 实际的implementation 实施,实现,执行,敷设entity 实体,存在vector quantification 矢量量化mislead 使…误解,给…错误印象,引错vex 使烦恼,使恼火defy 使落空facilitate 使容易,促进retina 视网膜compatible 适合的,兼容的transceiver 收发两用机authorize 授权,委托,允许data security 数据安全性data independence 数据独立data management 数据管理database 数据库database management system(DBMS) 数据库管理信息系统database transaction 数据库事务data integrity 数据完整性,数据一致性attenuation 衰减fading 衰落,衰减,消失dual 双的,二重的transient 瞬时的deterministic 宿命的,确定的algorithm 算法dissipation 损耗carbon 碳diabetes 糖尿病cumbersome 讨厌的,麻烦的,笨重的razor 剃刀,剃go by the name of 通称,普通叫做commucation session 通信会话traffic 通信业务(量)synchronous transmission 同步传输concurrent 同时发生的,共存的simultaneous 同时发生的,同时做的simultaneous 同时发生的,一齐的coaxial 同轴的copper 铜statistical 统计的,统计学的dominate 统治,支配invest in 投资perspective 透视,角度,远景graphics 图示,图解pictorial 图像的coating 涂层,层deduce 推理reasoning strategies 推理策略inference engine 推理机topology 拓扑结构heterodyne 外差法的peripheral 外界的,外部的,周围的gateway 网关hazardous 危险的microwave 微波(的)microprocessor 微处理机,微处理器microelectronic 微电子nuance 微小的差别(色彩等)encompass 围绕,包围,造成,设法做到maintenance 维护;保持;维修satellite communication 卫星通信satellite network 卫星网络transceiver 无线电收发信机radio-relay transmission 无线电中继传输without any doubt 无疑passive satellite 无源卫星sparse 稀少的,稀疏的downlink 下行链路precursor 先驱,前任visualization 显像feasibility 现实性,可行性linearity 线性度constrain 限制,约束,制约considerable 相当的,重要的geo-stationary 相对地面静止by contrast 相反,而,对比起来coorelation 相关性mutual 相互的mutually 相互的,共同的interconnect 相互连接,互连one after the other 相继,依次minicomputer 小型计算机protocol 协议,草案protocol 协议,规约,规程psycho-acoustic 心理(精神)听觉的;传音的channelization 信道化,通信信道选择run length encoding 行程编码groom 修饰,准备virtual ISDN 虚拟ISDNmultitude 许多,大批,大量whirl 旋转preference 选择,喜欢avalanche 雪崩pursue 寻求,从事interrogation 询问dumb 哑的,不说话的,无声的subcategory 亚类,子种类,子范畴orbital 眼眶;轨道oxygen 氧气,氧元素更多精品文档service switching and control points(SSCPs) 业务交换控制点service control points(SCPs) 业务控制点service control function(SCF) 业务控制功能in concert 一致,一齐handover 移交,越区切换at a rate of 以……的速率in the form of 以…的形式base on…以…为基础yttrium 钇(稀有金属,符号Y)asynchronous transmission 异步传输asynchronous 异步的exceptional 异常的,特殊的voice-grade 音频级indium 铟give rise to 引起,使产生cryptic 隐义的,秘密的hard disk 硬盘hard automation 硬自动化by means of 用,依靠equip with 用…装备subscriber 用户telex 用户电报PBX(private branch exchange) 用户小交换机或专用交换机be called upon to 用来…,(被)要求…superiority 优势predominance 优势,显著active satellite 有源卫星in comparison with 与…比较comparable to 与…可比preliminary 预备的,初步的premonition 预感,预兆nucleus 原子核valence 原子价circumference 圆周,周围teleprocessing 远程信息处理,遥控处理perspective 远景,前途constrain 约束,强迫mobile 运动的,流动的,机动的,装在车上的convey 运输,传递,转换impurity 杂质impurity 杂质,混杂物,不洁,不纯regenerative 再生的improve over 在……基础上改善play important role in 在…中起重要作用in close proximity 在附近,在很近underlying 在下的,基础的in this respect 在这方面entail 遭遇,导致presentation 赠与,图像,呈现,演示narrowband 窄(频)带deploy 展开,使用,推广应用megabit 兆比特germanium 锗positive 正电quadrature 正交orthogonal 正交的quadrature amplitude modulation(QAM) 正交幅度调制on the right track 正在轨道上sustain 支撑,撑住,维持,持续outgrowh 支派;长出;副产品dominate 支配,统治knowledge representation 知识表示knowledge engineering 知识工程knowledge base 知识库in diameter 直径helicopter 直升飞机acronym 只取首字母的缩写词as long as 只要,如果tutorial 指导教师的,指导的coin 制造(新字符),杜撰fabrication 制造,装配;捏造事实proton 质子intelligence 智能,智力,信息intelligent network 智能网intermediate 中间的nucleus(pl.nuclei) 中心,核心neutrons 中子terminal 终端,终端设备overlay 重叠,覆盖,涂覆highlight 重要的部分,焦点charge 主管,看管;承载dominant 主要的,控制的,最有力的cylinder 柱面expert system 专家系统private network 专用网络transition 转变,转换,跃迁relay 转播relay 转播,中继repeater 转发器,中继器pursue 追赶,追踪,追求,继续desktop publish 桌面出版ultraviolet 紫外线的,紫外的;紫外线辐射field 字段vendor 自动售货机,厂商naturally 自然的;天生具备的synthesize 综合,合成integrate 综合,使完全ISDN(intergrated services digital network) 综合业务数字网as a whole 总体上bus network 总线形网crossbar 纵横,交叉impedance 阻抗initial 最初的,开始的optimum 最佳条件appear as 作为…出现A Analog 模拟A/D Analog to Digital 模-数转换AAC Advanced Audio Coding 高级音频编码ABB Automatic Black Balance 自动黑平衡ABC American Broadcasting Company 美国广播公司Automatic Bass Compensation 自动低音补偿Automatic Brightness Control 自动亮度控制ABL Automatic Black Level 自动黑电平ABLC Automatic Brightness Limiter Circuit 自动亮度限制电路ABU Asian Broadcasting Union 亚洲广播联盟(亚广联ABS American Bureau of Standard 美国标准局AC Access Conditions 接入条件Audio Center 音频中心ACA Adjacent Channel Attenuation 邻频道衰减ACC Automatic Centering Control 自动中心控制Automatic Chroma Control 自动色度(增益ACK Automatic Chroma Killer 自动消色器ACP Additive Colour Process 加色法ACS Access Control System 接入控制系统Advanced Communication Service 高级通信业务Area Communication System 区域通信系统ADC Analog to Digital Converter 模-数转换器Automatic Degaussirng Circuit 自动消磁电路ADL Acoustic Delay Line 声延迟线ADS Audio Distribution System 音频分配系统AE Audio Erasing 音频(声音AEF Automatic Editing Function 自动编辑功能AES Audio Engineering Society 音频工程协会AF Audio Frequency 音频AFA Audio Frequency Amplifier 音频放大器AFC Automatic Frequency Coder 音频编码器Automatic Frequency Control 自动频率控制AFT Automatic Fine Tuning 自动微调Automatic Frequency Track 自动频率跟踪Automatic Frequency Trim 自动额率微调AGC Automatic Gain Control 自动增益控制AI Artificial Intelligence 人工智能ALM Audio-Level Meter 音频电平表AM Amplitude Modulation 调幅AMS Automatic Music Sensor 自动音乐传感装置ANC Automatic Noise Canceller 自动噪声消除器ANT ANTenna 天线AO Analog Output 模拟输出APS Automatic Program Search 自动节目搜索APPS Automatic Program Pause System 自动节目暂停系统APSS Automatic Program Search System 自动节目搜索系统AR Audio Response 音频响应ARC Automatic Remote Control 自动遥控ASCII American Standard Code for InformationInterchange 美国信息交换标准AST Automatic Scanning Tracking 自动扫描跟踪ATC Automatic Timing Control 自动定时控制Automatic Tone Correction 自动音频校正ATM Asynchronous Transfer Mode 异步传输模式ATF Automatic Track Finding 自动寻迹ATS Automatic Test System 自动测试系统ATSC Advanced Television Systems Committee(美国高级电视制式委员会)***C Automatic Volume Control 自动音量控制***R Automatic Voltage Regulator 自动稳压器AWB Automatic White Balance 自动白平衡AZC Automatic Zooming Control 自动变焦控制AZS Automatic Zero Setting 自动调零BA Branch Amplifier 分支放大器Buffer Amplifier 缓冲放大器BAC Binary-Analog Conversion 二进制模拟转换BB Black Burst 黑场信号BBC British Broadcasting Corporation 英国广播公司BBI Beijing Broadcasting Institute 北京广播学院BC Binary Code 二进制码Balanced Current 平衡电流Broadcast Control 广播控制BCT Bandwidth Compression Technique 带宽压缩技术BDB Bi-directional Data Bus 双向数据总线BER Basic Encoding Rules 基本编码规则Bit Error Rate 比特误码率BF Burst Flag 色同步旗脉冲BFA Bare Fiber Adapter 裸光纤适配器Brillouin Fiber Amplifier 布里渊光纤放大器BGM Background Music 背景音乐BIOS Basic Input/Output System 基本输入输出系统B-ISDN Broadband-ISDN 宽带综合业务数据网BIU Basic Information Unit 基本信息单元Bus Interface Unit 总线接口单元BM Bi-phase Modulation 双相调制BML Business Management Layer 商务管理层BN Backbone Network 主干网BNT Broadband Network Termination 宽带网络终端设备BO Bus Out 总线输出BPG Basic Pulse Generator 基准脉冲发生器BPS Band Pitch Shift 分频段变调节器BSI British Standard Institute 英国标准学会BSS Broadcast Satellite Service 广播卫星业务更多精品文档BT Block Terminal 分线盒、分组终端British Telecom 英国电信BTA Broadband Terminal Adapter 宽带终端适配器Broadcasting Technology Association (日本BTL Balanced Transformer-Less 桥式推挽放大电路BTS Broadcast Technical Standard 广播技术标准BTU Basic Transmission Unit 基本传输单元BVU Broadcasting Video Unit 广播视频型(一种3/4英寸带录像机记录格式BW BandWidth 带宽BWTV Black and White Television 黑白电视CA Conditional Access 条件接收CAC Conditional Access Control 条件接收控制CAL Continuity Accept Limit 连续性接受极限CAS Conditional Access System 条件接收系统Conditional Access Sub-system 条件接收子系统CATV Cable Television 有线电视,电缆电视Community Antenna Television 共用天线电视C*** Constant Angular Velocity 恒角速度CBC Canadian Broadcasting Corporation 加拿大广播公司CBS Columbia Broadcasting System (美国哥伦比亚广播公司CC Concentric Cable 同轴电缆CCG Chinese Character Generator 中文字幕发生器CCIR International Radio Consultative Committee 国际无线电咨询委员会CCITT International Telegraph and Telephone ConsultativeCommittee 国际电话电报咨询委员会CCR Central Control Room 中心控制室CCTV China Central Television 中国中央电视台Close-Circuit Television 闭路电视CCS Center Central System 中心控制系统CCU Camera Control Unit 摄像机控制器CCW Counter Clock-Wise 反时针方向CD Compact Disc 激光唱片CDA Current Dumping Amplifier 电流放大器CD-E Compact Disc Erasable 可抹式激光唱片CDFM Compact Disc File Manager 光盘文件管理(程序CDPG Compact-Disc Plus Graphic 带有静止图像的CD唱盘CD-ROM Compact Disc-Read Only Memory 只读式紧凑光盘CETV China Educational Television 中国教育电视台CF Color Framing 彩色成帧CGA Color Graphics Adapter 彩色图形(显示卡CI Common Interface 通用接口CGA Color Graphics Adapter 彩色图形(显示卡CI Common Interface 通用接口CIE Chinese Institute of Electronics 中国电子学会CII China Information Infrastructure 中国信息基础设施CIF Common Intermediate Format 通用中间格式CIS Chinese Industrial Standard 中国工业标准CLV Constant Linear Velocity 恒定线速度CM Colour Monitor 彩色监视器CMTS Cable Modem Termination System 线缆调制解调器终端系统CNR Carrier-to-Noise Ratio 载噪比CON Console 操纵台Controller 控制器CPB Corporation of Public Broadcasting (美国公共广播公司CPU Central Processing Unit 中央处理单元CRC Cyclic Redundancy Check 循环冗余校验CRCC CRI Cyclic Redundancy Check Code 循环冗余校验码CROM China Radio International 中国国际广播电台CRT Control Read Only Memory 控制只读存储器CS Cathode-Ray Tube 阴极射线管CSC Communication Satellite 通信卫星CSS Color Sub-carrier 彩色副载波Center Storage Server 中央存储服务器Content Scrambling System 内容加扰系统CSU Channel Service Unit 信道业务单元CT Color Temperature 色温CTC Cassette Tape Controller 盒式磁带控制器Channel Traffic Control 通道通信量控制Counter Timer Circuit 计数器定时器电路Counter Timer Control 计数器定时器控制CTE Cable Termination Equipment 线缆终端设备Customer Terminal Equipment 用户终端设备CTV Color Television 彩色电视CVD China Video Disc 中国数字视盘CW Carrie Wave 载波DAB Digital Audio Broadcasting 数字音频广播DASH Digital Audio Stationary Head 数字音频静止磁头DAT Digital Audio Tape 数字音频磁带DBMS Data Base Management System 数据库管理系统DBS Direct Broadcast Satellite 直播卫星DCC Digital Compact Cassette 数字小型盒带Dynamic Contrast Control 动态对比度控制DCT Digital Component Technology 数字分量技术Discrete Cosine Transform 离散余弦变换DCTV Digital Color Television 数字彩色电视DD Direct Drive 直接驱动DDC Direct Digital Control 直接数字控制DDE Dynamic Data Exchange 动态数据交换DDM Data Display Monitor 数据显示监视器DES Data Elementary Stream 数据基本码流Data Encryption Standard 美国数据加密标准DF Dispersion Flattened 色散平坦光纤DG Differential Gain 微分增益DI Digital Interface 数字接口DITEC Digital Television Camera 数字电视摄像机DL Delay Line 延时线DLD Dynamic Linear Drive 动态线性驱动DM Delta Modulation 增量调制Digital Modulation 数字调制DMB Digital Multimedia Broadcasting 数字多媒体广播DMC Dynamic Motion Control 动态控制DME Digital Multiple Effect 数字多功能特技DMS Digital Mastering System 数字主系统DN Data Network 数据网络DNG Digital News Gathering 数字新闻采集DNR Digital Noise Reducer 数字式降噪器DOB Data Output Bus 数据输出总线DOCSIS Data Over Cable Service InterfaceSpecifications 有线数据传输业务接口规范DOC Drop Out Compensation 失落补偿DOS Disc Operating System 磁盘操作系统DP Differential Phase 微分相位Data Pulse 数据脉冲DPCM Differential Pulse Code Modulation 差值脉冲编码调制DPL Dolby Pro Logic 杜比定向逻辑DSB Digital Satellite Broadcasting 数字卫星广播DSC Digital Studio Control 数字演播室控制DSD Dolby Surround Digital 杜比数字环绕声DSE Digital Special Effect 数字特技DSK Down-Stream Key 下游键DSP Digital Signal Processing 数字信号处理Digital Sound Processor 数字声音处理器DSS Digital Satellite System 数字卫星系统DT Digital Technique 数字技术Digital Television 数字电视Data Terminal 数据终端Data Transmission 数据传输DTB Digital Terrestrial Broadcasting 数字地面广播DTBC Digital Time-Base Corrector 数字时基校正器DTC Digital Television Camera 数字电视摄像机DTS Digital Theater System 数字影院系统Digital Tuning System 数字调谐系统Digital Television Standard 数字电视标准DVB Digital Video Broadcasting 数字视频广播DVC Digital Video Compression 数字视频压缩DVE Digital Video Effect 数字视频特技DVS Desktop Video Studio 桌上视频演播DVTR Digital Video Tape Recorder 数字磁带录像机EA Extension Amplifier 延长放大器EB Electron Beam 电子束EBS Emergency Broadcasting System 紧急广播系统EBU European Broadcasting Union 欧洲广播联盟EC Error Correction 误差校正ECN Emergency Communications Network 应急通信网络ECS European Communication Satellite 欧洲通信卫星EDC Error Detection Code 错误检测码EDE Electronic Data Exchange 电子数据交换EDF Erbium-Doped Fiber 掺饵光纤EDFA Erbium-Doped Fiber Amplifier 掺饵光纤放大器EDL Edit Decision List 编辑点清单EDTV Extended Definition Television 扩展清晰度电视EE Error Excepted 允许误差EFM Eight to Fourteen Modulation 8-14调制EFP Electronic Field Production 电子现场节目制作EH Ethernet Hosts 以太网主机EIN Equivalent Input Noise 等效输入噪声EIS Electronic Information System 电子信息系统EISA Extended Industrial Standard Architecture扩展工业标准总线EL Electro-Luminescent 场致发光EM Error Monitoring 误码监测EN End Node 末端节点ENG Electronic News Gathering 电子新闻采集EOT End of Tape 带尾EP Edit Point 编辑点Error Protocol 错误协议EPG Electronic Program Guides 电子节目指南EPS Emergency Power Supply 应急电源ERP Effective Radiated Power 有效辐射功率ES Elementary Stream 基本码流End System 终端系统ESA European Space Agency 欧洲空间局ETV Education Television 教育电视FA Enhanced Television 增强电视FABM FAS Facial Animation 面部动画FC Fiber Amplifier Booster Module 光纤放大器增强模块Fiber Access System 光纤接入系统Frequency Changer 变频器FCC Fiber Channel 光纤通道FD Film Composer 电影编辑系统Federal Communications Commission 美国联邦通信委员会FDCT Frequency Divider 分频器FDDI FDM Fiber Duct 光纤管道FDP Forward Discrete Cosine Transform 离散余弦正变换FE Fiber Distributed Data Interface 分布式光纤数据接口更多精品文档Frequency-Division Multiplexing 频分复用FF Fiber Distribution Point 光纤分配点FG Front End 前端FH Framing Error 成帧误差FIT Fast Forward 快进FN Frequency Generator 频率发生器FOA Frequency Hopping 跳频FOC Frame-Interline Transfer 帧一行间转移Fiber Node 光纤节点Fiber Optic Amplifier 光纤放大器FOM Fiber Optic Cable 光缆FON Fiber Optic Communications 光纤通信FOS Fiber Optic Coupler 光纤耦合器FOTC Fiber Optic Modem 光纤调制解调器FS Fiber Optic Net 光纤网Factor of Safety 安全系数Fiber Optic Trunk Cable 光缆干线FT Frame Scan 帧扫描FTP Frame Store 帧存储器FTTB Frame Synchro 帧同步机FTTC France Telecom 法国电信Absorber Circuit 吸收电路AC/AC Frequency Converter 交交变频电路AC power control交流电力控制AC Power Controller交流调功电路AC Power Electronic Switch交流电力电子开关Ac Voltage Controller交流调压电路Asynchronous Modulation异步调制Baker Clamping Circuit贝克箝位电路Bi-directional Triode Thyristor双向晶闸管Bipolar Junction Transistor-- BJT双极结型晶体管Boost-Buck Chopper升降压斩波电路Boost Chopper升压斩波电路Boost Converter升压变换器Bridge Reversible Chopper桥式可逆斩波电路Buck Chopper降压斩波电路Buck Converter降压变换器Commutation换流Conduction Angle导通角Constant Voltage Constant Frequency --CVCF 恒压恒频Continuous Conduction--CCM(电流)连续模式Control Circuit 控制电路Cuk Circuit CUK 斩波电路Current Reversible Chopper电流可逆斩波电路Current Source Type Inverter--CSTI 电流(源)型逆变电路Cyclo convertor周波变流器DC-AC-DC Converter直交直电路DC Chopping直流斩波DC Chopping Circuit直流斩波电路DC-DC Converter直流-直流变换器Device Commutation器件换流Direct Current Control直接电流控制Discontinuous Conduction mode (电流)断续模式displacement factor 位移因数distortion power 畸变功率double end converter 双端电路driving circuit 驱动电路electrical isolation 电气隔离fast acting fuse 快速熔断器fast recovery diode快恢复二极管fast revcovery epitaxial diodes 快恢复外延二极管fast switching thyristor快速晶闸管field controlled thyristor场控晶闸管flyback converter 反激电流forced commutation 强迫换流forward converter 正激电路frequency converter 变频器full bridge converter全桥电路full bridge rectifier 全桥整流电路full wave rectifier 全波整流电路fundamental factor基波因数gate turn-off thyristor——GTO 可关断晶闸管general purpose diode 普通二极管giant transistor——GTR 电力晶体管half bridge converter 半桥电路hard switching 硬开关high voltage IC 高压集成电路hysteresis comparison 带环比较方式indirect current control间接电流控制indirect DC-DC converter直接电流变换电路insulated-gate bipolar transistor---IGBT绝缘栅双极晶体管intelligent power module---IPM智能功率模块integrated gate-commutated thyristor---IGCT 集成门极换流晶闸管inversion 逆变latching effect 擎住效应leakage inductance 漏感light triggered thyristor---LTT光控晶闸管line commutation 电网换流load commutation 负载换流loop current 环流1 backplane 背板2 Band gap voltage reference 带隙电压参考3 bench top supply 工作台电源4 Block Diagram 方块图5 Bode Plot 波特图6 Bootstrap 自举7 Bottom FET Bottom FET8 bucket capacitor 桶形电容9 chassis 机架11 constant current source 恒流源12 Core Saturation 铁芯饱和13 crossover frequency 交叉频率14 current ripple 纹波电流15 Cycle by Cycle 逐周期16 cycle skipping 周期跳步17 Dead Time 死区时间18 DIE Temperature 核心温度19 Disable 非使能,无效,禁用,关断20 dominant pole 主极点21 Enable 使能,有效,启用22 ESD Rating ESD额定值23 Evaluation Board 评估板24 Exceeding the specifications below may result inpermanent damage to the device, or devicemalfunction. Operation outside of the parametersspecified in the Electrical Characteristics section is notimplied. 超过下面的规格使用可能引起永久的设备损害或设备故障。

集成电路专业英语

集成电路专业英语一、单词1. Integrated Circuit (IC)- 英语释义:A set of electronic circuits on one small flat piece (chip) of semiconductor material, typically silicon.- 用法:常作为名词短语使用,可在句中作主语、宾语等。

例如:The development of integrated circuits has revolutionized the electronics industry.(集成电路的发展使电子工业发生了革命性的变化。

)2. Semiconductor- 英语释义:A material which has a conductivity between that of an insulator and that of most metals, either due to the addition of an impurity or because of temperature effects.- 用法:作名词,例如:Silicon is a widely used semiconductor in integrated circuit manufacturing.(硅是集成电路制造中广泛使用的半导体。

)3. Transistor- 英语释义:A semiconductor device used to amplify or switch electronic signals and electrical power.- 用法:作名词,如:The transistor is a keyponent in integrated circuits.(晶体管是集成电路中的一个关键元件。

)4. Chip- 英语释义:A small piece of semiconducting material (usually silicon) on which an integrated circuit is fabricated.- 用法:作名词,可指集成电路芯片。

电子专业英语词汇

A.缩略词Modem:modulator and demodulator 调制解调器Rom :read only memory 只读存储器Ram:random access memory 随机存储器CAD-computer aided design 计算机辅助设计CAE-Computer Aided Engineering 计算机辅助工程CAM-Computer Aided Manufacturing 计算机辅助制造CPU- central processing unit 中央处理器PC- Personal Computer 个人计算机Program Counter 程序计数器IC- Integrated Circuit 集成电路MSI- medium-scale integration 中规模集成(电路)LSI- Large Scale Integrated circuit 大规模集成电路VLSI- Very Large Scale Integration 超大规模集成电路ULSI- Ultra Large Scale Integration 特大规模集成电路ASIC--Application-Specific Integrated Circuit 专用集成电路CEO- Chief Executive Officer 首席执行官CFO- Finance 首席财务官COO- Operate 首席运营官CIO- Information 首席信息官CTO- Technology 首席技术官PCB- Printed Circuit Board 印刷电路板MCS-Micro Computer System 微型计算机系统MCU- Micro Control Unit 微控制器MPU- Micro Processing Unit 微处理器SOC-System On a Chip 片上系统CRT- Cathode Ray Tube 阴极射线管LED- light-emitting diode 发光二级管LCD- Liquid Crystal Display 液晶显示屏IEEE-The Institute of Electrical and Electronics Engineers 电气和电子工程师学会[美]ISA Industry Standard Architecture 工业标准结构PCI Peripheral Component Interconnection 外设部件互连AGP Accelerated Graphics Port 加速图形端口Lab-Laboratory 实验室Maths- mathematics 数学ASIC Application Specific Integrated Circuit 特定用途集成电路FPGA Field Programmable Gate Array 现场可编程门阵列PLC Programmable Logic Controller 可编程逻辑控制器;Power Loading Control 动力负载控制;Power-Line Carrier 电力线载波;FET Field Effect Transistor 场效应晶体管MOSFET metallic oxide semiconductor field effect transistor[电子]金属氧化物半导体场效应晶体管RISC Reduced Instruction Set Computer,精简指令集计算机USB Universal Serial Bus , (Intel 公司开发的)通用串行总线(架构)EEPROM-Electrically Erasable, Programmable Read-Only Memory. B、单词Amplifier 放大器flip-flop触发器resistor电阻器resistance电阻capacitor电容器capacitance电容inductor电感器inductance电感operational amplifier运算放大器sensor传感器transducer 传感器,变换器register寄存器conductor导体semiconductor半导体feedback反馈diode二极管transistor 晶体管,三极管thermo-表示“热、热电”之义thermometer温度计thermocouple热电偶microcomputer 微型计算机monitor(监视器)1) direct current circuits 直流电路2) amplifier放大器3) analog electronics 模电4) semiconductor diode 半导体二极管5) transistor effect 晶体管效应6) microprocessor或microcontroller 微处理器或微控制器7) electrical engineering 电气工程8) power engineering 电力工程9) telecommunications engineering 通信工程10) internal devices 内部器件1)assembler language 汇编语言2)alternating current circuits交流电路3)passive electrical circuits无源电路4)three phase circuits三相电路5)digital electronics数字电子技术6)logic gates 逻辑门7)3D virtual reality image 三维虚拟图像8)computer programming计算机编程10)advanced programming techniques高级编程技术1)electrical components电子元件2)Ohm law欧姆定律3)limit current限制电流4)voltage divider分压器5)transistor biasing circuits晶体管偏置电路6)block DC current阻碍直流7)store electric energy 或store electrical energy储存电能8)inductive reactance感抗9)dielectric insulating material 或insulating material绝缘材料10)AC resistance/或AC impedance 交流阻抗1) known as capacitive reactance 称为容抗2) with units of ohms单位是欧姆3) prevent device from burning out防止器件烧掉4) has an AC resistance to AC current对交流电流有阻抗5) adjustment with a screw用一个螺丝调节6) in the shape of a cylinder呈圆柱形式7) block DC current, but pass AC current阻直流,但通交流8) to vary the inductance改变电感9) be given by the formula.由公式给出10) the RF amplifie音频放大器1) general-purpose meter通用仪表2) analog meter数字仪表3) reverse the test leads交换测试笔4) mechanical adjust机械调节5) measure resistance测量电阻6) positive voltage正向电压7) measure current测量电流8) voltage amplitude电压幅度9) dual-trace oscilloscope双踪示波器10) signal generator信号发生器1)analog multimeter模拟万用表2)extended range扩展范围3)specific meters特殊仪表4) include the function and range switches具有功能及范围选择旋钮5) present an electronic picture呈现一幅电子图像6) display the voltage waveform显示电压波形7) appear on the screen在屏幕上出现8) phase relationship相位关系9) as an example例如,作为一个例子10) in series with the circuit串联接入电路1) PN junction PN结2) anode阳极(正极)3) external resistance外阻4) bipolar transistor三极管5) a small current controls a large current一个小电流控制一个大电流7) enhancement MOS transistors增强型MOS管8) P-channelP沟道9) integrated circuits集成电路10) electron and hole电子和空穴1) semiconductor material半导体材料2) forward biased正向偏置3) depend on the external circuit resistance取决于外部电路的电阻4) excessive reverse-biased voltage过高的反偏电压5) is directly proportional to the amount of base current.是正比于基极电流6) may even appear almost as a short几乎可看成是短路7) cause stability problems for a transistor circuit.引起晶体管电路的稳定性(不好)问题8) digital technology数字技术9) the most popular technology最普遍的技术,最常用的技术10) use two complementary types of transistors N-channel and P-channel用两种互补型的晶体管-N沟道(MOS管)和P沟道(MOS管)1) electronic power supply 或steady DC V oltage source稳压电源2) bridge rectifier桥式整流器3) pulsating DC 脉冲直流电4) anode of diode二极管的正极5) peak voltage峰值电压6) capacitor filter电容滤波器7) charge and discharge充电和放电8) zener diode稳压管9) IEEE (Institute of Electrical and Electronics Engineers)电气电子工程师学会10) technical professional association专业技术组织1) equipment operation设备的运行2) device that converts AC into DC把交流电转换成直流电的器件(设备)3) the power lines电源线4) depending on the value of DC voltage needed根据(取决于)所需要的直流电压值5) a half-wave rectifier半波整流器6) so as to produce a constant DC output从而产生一个稳定的直流输出7) in the negative side of the capacitor在电容的负极8) flow through the load流过负载9) in the forward-biased condition在加正向偏置(电压)的条件下10) a series ( current-limiting) resistor一个串联(限制电流)电阻1) Kirchhoff’s V oltage Law基尔霍夫电压定律2) voltage sources电压源3) the law of conservation of electric charge电荷守恒定律4) at every instant of time在每一瞬时5) voltages across elements元件两端的电压6) radio transmission无线电传输7) frequency modulation调频信号8) the frequency domain频域9) linear resistor线性电阻10) amplitude modulation wave调幅波形2) under this circumstance在这种情况下3) present the second of Kirchhoff ’s laws给出基尔霍夫第二定律4) introduce the concept of a “loop”引入“回路”的概念5) An alternative statement of KVL KVL的另一种表述法6) voltages algebraically sum电压代数和7) sinusoidal steady-state response正弦稳态响应8) ordinary household voltage日常用电(即民用电和一般工业用电)的电压9) time-invariant circuit时不变电路10) percentage of modulation.调制百分比1) digital integrated circuits数字集成电路2) system design系统设计3) application-specific integrated circuit (ASIC)专用集成电路4) the productivity of chip designers芯片设计能力(生产力)5) sophisticated design tools复杂精致的设计工具6) fast response times快速时间响应7) combinational logic blocks组合逻辑(电路)块8) valid signals有效信号9) input-output delay输入输出延迟10) the highest frequency logic circuits高频逻辑电路1) very large scale integrated(VLSI) circuits1) 超大规模集成电路2) in coarse terms粗略地说3) integrate a greater number of transistors in a single die or integrated circuit (IC)在一个芯片上集成大量晶体管即集成电路4) make well-informed design decisions.作出全面的设计决定5) the ratio of channel width to channel length沟道宽度与沟道长度的比值6) output latch of a combinational block6) 组合块(电路)的输出锁存器7) defined in a high-level language用(计算机)高级语言定义(描述)8) reliability of MOS transistorsMOS管的可靠性9) reduce the power consumption减小消耗功率10) to realize circuit functions实现电路的功能1) decimal system十进制数字系统2) storage of information within the computer在计算机中信息的储存3) printed or displayed打印或显示4) logic operation逻辑运算5) combination of gates组合逻辑门6) provide an output high only when all inputs are high仅当输入全为高电平时输出为高电平7) above expressing上述表达式8) synchronous device同步器件9) be combined with other gates与其他门电路结合10) the versatility and flexibility of digital integrated circuits数字集成电路的通用性和多功能性1) flip-flop触发器2) asynchronous device异步器件3) at arbitrary time在任意时间4) change state only on arrival of a clock pulse当时钟脉冲信号来到时改变状态6) clear input清除输入(信号)7) play video games玩电视游戏,玩计算机游戏8) surf the web上网(网上冲浪)9) with a common clock pulse transition用同一时钟脉冲(控制)转换10) in its broadest definition用广义的定义1) make up a computer system组成一个计算机系统2) high performance software高性能的软件3) the input/output (or I/O) devices输入输出器件4) CPU instructions reside in memory存储在储存器中的CPU指令5) store data to an output device把数据储存到一个输出设备中6) the control bus 或control signal lines控制信号线7) interrupt lines中断线8) read data from a memory从存储器中读数据9) semiconductor integrated circuits半导体集成电路10) dynamic RAM memory动态随机存储器1) impact system performance影响系统的性能2) be generally associated with external devices通常与外部设备相连接3) read data from an input device从输入设备中读取数据4) connect the various components of a VNA machine与一台冯.诺依曼计算机的各种部件相连接5) data bus数据总线6) 80x86 family microprocessor80X86系列微处理器(芯片)7) to differentiate memory locations and I/O devices区分储存器的不同地址和不同的输入输出器件8) this prompts the question这就提出了一个问题9) worth a brief mention值得简要地提一下10) storage capacity in a single memory chip一个存储芯片的存储容量1) with some similarities to …与……有些类似2) in an academic sense以学术观点来看3) structured language结构化语言4) the distinguishing feature显著特征5) local variables局部变量6) side effect副作用7) readable programs易读的程序8) high-level computer languages计算机高级语言9) assembly language instructions汇编语言指令10) comments describing the statements描述语句的注释1) perform a specific task.执行一个指定的任务2) to creep into a program潜伏(隐藏)在一个程序中3) in various situations在各种情况下4) section off and hide from the rest of the program和程序的其他部分分开并隐藏起来5) provide an alternative to assembly language programming给出汇编语言编程的替代方法6) correspond to one assembly language statement与一条汇编语言对应7) using alphanumeric symbols用字母及数字符号8) make it easier for programmers to write使编程者容易书写(程序)9) two statement with the braces花括号中的两条语句1) still image静止图像2) relate to television与电视有关的3) the most common way of displaying images 最常见的显示图像方式4) CRT or the cathode ray tube阴极射线管,显像管5) pixel像素6) create magnetic fields6) 建立电磁场7) move the beam horizontally水平移动光束8) electron beam电子束9) emit red, green and blue light发射红、绿、蓝光10) electrical signals电信号1) satellite broadcast卫星广播2) the normal intensity signal标准亮度的信号3) be familiar with……对……很熟悉4) cable TV programs有线电视节目5) select the channel选(电视节目)频道1) reassemble the dots into a meaningful image1) 把像点重新拼成一幅有意义的图像2) second amazing feature第二个奇妙的特点3) hit the flat screen撞击平坦的屏幕4) contain three different parts含有三个不同的部分5) the three colors mix together三种颜色混合在一起。

电子信息技术专业英语

electro- 电electromagnetic wave 电磁波, electrodynamic 电动力(学)的

electrode 电极 anode 阳极、正极 cathode 阴极、负极 positive 阳性的、正的、正数 negative阴性的、负的、负数

2. 1 专业词汇 Speciality Vocabularies

Unit 5 Digital Logic Circuit (数字逻辑线路)

Unit 6 Electronic Instrument Introduction--Oscilloscope (电子仪器介绍---示波器)

Unit 7 Computer Basics (计算机基础) Unit 8 Computer Netwroks (计算机网络) Unit 9 A Manual of Setting Up Your PC (PC机安装 手册) Unit 10 Office 2000 Series (Office 2000 系列) Unit 11 Multimedia (多媒体) Unit 12 ISDN (integrated service digital network) (综 合业务数据网)

in the desired sequence 按希望的顺序

1 科技英语的特点 Features

1.1 长句 Long sentences A与B成(正/反)比例

e.g. For direct current and low-frequency (directly) alternating current (up to a few thousand A be (reversely) proportional to B cycles per second) the resistance is reversely proportional to the cross-sectional (inversely ) area of the path the current must travel; that (direct) is , given two conductors of the same A be in (reverse) proportion/ratio to B material and having same length , but (inverse) differing in crossing-sectional area , the one resistance is reversely proportional (reciprocal) with larger area will have the lower to area, that is, resistance. ratio of 3 to 7. 它们之间比率为3比7。 They are in a

Integrated_Circuits(集成电路)电子信息类专业英语、计算机类专业英语文章

集成电路集成电路数字逻辑和电子电路由称为晶体管的电子开关得到它们的(各种)功能。

粗略地说,晶体管好似一种电子控制阀,由此加在阀一端的能量可以使能量在另外两个连接端之间流动。

通过多个晶体管的组合就可以构成数字逻辑模块,如与门和触发电路等。

而晶体管是由半导体构成的。

查阅大学化学书中的元素周期表,你会查到半导体是介于金属与非金属之间的一类元素。

它们之所以被叫做半导体是由于它们表现出来的性质类似于金属和非金属。

可使半导体像金属那样导电,或者像非金属那样绝缘。

通过半导体和少量其它元素的混合可以精确地控制这些不同的电特性,这种混合技术称之为“半导体掺杂”。

半导体通过掺杂可以包含更多的电子(N型)或更少的电子(P型)。

常用的半导体是硅和锗,N型硅半导体掺入磷元素,而P型硅半导体掺入硼元素。

不同掺杂的半导体层形成的三明治状夹层结构可以构成一个晶体管,最常见的两类晶体管是双极型晶体管(BJT)和场效应晶体管(FET),图2.1给出了它们的图示。

图中给出了这些晶体管的硅结构,以及它们用于电路图中的符号。

BJT 是NPN晶体管,因为由N—P—N掺杂硅三层构成。

当小电流注入基极时,可使较大的电流从集电极流向发射极。

图示的FET是N沟道的场效应型晶体管,它由两块被P型基底分离的N型组成。

将电压加在绝缘的栅极上时,可使电流由漏极流向源极。

它被叫做N沟道是因为栅极电压诱导基底上的N通道,使电流能在两个N区域之间流动。

另一个基本的半导体结构是二极管,由N型和P型硅连接而成的结组成。

二极管的作用就像一个单向阀门,由于电流只能从P流向N。

可以构建一些特殊二极管,在加电压时可以发光,这些器件非常合适地被叫做发光二极管或LED。

这种小灯泡数以百万计地被制造出来,有各种各样的应用,从电话机到交通灯。

半导体材料上制作晶体管或二极管所形成的小芯片用塑料封装以防损伤和被外界污染。

在这封装里一些短线连接半导体夹层和从封装内伸出的插脚以便与(使用该晶体管的)电路其余部分连接。

电子信息工程专业英语词汇(精华整理版)

transistor n 晶体管diode n 二极管semiconductor n 半导体resistor n 电阻器capacitor n 电容器alternating adj 交互的amplifier n 扩音器,放大器integrated circuit 集成电路linear time invariant systems 线性时不变系统voltage n 电压,伏特数Condenser=capacitor n 电容器dielectric n 绝缘体;电解质electromagnetic adj 电磁的adj 非传导性的deflection n偏斜;偏转;偏差linear device 线性器件the insulation resistance 绝缘电阻anode n 阳极,正极cathode n 阴极breakdown n 故障;崩溃terminal n 终点站;终端,接线端emitter n 发射器collect v 收集,集聚,集中insulator n 绝缘体,绝热器oscilloscope n 示波镜;示波器gain n 增益,放大倍数forward biased 正向偏置reverse biased 反向偏置P-N junction PN结MOS(metal-oxide semiconductor)金属氧化物半导体enhancement and exhausted 增强型和耗尽型integrated circuits 集成电路analog n 模拟digital adj 数字的,数位的horizontal adj, 水平的,地平线的vertical adj 垂直的,顶点的amplitude n 振幅,广阔,丰富multimeter n 万用表frequency n 频率,周率the cathode-ray tube 阴极射线管dual-trace oscilloscope 双踪示波器signal generating device 信号发生器peak-to-peak output voltage 输出电压峰峰值sine wave 正弦波triangle wave 三角波square wave 方波amplifier 放大器,扩音器oscillator n 振荡器feedback n 反馈,回应phase n 相,阶段,状态filter n 滤波器,过滤器rectifier n整流器;纠正者band-stop filter 带阻滤波器band-pass filter 带通滤波器decimal adj 十进制的,小数的hexadecimal adj/n十六进制的binary adj 二进制的;二元的octal adj 八进制的domain n 域;领域code n代码,密码,编码v编码the Fourier transform 傅里叶变换Fast Fourier Transform 快速傅里叶变换microcontroller n 微处理器;微控制器assembly language instrucions n 汇编语言指令chip n 芯片,碎片modular adj 模块化的;模数的sensor n 传感器plug vt堵,塞,插上n塞子,插头,插销coaxial adj 同轴的,共轴的fiber n 光纤relay contact 继电接触器Artificial Intelligence 人工智能Perceptive Systems 感知系统neural network 神经网络fuzzy logic 模糊逻辑intelligent agent 智能代理electromagnetic adj 电磁的coaxial adj 同轴的,共轴的microwave n 微波charge v充电,使充电insulator n 绝缘体,绝缘物nonconductive adj非导体的,绝缘的simulation n 仿真;模拟prototype n 原型array n 排队,编队vector n 向量,矢量inverse adj倒转的,反转的n反面;相反v倒转high-performance 高精确性,高性能two-dimensional 二维的;缺乏深度的three-dimensional 三维的;立体的;真实的object-oriented programming面向对象的程序设计spectral adj 光谱的distortion n 失真,扭曲,变形wavelength n 波长refractive adj 折射的ivision Multiplexing单工传输simplex transmission半双工传输half-duplex transmission全双工传输full-duplex transmission电路交换circuit switching数字传输技术Digital transmission technology灰度图像Grey scale images灰度级Grey scale level幅度谱Magnitude spectrum相位谱Phase spectrum频谱frequency spectrum相干解调coherent demodulation coherent相干的数字图像压缩digital image compression图像编码image encoding量化quantization人机交互man machine interface交互式会话Conversational interaction路由算法Routing Algorithm目标识别Object recognition话音变换Voice transform中继线trunk line传输时延transmission delay远程监控remote monitoring光链路optical linkhalf-duplex transmission 半双工传输accompaniment 伴随物,附属物reservation 保留,预定quotation 报价单,行情报告,引语memorandum 备忘录redundancy 备用be viewed as 被看作…be regards as 被认为是as such 本身;照此;以这种资格textual 本文的,正文的variation 变化,变量conversion 变化,转化identity 标识;标志criterion 标准,准则in parallel on 并联到,合并到juxtapose 并置,并列dialing pulse 拨号脉冲wave-guide 波导wavelength division multiplexed 波分复用baud rate 波特率playback 播放(录音带,唱片)no greater than 不大于update 不断改进,使…适合新的要求,更新asymmetric 不对称的irrespective 不考虑的,不顾的inevitably 不可避免的inevitable 不可避免的,不可逃避的,必定的segment 部分abrasion 擦伤,磨损deploy 采用,利用,推广应用take the form of 采用…的形式parameter 参数,参量layer 层dope 掺杂FET(field effect transistors) 场效应管audio recording 唱片ultra-high-frequency(UHF) 超高频in excess of 超过in excess of 超过hypertext 超文本ingredient 成分,因素ingredient 成分,组成部分,要素metropolitan-area network(WAN) 城域网metropolitan area network(WAN) 城域网,城市网络congestion 充满,拥挤,阻塞collision 冲突extractive 抽出;释放出extract 抽取,取出,分离lease 出租,租约,租界期限,租界物pass on 传递,切换transmission 传输facsimile 传真innovative=innovatory 创新的,富有革新精神的track 磁道impetus 促进,激励cluster 簇stored-program control(SPC) 存储程序控制a large number of 大量的peal 大声响,发出supersede 代替supplant 代替,取代out-of-band signaling 带外信号simplex transmission 单工传输monochromatic 单色的,单色光的,黑白的ballistic 弹道的,射击的,冲击的conductor 导体hierarchy 等级制度,层次infrastructure 底层结构,基础结构geographic 地理的,地区的geographically 地理上GIS(ground instrumentation system) 地面测量系统ground station 地面站earth orbit 地球轨道extraterrestrial 地球外的,地球大气圈外的Land-sat 地球资源卫星rug 地毯,毯子ignite 点火,点燃,使兴奋electromagnetic 电磁的inductive 电感arc 电弧telephony 电话(学),通话dielectric 电介质,绝缘材料;电解质的,绝缘的capacitor 电容telecommunication 电信,无线电通讯scenario 电影剧本,方案modem pool 调制解调器(存储)池superimposing 叠加,重叠pin 钉住,扣住,抓住customize 定做,定制monolithic 独立的,完全统一的aluminize 镀铝strategic 对全局有重要意义的,战略的substantial 多的,大的,实际上的multi-path fading 多径衰落multi-path 多路,多途径;多路的,多途径的multi-access 多路存取,多路进入multiplex 多路复用multiplex 多路复用的degradation 恶化,降级dioxide 二氧化碳LED(light-emitting-diode) 发光二极管evolution 发展,展开,渐进feedback 反馈,回授dimension 范围,方向,维,元scenario 方案scenario 方案,电影剧本amplifer 放大器noninvasive 非侵略的,非侵害的tariff 费率,关税率;对…征税distributed functional plane(DFP) 分布功能平面DQDB(distributed queue dual bus) 分布式队列双总线hierarchy 分层,层次partition 分成segmentation 分割interface 分界面,接口asunder 分开地,分离地detached 分离的,分开的,孤立的dispense 分配allocate 分配,配给;配给物centigrade 分为百度的,百分度的,摄氏温度的fractal 分形molecule 分子,微小,些微cellular 蜂窝状的cellular 蜂窝状的,格形的,多孔的auxiliary storage(also called secondary storage)辅助存储器decay 腐烂,衰减,衰退negative 负电vicinity 附近,邻近vicinity 附近地区,近处sophisticated 复杂的,高级的,现代化的high-frequency(HF) 高频high definition television 高清晰度电视chromium 铬annotate 给…作注解in terms of 根据,按照disclosure 公布,企业决算公开public network 公用网functionality 功能,功能度mercury 汞resonator 共鸣器resonance 共振whimsical 古怪的,反复无常的administration 管理,经营cursor 光标(显示器),游标,指针optical computer 光计算机photoconductor 光敏电阻optical disks 光盘optically 光学地,光地wide-area networks 广域网specification 规范,说明书silicon 硅the international telecommunication union(ITU)国际电信联盟excess 过剩obsolete 过时的,废弃的maritime 海事的synthetic 合成的,人造的,综合的synthetic 合成的,综合性的rational 合乎理性的rationalization 合理化streamline 合理化,理顺infrared 红外线的,红外线skepticism 怀疑论ring network 环形网hybrid 混合物counterpart 伙伴,副本,对应物electromechanical 机电的,电动机械的Robot 机器人Robotics 机器人技术,机器人学accumulation 积累infrastructure 基础,基础结构substrate 基质,底质upheaval 激变,剧变compact disc 激光磁盘(CD)concentrator 集中器,集线器centrex system 集中式用户交换功能系统converge on 集中于,聚集在…上lumped element 集总元件CAI(computer-aided instruction) 计算机辅助教学computer-integrated manufacturing(CIM) 计算机集成制造computer mediated communication(CMC) 计算机中介通信record 记录register 记录器,寄存器expedite 加快,促进weight 加权accelerate 加速,加快,促进categorize 加以类别,分类in addition 加之,又,另外hypothetical 假设的rigidly 坚硬的,僵硬的compatibility 兼容性,相容性surveillance 监视surveillance 监视retrieval 检索,(可)补救verification 检验simplicity 简单,简明film 胶片,薄膜take over 接管,接任ruggedness 结实threshold 界限,临界值with the aid of 借助于,用,通过wire line 金属线路,有线线路coherent 紧凑的,表达清楚的,粘附的,相干的compact 紧密的approximation 近似undertake 进行,从事transistor 晶体管elaborate 精心制作的,细心完成的,周密安排的vigilant 警戒的,警惕的alcohol 酒精,酒local area networks(LANs) 局域网local-area networks(LANs) 局域网drama 剧本,戏剧,戏剧的演出focus on 聚集在,集中于,注视insulator 绝缘root mean square 均方根uniform 均匀的open-system-interconnection(OSI) 开放系统互连expire 开始无效,满期,终止immunity 抗扰,免除,免疫性take…into account 考虑,重视…programmable industrial automation 可编程工业自动化demountable 可拆卸的tunable 可调的reliable 可靠be likely to 可能,大约,像要videotex video 可视图文电视negligible 可以忽略的aerial 空气的,空中的,无形的,虚幻的;天线broadband 宽(频)带pervasive 扩大的,渗透的tensile 拉力的,张力的romanticism 浪漫精神,浪漫主义discrete 离散,不连续ion 离子force 力量;力stereophonic 立体声的continuum 连续统一体,连续统,闭联集smart 灵巧的;精明的;洒脱的token 令牌on the other hand 另一方面hexagonal 六边形的,六角形的hexagon 六角形,六边形monopoly 垄断,专利video-clip 录像剪辑aluminum 铝pebble 卵石,水晶透镜forum 论坛,讨论会logical relationships 逻辑关系code book 码本pulse code modulation(PCM) 脉冲编码调制roam 漫步,漫游bps(bits per second) 每秒钟传输的比特ZIP codes 美国邮区划分的五位编码susceptible(to) 敏感的,易受…的analog 模拟,模拟量pattern recognition模式识别bibliographic 目录的,文献的neodymium 钕the european telecommunicationstandardization institute(ETSI) 欧洲电信标准局coordinate 配合的,协调的;使配合,调整ratify 批准,认可bias 偏差;偏置deviate 偏离,与…不同spectrum 频谱come into play 其作用entrepreneurial 企业的heuristic methods 启发式方法play a …role(part) 起…作用stem from 起源于;由…发生organic 器官的,有机的,组织的hypothesis 前提front-end 前置,前级potential 潜势的,潜力的intensity 强度coincidence 巧合,吻合,一致scalpel 轻便小刀,解剖刀inventory 清单,报表spherical 球的,球形的distinguish 区别,辨别succumb 屈服,屈从,死global functional plane(GFP) 全局功能平面full-duplex transmission 全双工传输hologram 全息照相,全息图deficiency 缺乏thermonuclear 热核的artifact 人工制品AI(artificial intelligence) 人工智能fusion 熔解,熔化diskettes(also called floppy disk) 软盘sector 扇区entropy 熵uplink 上行链路arsenic 砷neural network 神经网络very-high-frequency(VHF) 甚高频upgrade 升级distortion 失真,畸变identification 识别,鉴定,验明pragmatic 实际的implementation 实施,实现,执行,敷设entity 实体,存在vector quantification 矢量量化mislead 使…误解,给…错误印象,引错vex 使烦恼,使恼火defy 使落空facilitate 使容易,促进retina 视网膜compatible 适合的,兼容的transceiver 收发两用机authorize 授权,委托,允许data security 数据安全性data independence 数据独立data management 数据管理database 数据库database management system(DBMS) 数据库管理信息系统database transaction 数据库事务data integrity 数据完整性,数据一致性attenuation 衰减fading 衰落,衰减,消失dual 双的,二重的transient 瞬时的deterministic 宿命的,确定的algorithm 算法dissipation 损耗carbon 碳diabetes 糖尿病cumbersome 讨厌的,麻烦的,笨重的razor 剃刀,剃go by the name of 通称,普通叫做commucation session 通信会话traffic 通信业务(量)synchronous transmission 同步传输concurrent 同时发生的,共存的simultaneous 同时发生的,同时做的simultaneous 同时发生的,一齐的coaxial 同轴的copper 铜statistical 统计的,统计学的dominate 统治,支配invest in 投资perspective 透视,角度,远景graphics 图示,图解pictorial 图像的coating 涂层,层deduce 推理reasoning strategies 推理策略inference engine 推理机topology 拓扑结构heterodyne 外差法的peripheral 外界的,外部的,周围的gateway 网关hazardous 危险的microwave 微波(的)microprocessor 微处理机,微处理器microelectronic 微电子nuance 微小的差别(色彩等)encompass 围绕,包围,造成,设法做到maintenance 维护;保持;维修satellite communication 卫星通信satellite network 卫星网络transceiver 无线电收发信机radio-relay transmission 无线电中继传输without any doubt 无疑passive satellite 无源卫星sparse 稀少的,稀疏的downlink 下行链路precursor 先驱,前任visualization 显像feasibility 现实性,可行性linearity 线性度constrain 限制,约束,制约considerable 相当的,重要的geo-stationary 相对地面静止by contrast 相反,而,对比起来coorelation 相关性mutual 相互的mutually 相互的,共同的interconnect 相互连接,互连one after the other 相继,依次minicomputer 小型计算机protocol 协议,草案protocol 协议,规约,规程psycho-acoustic 心理(精神)听觉的;传音的channelization 信道化,通信信道选择run length encoding 行程编码groom 修饰,准备virtual ISDN 虚拟ISDNmultitude 许多,大批,大量whirl 旋转preference 选择,喜欢avalanche 雪崩pursue 寻求,从事interrogation 询问dumb 哑的,不说话的,无声的subcategory 亚类,子种类,子范畴orbital 眼眶;轨道oxygen 氧气,氧元素service switching and control points(SSCPs) 业务交换控制点service control points(SCPs) 业务控制点service control function(SCF) 业务控制功能in concert 一致,一齐handover 移交,越区切换at a rate of 以……的速率in the form of 以…的形式base on…以…为基础yttrium 钇(稀有金属,符号Y)asynchronous transmission 异步传输asynchronous 异步的exceptional 异常的,特殊的voice-grade 音频级indium 铟give rise to 引起,使产生cryptic 隐义的,秘密的hard disk 硬盘hard automation 硬自动化by means of 用,依靠equip with 用…装备subscriber 用户telex 用户电报PBX(private branch exchange) 用户小交换机或专用交换机be called upon to 用来…,(被)要求…superiority 优势predominance 优势,显著active satellite 有源卫星in comparison with 与…比较comparable to 与…可比preliminary 预备的,初步的premonition 预感,预兆nucleus 原子核valence 原子价circumference 圆周,周围teleprocessing 远程信息处理,遥控处理perspective 远景,前途constrain 约束,强迫mobile 运动的,流动的,机动的,装在车上的convey 运输,传递,转换impurity 杂质impurity 杂质,混杂物,不洁,不纯regenerative 再生的improve over 在……基础上改善play important role in 在…中起重要作用in close proximity 在附近,在很近underlying 在下的,基础的in this respect 在这方面germanium 锗positive 正电quadrature 正交orthogonal 正交的quadrature amplitude modulation(QAM) 正交幅度调制on the right track 正在轨道上sustain 支撑,撑住,维持,持续outgrowh 支派;长出;副产品dominate 支配,统治knowledge representation 知识表示knowledge engineering 知识工程knowledge base 知识库in diameter 直径helicopter 直升飞机acronym 只取首字母的缩写词as long as 只要,如果tutorial 指导教师的,指导的coin 制造(新字符),杜撰fabrication 制造,装配;捏造事实proton 质子intelligence 智能,智力,信息intelligent network 智能网intermediate 中间的nucleus(pl.nuclei) 中心,核心neutrons 中子terminal 终端,终端设备overlay 重叠,覆盖,涂覆highlight 重要的部分,焦点charge 主管,看管;承载dominant 主要的,控制的,最有力的cylinder 柱面expert system 专家系统private network 专用网络transition 转变,转换,跃迁relay 转播relay 转播,中继repeater 转发器,中继器pursue 追赶,追踪,追求,继续desktop publish 桌面出版ultraviolet 紫外线的,紫外的;紫外线辐射field 字段vendor 自动售货机,厂商naturally 自然的;天生具备的synthesize 综合,合成integrate 综合,使完全ISDN(intergrated services digital network) 综合业务数字网as a whole 总体上bus network 总线形网crossbar 纵横,交叉impedance 阻抗initial 最初的,开始的optimum 最佳条件appear as 作为…出现A Analog 模拟A/D Analog to Digital 模-数转换AAC Advanced Audio Coding 高级音频编码ABB Automatic Black Balance 自动黑平衡ABC American Broadcasting Company 美国广播公司Automatic Bass Compensation 自动低音补偿Automatic Brightness Control 自动亮度控制ABL Automatic Black Level 自动黑电平ABLC Automatic Brightness LimiterCircuit 自动亮度限制电路ABU Asian Broadcasting Union 亚洲广播联盟(亚广联ABS American Bureau of Standard 美国标准局AC Access Conditions 接入条件Audio Center 音频中心ACA Adjacent Channel Attenuation 邻频道衰减ACC Automatic Centering Control 自动中心控制Automatic Chroma Control 自动色度(增益ACK Automatic Chroma Killer 自动消色器ACP Additive Colour Process 加色法ACS Access Control System 接入控制系统Advanced Communication Service 高级通信业务Area Communication System 区域通信系统ADC Analog to Digital Converter 模-数转换器Automatic Degaussirng Circuit 自动消磁电路ADL Acoustic Delay Line 声延迟线ADS Audio Distribution System 音频分配系统AE Audio Erasing 音频(声音AEF Automatic Editing Function 自动编辑功能AES Audio Engineering Society 音频工程协会AF Audio Frequency 音频AFA Audio Frequency Amplifier 音频放大器AFC Automatic Frequency Coder 音频编码器Automatic Frequency Control 自动频率控制AFT Automatic Fine Tuning 自动微调Automatic Frequency Track 自动频率跟踪Automatic Frequency Trim 自动额率微调AGC Automatic Gain Control 自动增益控制AI Artificial Intelligence 人工智能ALM Audio-Level Meter 音频电平表AM Amplitude Modulation 调幅AMS Automatic Music Sensor 自动音乐传感装置ANC Automatic Noise Canceller 自动噪声消除器ANT ANTenna 天线AO Analog Output 模拟输出APS Automatic Program Search 自动节目搜索APPS Automatic Program Pause System 自动节目暂停系统APSS Automatic Program Search System 自动节目搜索系统AR Audio Response 音频响应ARC Automatic Remote Control 自动遥控ASCII American Standard Code for Information Interchange 美国信息交换标准AST Automatic Scanning Tracking 自动扫描跟踪ATC Automatic Timing Control 自动定时控制Automatic Tone Correction 自动音频校正ATM Asynchronous Transfer Mode 异步传输模式ATF Automatic Track Finding 自动寻迹ATS Automatic Test System 自动测试系统ATSC Advanced Television Systems Committee (美国高级电视制式委员会)***C Automatic Volume Control 自动音量控制***R Automatic Voltage Regulator 自动稳压器AWB Automatic White Balance 自动白平衡AZC Automatic Zooming Control 自动变焦控制AZS Automatic Zero Setting 自动调零BA Branch Amplifier 分支放大器Buffer Amplifier 缓冲放大器BAC Binary-Analog Conversion 二进制模拟转换BB Black Burst 黑场信号BBC British Broadcasting Corporation 英国广播公司BBI Beijing Broadcasting Institute 北京广播学院BC Binary Code 二进制码Balanced Current 平衡电流Broadcast Control 广播控制BCT Bandwidth Compression Technique带宽压缩技术BDB Bi-directional Data Bus 双向数据总线BER Basic Encoding Rules 基本编码规则Bit Error Rate 比特误码率BF Burst Flag 色同步旗脉冲BFA Bare Fiber Adapter 裸光纤适配器Brillouin Fiber Amplifier 布里渊光纤放大器BGM Background Music 背景音乐BIOS Basic Input/Output System 基本输入输出系统B-ISDN Broadband-ISDN 宽带综合业务数据网BIU Basic Information Unit 基本信息单元Bus Interface Unit 总线接口单元BM Bi-phase Modulation 双相调制BML Business Management Layer 商务管理层BN Backbone Network 主干网BNT Broadband Network Termination 宽带网络终端设备BO Bus Out 总线输出BPG Basic Pulse Generator 基准脉冲发生器BPS Band Pitch Shift 分频段变调节器BSI British Standard Institute 英国标准学会BSS Broadcast Satellite Service 广播卫星业务BT Block Terminal 分线盒、分组终端British Telecom 英国电信BTA Broadband Terminal Adapter 宽带终端适配器Broadcasting Technology Association (日本BTL Balanced Transformer-Less 桥式推挽放大电路BTS Broadcast Technical Standard 广播技术标准BTU Basic Transmission Unit 基本传输单元BVU Broadcasting Video Unit 广播视频型(一种3/4英寸带录像机记录格式BW BandWidth 带宽BWTV Black and White Television 黑白电视CA Conditional Access 条件接收CAC Conditional Access Control 条件接收控制CAL Continuity Accept Limit 连续性接受极限CAS Conditional Access System 条件接收系统Conditional Access Sub-system 条件接收子系统CATV Cable Television 有线电视,电缆电视Community Antenna Television 共用天线电视C*** Constant Angular Velocity 恒角速度CBC Canadian Broadcasting Corporation加拿大广播公司CBS Columbia Broadcasting System (美国哥伦比亚广播公司CC Concentric Cable 同轴电缆CCG Chinese Character Generator 中文字幕发生器CCIR International Radio ConsultativeCommittee 国际无线电咨询委员会CCITT International Telegraph andTelephone ConsultativeCommittee 国际电话电报咨询委员会CCR Central Control Room 中心控制室CCTV China Central Television 中国中央电视台Close-Circuit Television 闭路电视CCS Center Central System 中心控制系统CCU Camera Control Unit 摄像机控制器CCW Counter Clock-Wise 反时针方向CD Compact Disc 激光唱片CDA Current Dumping Amplifier 电流放大器CD-E Compact Disc Erasable 可抹式激光唱片CDFM Compact Disc File Manager 光盘文件管理(程序CDPG Compact-Disc Plus Graphic 带有静止图像的CD唱盘CD-ROM Compact Disc-Read OnlyMemory 只读式紧凑光盘CETV China Educational Television 中国教育电视台CF Color Framing 彩色成帧CGA Color Graphics Adapter 彩色图形(显示卡CI Common Interface 通用接口CGA Color Graphics Adapter 彩色图形(显示卡CI Common Interface 通用接口CIE Chinese Institute of Electronics 中国电子学会CII China Information Infrastructure 中国信息基础设施CIF Common Intermediate Format 通用中间格式CIS Chinese Industrial Standard 中国工业标准CLV Constant Linear Velocity 恒定线速度CM Colour Monitor 彩色监视器CMTS Cable Modem Termination System线缆调制解调器终端系统CNR Carrier-to-Noise Ratio 载噪比CON Console 操纵台Controller 控制器CPB Corporation of Public Broadcasting(美国公共广播公司CPU Central Processing Unit 中央处理单元CRC Cyclic Redundancy Check 循环冗余校验CRCC CRI Cyclic Redundancy Check Code循环冗余校验码CROM China Radio International 中国国际广播电台CRT Control Read Only Memory 控制只读存储器CS Cathode-Ray Tube 阴极射线管CSC Communication Satellite 通信卫星CSS Color Sub-carrier 彩色副载波Center Storage Server 中央存储服务器Content Scrambling System 内容加扰系统CSU Channel Service Unit 信道业务单元CT Color Temperature 色温CTC Cassette Tape Controller 盒式磁带控制器Channel Traffic Control 通道通信量控制Counter Timer Circuit 计数器定时器电路Counter Timer Control 计数器定时器控制CTE Cable Termination Equipment 线缆终端设备Customer Terminal Equipment 用户终端设备CTV Color Television 彩色电视CVD China Video Disc 中国数字视盘CW Carrie Wave 载波DAB Digital Audio Broadcasting 数字音频广播DASH Digital Audio Stationary Head 数字音频静止磁头DAT Digital Audio Tape 数字音频磁带DBMS Data Base Management System 数据库管理系统DBS Direct Broadcast Satellite 直播卫星DCC Digital Compact Cassette 数字小型盒带Dynamic Contrast Control 动态对比度控制DCT Digital Component Technology 数字分量技术Discrete Cosine Transform 离散余弦变换DCTV Digital Color Television 数字彩色电视DD Direct Drive 直接驱动DDC Direct Digital Control 直接数字控制DDE Dynamic Data Exchange 动态数据交换DDM Data Display Monitor 数据显示监视器DES Data Elementary Stream 数据基本码流Data Encryption Standard 美国数据加密标准DF Dispersion Flattened 色散平坦光纤DG Differential Gain 微分增益DI Digital Interface 数字接口DITEC Digital Television Camera 数字电视摄像机DL Delay Line 延时线DLD Dynamic Linear Drive 动态线性驱动DM Delta Modulation 增量调制Digital Modulation 数字调制DMB Digital Multimedia Broadcasting 数字多媒体广播DMC Dynamic Motion Control 动态控制DME Digital Multiple Effect 数字多功能特技DMS Digital Mastering System 数字主系统DN Data Network 数据网络DNG Digital News Gathering 数字新闻采集DNR Digital Noise Reducer 数字式降噪器DOB Data Output Bus 数据输出总线DOCSIS Data Over Cable Service Interface Specifications 有线数据传输业务接口规范DOC Drop Out Compensation 失落补偿DOS Disc Operating System 磁盘操作系统DP Differential Phase 微分相位Data Pulse 数据脉冲DPCM Differential Pulse Code Modulation 差值脉冲编码调制DPL Dolby Pro Logic 杜比定向逻辑DSB Digital Satellite Broadcasting 数字卫星广播DSC Digital Studio Control 数字演播室控制DSD Dolby Surround Digital 杜比数字环绕声DSE Digital Special Effect 数字特技DSK Down-Stream Key 下游键DSP Digital Signal Processing 数字信号处理Digital Sound Processor 数字声音处理器DSS Digital Satellite System 数字卫星系统DT Digital Technique 数字技术Digital Television 数字电视Data Terminal 数据终端Data Transmission 数据传输DTB Digital Terrestrial Broadcasting 数字地面广播DTBC Digital Time-Base Corrector 数字时基校正器DTC Digital Television Camera 数字电视摄像机DTS Digital Theater System 数字影院系统Digital Tuning System 数字调谐系统Digital Television Standard 数字电视标准DVB Digital Video Broadcasting 数字视频广播DVC Digital Video Compression 数字视频压缩DVE Digital Video Effect 数字视频特技DVS Desktop Video Studio 桌上视频演播DVTR Digital Video Tape Recorder 数字磁带录像机EA Extension Amplifier 延长放大器EB Electron Beam 电子束EBS Emergency Broadcasting System 紧急广播系统EBU European Broadcasting Union 欧洲广播联盟EC Error Correction 误差校正ECN Emergency Communications Network应急通信网络ECS European Communication Satellite 欧洲通信卫星EDC Error Detection Code 错误检测码EDE Electronic Data Exchange 电子数据交换EDF Erbium-Doped Fiber 掺饵光纤EDFA Erbium-Doped Fiber Amplifier 掺饵光纤放大器EDL Edit Decision List 编辑点清单EDTV Extended Definition Television 扩展清晰度电视EE Error Excepted 允许误差EFM Eight to Fourteen Modulation 8-14调制EFP Electronic Field Production 电子现场节目制作EH Ethernet Hosts 以太网主机EIN Equivalent Input Noise 等效输入噪声EIS Electronic Information System 电子信息系统EISA Extended Industrial StandardArchitecture 扩展工业标准总线EL Electro-Luminescent 场致发光EM Error Monitoring 误码监测EN End Node 末端节点ENG Electronic News Gathering 电子新闻采集EOT End of Tape 带尾EP Edit Point 编辑点Error Protocol 错误协议EPG Electronic Program Guides 电子节目指南EPS Emergency Power Supply 应急电源ERP Effective Radiated Power 有效辐射功率ES Elementary Stream 基本码流End System 终端系统ESA European Space Agency 欧洲空间局ETV Education Television 教育电视FA Enhanced Television 增强电视FABM FAS Facial Animation 面部动画FC Fiber Amplifier Booster Module 光纤放大器增强模块Fiber Access System 光纤接入系统Frequency Changer 变频器FCC Fiber Channel 光纤通道FD Film Composer 电影编辑系统Federal Communications Commission 美国联邦通信委员会FDCT Frequency Divider 分频器FDDI FDM Fiber Duct 光纤管道FDP Forward Discrete Cosine Transform离散余弦正变换FE Fiber Distributed Data Interface 分布式光纤数据接口Frequency-Division Multiplexing 频分复用FF Fiber Distribution Point 光纤分配点FG Front End 前端FH Framing Error 成帧误差FIT Fast Forward 快进FN Frequency Generator 频率发生器FOA Frequency Hopping 跳频FOC Frame-Interline Transfer 帧一行间转移Fiber Node 光纤节点Fiber Optic Amplifier 光纤放大器FOM Fiber Optic Cable 光缆FON Fiber Optic Communications 光纤通信FOS Fiber Optic Coupler 光纤耦合器FOTC Fiber Optic Modem 光纤调制解调器FS Fiber Optic Net 光纤网Factor of Safety 安全系数Fiber Optic Trunk Cable 光缆干线FT Frame Scan 帧扫描FTP Frame Store 帧存储器FTTB Frame Synchro 帧同步机FTTC France Telecom 法国电信Absorber Circuit 吸收电路AC/AC Frequency Converter 交交变频电路AC power control交流电力控制AC Power Controller交流调功电路AC Power Electronic Switch交流电力电子开关Ac Voltage Controller交流调压电路Asynchronous Modulation异步调制Baker Clamping Circuit贝克箝位电路Bi-directional Triode Thyristor双向晶闸管Bipolar Junction Transistor-- BJT双极结型晶体管Boost-Buck Chopper升降压斩波电路Boost Chopper升压斩波电路Boost Converter升压变换器Bridge Reversible Chopper桥式可逆斩波电路Buck Chopper降压斩波电路Buck Converter降压变换器Commutation换流Conduction Angle导通角Constant Voltage Constant Frequency --CVCF恒压恒频Continuous Conduction--CCM(电流)连续模式Control Circuit 控制电路Cuk Circuit CUK 斩波电路Current Reversible Chopper电流可逆斩波电路Current Source Type Inverter--CSTI 电流(源)型逆变电路Cyclo convertor周波变流器DC-AC-DC Converter直交直电路DC Chopping直流斩波DC Chopping Circuit直流斩波电路DC-DC Converter直流-直流变换器Device Commutation器件换流Direct Current Control直接电流控制Discontinuous Conduction mode (电流)断续模式displacement factor 位移因数distortion power 畸变功率double end converter 双端电路driving circuit 驱动电路electrical isolation 电气隔离fast acting fuse 快速熔断器fast recovery diode快恢复二极管fast revcovery epitaxial diodes 快恢复外延二极管fast switching thyristor快速晶闸管field controlled thyristor场控晶闸管flyback converter 反激电流forced commutation 强迫换流forward converter 正激电路frequency converter 变频器full bridge converter全桥电路full bridge rectifier 全桥整流电路full wave rectifier 全波整流电路fundamental factor基波因数gate turn-off thyristor——GTO 可关断晶闸管general purpose diode 普通二极管giant transistor——GTR 电力晶体管half bridge converter 半桥电路hard switching 硬开关high voltage IC 高压集成电路hysteresis comparison 带环比较方式indirect current control间接电流控制indirect DC-DC converter直接电流变换电路insulated-gate bipolar transistor---IGBT绝缘栅双极晶体管intelligent power module---IPM智能功率模块integrated gate-commutated thyristor---IGCT 集成门极换流晶闸管inversion 逆变latching effect 擎住效应leakage inductance 漏感light triggered thyristor---LTT光控晶闸管line commutation 电网换流load commutation 负载换流loop current 环流1 backplane 背板2 Band gap voltage reference 带隙电压参考3 bench top supply 工作台电源4 Block Diagram 方块图5 Bode Plot 波特图6 Bootstrap 自举7 Bottom FET Bottom FET8 bucket capacitor 桶形电容9 chassis 机架11 constant current source 恒流源12 Core Saturation 铁芯饱和13 crossover frequency 交叉频率14 current ripple 纹波电流15 Cycle by Cycle 逐周期16 cycle skipping 周期跳步17 Dead Time 死区时间18 DIE Temperature 核心温度19 Disable 非使能,无效,禁用,关断20 dominant pole 主极点21 Enable 使能,有效,启用22 ESD Rating ESD额定值23 Evaluation Board 评估板24 Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied. 超过下面的规格使用可能引起永久的设备损害或设备故障。

Integrated_Circuits(集成电路)电子信息类专业英语、计算机类专业英语文章

Integrated Circuits(集成电路)The Integrated CircuitDigital logic and electronic circuits derive their functionality from electronic switches called transistor. Roughly speaking, the transistor can be likened to an electronically controlled valve whereby energy applied to one connection of the valve enables energy to flow between two other connections.By combining multiple transistors, digital logic building blocks such as AND gates and flip-flops are formed. Transistors, in turn, are made from semiconductors. Consult a periodic table of elements in a college chemistry textbook, and you will locate semiconductors as a group of elements separating the metals and nonmetals.They are called semiconductors because of their ability to behave as both metals and nonmetals. A semiconductor can be made to conduct electricity like a metal or to insulate as a nonmetal does. These differing electrical properties can be accurately controlled by mixing the semiconductor with small amounts of other elements. This mixing is called doping. A semiconductor can be doped to contain more electrons (N-type) or fewer electrons (P-type). Examples of commonly used semiconductors are silicon and germanium. Phosphorous and boron are two elements that are used to dope N-type and P-type silicon, respectively.A transistor is constructed by creating a sandwich of differently doped semiconductor layers. The two most common types of transistors, the bipolar-junction transistor (BJT) and the field-effect transistor (FET) are schematically illustrated.This figure shows both the silicon structures of these elements and their graphical symbolic representation as would be seen in a circuit diagram. The BJT shown is an NPN transistor, because it is composed of a sandwich of N-P-N doped silicon. When a small current is injected into the base terminal, a larger current is enabled to flow from the collector to the emitter.The FET shown is an N-channel FET, which is composed of two N-type regions separated by a P-type substrate. When a voltage is applied to the insulated gate terminal, a current is enabled to flow from the drain to the source. It is called N-channel, because the gate voltage induces an N-channel within the substrate, enabling current to flow between the N-regions.Another basic semiconductor structure is a diode, which is formed simply by a junction of N-type and P-type silicon. Diodes act like one-way valves by conducting current only from P to N. Special diodes can be created that emit light when a voltage is applied. Appropriately enough, these components are called light emitting diodes, or LEDs. These small lights are manufactured by the millions and are found in diverse applications from telephones to traffic lights.The resulting small chip of semiconductor material on which a transistor or diode is fabricated can be encased in a small plastic package for protection against damage and contamination from the out-side world.Small wires are connected within this package between the semiconductor sandwich and pins that protrude from the package to make electrical contact with other parts of the intended circuit. Once you have several discrete transistors, digital logic can be built by directly wiring these components together. The circuit will function, but any substantial amount of digital logic will be very bulky, because several transistors are required to implement each of the various types of logic gates.At the time of the invention of the transistor in 1947 by John Bardeen, Walter Brattain, and William Shockley, the only way to assemble multiple transistors into a single circuit was to buyseparate discrete transistors and wire them together. In 1959, Jack Kilby and Robert Noyce independently invented a means of fabricating multiple transistors on a single slab of semiconductor material. Their invention would come to be known as the integrated circuit, or IC, which is the foundation of our modern computerized world. An IC is so called because it integrates multiple transistors and diodes onto the same small semiconductor chip. Instead of having to solder individual wires between discrete components, an IC contains many small components that are already wired together in the desired topology to form a circuit.A typical IC, without its plastic or ceramic package, is a square or rectangular silicon die measuring from 2 to 15 mm on an edge. Depending on the level of technology used to manufacture the IC, there may be anywhere from a dozen to tens of millions of individual transistors on this small chip. This amazing density of electronic components indicates that the transistors and the wires that connect them are extremely small in size. Dimensions on an IC are measured in units of micrometers, with one micrometer (1mm) being one millionth of a meter. To serve as a reference point, a human hair is roughly 100mm in diameter. Some modern ICs contain components and wires that are measured in increments as small as 0.1mm!When an IC is designed and fabricated, it generally follows one of two main transistor technologies: bipolar or metal-oxide semiconductor (MOS). Bipolar processes create BJTs, whereas MOS processes create FETs. Bipolar logic was more common before the 1980s, but MOS technologies have since accounted the great majority of digital logic ICs. N-channel FETs are fabricated in an NMOS process, and P-channel FETs are fabricated in a PMOS process. In the 1980s, complementary-MOS, or CMOS, became the dominant process technology and remains so to this day. CMOS ICs incorporate both NMOS and PMOS transistors.Application Specific Integrated CircuitAn application-specific integrated circuit (ASIC) is an integrated circuit (IC) customized for a particular use, rather than intended for general-purpose use. For example, a chip designed solely to run a cell phone is an ASIC. In contrast, the 7400 series and 4000 series integrated circuits are logic building blocks that can be wired together for use in many different applications.As feature sizes have shrunk and design tools improved over the years, the maximum complexity (and hence functionality) possible in an ASIC has grown from 5,000 gates to over 100 million.Modern ASICs often include entire 32-bit processors, memory blocks including ROM, RAM, EEPROM, Flash and other large building blocks. Such an ASIC is often termed a SoC (System-on-Chip). Designers of digital ASICs use a hardware description language (HDL), such as Verilog or VHDL, to describe the functionality of ASICs.Field-programmable gate arrays (FPGA) are the modern day equivalent of 7400 series logic and a breadboard, containing programmable logic blocks and programmable interconnects that allow the same FPGA to be used in many different applications. For smaller designs and/or lower production volumes, FPGAs may be more cost effective than an ASIC design. The non-recurring engineering cost (the cost to setup the factory to produce a particular ASIC) can run into hundreds of thousands of dollars.The general term application specific integrated circuit includes FPGAs, but most designers use ASIC only for non-field programmable devices and make a distinction between ASIC and FPGAs.中文翻译:集成电路集成电路数字逻辑和电子电路由称为晶体管的电子开关得到它们的(各种)功能。

电子信息类专业英语第4章

Unit 4 Integrated Circuit

The key to the transistor’s rapid development was the use of silicon instead of wire as the basic conductive material. This element, which comprises 28 percent of the earth’s crust, is not only stable over a wide range of temperatures, but also offers dependable manufacturing control.

low power dissipation

低功耗

超大规

Unit 4 Integrated Circuit

Expressions

subject to 遭受

take up

占有

lead to

导致

call upon

号召

such as

比如

make up

形成

lie in...

位于…,在于…

be classified by function into 按功能分类为

Unit 4 Integrated Circuit

The development of integrated circuits has revolutionized the fields of communications, information handling, and computing. Integrated circuits reduce the size and the weight of devices and lower manufacturing and system costs, while at the same time providing high speed, excellent functional performance, low power dissipation and increased reliability. ICs are widely used in the electronic industry.

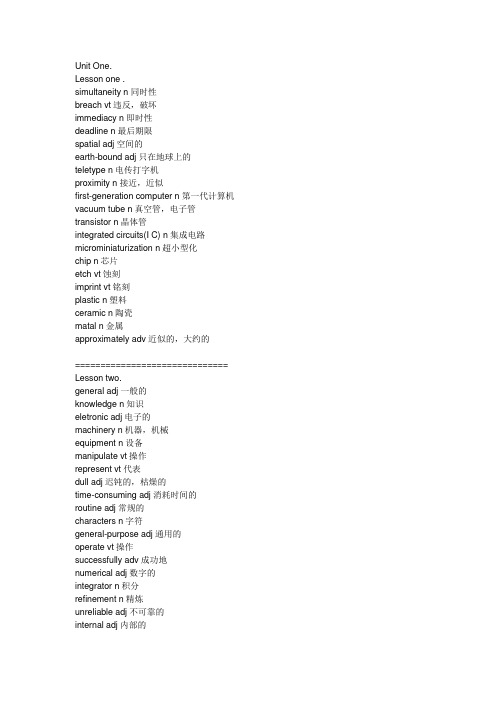

IntegratedCircuits集成电路电子信息类专业英语计算机类专业英语文