caputer生成网表报错原因解析#(精选.)

caputer生成网表报错原因解析演示教学

c a p u t e r生成网表报错原因解析(1)Warning "No_connect"#1 Warning [ALG0047] "No_connect" property on Pin "P1.8" ignored forP1: SCHEMATIC1, 13)URAT (7.90, 1.20). Connecting pin to net "N16811229".&H)K]-hwM$k3D3pd-T$W7heALG0047,这个警告基本可以忽略;造成这个问题的原因是,设计之初先对器件相关的管脚上加上'X'(也就是NC符号),更新设计的过程又对管脚做了连接处理;但是后面的连接处理没有去掉管脚的NC 属性,不信的话把那个管脚上的net删掉看看。

RG9f解决办法很简单,对这些管脚再做一次NC(2)Warning Part Name#5 Warning [ALG0016] Part Name "CAP PN_C100UP-6.3V-SMT-S_100UF/6.3V" is renamed to "CAP PN_C100UP-6.3V-SMT-S_100UF/"这个警告不可避免,allegro对相关的属性名称进行合并,超过一定数量的字符就截掉;在命名规范的前提下就不考虑这个警告了。

无法根治这个#2 Warning [ALG0016] Part Name "?j#w?rm之类的错误在于你建立元件原理图的时候你的原件Value值太长了超过32个字符,从而使系统在进行命名规范的时候溢出,而出错,很简单的,只写关键元件名,比如 A2541P10_HDR2X5-100MIL_2X5 HEADER" is renamed to "A2541P10_HDR2X5-100MIL_2X5 HEAD错误只需要把2X5 HEADER更改为A2541P10,去除中间的空格即可.Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for component instance C255:PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instanceC255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Disp (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instanceC245: PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)比较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308. Check the name and value syntax for invalid characters in theprimitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the packaging operation did notcomplete. Check the pxl.log file for the errors causingthis situation and package the design again.#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has encountered a null object ID. The design may not have been saved correctly. Save the schematic and rerun packaging.#187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\motherboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done*******掌握排错方法,查找文件pstchip.dat,第on line 5308 看看错误,便可以解决(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决*********************************************************** *********************** Netlisting the design*********************************************************** **********************Design Name:E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File:D:\Cadence\SPB_16.2\tools\capture\allegro.cfgSpawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"#1 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property for component instance MG2: Basic, PG06_Stepmotor (180.34, 83.82) .#2 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property for component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64) .#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in footprint names. The supported characters include Alphabets, Numerics, Underscore(_) and Hyphen(-).#4 Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#14 Warning [ALG0051] Pin "GND" is renamed to "GND#W8" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).这条警告信息,在命名规范的前提下就不考虑这个警告了。

Cadence中Capture向Allegro中导入网表时的常见错误

一、Capture生成netlist的时候报错:1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed错误解释:allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不一样,allegro.cfg 文件找不到是理所当然的。

处理办法:点生成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j"CC2430_DEMO"#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).#17 Aborting Netlisting... Please correct the above errors and retry.错误解释:Error [ALG0012] Property "PCB Footprint" missing from part <Part Reference>: <Schematic> , <Page> (<LocationX> , <LocationY)>A PCB Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.在Allegro中,每个器件都需要一个PCB封装。

Cadence中Capture向Allegro中导入网表时的常见错误

一、Capture生成netlist的时候报错:1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed错误解释:allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不一样,allegro.cfg 文件找不到是理所当然的。

处理办法:点生成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j"CC2430_DEMO"#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).#17 Aborting Netlisting... Please correct the above errors and retry.错误解释:Error [ALG0012] Property "PCB Footprint" missing from part <Part Reference>: <Schematic> , <Page> (<LocationX> , <LocationY)>A PCB Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.在Allegro中,每个器件都需要一个PCB封装。

【免费下载】cadence生成网络表时出现如下错误解决办法

U(ZE0B5L5b%X;n4g Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for componen t instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Disp (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C245: PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)比较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308.Check the name and value syntax for invalid characters in theprimitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the pac kaging operation did not complete. Check the pxl.log file for the errors causing this situ ation and package the design again.#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has enc ountered a null object ID. The design may not have been saved correctly. Save the sc hematic and rerun packaging.#187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\motherb oard.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done*******掌握排错方法,查找文件pstchip.dat,第on line 5308 看看错误,便可以解决(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决********************************************************************************** Netlisting the design*********************************************************************************Design Name:E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File:D:\Cadence\SPB_16.2\tools\capture\allegro.cfgSpawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basic board.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"#1 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance MG2: Basic, PG06_Stepmotor (180.34, 83.82) .#2 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64) .#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in foot print names. The supported characters include Alphabets, Numerics, Underscore(_) and Hyphen(-).#4 Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboa rd.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#14 Warning [ALG0051] Pin "GND" is renamed to "GND#W8" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).这条警告信息,在命名规范的前提下就不考虑这个警告了。

ORCAD出ALLEGRO网表非法错误案例:

错误报告内容:Spawning... "D:\Cadence\SPB_16.5\tools\capture\pstswp.exe" -pst -d"e:\work\yuleying\hj-am13-mb-0.0.0\sch\hj-am13-mb-v000\hj-am13-mb-v000.dsn" -n "e:\work\yuleying\hj-am13-mb-0.0.0\sch\hj-am13-mb-v000\allegro" -c"D:\Cadence\SPB_16.5\tools\capture\allegro.cfg" -v 3 -l 31 -s "" -j "PCB Footprint"-hpath "HPathForCollision"#1 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#2 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#3 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#4 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#5 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#6 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#7 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#8 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#9 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#10 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#11 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#12 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#13 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#14 ERROR(ORCAP-36055): Illegal character in \hj-am13-mb-v0.0.0(a10)\.#15 ERROR(ORCAP-36035): Multiple pin GND's which have different nets connected for J10: SCHEMATIC1,6.VIDEO_DEC (96.52, 175.26).#16 ERROR(ORCAP-36018): Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.5\tools\capture\pstswp.exe" -pst -d"e:\work\yuleying\hj-am13-mb-0.0.0\sch\hj-am13-mb-v000\hj-am13-mb-v000.dsn" -n "e:\work\yuleying\hj-am13-mb-0.0.0\sch\hj-am13-mb-v000\allegro" -c"D:\Cadence\SPB_16.5\tools\capture\allegro.cfg" -v 3 -l 31 -s "" -j "PCB Footprint"-hpath "HPathForCollision"INFO(ORCAP-32005): *** Done ***分析原因:首先确认了是非法字符,ORCAD包含的非法字符有:”/”、“<”、“>”、“#”、“$”、“(”、“)”。

caputer生成网表报错原因解析

(1)Warning "No_connect"#1 Warning [ALG0047] "No_connect" property on Pin "P1.8" ignored forP1: SCHEMATIC1, 13)URAT (7.90, 1.20). Connecting pin to net "N16811229".&H)K]-hwM$k3D3pd-T$W7heALG0047,这个警告基本可以忽略;造成这个问题的原因是,设计之初先对器件相关的管脚上加上'X'(也就是NC符号),更新设计的过程又对管脚做了连接处理;但是后面的连接处理没有去掉管脚的NC 属性,不信的话把那个管脚上的net删掉看看。

RG9f解决办法很简单,对这些管脚再做一次NC(2)Warning Part Name#5 Warning [ALG0016] Part Name "CAP PN_C100UP-6.3V-SMT-S_100UF/6.3V" is renamed to "CAP PN_C100UP-6.3V-SMT-S_100UF/"这个警告不可避免,allegro对相关的属性名称进行合并,超过一定数量的字符就截掉;在命名规范的前提下就不考虑这个警告了。

无法根治这个#2 Warning [ALG0016] Part Name "?j#w?rm之类的错误在于你建立元件原理图的时候你的原件Value值太长了超过32个字符,从而使系统在进行命名规范的时候溢出,而出错,很简单的,只写关键元件名,比如 A2541P10_HDR2X5-100MIL_2X5 HEADER" is renamed to "A2541P10_HDR2X5-100MIL_2X5 HEAD错误只需要把2X5 HEADER更改为A2541P10,去除中间的空格即可.Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for component instance C255:PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instanceC255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Disp (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instanceC245: PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)比较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308. Check the name and value syntax for invalid characters intheprimitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the packaging operation did not complete. Check the pxl.log file for the errors causingthis situation and package the design again.#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has encountered a null object ID. The design may not have been saved correctly. Save the schematic and rerun packaging.#187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\motherboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done*******掌握排错方法,查找文件pstchip.dat,第on line 5308 看看错误,便可以解决(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决*********************************************************** *********************** Netlisting the design*********************************************************** **********************Design Name:E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File:D:\Cadence\SPB_16.2\tools\capture\allegro.cfgSpawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"#1 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property for component instance MG2: Basic, PG06_Stepmotor (180.34, 83.82) .#2 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property for component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64) .#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in footprint names. The supported characters include Alphabets, Numerics, Underscore(_) and Hyphen(-).#4 Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#14 Warning [ALG0051] Pin "GND" is renamed to "GND#W8" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).这条警告信息,在命名规范的前提下就不考虑这个警告了。

Cadence中Capture向Allegro中导入网表时的常见错误讲解学习

一、Capture生成netlist的时候报错:1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed错误解释:allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不一样,allegro.cfg 文件找不到是理所当然的。

处理办法:点生成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j"CC2430_DEMO"#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).#17 Aborting Netlisting... Please correct the above errors and retry.错误解释:Error [ALG0012] Property "PCB Footprint" missing from part <Part Reference>: <Schematic> , <Page> (<LocationX> , <LocationY)>A PCB Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.在Allegro中,每个器件都需要一个PCB封装。

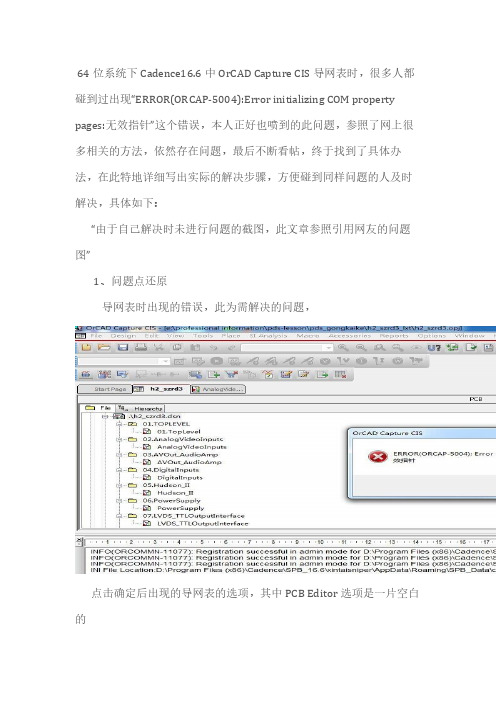

candence网标 (orcap-5004)错误解决方法

64位系统下Cadence16.6中OrCAD Capture CIS导网表时,很多人都碰到过出现“ERROR(ORCAP-5004):Error initializing COM property pages:无效指针”这个错误,本人正好也喷到的此问题,参照了网上很多相关的方法,依然存在问题,最后不断看帖,终于找到了具体办法,在此特地详细写出实际的解决步骤,方便碰到同样问题的人及时解决,具体如下:“由于自己解决时未进行问题的截图,此文章参照引用网友的问题图”1、问题点还原导网表时出现的错误,此为需解决的问题,点击确定后出现的导网表的选项,其中PCB Editor选项是一片空白的2、解决办法先打开我的电脑C盘,按照此目录“C:\Windows\SysWOW64”找到cmd.exe的应用点击鼠标右键以管理员身份运行进入DOS命令窗口下先复制如下这一行的代码(其中相应文件的路径请按照自己安装的文件路径进行修改)regsvr32 "D:\Program Files(x86)\Cadence\SPB_16.6\tools\capture\orTrueReuse.ocx"在DOS窗口下点击鼠标右键选择粘贴(不能按ctr+v的快捷键)粘贴第一行后如图所示之后直接按回车键,第一个文件更改成功再复制下行的代码(其中相应文件的路径请按照自己安装的文件路径进行修改)regsvr32 "D:\Program Files(x86)\Cadence\SPB_16.6\tools\capture\orpxllite.ocx"继续在DOS窗口下粘贴任然按回车键,第二个文件更改成功此时,两个文件的更改已经成功,我们重新打开Cadence16.6中OrCAD Capture CIS的文件进行查看我们可以看到PCB Editor选项已经正常了,问题完美解决!。

cadence生成网络表时出现如下错误解决办法

U(ZE0B5L5b%X;n4g Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for componen t instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Dis p (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance C245: PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)比较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308.Check the name and value syntax for invalid characters in theprimitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the pac kaging operation did not complete. Check the pxl.log file for the errors causing this situ ation and package the design again.#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has enc ountered a null object ID. The design may not have been saved correctly. Save the sc hematic and rerun packaging.#187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\motherb oard.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done*******掌握排错方法,查找文件pstchip.dat,第on line 5308 看看错误,便可以解决(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决********************************************************************************** Netlisting the design*********************************************************************************Design Name:E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File:D:\Cadence\SPB_16.2\tools\capture\allegro.cfgSpawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basic board.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"#1 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance MG2: Basic, PG06_Stepmotor (180.34, 83.82) .#2 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property f or component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64) .#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in foot print names. The supported characters include Alphabets, Numerics, Underscore(_) and Hyphen(-).#4 Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboa rd.dsn" -n "E:\FPGA\SCH\allegro" -c "D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" after substituting illegal ch aracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACO NFIG (2.40, 3.10).#14 Warning [ALG0051] Pin "GND" is renamed to "GND#W8" after substituting illegal c haracters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGAC ONFIG (2.40, 3.10).这条警告信息,在命名规范的前提下就不考虑这个警告了。

ORCAD导ALLEGRO网表错误:ERROR(ORCAP

ORCAD导ALLEGRO⽹表错误:ERROR(ORCAP错误报告内容:Spawning..."D:\Cadence\SPB_16.5\tools\capture\pstswp.exe" -pst -d"e:\work\yuleying\hj-am13-mb-0.0.0\sch\hj-am13-mb-v000\hj-am13-mb-v000.dsn"-n "e:\work\yuleying\hj-am13-mb-0.0.0\sch\hj-am13-mb-v000\allegro" -c"D:\Cadence\SPB_16.5\tools\capture\allegro.cfg" -v 3 -l31 -s "" -j "PCBFootprint" -hpath "HPathForCollision"#1 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#2 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#3 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#4 ERROR(ORCAP-36055): Illegalcharacter in \hj-am13-mb-v0.0.0(a10)\.#5 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#6 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#7 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#8 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#9 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#10 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#11 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#12 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#13 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#14 ERROR(ORCAP-36055):Illegal character in \hj-am13-mb-v0.0.0(a10)\.#15 ERROR(ORCAP-36035): Multiple pin GND's whichhave different nets connected for J10: SCHEMATIC1, 6.VIDEO_DEC(96.52, 175.26).#16 ERROR(ORCAP-36018):Aborting Netlisting... Please correct the above errors and retry. Exiting... "D:\Cadence\SPB_16.5\tools\capture\pstswp.exe"-pst -d"e:\work\yuleying\hj-am13-mb-0.0.0\sch\hj-am13-mb-v000\hj-am13-mb-v000.dsn"-n "e:\work\yuleying\hj-am13-mb-0.0.0\sch\hj-am13-mb-v000\allegro" -c"D:\Cadence\SPB_16.5\tools\capture\allegro.cfg" -v 3 -l31 -s "" -j "PCBFootprint" -hpath "HPathForCollision"INFO(ORCAP-32005): *** Done***分析原因:⾸先确认了是⾮法字符,ORCAD包含的⾮法字符有:”/”、“<”、“>”、“#”、“$”、“(”、“)”。

OrCAD Capture CIS导网表常见问题

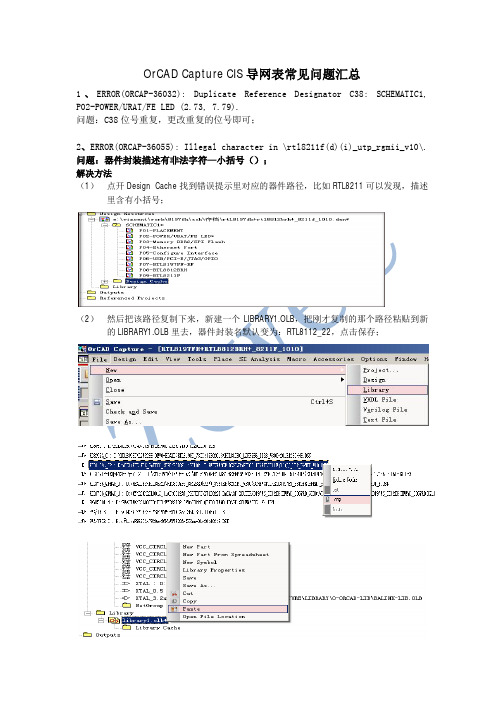

OrCAD Capture CIS导网表常见问题汇总1、ERROR(ORCAP-36032): Duplicate Reference Designator C38: SCHEMATIC1, P02-POWER/URAT/FE LED (2.73, 7.79).问题:C38位号重复,更改重复的位号即可;2、ERROR(ORCAP-36055): Illegal character in \rtl8211f(d)(i)_utp_rgmii_v10\. 问题:器件封装描述有非法字符—小括号();解决方法(1)点开Design Cache找到错误提示里对应的器件路径,比如RTL8211可以发现,描述里含有小括号;(2)然后把该路径复制下来,新建一个LIBRARY1.OLB,把刚才复制的那个路径粘贴到新的LIBRARY1.OLB里去,器件封装名默认变为:RTL8112_22,点击保存;(3)回到Design Cache找到器件路径,把路径替换为新建LIBRARY1.OLB的路径,并下拉找到8211对应的封装名:RTL8112_22;(4)更改后路径变为如下,已无非法字符了;3、ERROR(ORCAP-36071): Illegal character "Dot(.)" found in "PCB Footprint" property for component instance T25: SCHEMATIC1, P04-Ethernet Port (7.72, 6.48) .问题:PCB Footprint描述含有非法字符-“.”,在PCB Footprint里把点去掉即可;4、ERROR(ORCAP-36041): Duplicate Pin Name "XTALP" found on Package XTAL , Y1 Pin Number 3: SCHEMATIC1, P08-RTL8812BRH (16.51, 13.40). Please renumber one of these.问题:有2个管脚封装名称相同,都是XTALP,点开封装,更改管脚名称即可;5、ERROR(ORCAP-36022): Pin number missing from Pin "1" of Package CAP NP , C101: SCHEMATIC1, P04-Ethernet Port (1.80, 6.10). All pins should be numbered.问题:电容C101,有管脚没有管脚编码,点开电容封装(Eidit Part)把每个管脚编号及写上名称即可;6、WARNING(ORCAP-36038): "No_connect" property on Pin "U1.98" ignored for U1: SCHEMATIC1, P02-POWER/URAT/FE LED (16.93, 11.04). Connecting pin to net "VFB2V5_1V8".问题:U1的98pin属性是No_connect,但是却有连线,需点开编辑属性,找到pin栏,把no-connect属性那个勾去掉即可;7、WARNING(ORCAP-36006): Part Name "SMA/UFLR_0_RF_CABLE_P3M5_SMA/UFLR" is renamed to "SMA/UFLR_0_RF_CABLE_P3M5_SMA/UF".问题:封装路径名字太长(导网表时默认是31字节),按照第2点的第2步,粘贴路径后再rename,把路径名称改短一点即可;8、WARNING(ORCAP-36006): Part Name "C_C0201_贴片电容_1NF" is renamed to "C_C0201__1NF".问题:part name里有中文字体,需去掉,如下图,把part的class值设置为空格即可;9、WARNING(ORCAP-36006):Part Name"SPDT/SKYWORKS/SKY85601-21_3_QFN16_P0M5_3M4X3M4__SKY85717-21/RTC5638H," is renamed to "SPDT/SKYWORKS/SKY85601-21_3_QFN16_P0M5_3M4X3M4__SK".问题:part的路径名太长,在Design Cache里找到对应器件part,复制到新建的LIBRARY1.OLB 里,并重新命名,再把part路径按照第2点第3步方法更新即可;10、ERROR(SPCODD-248): All physical pins are common in section 9 of physical part 'RTL8197F-DRQFN128_QFN128-1010-5-H9-E55__RTL8197FH'. Each section must have at least one non-common pin.问题:打开封装可知,芯片RTL8197FH的封装分为好多个部分。

Cadence16网表导入错误及其警告信息总结

Cadence16⽹表导⼊错误及其警告信息总结Cadence 16导⼊⽹表的时候,经常会弹出错误,让⼈头疼的不是错误很多,⽽是莫名其妙,熟练的布线⼯程师可以5分钟之内⼲掉所有的警告信息或者是错误,但是有⼏个类型的错误可就不这么好搞了.下⾯我们来看看常见的⼏种莫名其妙类型的错误。

AWARNING(SPMHNI-194): Symbol 'TO252' for device '78M05' not found in PSMPATH or must be "dbdoctor"ed. Symbol exte nts are greater than the drawing extents ... increase the drawing extents.BERROR(SPMHNI-196): Symbol 'FQAP32' for device 'U1' has extra pin '31'.ERROR(SPMHNI-196): Symbol 'FQAP32' for device 'U2' has extra pin '32'.CERROR(SPMHNI-337): Symbol 'SO14' for device 'LM339' warning(SPMHUNT-127): Could not find padstack SMT80X26.[he lp]A类的错误的意思是说封装Symbol尺⼨⼤于绘图的尺⼨这种错误的解决办法,需要重新回到Allegro当中重新设置相关.dra⽂件绘图区的尺⼨⼤⼩,如果在当前的Allegro PCB⼯程当中,那你是搞不定的。

就是说当绘制封装图的时候,就要把封装的整个绘图区的尺⼨设的⽐相应封装的尺⼨稍微⼤那么⼀点点,就可以了。

常见的导网表报错处理

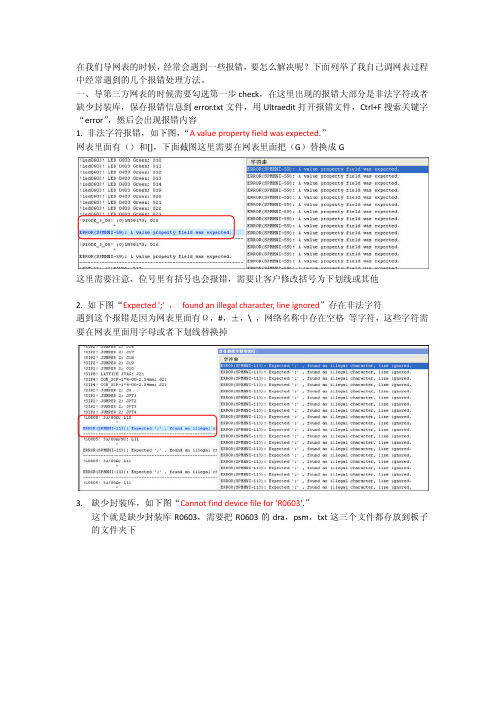

在我们导网表的时候,经常会遇到一些报错,要怎么解决呢?下面列举了我自己调网表过程中经常遇到的几个报错处理方法。

一、导第三方网表的时候需要勾选第一步check,在这里出现的报错大部分是非法字符或者缺少封装库,保存报错信息到error.txt文件,用Ultraedit打开报错文件,Ctrl+F搜索关键字“error”,然后会出现报错内容1. 非法字符报错,如下图,“A value property field was expected.”网表里面有()和[],下面截图这里需要在网表里面把(G)替换成G这里需要注意,位号里有括号也会报错,需要让客户修改括号为下划线或其他2. 如下图“Expected ';' ,found an illegal character, line ignored”存在非法字符遇到这个报错是因为网表里面有Ω,#,±,\ ,网络名称中存在空格等字符,这些字符需要在网表里面用字母或者下划线替换掉3.缺少封装库,如下图“Cannot find device file for 'R0603'.”这个就是缺少封装库R0603,需要把R0603的dra,psm,txt这三个文件都存放到板子的文件夹下4.假如导第三网表时第一步Check时无报错,但是第二步导入网表时报错,这时常见的就多于原理图时不会报错,,封装库数多于原理图时不会报错,封装库引脚是引脚不匹配。

(注意调第三方网表时注意调第三方网表时,封装库引脚数引脚数少于封装库才会报错)下图ERROR“Pin number '9' not in device file 'sop8-127-620x500hs229x22~”意思是pin9脚不在封装库里面遇到引脚不匹配时就需要找建库人员核对,看是否封装库缺少引脚了,或者是客户的原理图中多了引脚。

二、导第一方网表常见报错1.非法字符的报错Package property error: 'VALUE'='0.022μ'. Illegal character(s) present in the name or value这里就是Value值里面有非法字符μ,同样也是用Ultraedit工具打开第一方网表的pstchip.dat文件,在里面将μ替换成U保存2. 缺少封装库报错,如下图缺少封装库R0603_3P ,需要把R0603_3P 的dra ,psm 文件放到目录下。

Cadence中Capture向Allegro中导入网表时的常见错误

一、Capture生成netlist的时候报错:1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed错误解释:allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不一样,allegro.cfg 文件找不到是理所当然的。

处理办法:点生成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j"CC2430_DEMO"#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).#17 Aborting Netlisting... Please correct the above errors and retry.错误解释:Error [ALG0012] Property "PCB Footprint" missing from part <Part Reference>: <Schematic> , <Page> (<LocationX> , <LocationY)>A PCB Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.在Allegro中,每个器件都需要一个PCB封装。

failed to discovery tables to capture

failed to discovery tables to capture 我尝试进行数据采集时遇到了无法发现表格的问题。

当我开始采集数

据时,我预期在目标网页中找到一些表格来捕捉和提取所需的数据。

然而,我遇到了一些困难,无法找到任何表格来捕获。

首先,我仔细检查了网页的内容和结构。

我浏览了整个页面,查看源

代码,并使用开发者工具来分析页面的元素。

然而,在整个页面上,我没

有找到任何类似于表格或数据网格的元素。

这让我感到困惑,因为通常网

页上的数据通常是以表格的形式呈现的。

接下来,我尝试通过关键词来查找表格。

我在页面上使用了各种关键

词和短语,如“表格”、“数据网格”、“数据表”等。

然而,这些尝试

都没有找到我需要的表格。

我还检查了其他类似页面的网站,看看它们是否有相似的表格。

不幸

的是,我在其他网站上也没有找到所需的表格。

这使我怀疑是否存在任何

表格,或者是否有其他方法来捕获所需的数据。

在面对这个问题时,我开始考虑其他采集数据的方法。

我考虑使用Python的爬虫库来直接请求和解析页面的数据,而不是依赖于表格。

这

样可以更灵活地捕捉所需的数据,而不受表格的限制。

尽管我无法发现表格来捕捉数据,但我仍然有其他途径来获取所需的

信息。

通过对网页结构和源代码的分析,以及使用网页爬虫库进行直接请

求和解析,我相信我可以成功地采集到所需的数据。

OrCAD 导网表出现conflicting values of part name found on different sections of U1.

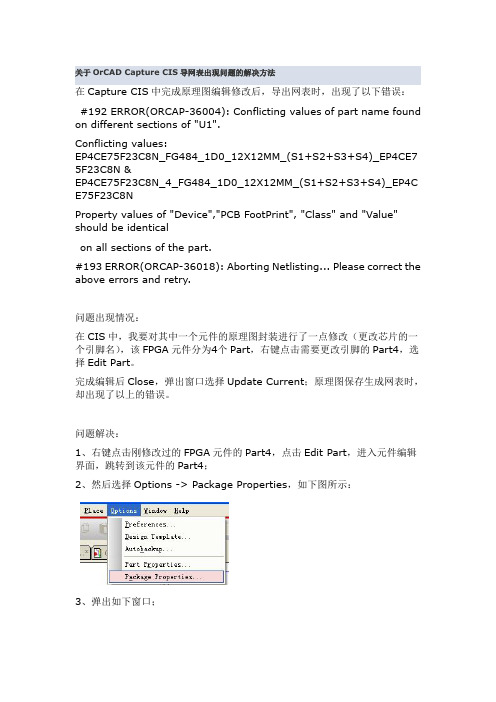

关于OrCAD Capture CIS导网表出现问题的解决方法在Capture CIS中完成原理图编辑修改后,导出网表时,出现了以下错误:#192ERROR(ORCAP-36004):Conflicting values of part name found on different sections of"U1".Conflicting values:EP4CE75F23C8N_FG484_1D0_12X12MM_(S1+S2+S3+S4)_EP4CE7 5F23C8N&EP4CE75F23C8N_4_FG484_1D0_12X12MM_(S1+S2+S3+S4)_EP4C E75F23C8NProperty values of"Device","PCB FootPrint","Class"and"Value" should be identicalon all sections of the part.#193ERROR(ORCAP-36018):Aborting Netlisting...Please correct the above errors and retry.问题出现情况:在CIS中,我要对其中一个元件的原理图封装进行了一点修改(更改芯片的一个引脚名),该FPGA元件分为4个Part,右键点击需要更改引脚的Part4,选择Edit Part。

完成编辑后Close,弹出窗口选择Update Current;原理图保存生成网表时,却出现了以上的错误。

问题解决:1、右键点击刚修改过的FPGA元件的Part4,点击Edit Part,进入元件编辑界面,跳转到该元件的Part4;2、然后选择Options->Package Properties,如下图所示:3、弹出如下窗口;注意到该Part Name变成了EP4CE75F23C8N_4,多了个尾缀_4,将该尾缀去掉,保存并更新元件;然后再导出网表,以上出现的错误问题解决。

Orcad生成Allegro网表失败解决方法

Orcad⽣成Allegro⽹表失败解决⽅法错误提⽰:ERROR(SPCODD-433):Error at line 515 in file E:\NUMERICSIGN\ALLEGRO/pstxnet.dat. Error in syntax.在如下博⽂找到类似问题,发现果然是“'”pin脚定义引起的。

PCB Editor, Allegro不识别。

修改器件pin脚定义后okey! 感谢!幻翼的百度空间Cadence⽹表错误2009-02-08 13:49原理图过了DRC检查,到了⽣成⽹表的时候,突然出现以下错误:#38 DDB_ERROR: Terminating character ''''='''' not found on line 20740.DDB_INFO: File E:\laoyao\2205\SCH\allegro/pstxnet.dat not loaded打开pstxnet.dat⽂件,找到20740⾏,按照⾥⾯的描述找到相应元件的管脚,发现这是⼀个空管脚,标上了叉。

仔细检查发现没什么问题,重新调⽤该元件。

再次⽣成⽹表,出现了同样的错误,只是到了另外⼀个元件的空管脚。

不管了,再次重新调⽤……这时⼀直以为只要将有空脚的元件重新调⽤就可以了。

终于错误到了⽂件的最后⼀⾏,可是却出现了下⾯的错误:Error: Line 20926 in file E:\laoyao\2205\SCH\allegro/pstxnet.dat:Error in SyntaxDetected in function: pstParseSubscript这时的pstxnet.dat已到了最后⼀⾏,是空⽩⾏,晕,空⽩⾏居然会有错误!百思不得其解,把空⽩⾏上⾯那⾏描述的元件再替换⼀次,这时⼜出现了第⼀次显⽰的错误。

再次重新调⽤替换,⼀直到替换到ARM这个元件,狂晕,重新调⽤也不⾏!后来发现开始已经调⽤过的元件空脚还会出现问题,难道是盗版Cadence⼤BUG?只要是元件的空管脚都会出现这个错误。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(1)Warning "No_connect"#1 Warning [ALG0047] "No_connect" property on Pin "P1.8" ignored forP1: SCHEMATIC1, 13)URAT (7.90, 1.20). Connecting pin to net "N16811229".&H)K]-hwM$k3D3pd-T$W7heALG0047,这个警告基本可以忽略;造成这个问题的原因是,设计之初先对器件相关的管脚上加上'X'(也就是NC符号),更新设计的过程又对管脚做了连接处理;但是后面的连接处理没有去掉管脚的NC 属性,不信的话把那个管脚上的net删掉看看。

RG9f解决办法很简单,对这些管脚再做一次NC(2)Warning Part Name#5 Warning [ALG0016] Part Name "CAP PN_C100UP-6.3V-SMT-S_100UF/6.3V" is renamed to "CAP PN_C100UP-6.3V-SMT-S_100UF/"这个警告不可避免,allegro对相关的属性名称进行合并,超过一定数量的字符就截掉;在命名规范的前提下就不考虑这个警告了。

无法根治这个#2 Warning [ALG0016] Part Name "?j#w?rm之类的错误在于你建立元件原理图的时候你的原件Value值太长了超过32个字符,从而使系统在进行命名规范的时候溢出,而出错,很简单的,只写关键元件名,比如 A2541P10_HDR2X5-100MIL_2X5 HEADER" is renamed to "A2541P10_HDR2X5-100MIL_2X5 HEAD错误只需要把2X5 HEADER更改为A2541P10,去除中间的空格即可.Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for component instance C255:PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instanceC255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Disp (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instanceC245: PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)比较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308. Check the name and value syntax for invalid characters in theprimitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the packaging operation did not complete. Check the pxl.log file for the errors causingthis situation and package the design again.#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has encountered a null object ID. The design may not have been saved correctly. Save the schematic and rerun packaging.#187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\motherboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done*******掌握排错方法,查找文件pstchip.dat,第on line 5308 看看错误,便可以解决(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决*********************************************************** *********************** Netlisting the design*********************************************************** **********************Design Name:E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File:D:\Cadence\SPB_16.2\tools\capture\allegro.cfgSpawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"#1 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property for component instance MG2: Basic, PG06_Stepmotor (180.34, 83.82) .#2 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property for component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64) .#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in footprint names. The supported characters include Alphabets, Numerics, Underscore(_) and Hyphen(-).#4 Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#14 Warning [ALG0051] Pin "GND" is renamed to "GND#W8" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).这条警告信息,在命名规范的前提下就不考虑这个警告了。